EMEA ACADEMIC

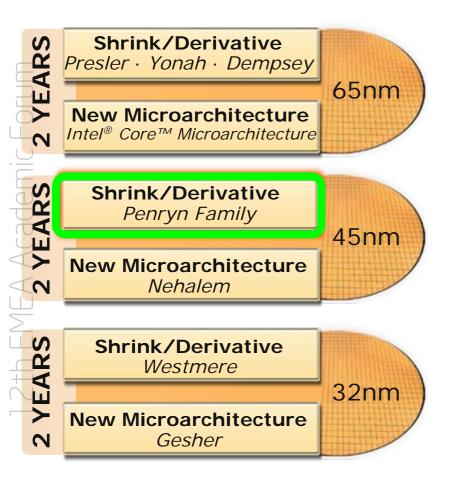

### Technical Overview of the 45nm Next Generation Intel® Core™ Microarchitecture (Penryn)

Ronny Ronen Sr. Principal Engineer Corporate Technology Group June 13, 2007

Based on Stephen Fischer's 4/2006 Intel Developer Forum (IDF) talk

© 2007 Intel Corporation

## **IDC – Israel Development Center**

Located on Israel's Mediterranean coast, Haifa is the home of Intel's Israel Development Center (IDC).

IDC was established in 1974, and is Intel's first development center outside the US. The center is a multidisciplinary team, with close to 2000 employees.

Many of Intel's leading products were developed and originated at IDC.

IDC's employees are currently working on Intel's future microprocessors, CAD tools, advanced networking components and software technologies.

The Intel® Core™ Microarchitecture was developed in Haifa, Israel The Penryn Processor was developed in Folsom, US.

> Next Generation Intel® Core™ Microarchitecture Ronny Ronen, EMEA Academic Forum '07 4

- Penryn Family Design Goals

- Processor Architecture Basics

- Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture Refresh

- Intel 45nm High-K Silicon Technology

- Enhancing the Intel® Core™ Microarchitecture

- Microarchitecture Enhancements

- New Intel® SSE4 Instructions

- Power Management Enhancements

- Summary

2th EMEA Academic Forum

# Terminology

- Architecture/microarchitecture

- Intel® Core™ Microarchitecture → "Merom"

- Enhanced Intel® Core™ Microarchitecture → Penryn

- Products

- Intel® Core™ 2 Dou processor (65nm) → Merom/Conroe/Woodcrest

- <no name> (45nm) → Penryn

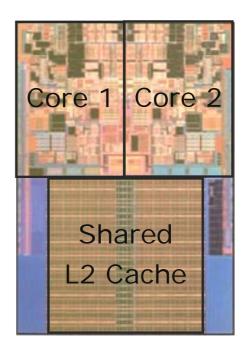

- Penryn is

EMEA Academic Four

Zth

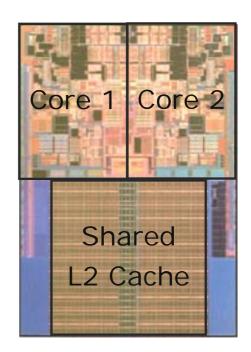

- Next generation based on "Merom" arch/microarch

- It will have both dual core and quad core versions

- The Dual core shares L2 cache

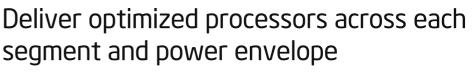

# Penryn Family Design Goals

Extend leadership in performance and energy efficiency

- Increase performance per given clock cycle

- Increase processor frequencies

- Further gains in energy efficiency

Deliver lead product for 45nm High K + metal gate process technology

Mobile, desktop, workstation, and server segments

- Penryn Family Design Goals

- Processor Architecture Basics

- Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture Refresh

- Intel 45nm High-K Silicon Technology

- Enhancing the Intel® Core™ Microarchitecture

- Microarchitecture Enhancements

- New Intel® SSE4 Instructions

- Power Management Enhancements

- Summary

2th EMEA Academic Forum

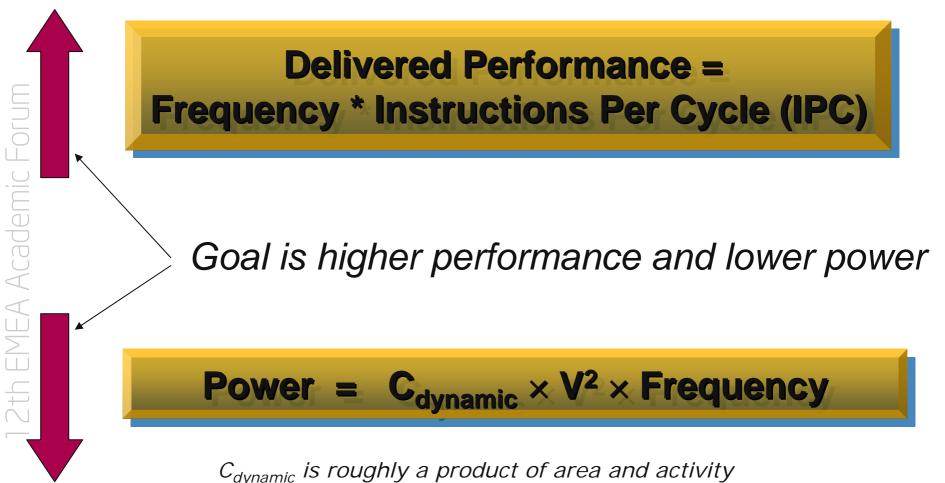

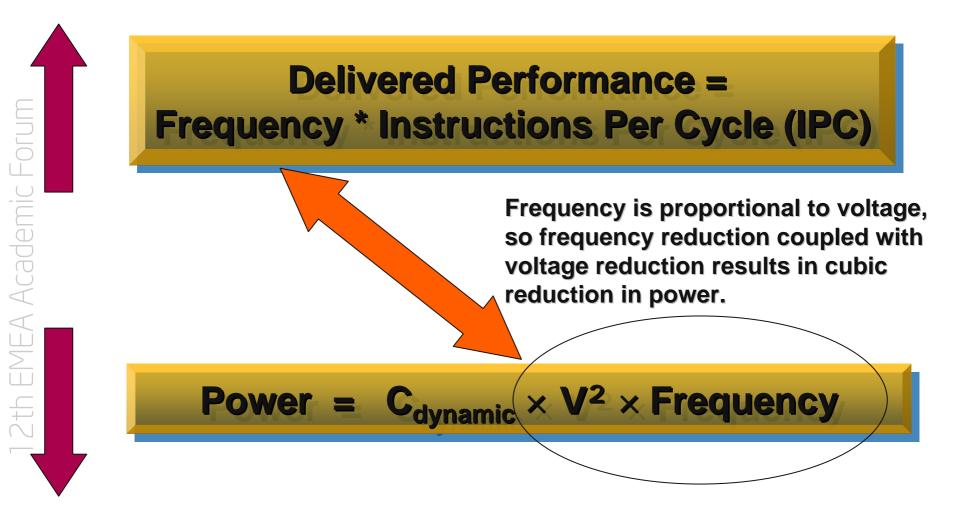

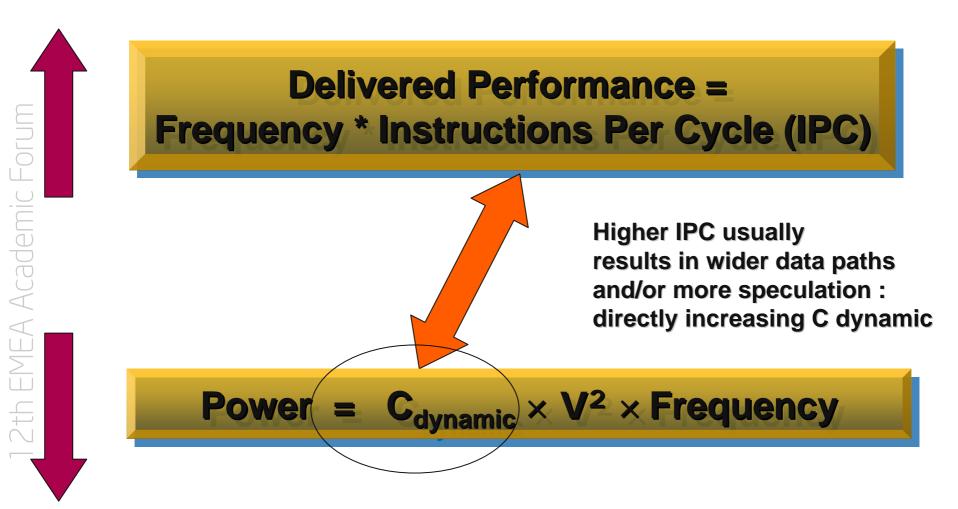

### **Processor Architecture Basics**

"how many bits" \* "how much do they toggle"

Next Generation Intel® Core<sup>™</sup> Microarchitecture Ronny Ronen, EMEA Academic Forum '07 **9**

### **Processor Architecture Basics**

Next Generation Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture Ronny Ronen, EMEA Academic Forum '07 **10**

### **Processor Architecture Basics**

Next Generation Intel® Core<sup>™</sup> Microarchitecture Ronny Ronen, EMEA Academic Forum '07 **11**

- Penryn Family Design Goals

- Processor Architecture Basics

- Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture Refresh

- Intel 45nm High-K Silicon Technology

- Enhancing the Intel® Core™ Microarchitecture

- Microarchitecture Enhancements

- New Intel® SSE4 Instructions

- Power Management Enhancements

- Summary

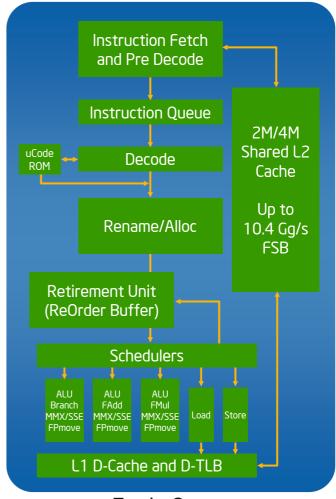

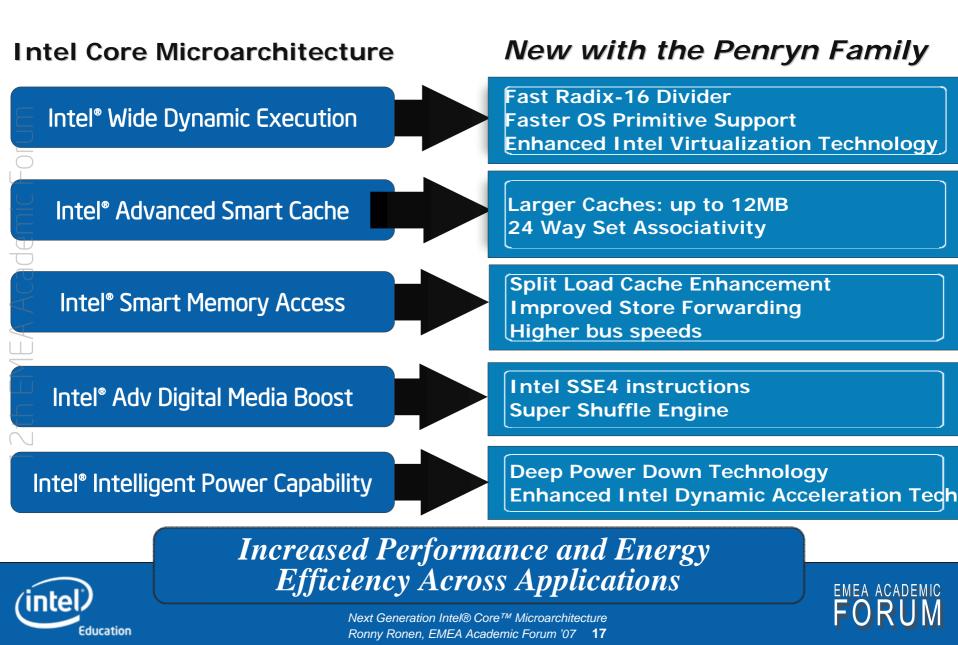

### Intel® Core™ Microarchitecture Refresh

#### Intel<sup>®</sup> Wide Dynamic Execution

4 instructions per clock cycle vs. 3; 14 Stage Pipe, Micro and Macro Fusion, Enhanced ALUs

#### Intel<sup>®</sup> Advanced Smart Cache

Each core pair can access shared L2 cache;

### Intel<sup>®</sup> Smart Memory Access

HW based Mem Disambiguation: "Load" can pass "Store"; Improved Prefetchers: Hiding latency to memory subsystem

#### Intel<sup>®</sup> Advanced Digital Media Boost

128 bit Single cycle SSE

#### Intel<sup>®</sup> Intelligent Power Capability

Ultra fine grain power control; Split bus for varying data width; Platform level power management

#### 'Each Core'

- Penryn Family Design Goals

- Processor Architecture Basics

- Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture Refresh

- Intel 45nm High-K Silicon Technology

- Enhancing the Intel® Core™ Microarchitecture

- Microarchitecture Enhancements

- New Intel® SSE4 Instructions

- Power Management Enhancements

- Summary

2th EMEA Academic Forum

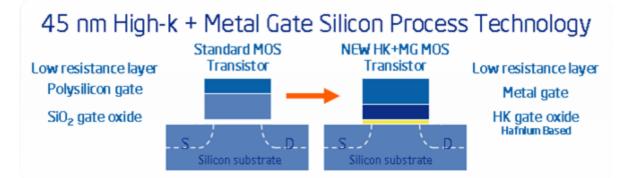

### Next Generation Intel 45 nm High-k Process Technology

- ~2x larger transistor budget provides freedom to add new features and higher performance with cost effective die sizes

- >20% faster transistor switching speed delivers higher core speeds and increased instructions per second

- Lower leakage current reduces power consumption or enables more capability and performance within a given power envelope compared to 65nm processors

High-k example: Hafnium oxide (HfO2) k >20

- Penryn Family Design Goals

- Processor Architecture Basics

- Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture Refresh

- Intel 45nm High-K Silicon Technology

- Enhancing the Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture

- Microarchitecture Enhancements

- New Intel® SSE4 Instructions

- Power Management Enhancements

- Summary

### Enhanced Intel® Core™ Microarchitecture

- Penryn Family Design Goals

- Processor Architecture Basics

- Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture Refresh

- Intel 45nm High-K Silicon Technology

- Enhancing the Intel® Core<sup>™</sup> Microarchitecture

- Microarchitecture Enhancements

- New Intel® SSE4 Instructions

- Power Management Enhancements

- Summary

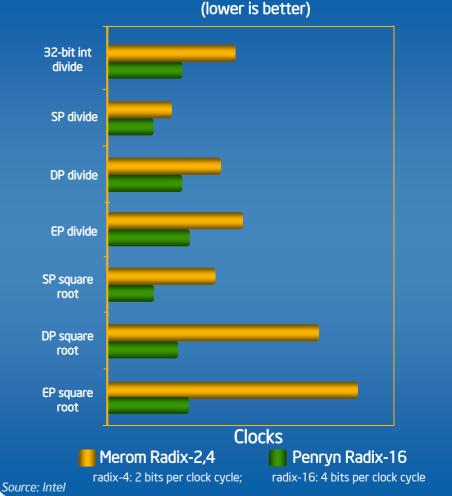

# Fast Radix-16 Divider

Leading edge divider performance 4 bits processed per cycle vs. 2 bits per cycle Innovative radix-16 based architecture Academi Utilized for both floating-point and integer operations Optimized square root Early-out algorithm for both integer and FP data allows lower latency 6 cycle minimum

Education

EMEA ACADEMIC

Maximum Processor Instruction Latency

### **On Avg: Doubles the Divide Execution Speed**

Next Generation Intel® Core<sup>™</sup> Microarchitecture Ronny Ronen, EMEA Academic Forum '07 **19**

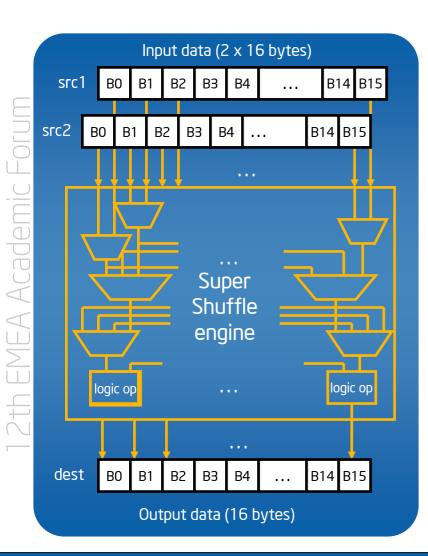

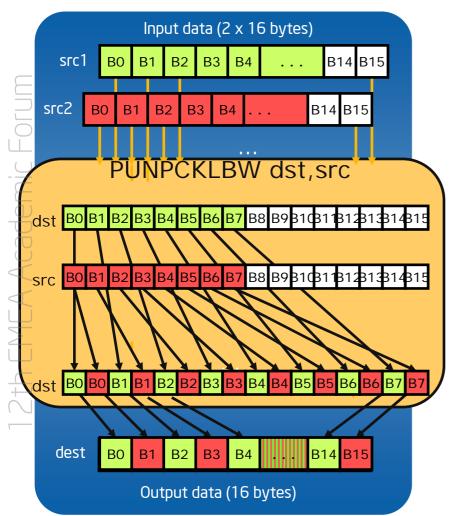

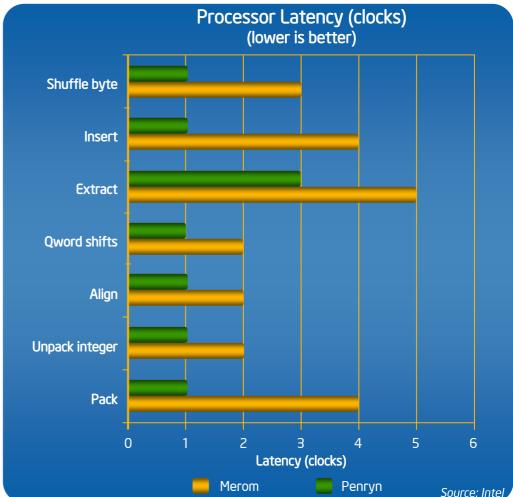

# **Super Shuffle Engine**

- Shuffle operations required for SSE data formatting operations

- Unpacking

- Packing

- Align concatenated sources

- Wide shifts

- Insertion and extraction

- Setup for horizontal arithmetic functions

- Penryn super shuffle engine performs 128 bit operation in single cycle

- No software changes required

Doubles shuffle speed

# **Super Shuffle Engine**

- Shuffle operations required for SSE data formatting operations

- Unpacking

- Packing

- Align concatenated sources

- Wide shifts

- Insertion and extraction

- Setup for horizontal arithmetic functions

- Penryn super shuffle engine performs 128 bit operation in single cycle

- No software changes required

Doubles shuffle speed

# Super Shuffle Engine

- Doubles the speed for most byte, word, and dword granular SSE data shuffle operations

- Also key capability for performance effective enabling of new SSE4 functionality

- Blends

- Dot product

- Multiple sum-of-abs differences

EMEA ACADEMIC

### 2X Faster SSE Shuffle Instruction Execution

Next Generation Intel® Core™ Microarchitecture Ronny Ronen, EMEA Academic Forum '07 22

Forum 2th EMEA Academic

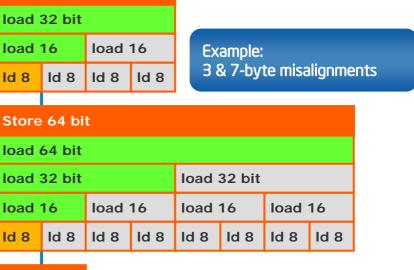

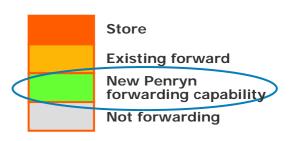

# **Store Forwarding: Misaligned Store**

Store 32 bit

**Id 8**

#### 8-byte misaligned store results can now be forwarded to a load

- Shortens load latency

- No longer has to wait for cache update

|        | Ехап         | nple:  |         |      |             |      | load 16 |      | load 16 |    |  |

|--------|--------------|--------|---------|------|-------------|------|---------|------|---------|----|--|

|        | 1-by         | te mis | alignmo | ent  |             |      | ld 8    | ld 8 | ld 8    | lo |  |

|        | Store 64 bit |        |         |      |             |      |         |      |         |    |  |

|        | load 64 bit  |        |         |      |             |      |         |      |         |    |  |

|        | load         | 32 bit |         |      | load 32 bit |      |         |      |         |    |  |

|        | load 16      |        | load 16 |      | load 16     |      | load 16 |      |         |    |  |

|        | ld 8         | ld 8   | ld 8    | ld 8 | ld 8        | ld 8 | ld 8    | ld 8 |         |    |  |

| 0 1    | 2            | 3      | 4       | 5    | 6           | 7    | 8       |      |         |    |  |

| Addres | s aligr      | nmen   | t       |      |             |      |         |      |         |    |  |

Education

B

### **Improved OS Synchronization Primitive** Performance

- Faster locked instruction performance

- Key primitive for multiple thread synchronization

- >Faster locks enable more concurrency between threads

- Up to 55-80% faster

### Faster interrupt masking control

- Execution time critical to OS for shared resource control

- Uarch improvements to eliminate pipeline stalls in the common case

- CLI/STI instrs as much as 2X faster

#### Example spin lock sequence:

Used for controlling access to shared resources (i.e. I/O, kernel state) Applicable for MT/MP OS env

| jns lock_acquired                      | ;atomic decrement<br>d ;exit if lock was 1 |

|----------------------------------------|--------------------------------------------|

| spin:                                  |                                            |

| pause                                  | ;otherwise loop until                      |

| cmp [edi], 0<br>jle spin               | ; lock is released                         |

| jmp spin_lock<br>lock_acquired:<br>ret | ;try to reacquire lock                     |

- Faster access of Time Stamp Counter

- RDTSC instr as much as **3X** faster

- Key functionality for database servers, OS time-of-day services frequent in transaction processing

Improves Server Performance Scalability

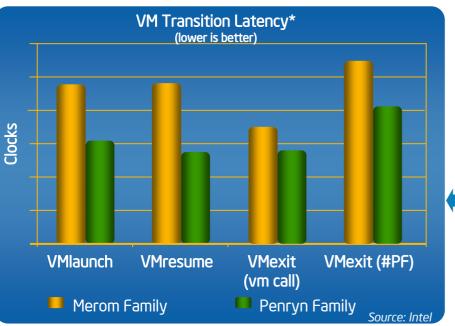

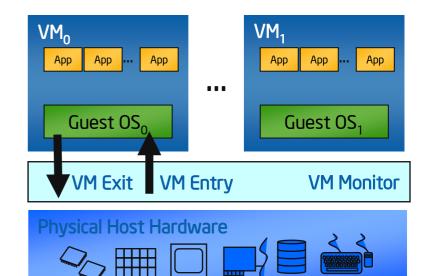

### **Virtualization Performance Improvements**

- Intel® Virtualization technology addresses today's IT concerns

- Data center consolidation

- Dynamic load balancing

- Disaster recovery

Penryn improves VT-x instruction context switch times by ~25-75%

\* Comparisons based on RTL simulations via micro-kernel workloads with cache hits

Next Generation Intel® Core<sup>™</sup> Microarchitecture Ronny Ronen, EMEA Academic Forum '07 **25**

### **Improved Caches**

• Up to 50% Larger Level 2 Cache

24-Way Set Associativity – Helps maximize utilization

of the larger L2 Cache

- Compared to 16-way associativity on previous generation

Minimizes Latency on Commonly Used Data

Academic Forum

- Penryn Family Design Goals

- Processor Architecture Basics

- Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture Refresh

- Intel 45nm High-K Silicon Technology

- Enhancing the Intel® Core™ Microarchitecture

- Microarchitecture Enhancements

- New Intel® SSE4 Instructions

- Power Management Enhancements

- Summary

EMEA Academic Forum 2th

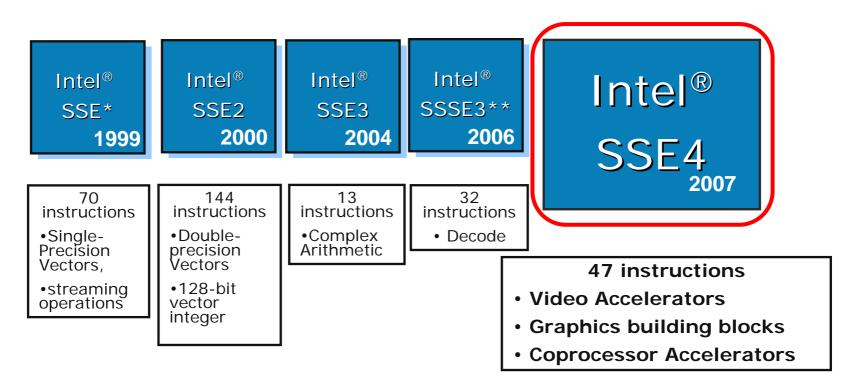

# **SSE4 History**

Enhanced Intel® Core<sup>™</sup> Microarchitecture (Penryn) supports 47 new instructions

This continues a trend set by SSE, SSE2, SSE3, and SSSE3 These extensions are a result of continuous customer feedback over the years!

\* Streaming SIMD Extension \*\* SSSE3: Supplemental Streaming SIMD Extension 3

> Next Generation Intel® Core™ Microarchitecture Ronny Ronen, EMEA Academic Forum '07 28

Education

### **New Intel® SSE4 Instructions**

### Components

Video Accelerators– 2X faster \*\*

14 instructions accelerate 4x4 SAD, Subpixel Filtering, and Search

### Graphics Building Blocks –

32 Common Graphics Primitives generalized for compiler autovectorization

Streaming Load -

up to 9X faster\*\*\*

access to device memory

Applications

- Video

- Authoring up to 1.4X faster \*

- Encoding

- Search

- Portable Video Devices

- Imaging

- e.g. Photo processing

- Graphics

- Gaming and Physics

- 3D content creation

- Off-chip Accelerators

### SSE4 – Continuing a History of ISA Innovation

\* Demonstrated in IDF 2007

\*\* Gains of 2-3X on block SAD (Sum of Absolute Difference). As demonstrated in the "Motion Estimation with Intel® SSE4" whitepaper

\*\*\* Compared to existing loads to WC memory, measured using 45nm Hi-k Intel dual core desktop processor 1333 FSB, and software published in the "Using SSE4 Streaming Load" Whitepaper

### Penryn SSE4 Instruction summary

| Instruction Category                            | Instructions                                                                                                                          | Benefits                                                                                  |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Packed DWORD Multiplies                         | PMULLD, PMULDQ                                                                                                                        | Improved automated compiler vectorization                                                 |

| Floating Point Dot Product                      | DPPS, DPPD                                                                                                                            | 3D content creation, gaming, support for<br>languages such as CG and HLSL                 |

| Multi-packed sum of<br>absolute diffs & min pos | MPSADBW, PHMINPOSUW                                                                                                                   | Video processing                                                                          |

| Packed Blending                                 | BLENDPS, BLENDPD, BLENDVPS,<br>BLENDVPD, PBLENDVB, PBLENDDW                                                                           | Compiler vectorization and applications such as video processing, multi-media and gaming  |

| Packed Integer Min and<br>Max                   | PMINSB, PMAXSB, PMINUW,<br>PMAXUW, PMINUD, PMAXUD,<br>PMINDS, PMAXSD                                                                  | Compiler vectorization and applications such as video processing, multi-media and gaming  |

| Floating Point Round                            | ROUNDPS, ROUNDSS, ROUNDPD,<br>ROUNDSD                                                                                                 | Image processing, graphics, video processing, 2D/3D applications, multimedia, and gaming. |

| Register<br>Insertion/Extraction                | INSERTPS, PINSRB, PINSRD,<br>PINSRQ, EXTRACTPS, PEXTRB,<br>PEXTRD, PEXTRW, PEXTRQ                                                     | Compiler vectorization and applications such as video processing, multi-media and gaming  |

| Packed Format Conversion                        | PMOVSXBW, PMOVZXBW,<br>PMOVSXBD, PMOVZXBD, PMOVSXBQ,<br>PMOVZXBQ, PMOVSXWD,<br>PMOVZXWD, PMOVSXWQ,<br>PMOVZXWQ, PMOVSXDQ,<br>PMOVZXDQ | Compiler vectorization and applications such as video processing, multi-media and gaming  |

| Streaming load                                  | ΜΟΥΝΤΟΩΑ                                                                                                                              | Video processing, imaging, data sharing apps with GPU                                     |

| Packed Test & Set                               | PTEST                                                                                                                                 | Compiler vectorization and applications such as video processing, multi-media and gaming  |

| Packed Compare for Equal                        | ΡϹϺΡΕQQ                                                                                                                               | Compiler vectorization and applications such as video processing, multi-media and gaming  |

| Pack DWORD to Unsigned<br>WORD                  | PACKUSDW                                                                                                                              | Compiler vectorization and applications such as video processing, multi-media and gaming  |

EMEA ACADEMIC

VI

FOR

- Penryn Family Design Goals

- Processor Architecture Basics

- Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture Refresh

- Intel 45nm High-K Silicon Technology

- Enhancing the Intel® Core<sup>™</sup> Microarchitecture

- Microarchitecture Enhancements

- New Intel<sup>®</sup> SSE4 Instructions

- Power Management Enhancements

- Summary

EMEA Academic Forum

Zth (

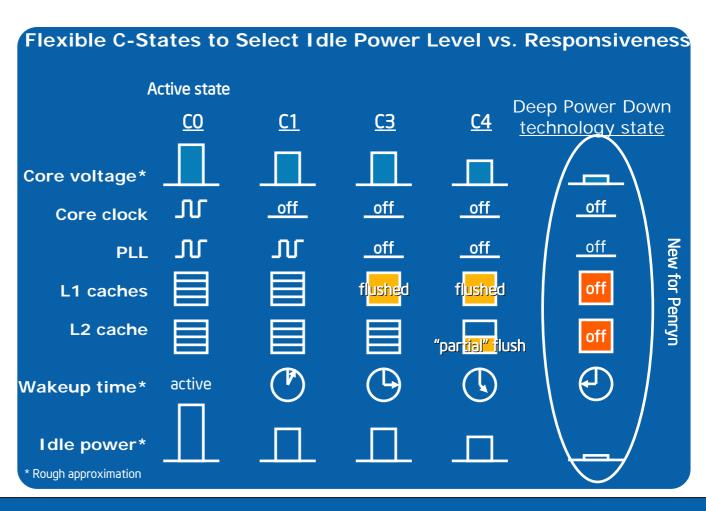

# **Power Management Enhancements**

- •Penryn builds on the power and thermal architecture capabilities in the Core<sup>™</sup> microarchitecture

- C-states: Processor idle condition low power states

- P-states: Performance states

- Thermal monitoring capability

- Digital thermometer access

- Intelligent voltage regulator management

- Fine grained power management applied across the microarchitecture

### •Key New Mobile Power/Thermal Features in Penryn:

- Deep Power Down technology:

A radically new and innovative idle power management state

- Enhanced dynamic acceleration technology:

A deterministic and platform power-friendly performance boost using power headroom of idled core

Соге

DTS

contro and

status

PSI / VID

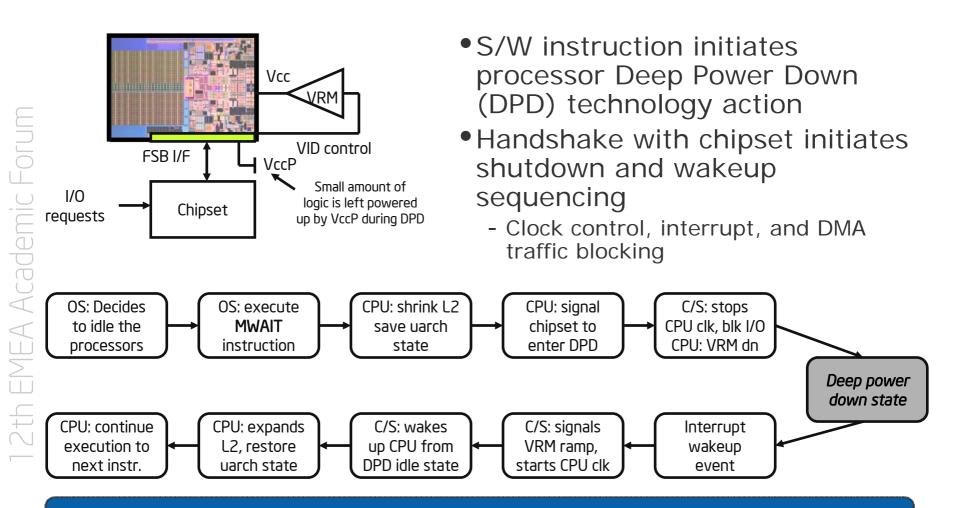

## **Deep Power Down Technology**

### Available on Mobile Penryn Family Processors

New Power Management State

Significantly reduces processor power consumed in idle mode

Further Extends Battery Life

Next Generation Intel® Core<sup>™</sup> Microarchitecture Ronny Ronen, EMEA Academic Forum '07 **33**

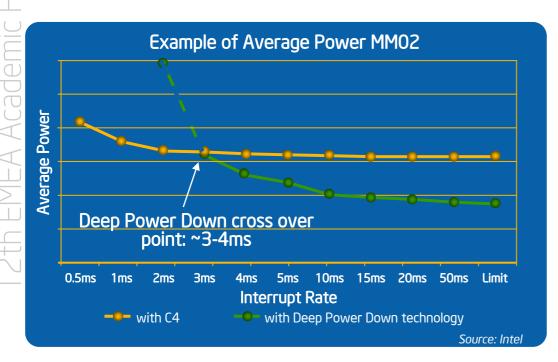

# Interrupt Rate Sensitivity of Average Power

Deep Power Down technology delivers greatest

benefit at reduced interrupt rates

Penryn supports intelligent heuristics to recognize when:

- Deep Power Down energy cost > idle period savings

- Demotes OS Deep power down requests to C4

Auto demote capability

MMO2 – BAPco\* Mobile Mark\* 2002

Next Generation Intel® Core<sup>™</sup> Microarchitecture Ronny Ronen, EMEA Academic Forum '07 **34**

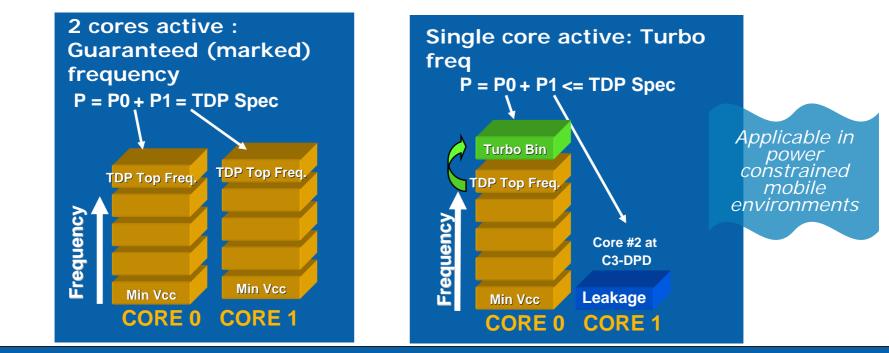

### **Enhanced Dynamic Acceleration Technology**

EMEA ACADEMIC

- **Concept:** In multi-core CPUs, use the power headroom of idle core to boost performance of the non-idle core

- How it works:

- Enhanced Dynamic Acceleration technology available when one core enters an idle power C-state

- Potential frequency boost on other core for single threaded apps

- Processor still stays within the specified thermal design power (TDP) for any thermally significant amount of time

Next Generation Intel® Core™ Microarchitecture Ronny Ronen, EMEA Academic Forum '07 35

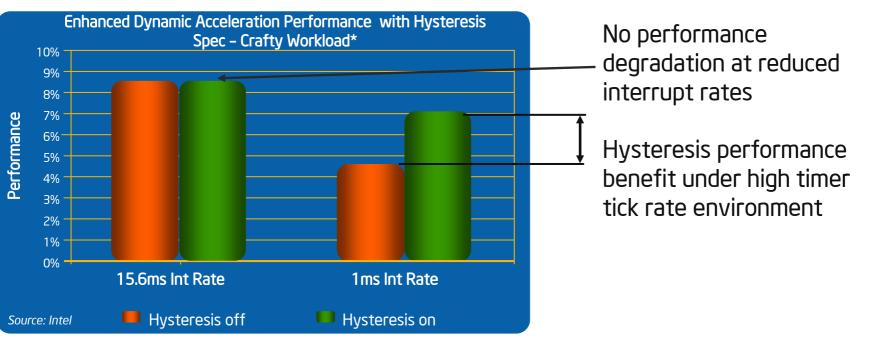

### Enhanced Dynamic Acceleration Technology Performance

- Delivers greatest benefit when 2nd core remains in idle mode

- Penryn supports a hysteresis mechanism to allow operation even when 2nd core is awoken for short intervals

\* Measured results from preliminary silicon. 'crafty' is a workload component of ISPECO0 See backup slide for details on system configuration used for this measurement

# Agenda

- Penryn Family Design Goals

- Processor Architecture Basics

- Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture Refresh

- Intel 45nm High-K Silicon Technology

- Enhancing the Intel® Core™ Microarchitecture

- Microarchitecture Enhancements

- New Intel® SSE4 Instructions

- Power Management Enhancements

## Summary

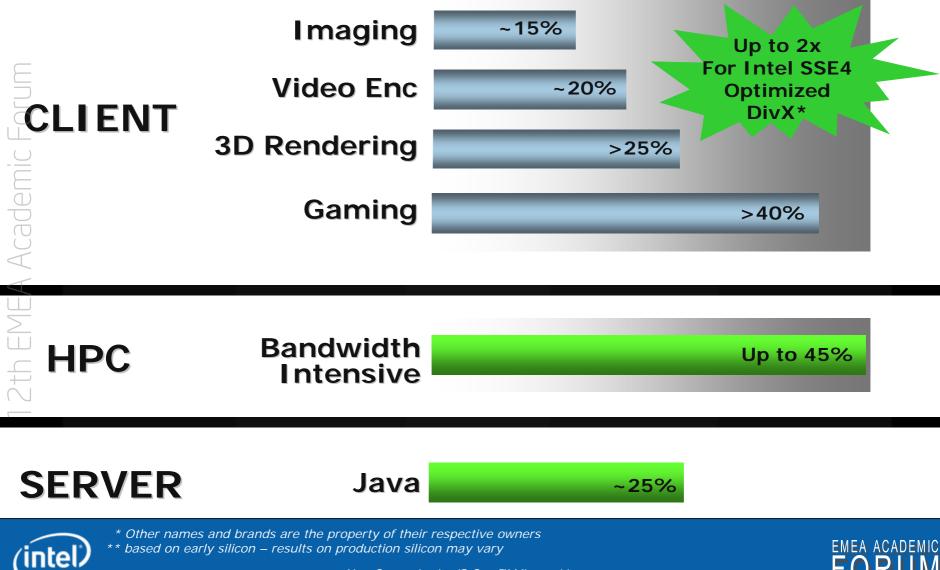

## Early Penryn Family Performance Indicators<sup>\*</sup>\* 45nm Hi-k vs 65nm Intel® Core™ 2 and Xeon™ Processors

Next Generation Intel® Core<sup>™</sup> Microarchitecture Ronny Ronen, EMEA Academic Forum '07 **38**

Education

# 45nm Next Generation Intel® Core™ and Xeon Family processors (Penryn)

- Intel's leading 45 nm High-k silicon process coupled with enhanced Intel Core Microarchitecture

- Greater performance at given frequency and higher frequencies

- Greater energy efficiency

- Optimized configurations for server, workstation, desktop, and mobile

# On Track for 2H'07 Production

# Additional sources of information on this topic:

### • More web based info:

- Intel® Core<sup>™</sup> Microarchitecture: <u>http://www.intel.com/technology/architecture/coremicro/index.htm</u>

- Intel® SSE4 Instructions: http://download.intel.com/technology/architecture/new-instructions-paper.pdf

- 45 nm Process Technology & High-k gate dielectrics http://www.intel.com/technology/silicon/45nm\_technology.htm http://en.wikipedia.org/wiki/High-k

- Penryn

http://www.intel.com/technology/magazine/45nm/coremicroarchitecture-0507.htm

1 2th EMEA Academic Forum

Next Generation Intel® Core™ Microarchitecture Ronny Ronen, EMEA Academic Forum '07 42

# Legal Disclaimer

- INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

- Intel may make changes to specifications and product descriptions at any time, without notice.

- Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

- The Intel® Core<sup>™</sup> Microarchitecture, Intel® Pentium, Intel® Pentium II, Intel® Pentium III, Intel® Pentium 4, Intel® Pentium Pro, Intel® Pentium D, Intel® Pentium M, Itanium®, Xeon® may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

- Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

- This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

- All dates specified are target dates, are provided for planning purposes only and are subject to change.

- All products, dates, and figures specified are preliminary based on current expectations, provided for planning purposes only, and are subject to change without notice.

- Intel and the Intel logo is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

- \*Other names and brands are the property of their respective owners.

- Copyright © 2007, Intel Corporation

# Terminology

- Architecture/microarchitecture

- Intel® Core™ Microarchitecture → "Merom"

- Enhanced Intel® Core™ Microarchitecture → Penryn

- Products

- Intel® Core™ 2 Dou processor (65nm) → Merom/Conroe/Woodcrest

- <no name> (45nm) → Penryn

- Penryn is

- Next generation based on "Merom" arch/microarch

- It will have both dual core and quad core versions

- The Dual core shares L2 cache

# System configuration data used for Enhanced Dynamic Acceleration Technology measurements

- Mobile Penryn pre-production processor

- Mobile pre-production chipset

- Windows\* XP\* SP2

- Max Battery CPU setting

# **Appendix A: Performance** Configurations

Client

- Pre-production 45nm Hi-k Intel Core 2 quad core processor (12MB L2, 3.33GHz, 1333MHz FSB) compared to Intel® Core<sup>™</sup> 2 Extreme

Pre-production 45nm Hi-k Intel Core 2 quad core processes L2, 3.33GHz, 1333MHz FSB) compared to Intel® Corespondencessor QX6800 (8MB L2, 2.93GHz, 1066MHz FSB)

Applications: Half-Life\* 2 build 2707, Cinbench\* R9.5, MainConcept\* H.264 Encoder v2.1, Photoshop\* CS2

Server

Based on Intel internal measurement/projection on a S Java benchmark. March 2007. Pre-production 45nm Hi Xeon™ processor is compared to current generation Qu Intel® Xeon® processor X5355 on the Bensley Server Based on Intel internal measurement/projection on a Server Side Java benchmark. March 2007. Pre-production 45nm Hi-k Intel® Xeon<sup>™</sup> processor is compared to current generation Quad-Core Intel® Xeon® processor X5355 on the Bensley Server platform

#### HPC

Based on Intel internal measurement on bandwidth intensive floating point benchmarks. March 2007. New generation Stoakley platform with Pre-production 45nm Hi-k Intel<sup>®</sup> Xeon<sup>™</sup> processor with 1600 MHz FSB is compared to current generation Quad-Core Intel® Xeon® processor X5355 based Bensley platform

# **Client Performance Results**

- Source: Intel. Configuration: Preproduction 45nm Hi-k Intel® quad core processor ( 3.33 GHz/1333/12MB quad-core ) and Intel® Core™ 2 Extreme processor QX6800 ( 2.93 GHz/1066/8MB ) on modified Intel D975XBX2 Rev. 505; with Dual channel (2x1GB) DDRII 800 5-5-5-15 ASUS EN8800GTX GeForce GTX graphics, 300GB NCQ SATA. Windows\* Vista\* 32 bit build 6000.

- Performance tests and ratings are measured using specific systems and/or components and reflect approximate performance of Intel products as measured by those tests. Any difference in system hardware, software, or configuration may affect actual performance. Buyers should consult other sources of information to evaluate system or component performance they are considering purchasing. For information on performance tests and performance of Intel products, visit http://www.intel.com/performance/resources/limits.htm

|                                                                                 | Intel® Core™2 Extreme processor<br>QX6800<br>(8MB L2, 2.93 GHz, 1066 FSB) | 45nm Hi-k Intel® quad core<br>processor<br>(12MB L2, 3.33 GHz, 1333 FSB) | Percent<br>Faster |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------|

| DivX* 6.6 Alpha with VirtualDub<br>1.7.1 (time in seconds – lower is<br>better) | 38                                                                        | 18                                                                       | 211%              |

| Half-Life* 2 build 2707<br>(frames per second - higher is<br>better)            | 151                                                                       | 213                                                                      | 41%               |

| Cinebench* R9.5<br>(score - higher is better)<br>MainConcept* H.264 Encoder     | 1549                                                                      | 1935                                                                     | 25%               |

| v2.1<br>(time in seconds - lower is                                             | 88.0                                                                      | 73.4                                                                     | 20%               |

| better)<br>Photoshop* CS2<br>(time in seconds - lower is<br>better)             | 105                                                                       | 91.0                                                                     | 15%               |

EMEA ACADEMIC

## Deep Power Down Technology in Action

Autonomous Power Down Capability for Longer Battery Life

B