# intel®

# Intel<sup>®</sup> 80333 I/O Processor

Design Guide

March 2005

Order Number: 305434-001US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling1-800-548-4725, or by visiting Intel's website at http://www.intel.com.

AlertVIEW, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, LANDesk, LanRover, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, Trillium, VoiceBrick, Vtune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

The ARM\* and ARM Powered logo marks (the ARM marks) are trademarks of ARM, Ltd., and Intel uses these marks under license from ARM, Ltd.î

\*Other names and brands may be claimed as the property of others.

Copyright© Intel Corporation 2002

# int<sub>el</sub>。 Contents

| <ul> <li>1.1 About This Document</li></ul>                                                                                        | 12<br>14<br>15<br>21<br>23<br>23<br>30<br>30<br>31<br>32<br>32 |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| <ul> <li>2 Package Information</li> <li>2.1 Power Plane Layout</li> </ul>                                                         | 17<br>21<br>23<br>30<br>30<br>31<br>32<br>32                   |

| 2.1 Power Plane Layout                                                                                                            | 21<br>23<br>30<br>30<br>31<br>32<br>32                         |

| <ul> <li>2.1 Power Plane Layout</li> <li>2.2 Intel<sup>®</sup> 80333 I/O Processor Applications</li> </ul>                        | 23<br>25<br>30<br>30<br>31<br>32<br>32                         |

| 2.2 Intel <sup>®</sup> 80333 I/O Processor Applications                                                                           | 25<br>30<br>30<br>31<br>32<br>32                               |

|                                                                                                                                   | 30<br>30<br>31<br>32<br>32                                     |

| 3 Terminations                                                                                                                    | 30<br>31<br>32<br>32                                           |

| 3.1 Analog Filters                                                                                                                | 31<br>32<br>32                                                 |

| 3.2 PE_V <sub>CCBG</sub> Pin Requirements                                                                                         | 32<br>32                                                       |

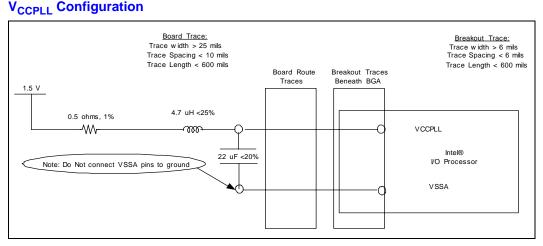

| 3.2.1 V <sub>CCPLL</sub> Pin Requirements                                                                                         | 32                                                             |

| <ul> <li>3.3 PCI-Express Resistor Compensation</li> <li>3.4 DDR Resistor Compensation</li> </ul>                                  |                                                                |

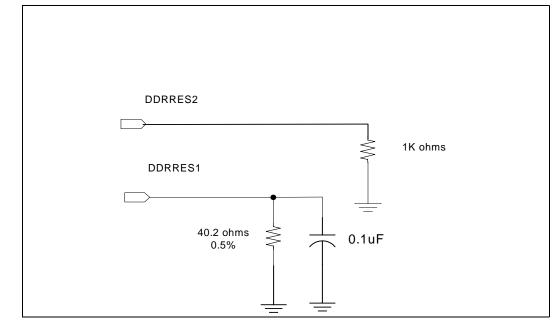

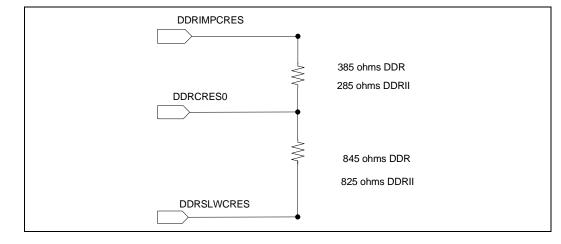

| 3.4 DDR Resistor Compensation                                                                                                     |                                                                |

|                                                                                                                                   |                                                                |

| 4 Routing Guidelines                                                                                                              |                                                                |

| 4.1 General Routing Guidelines                                                                                                    |                                                                |

| <ul><li>4.2 Crosstalk</li><li>4.3 EMI Considerations</li></ul>                                                                    |                                                                |

| 4.3 ENICOnsiderations                                                                                                             |                                                                |

| 4.4.1 Decoupling                                                                                                                  |                                                                |

| 4.5 Trace Impedance                                                                                                               |                                                                |

| 5 Board Layout Guidelines                                                                                                         | 41                                                             |

| 5.1 Motherboard Stack Up Information                                                                                              | 41                                                             |

| 5.2 Adapter Card Stackup                                                                                                          |                                                                |

| 6 PCI-X Layout Guidelines                                                                                                         | 45                                                             |

| 6.1 Interrupt Routing and IDSEL Lines                                                                                             | 45                                                             |

| 6.1.1 PCI Arbitration                                                                                                             |                                                                |

| 6.1.2 PCI Resistor Compensation                                                                                                   |                                                                |

| 6.1.3 PCI Hot Plug                                                                                                                |                                                                |

| 6.2 PCI General Layout Guidelines                                                                                                 |                                                                |

| <ul> <li>6.3 PCI-X Topology Layout Guidelines</li> <li>6.4 Intel<sup>®</sup> 80333 I/O Processor PCI/X Layout Analysis</li> </ul> |                                                                |

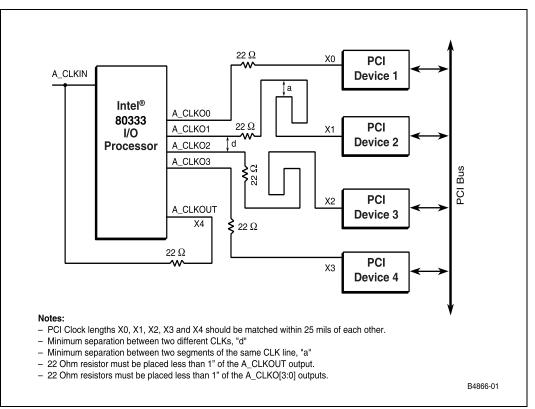

| 6.4.1 PCI Clock Layout Guidelines                                                                                                 |                                                                |

| 6.4.2 Single-Slot at 133 MHz                                                                                                      |                                                                |

| 6.4.3 Embedded PCI-X 133 MHz                                                                                                      |                                                                |

| 6.4.4 Embedded PCI-X 133 MHz Alternate Topology                                                                                   |                                                                |

| 6.4.5 Combination of PCI-X 133 MHz Slot and Embedded Topology                                                                     |                                                                |

| 6.4.6 Combination PCI-X 133 MHz Slot and Embedded Topology 2                                                                      |                                                                |

| 6.4.7 PCI-X 133 MHz Hot Plug Topology<br>6.4.8 PCI-X 100 MHz Slot Topology                                                        |                                                                |

| 6.4.9 PCI-X 100 MHz Embedded Topology                                                                                             |                                                                |

| 6.4.10 PCI-X 100 MHz Slot and Embedded Topology                                                                                   |                                                                |

# intط®

|   |       | 6.4.11   | PCI-X 100   | MHz Slot and Embedded Topology 2                                                           | 63  |

|---|-------|----------|-------------|--------------------------------------------------------------------------------------------|-----|

|   |       | 6.4.12   | PCI-X 100   | MHz Hot Plug Topology                                                                      | 64  |

|   |       | 6.4.13   | PCI-X 66 M  | MHz Slot Topology                                                                          | 65  |

|   |       | 6.4.14   | PCI-X 66 M  | MHz Embedded Topology                                                                      | 66  |

|   |       | 6.4.15   | PCI-X 66 M  | MHz Mixed Mode Topology                                                                    | 67  |

|   |       |          |             | Hz Slot Topology                                                                           |     |

|   |       | 6.4.17   | PCI 66 MF   | Iz Embedded Topology                                                                       | 69  |

|   |       | 6.4.18   | PCI 66 MF   | Iz Mixed Mode Topology                                                                     | 70  |

|   |       |          |             | Iz Slot Topology                                                                           |     |

|   |       | 6.4.20   | PCI 33 MF   | Iz Embedded Mode Topology                                                                  | 72  |

|   |       | 6.4.21   | PCI 33 MF   | Iz Mixed Topology                                                                          | 73  |

| 7 | PCI E | xpress l | _ayout      |                                                                                            | 75  |

|   | 7.1   | Genera   | I Recomme   | endations                                                                                  | 75  |

|   |       | 7.1.1    | Simulation  | Conditions                                                                                 | 75  |

|   | 7.2   | PCI Exp  | press Layou | ut Guidelines for an 80333 on a Motherboard-Adapter Card Topology                          | .78 |

|   | 7.3   | Clock R  | outing Guid | delines                                                                                    | 81  |

| 8 | Memo  | ory Cont | roller      |                                                                                            | 83  |

|   | 8.1   | DDR Bi   | as Voltages | S                                                                                          | 83  |

|   | 8.2   |          |             | rocessor DDR Overview                                                                      |     |

|   | 8.3   |          |             | tegrity Simulation Conditions                                                              |     |

|   |       | 8.3.1    |             | Stackup Example                                                                            |     |

|   | 8.4   | DDR La   |             | elines                                                                                     |     |

|   |       | 8.4.1    | Source Sy   | nchronous Signal Group                                                                     | 88  |

|   |       |          |             | Routing Requirements                                                                       |     |

|   |       | 8.4.2    | Clock Sign  | nal Groups                                                                                 | 99  |

|   |       |          | 8.4.2.1 (   | Control Signals Termination                                                                | 103 |

|   |       | 8.4.3    | Embedded    | d Configuration                                                                            | 107 |

|   |       |          |             | DDR 333 Source Synchronous Routine Guidelines                                              |     |

|   |       |          | 8.4.3.2     | DDR 333 Embedded Clock Routing Recommendations                                             | 110 |

|   |       |          |             | DDR 333 Embedded Address/Command/Control Routing Guidelines                                |     |

|   | 8.5   |          | •           | delines                                                                                    |     |

|   |       | 8.5.1    |             | Conditions                                                                                 |     |

|   |       | 8.5.2    |             | ) Trace Width/Impedance Requirements                                                       |     |

|   |       | 8.5.3    | DIMM Lay    | out Design                                                                                 | 122 |

|   |       |          | 8.5.3.1     | DDR II 400 DIMM Source Synchronous Routing                                                 | 122 |

|   |       |          |             | DDRII 400 Clock Routing Guidelines<br>DDRII 400 Address/Command/Control Routing Guidelines |     |

|   |       | 8.5.4    |             | d Configuration                                                                            |     |

|   |       | 0.3.4    |             | DDRII 400 Embedded Source Synchronous Routine Guidelines                                   |     |

|   |       |          |             | DDRII 400 Embedded Source Synchronous Routine Guidelines                                   |     |

|   |       |          | 8.5.4.3     | DDRII 400 Embedded Address/Command/Control Routing Guidelines                              | 3   |

|   | 8.6   | ים סחח   |             | 134<br>nation                                                                              | 122 |

|   | 8.7   |          | •           | Voltage                                                                                    |     |

|   | 8.8   |          |             | e                                                                                          |     |

| _ |       | -        |             |                                                                                            |     |

| 9 | •     |          |             |                                                                                            |     |

|   | 9.1   |          |             | nals                                                                                       |     |

|   |       | 9.1.1    |             | Pata Signal Definitions                                                                    |     |

|   |       | 9.1.2    | Control/Sta | atus Signal Definitions                                                                    | 141 |

#### Intel® 80333 I/O Processor Design Guide Contents

|    |        | 9.1.3 Bus Width                                                      | 142 |

|----|--------|----------------------------------------------------------------------|-----|

|    |        | 9.1.4 Flash Memory Support                                           | 143 |

|    |        | 9.1.5 Layout Guidelines for the Peripheral Bus                       | 144 |

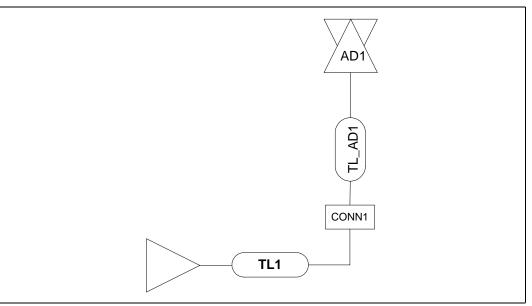

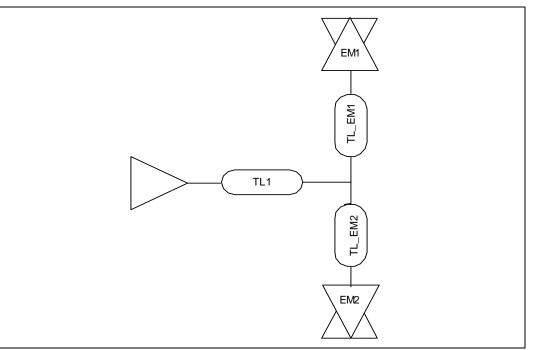

|    | 9.2    | Topology Layout Guidelines                                           |     |

| 10 | Powe   | er Delivery                                                          | 149 |

|    | 10.1   | Power Sequencing                                                     |     |

|    | 10.2   | Power Failure                                                        |     |

|    |        | 10.2.1 Theory of Operation                                           | 150 |

|    |        | 10.2.2 Power Failure Sequence                                        |     |

|    | 10.3   | Power Failure Circuitry                                              | 151 |

|    |        | 10.3.1 Power Delay                                                   | 151 |

|    | 10.4   | Battery Backup                                                       | 152 |

|    |        | 10.4.1 Non-Battery Backup Circuits                                   |     |

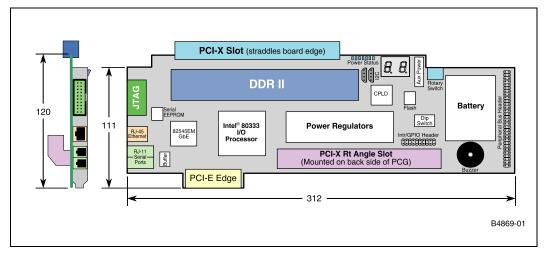

| 11 | Intel® | 80333 I/O Processor Evaluation Board                                 | 155 |

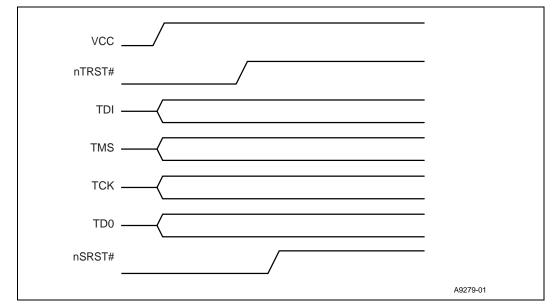

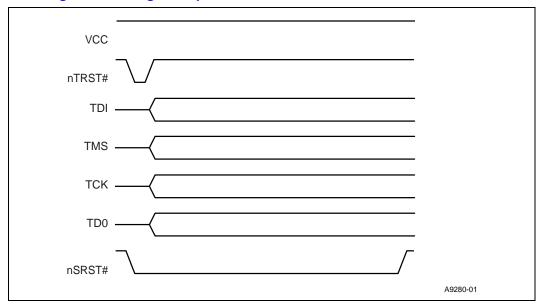

| 12 | JTAG   | G Circuitry for Debug                                                | 159 |

|    | 12.1   | Requirements                                                         |     |

|    | 12.2   | JTAG Signals / Header                                                |     |

|    | 12.3   | System Requirements                                                  | 161 |

|    | 12.4   | JTAG Hardware Requirements                                           |     |

|    |        | 12.4.1 Macraigor Raven and WindRiver Systems visionPROBE / visionICE |     |

|    |        | 12.4.2 ARM Multi-ICE                                                 |     |

| 13 | Debu   | g Connectors and Logic Analyzer Connectivity                         |     |

|    | 13.1   | Probing PCI-X Signals                                                |     |

|    | 13.2   | PCI-Express Debugging                                                |     |

|    |        | 13.2.1 Physical Layer Debugging                                      |     |

|    |        | 13.2.2 Transaction Layer Testing                                     |     |

| 14 | Refer  | rences                                                               |     |

|    | 14.1   | Related Documents                                                    |     |

|    | 14.2   | Electronic Information                                               |     |

|    | -      |                                                                      |     |

### **Figures**

| 1        | Intel <sup>®</sup> 80333 I/O Processor Functional Block Diagram               | .16  |

|----------|-------------------------------------------------------------------------------|------|

| 2        | Intel <sup>®</sup> 80333 I/O Processor 829-Ball FCBGA Package Diagram         | .18  |

| 3        | Intel <sup>®</sup> 80333 I/O Processor Ballout (Top View)                     |      |

| 4        | Intel <sup>®</sup> 80333 I/O Processor Ballout (Bottom View)                  | 20   |

| 5        | Intel <sup>®</sup> 80333 I/O Processor Power Plane Layout                     |      |

| 6        | Inductively Isolated Split Plane                                              |      |

| 7        | Intel <sup>®</sup> 80333 I/O Processor MCH Motherboard Block Diagram          |      |

| 8        | Intel <sup>®</sup> 80333 I/O Processor PCI-Express Adapter Card Block Diagram |      |

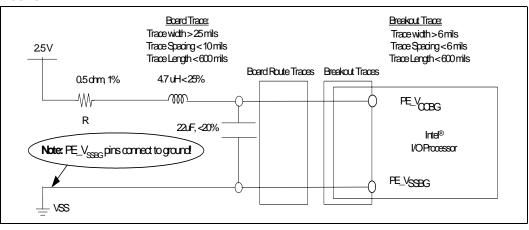

| 9        | V <sub>CCBG</sub> Filter Circuit                                              |      |

| 9<br>10  | V <sub>CCBG</sub> i mer Circuit<br>V <sub>CCPLI</sub> Configuration           |      |

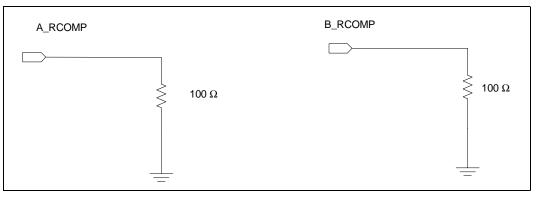

| 11       | PCI-Express RCOMP                                                             |      |

| 12       | Intel <sup>®</sup> 80333 I/O Processor DDRRES Resistor Compensation Circuitry |      |

|          |                                                                               |      |

| 13       | DDR Driver Compensation Circuitry                                             |      |

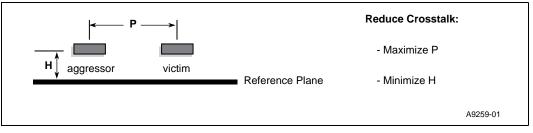

| 14       | Crosstalk Effects on Trace Distance and Height                                |      |

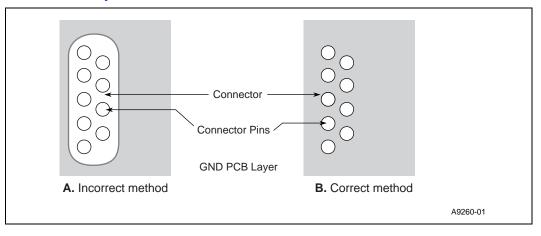

| 15       | PCB Ground Layout Around Connectors                                           |      |

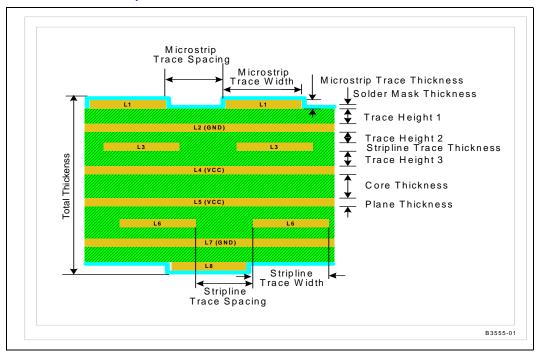

| 16       | Motherboard Stackup Recommendations                                           |      |

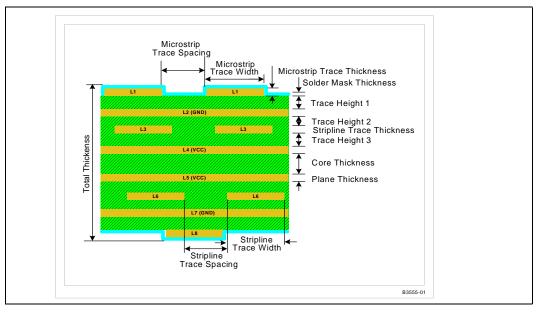

| 17       | Adapter Card Stackup                                                          |      |

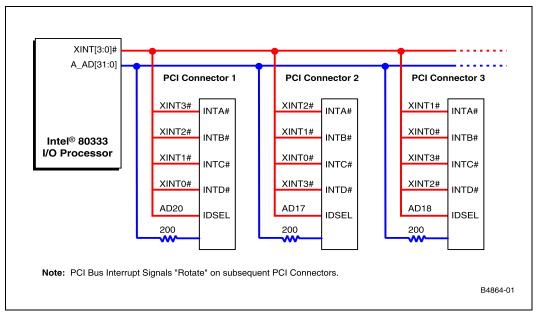

| 18       | Interrupt and IDSEL Mapping                                                   |      |

| 19       | PCI RCOMP                                                                     |      |

| 20       | Intel <sup>®</sup> 80333 I/O Processor Parallel 1 Slot Hot-Plug No Glue Mode  |      |

| 21       | PCI Clock Distribution and Matching Requirements                              |      |

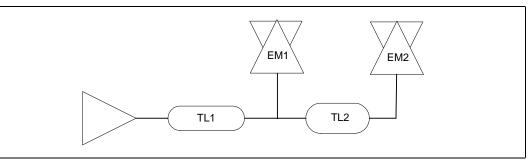

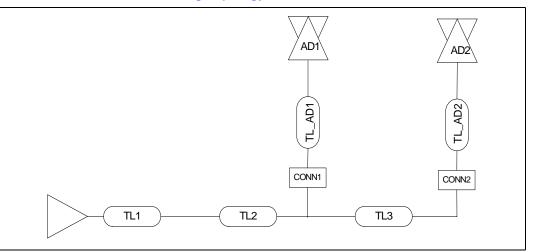

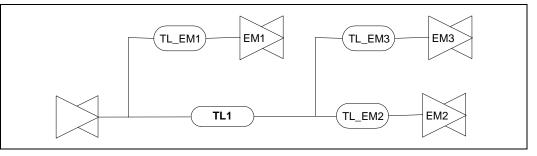

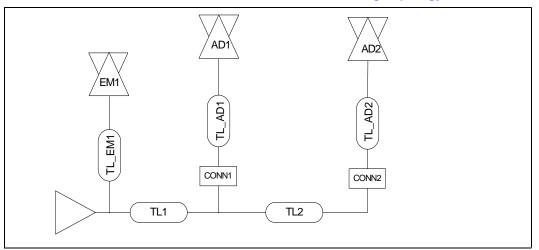

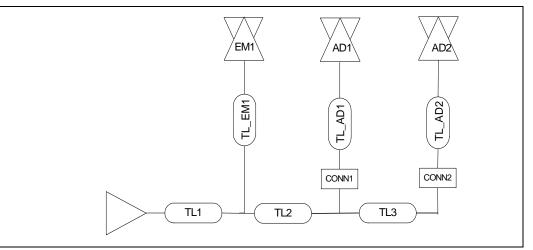

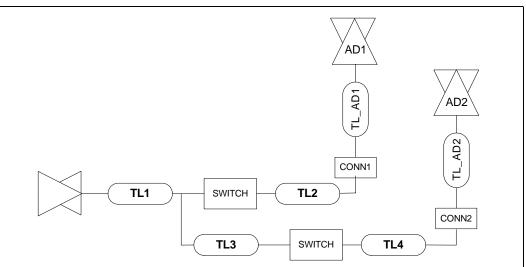

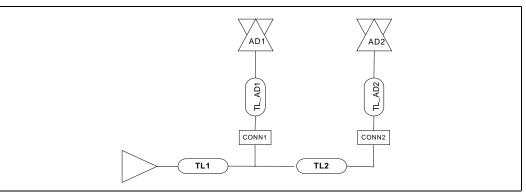

| 22       | Single-Slot Point-to-Point Topology                                           |      |

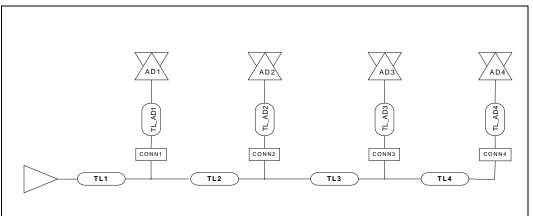

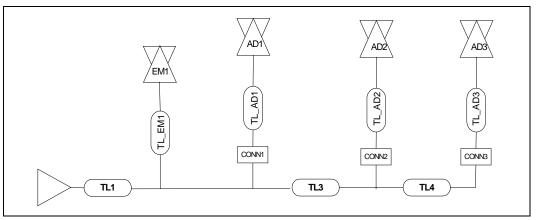

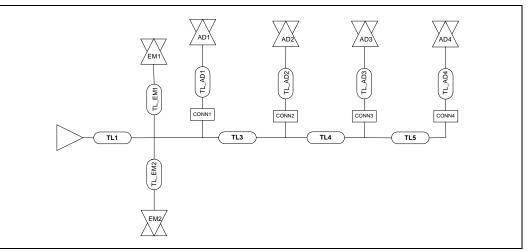

| 23       | Embedded PCI-X 133 MHz Topology                                               |      |

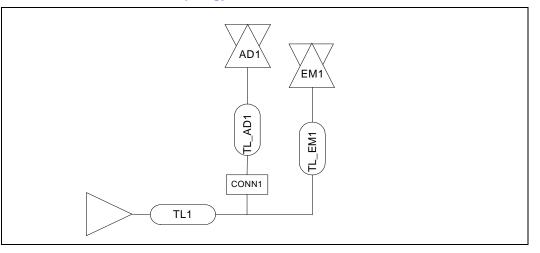

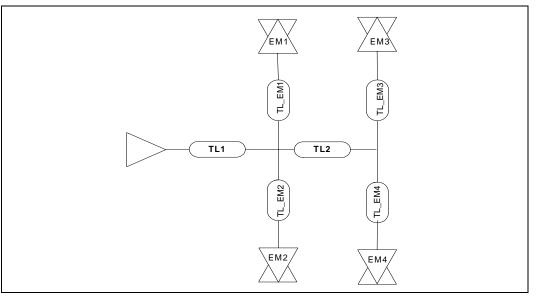

| 24       | Embedded PCI-X 133 MHz Alternate Topology                                     | . 56 |

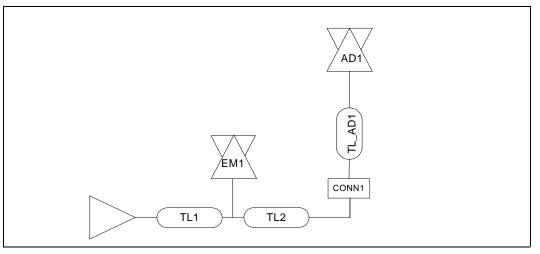

| 25       | Embedded PCI-X 133 MHz Topology                                               | . 57 |

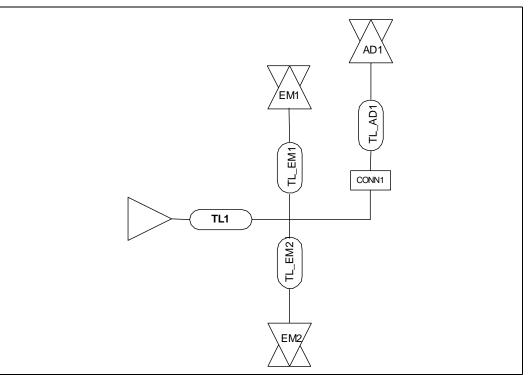

| 26       | Embedded PCI-X 133 MHz Topology                                               | . 58 |

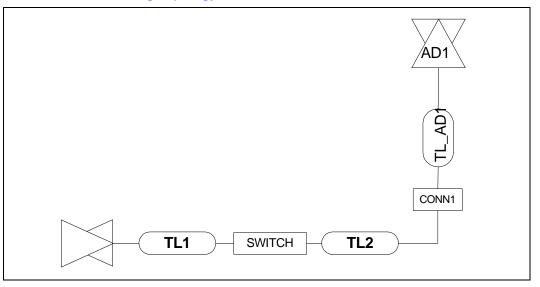

| 27       | PCI-X 133 MHz Hot Plug Topology                                               | . 59 |

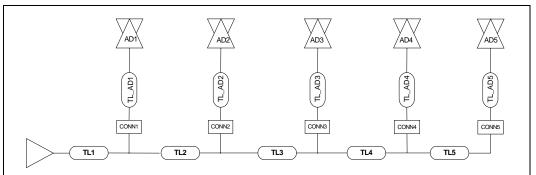

| 28       | Slot PCI-X 100 MHz Slot Routing Topology                                      | .60  |

| 29       | Embedded PCI-X 100 MHz Routing Topology                                       |      |

| 30       | Combination of Slot and Embedded PCI-X 100 MHz Routing Topology               |      |

| 31       | Combination of Slots and Embedded PCI-X 100 MHz Routing Topology              | .63  |

| 32       | PCI-X 100 MHz Hot Plug Topology                                               |      |

| 33       | PCI-X 66 MHz Slot Routing Topology                                            |      |

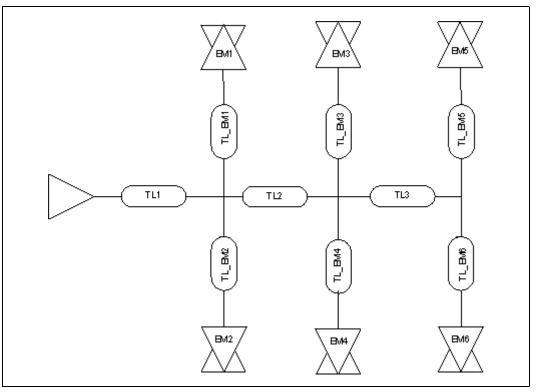

| 34       | PCI-X 66 MHz Embedded Routing Topology                                        |      |

| 35       | PCI-X 66 MHz Mixed Mode Routing Topology                                      |      |

| 36       | PCI 66 MHz Topology                                                           |      |

| 37       | PCI 66 MHz Embedded Topology                                                  |      |

| 38       | PCI 66 MHz Mixed Topology                                                     | 70   |

| 39       | PCI 33 MHz Slot Routing Topology                                              | 71   |

| 40       | PCI 33 MHz Embedded Mode Routing Topology                                     |      |

| 41       | PCI 33 MHz Mixed Mode Routing Topology                                        |      |

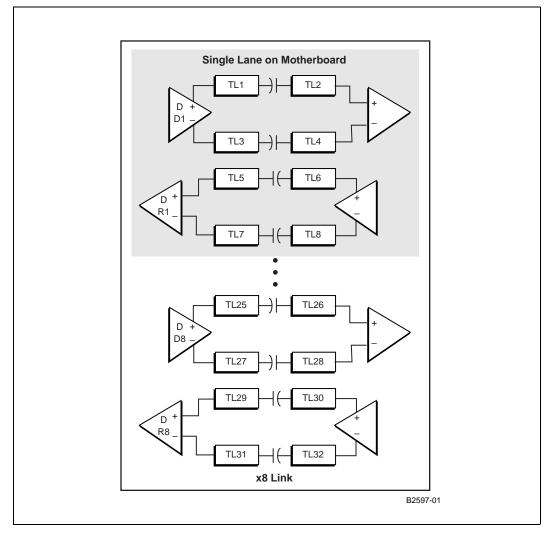

| 42       | Motherboard Topology                                                          |      |

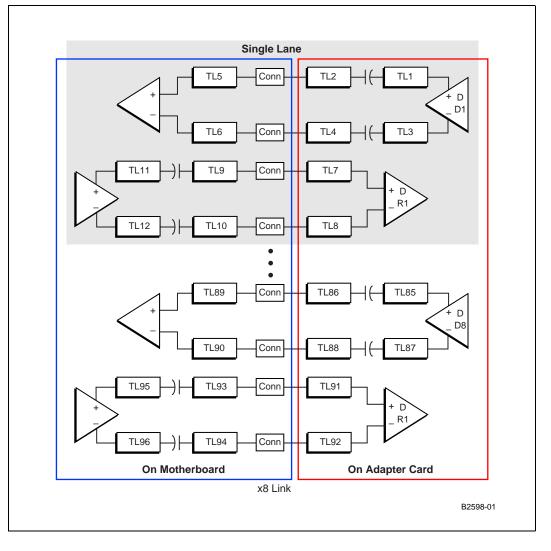

| 43       | Motherboard-Adapter Card Topology                                             |      |

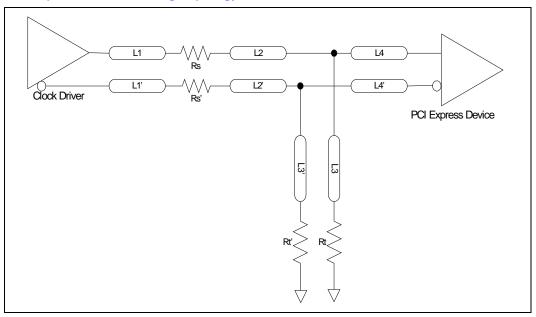

| 44       | PCI Express Clock Routing Topology                                            |      |

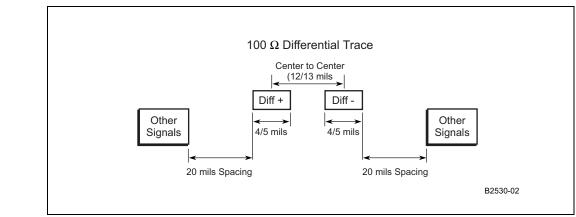

| 44       | 100 ohm Differential Trace                                                    |      |

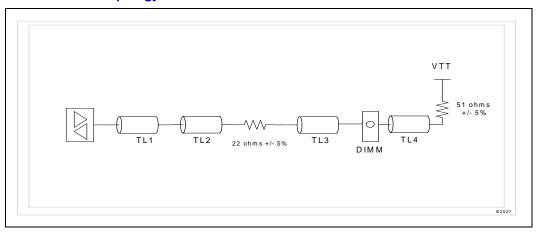

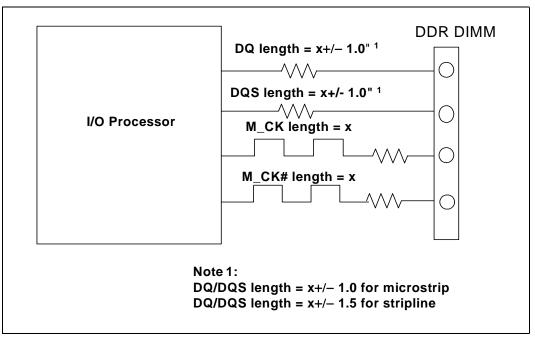

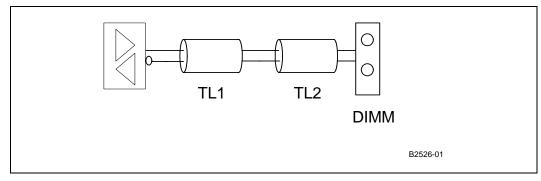

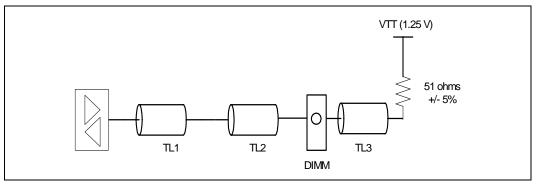

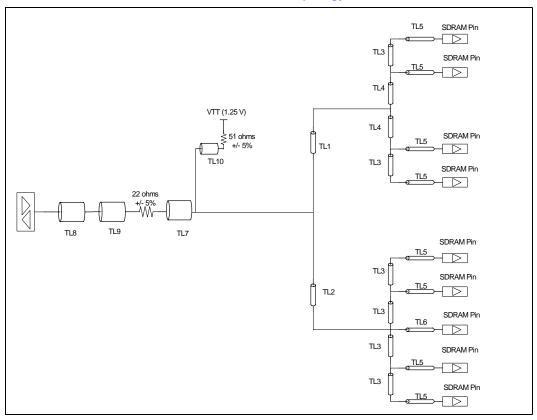

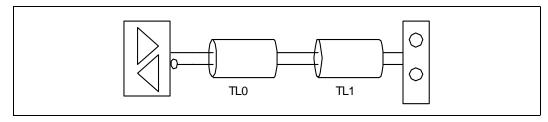

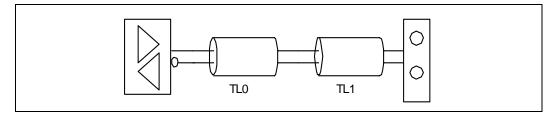

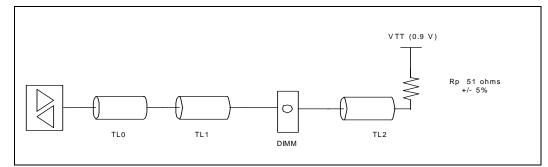

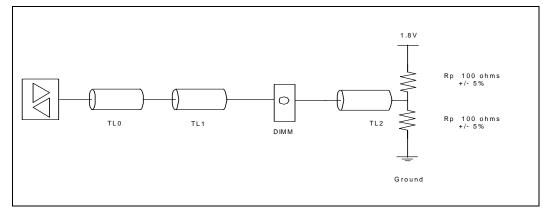

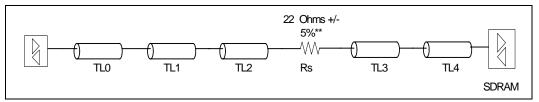

| 45<br>46 | DIMM DQ/DQS Topology                                                          |      |

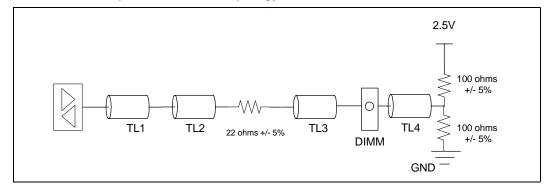

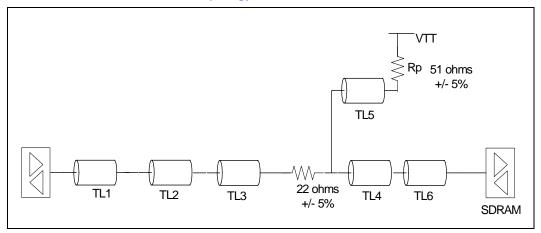

| 40<br>47 | DIMM DQ/DQS Split Termination Topology                                        |      |

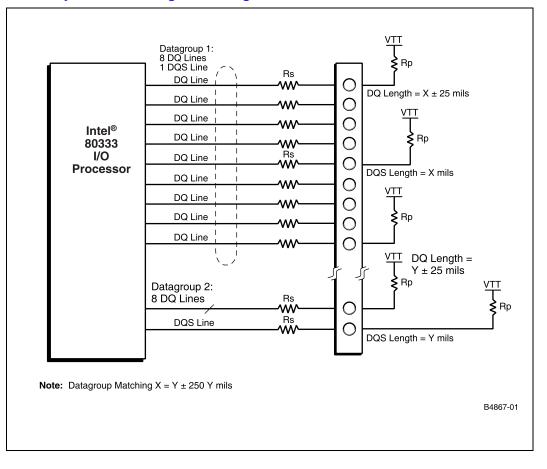

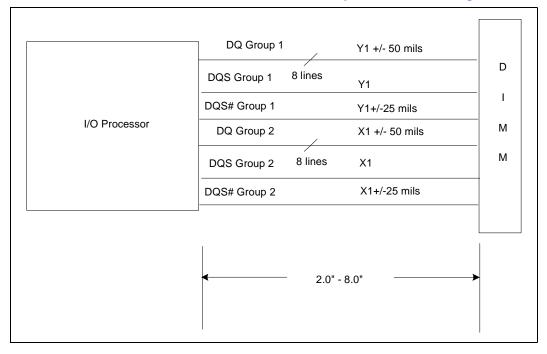

| 47<br>48 | Source Synchronous Length Matching                                            |      |

| 40       | Ouros Oynonionous Lengui Matoning                                             | . 31 |

| 49 | Data Group Length Matching                                                       |     |

|----|----------------------------------------------------------------------------------|-----|

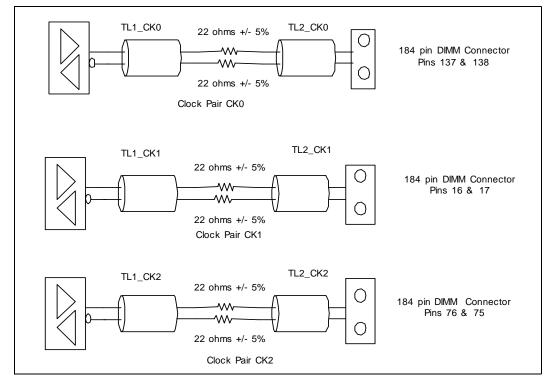

| 50 | DDR 333 Registered DIMM Clock Topology                                           | 101 |

| 51 | DDR 333 Unbuffered DIMM Clock Topology                                           |     |

| 52 | Trace Length Requirements for Source Clocked Routing                             | 103 |

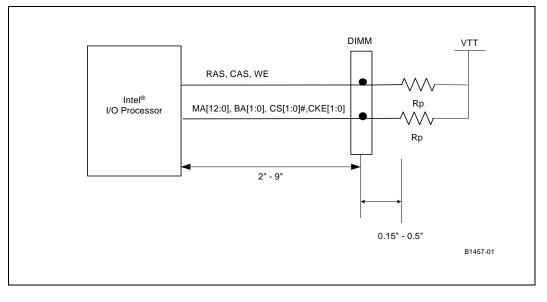

| 53 | DDR 333 DIMM Unbuffered/Registered Address/CMD Topology Lengths                  | 105 |

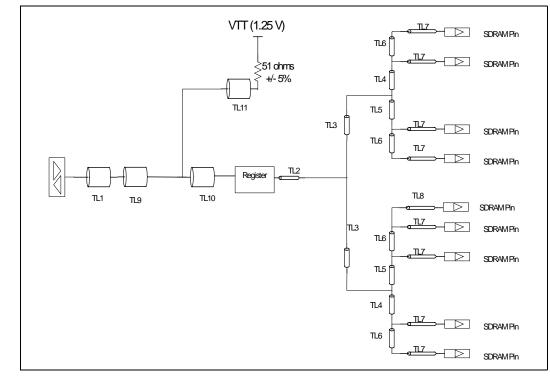

| 54 | Embedded DDR 333 DQ/DQS Topology                                                 | 109 |

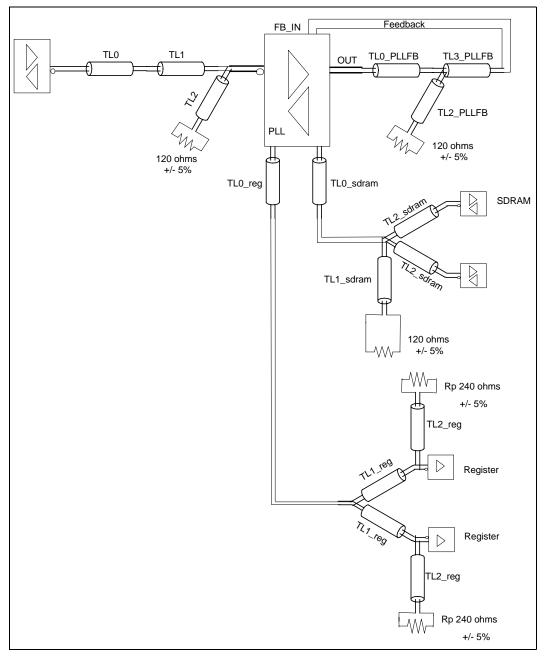

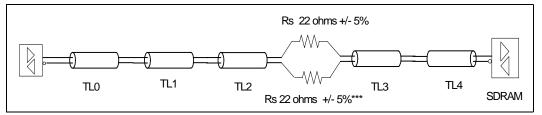

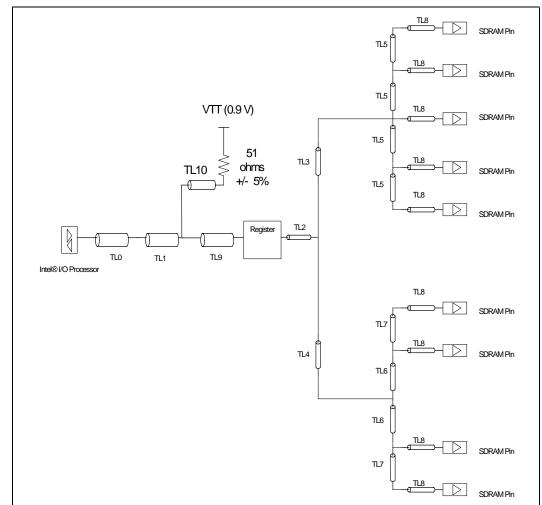

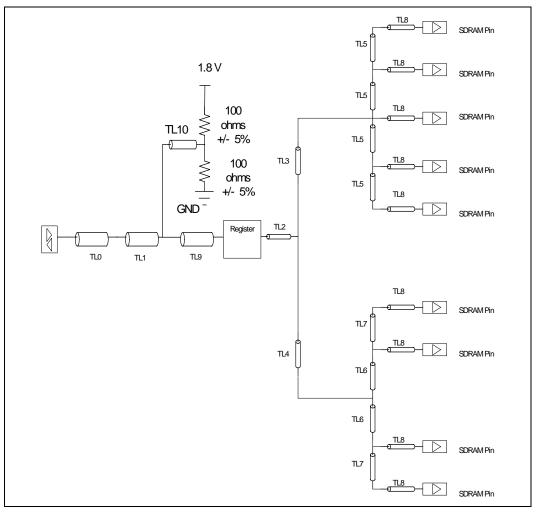

| 55 | Embedded DDR 333 Buffered Clock Topology                                         | 110 |

| 56 | Embedded DDR 333 Unbuffered Clock Topology                                       | 113 |

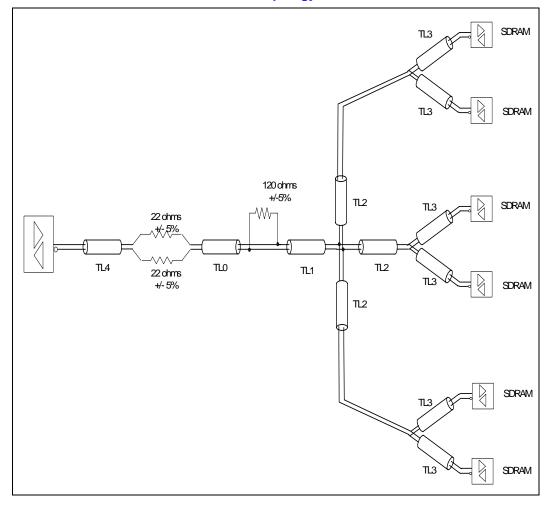

| 57 | Embedded DDR 333 Unbuffered ADDR/CMD Topology                                    |     |

| 58 | Embedded DDR 333 Registered ADDR/CMD Topology                                    |     |

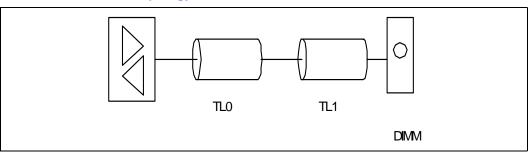

| 59 | Intel <sup>®</sup> 80333 I/O Processor DDRII 400 DIMM Source Synchronous Routing |     |

| 60 | DDR II 400 DIMM DQ Topology                                                      |     |

| 61 | DDR II 400 DIMM DQS Topology                                                     |     |

| 62 | DDR II 400 DIMM Clock Topology                                                   |     |

| 63 | DDR II 400 DIMM Address/CMD Topology                                             |     |

| 64 | DDR II 400 DIMM Address/CMD Split Termination Topology                           |     |

| 65 | DDR II 400 Embedded DQ Topology                                                  |     |

| 66 | DDR II 400 Embedded DQS Topology                                                 |     |

| 67 | DDR II 400 Embedded Clock Topology                                               |     |

| 68 | DDR II 400 Embedded Address/Control Topology                                     |     |

| 69 | DDR II 400 Embedded Address/Control Topology With Split Termination              | 137 |

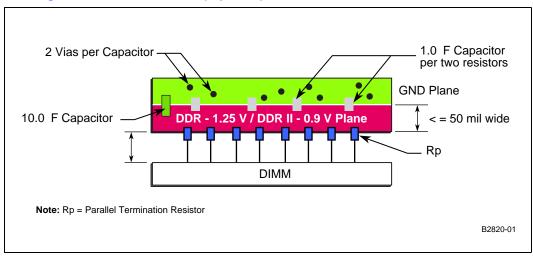

| 70 | Routing Termination Resistors (top view)                                         |     |

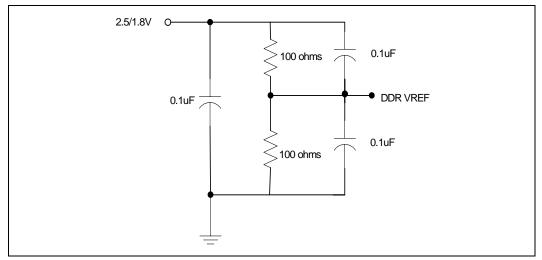

| 71 | DDR V <sub>REF</sub> Circuit                                                     |     |

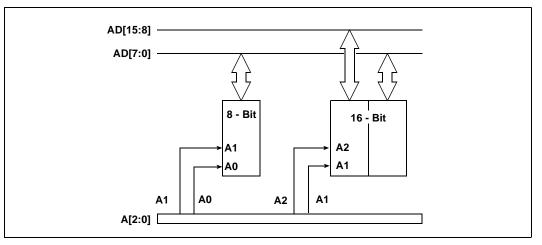

| 72 | Data Width and Low Order Address Lines                                           |     |

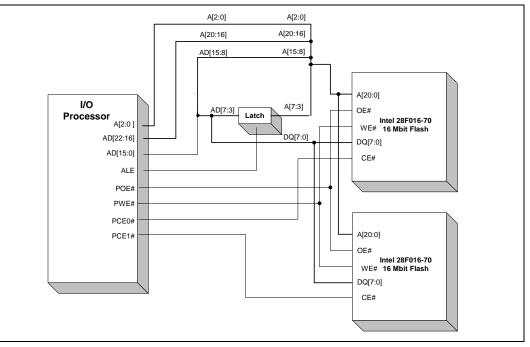

| 73 | Four MByte Flash Memory System                                                   |     |

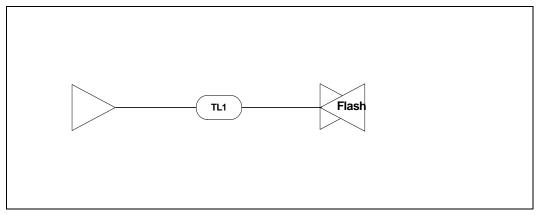

| 74 | Peripheral Bus Unlatched Bidirectional Single Load Topology                      |     |

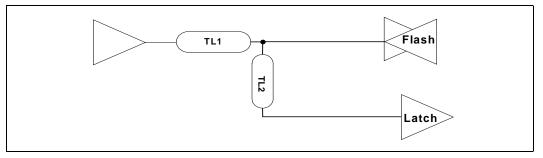

| 75 | Peripheral Bus Latched Bidirectional Single Load Topology                        |     |

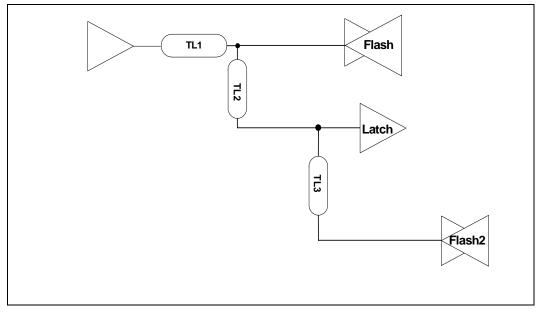

| 76 | Peripheral Bus Latched Bidirectional Two Load Topology                           |     |

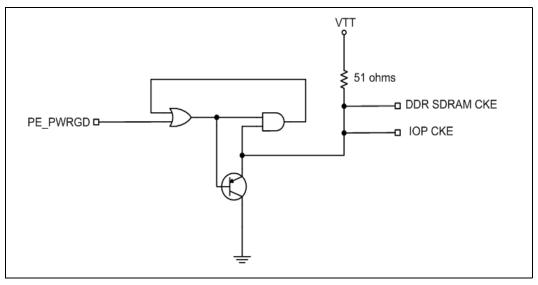

| 77 | SCKE Circuit.                                                                    |     |

| 78 | IQ80333 Block Diagram                                                            |     |

| 79 | IQ80333 Form Factor                                                              |     |

| 80 | JTAG Header Pin Out                                                              |     |

| 81 | JTAG Signals at Powerup                                                          |     |

| 82 | JTAG Signals at Debug Startup                                                    |     |

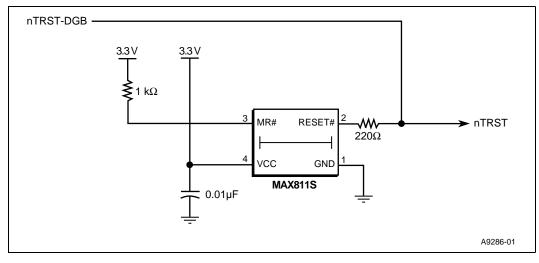

| 83 | Example Power-Up Circuit for nTRST                                               | 162 |

### **Tables**

| 1        | Terminology and Definitions                                              | 12  |

|----------|--------------------------------------------------------------------------|-----|

| 2        | FC-style, H-PBGA Package Dimensions                                      | 17  |

| 3        | Terminations: Pull-up/Pull-down                                          | 25  |

| 4        | Decoupling Recommendations                                               | 38  |

| 5        | Motherboard Stack Up, Stripline and Microstrip                           |     |

| 6        | Adapter Card Stack Up, Microstrip and Stripline                          |     |

| 7        | Hot-Plug Decoding Mode                                                   |     |

| 8        | PCI-X Slot Guidelines                                                    |     |

| 9        | PCI-X Clock Layout Requirements Summary                                  |     |

| 10       | PCI-X 133 MHz Single Slot Routing Recommendations                        |     |

| 11       | Embedded PCI-X 133 MHz Routing Recommendations                           |     |

|          |                                                                          |     |

| 12       | Embedded PCI-X 133 MHz Alternate Topology Routing Recommendations        |     |

| 13       | Embedded and Slot PCI-X 133 MHz Routing Recommendations                  |     |

| 14       | Embedded and Slot PCI-X 133 MHz Routing Recommendations                  |     |

| 15       | PCI-X 133 MHz Hot Plug Routing Recommendations                           |     |

| 16       | PCI-X 100 MHz Slot Topology Routing Recommendations                      |     |

| 17       | PCI-X 100 MHz Embedded Routing Recommendations                           |     |

| 18       | Combination of Slot and Embedded PCI-X 100 MHz Routing Recommendations   |     |

| 19       | Combination of Slot and Embedded PCI-X 100 MHz Routing 2 Recommendations |     |

| 20       | PCI-X 100 MHz Hot Plug Routing Recommendations                           |     |

| 21       | PCI-X 66 MHz Slot Routing Recommendations                                | 65  |

| 22       | PCI-X 66 MHz Embedded Routing Recommendations                            | 66  |

| 23       | PCI-X 66 MHz Mixed Mode Routing Recommendations                          |     |

| 24       | PCI 66 MHz Slot Table                                                    |     |

| 25       | PCI 66 MHz Embedded Table                                                |     |

| 26       | PCI 66 MHz Mixed Mode Table                                              | 70  |

| 27       | PCI 33 MHz Slot Routing Recommendations                                  |     |

| 28       | PCI 33 MHz Embedded Routing Recommendations                              |     |

| 29       | PCI 33 MHz Mixed Mode Routing Recommendations                            |     |

| 30       | PCI Express Layout for 80333 on the Motherboard                          |     |

| 31       | PCI Express Layout for Baseboard Topology                                |     |

| 32       | PCI Express Layout for 80333 Adapter Card Topology                       |     |

| 33       | PCI Express Layout for 80333 Adapter Card Topology                       |     |

| 33<br>34 | DDR Bias Voltages                                                        |     |

| -        | •                                                                        |     |

| 35       | DDR II Bias Voltage                                                      |     |

| 36       | Core Speed and Memory Configuration                                      |     |

| 37       | Simulated DDR 333 Topologies                                             |     |

| 38       | Example Topologies for DDR Trace                                         |     |

| 39       | x64 DDR Memory Configuration                                             |     |

| 40       | x72 DDR Memory Configuration                                             |     |

| 41       | Source Synchronous Termination Requirements                              |     |

| 42       | Source Synchronous Routing Recommendations                               | 89  |

| 43       | DIMM DQ/DQS Topology Lengths                                             |     |

| 44       | Die to Ball Internal Lengths                                             |     |

| 45       | DIMM DQ/DQS Split Termination Topology Lengths                           | 96  |

| 46       | DIMM Clocked Signal Group Termination                                    |     |

| 47       | Clock Signal Group Registered/Unbuffered DIMM Routing Requirements       | 100 |

| 48       | Registered DIMM Clock Topology Lengths                                   |     |

# intel®

| 49 | DDR 333 Unbuffered DIMM Clock Topology Lengths                               | 102 |

|----|------------------------------------------------------------------------------|-----|

| 50 | Source Clocked Signal Routing                                                |     |

| 51 | Control Signals Routing Guidelines                                           |     |

| 52 | Control Signal DIMM Topology Lengths                                         |     |

| 53 | DDR 333 Embedded Source Synchronous Routing Recommendations                  |     |

| 54 | Embedded DDR 333 DQ/DQS Topology Lengths                                     | 109 |

| 55 | DDR 333 Embedded Registered/Unbuffered Clock Routing Recommendations         | 111 |

| 56 | Embedded DDR 333 Buffered Clock Topology Lengths                             |     |

| 57 | Embedded DDR 333 Unbuffered Clock Topology Lengths                           |     |

| 58 | DDR 333 Embedded Address/Command Routing Recommendations                     | 114 |

| 59 | Embedded DDR 333 Unbuffered Address/CMD Topology Lengths                     | 116 |

| 60 | Embedded DDR 333 Registered Address/CMD Topology Lengths                     | 117 |

| 61 | x64 DDR Memory Configuration                                                 | 119 |

| 62 | x72 DDR Memory Configuration                                                 | 119 |

| 63 | DDR II Topologies Simulated                                                  |     |

| 64 | Example Topology for DDRII Trace Width/Impedance Requirements                | 121 |

| 65 | DDRII 400 DIMM Source Synchronous Routing Recommendations                    |     |

| 67 | DDR II 400 DIMM DQS Lengths                                                  | 124 |

| 66 | DDR II 400 DIMM DQ Lengths                                                   | 124 |

| 68 | DDRII 400 DIMM Clock Routing Recommendations                                 | 125 |

| 69 | DDR II 400 DIMM Clock Lengths                                                | 125 |

| 70 | DDRII 400 DIMM Address/Command/Control Routing Recommendation                | 126 |

| 71 | DDR II 400 DIMM Address/CMD Lengths                                          | 127 |

| 72 | DDRII 400 Embedded Source Synchronous Routing Recommendations                | 128 |

| 73 | DDR II 400 Embedded DQ Lengths                                               | 129 |

| 74 | DDR II 400 Embedded DQS Lengths                                              |     |

| 75 | DDRII 400 Embedded Clock Routing Recommendations                             | 131 |

| 76 | DDR II 400 Embedded Clock (PLL) Lengths                                      |     |

| 77 | DDRII 400 Embedded Address/Command/Control Routing Recommendations           | 134 |

| 78 | DDR II 400 Embedded Address/CMD Lengths                                      | 135 |

| 79 | Flash Wait State Profile Programming                                         | 143 |

| 80 | Routing Guideline Bidirectional Single Load                                  |     |

| 81 | Routing Guideline Latched Bidirectional Latch Single Load                    |     |

| 82 | Routing Guideline Latch Bidirectional Two Loads                              | 147 |

| 83 | Intel <sup>®</sup> 80333 I/O Processor Bias Voltages                         | 149 |

| 84 | IQ80333 Features                                                             |     |

| 85 | Intel <sup>®</sup> 80333 I/O Processor CPU Frequencies and DDR Configuration | 157 |

| 86 | DDR II DIMM Configurations                                                   | 157 |

| 87 | Logic Analyzer Pod 1                                                         | 163 |

| 89 | Logic Analyzer Pod 3                                                         | 164 |

| 88 | Logic Analyzer Pod 2                                                         | 164 |

| 91 | Logic Analyzer Pod 5                                                         | 165 |

| 90 | Logic Analyzer Pod 4                                                         | 165 |

| 92 | Logic Analyzer Pod 6                                                         |     |

| 93 | Design References                                                            |     |

| 94 | Intel Related Documentation                                                  |     |

| 95 | Electronic Information                                                       | 170 |

# **Revision History**

тата

| Date       | Revision | Description     |

|------------|----------|-----------------|

| March 2005 | 001      | Initial release |

# Introduction

### 1.1 About This Document

This document provides layout information and guidelines for designing platform or add-in board applications with the Intel<sup>®</sup> 80333 I/O Processor (80333), which is ARM\* architecture compliant. It is recommended that this document be used as a guideline. Intel recommends employing best-known design practices with board level simulation, signal integrity testing and validation for a robust design.

Designers please note that this guide focuses upon specific design considerations for the 80333 and is not intended to be an all-inclusive list of all good design practices. Use this guide as a starting point and use empirical data to optimize your particular design.

Intel Corporation assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice. In particular, descriptions of features, timings, packaging, and pin-outs does not imply a commitment to implement them. In fact, this specification does not imply a commitment by Intel to design, manufacture, or sell the product described herein.

### **1.1.1 Terminology and Definitions**

### Table 1.Terminology and Definitions (Sheet 1 of 2)

| Term                         | Defir                                                                                                                                                                                                                                                                                                                                                            | nition                                                                                                                                                                                                                                                                                            |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 80333                        | Intel <sup>®</sup> 80333 I/O Processor                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                   |  |  |

| Stripline                    |                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>Stripline in a PCB is composed of the conductor inserted in a dielectric with GND planes to the top and bottom.</li> <li><b>NOTE:</b> An easy way to distinguish stripline from microstrip is that you need to strip away layers of the board to view the trace on stripline.</li> </ul> |  |  |

| Microstrip                   |                                                                                                                                                                                                                                                                                                                                                                  | Microstrip in a PCB is composed of the conductor on the top layer above the dielectric with a ground plane below                                                                                                                                                                                  |  |  |

| Prepreg                      | Material used for the lamination process of ma epoxy material that is placed between two core forms around adjacent traces.                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                   |  |  |

| Core                         | Material used for the lamination process of ma laminate with copper on each side. The core is                                                                                                                                                                                                                                                                    | nufacturing PCBs. This material is two sided an internal layer that is etched.                                                                                                                                                                                                                    |  |  |

| PCB                          | Layer 1: copper<br>Prepreg<br>Layer 2: GND<br>Core<br>Layer 3: V <sub>CC</sub><br>Prepreg<br>Layer 4: copper<br>Example of a Four-Layer Stack                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                   |  |  |

| DDR                          | Double Data Rate Synchronous DRAM. Data is<br>clock.                                                                                                                                                                                                                                                                                                             | clocked on both rising and falling edges of the                                                                                                                                                                                                                                                   |  |  |

| DDR II                       | DDR II is backward compatible with DDR I. Ho<br>3.2 GBytes/sec with a clock rate of 200 MHz for<br>rate of 6.4 Gbytes/sec with a clock rate of 400<br>configuration.                                                                                                                                                                                             | or multiple DIMM configurations. It allows data                                                                                                                                                                                                                                                   |  |  |

| DIMM                         | Dual Inline Memory Module                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                   |  |  |

| Source<br>Synchronous<br>DDR | <ul> <li>For reads data leaves the DDR or memory controller with a data strobe. The memory controller delays the data strobe internally to line it up with the data valid window.</li> <li>For writes the memory controller places the data strobe in the middle of the data valid window to ensure that the correct data gets clocked into the DRAM.</li> </ul> |                                                                                                                                                                                                                                                                                                   |  |  |

| SSTL_2                       | Series Stub Terminated Logic for 2.5 V                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                   |  |  |

| JEDEC                        | Provides standards for the semiconductor indu                                                                                                                                                                                                                                                                                                                    | stry.                                                                                                                                                                                                                                                                                             |  |  |

| DLL                          | Delay Lock Loop - refers to the DDR feature us<br>in data.                                                                                                                                                                                                                                                                                                       | ed to provide appropriate strobe delay to clock                                                                                                                                                                                                                                                   |  |  |

# intel®

Table 1.Terminology and Definitions (Sheet 2 of 2)

| Term                                                                                                                          | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                               | A network that transmits a coupled signal to another network is aggressor network.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Aggressor                                                                                                                     | Zo<br>Zo<br>Victim Network<br>Aggressor Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Victim                                                                                                                        | A network that receives a coupled cross-talk signal from another network is a victim network.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Network                                                                                                                       | The trace of a PCB that completes an electrical connection between two or more components.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Stub                                                                                                                          | Branch from a trunk terminating at the pad of an agent.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| ISI                                                                                                                           | Intersymbol Interference (ISI). This occurs when a transition that has not been completely dissipated, interferes with a signal being transmitted down a transmission line. ISI can impact both the timing and signal integrity. It is dependent on frequency, time delay of the line and the refection coefficient at the driver and receiver. Examples of ISI patterns that could be used in testing at the maximum allowable frequencies are the sequences shown below:<br>010101010101010101<br>0001110011100111 |  |  |

| CRB                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| PC1600                                                                                                                        | JEDEC Names for DDR based on peak data rates.<br>PC1600= clock of 100 MHz * 2 data words/clock * 8 bytes = 1600 MB/sec                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| PC2100 JEDEC Names for DDR based on peak data rates.<br>PC2100= clock of 133 MHz * 2 data words/clock * 8 bytes = 2128 MB/sec |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| PC2700                                                                                                                        | JEDEC Names for DDR II based on peak data rates.<br>PC2700= clock of 167 MHz * 2 data words/clock * 8 bytes = 2672 MB/sec                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| PC3200                                                                                                                        | JEDEC Names for DDR II based on peak data rates.<br>PC3200= clock of 200 MHz * 2 data words/clock * 8 bytes = 3200 MB/sec                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Downstream                                                                                                                    | At or toward a PCI Express port directed to the PCI Express root complex (to a bus with a lower number)                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Upstream                                                                                                                      | At or toward a PCI Express port directed away from root complex (to a bus with a higher number).                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Local memory                                                                                                                  | Memory subsystem on the Intel XScale <sup>®</sup> core DDR SDRAM or Peripheral Bus Interface busses.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| DWORD                                                                                                                         | 32-bit data word.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Local bus                                                                                                                     | 80333 Internal Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Outbound                                                                                                                      | At or toward the PCI interface of the 80333 ATU from the Internal Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Inbound                                                                                                                       | At or toward the Internal Bus of the 80333 from the PCI interface of the ATU.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Local processor                                                                                                               | Intel XScale <sup>®</sup> core within the 80333                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Core processor                                                                                                                | Intel XScale <sup>®</sup> core within the 80333                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Flip Chip                                                                                                                     | FC-BGA (flip chip-ball grid array) chip packages are designed with core flipped up on the back of the chip, facing away from the PCB. This allows more efficient cooling of the package.                                                                                                                                                                                                                                                                                                                             |  |  |

| Mode<br>Conversion                                                                                                            | Mode Conversions are due to imperfections on the interconnect which transform differential mode voltage to common mode voltage and common mode voltage to differential voltage.                                                                                                                                                                                                                                                                                                                                      |  |  |

| ROMB                                                                                                                          | Raid on motherboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| ODT                                                                                                                           | On Die Termination - eliminates the need for termination resistors by placing the termination at the chip.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

### 1.1.2 Other Relevant Documents

- 1. Intel® 80333 I/O Processor Specification Update (305435), Intel Corporation

- 2. Intel<sup>®</sup> 80333 I/O Processor Developer's Manual (305432), Intel Corporation

- 3. Intel<sup>®</sup> 80333 I/O Processor Datasheet (305433), Intel Corporation

- 4. Intel XScale<sup>®</sup> 80200 Processor based on Intel<sup>®</sup> Microarchitecture Developer's Manual (273411), Intel Corporation

- 5. PCI Express Specification, Revision 1.0a

- 6. PCI Express Card Electromechanical Specification 1.0a

- 7. PCI Local Bus Specification, Revision 2.3 PCI Special Interest Group

- 8. PCI-X Specification, Revision 1.0b PCI Special Interest Group

- 9. PCI Bus Power Management Interface Specification, Revision 1.1 PCI Special Interest Group

- 10. IEEE Standard Test Access Port and Boundary-Scan Architecture (IEEE JTAG-1149.1-1990)

- 11. PCI Bus Hot-Plug Specification, Revision 1.1 PCI Special Interest Group

# intel

## 1.2 About the Intel<sup>®</sup> 80333 I/O Processor

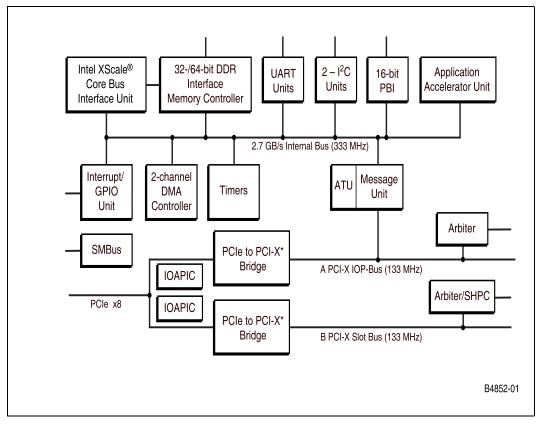

The 80333 is a multi-function device that integrates the Intel XScale<sup>®</sup> core (ARM\* architecture compliant) with intelligent peripherals and dual PCI Express-to-PCI Bridges. The 80333 consolidates the following into a single system:

- Intel XScale<sup>®</sup> core

- x8 PCI Express Upstream Link

- Two PCI Express-to-PCI Bridges supporting PCI-X interface on both segments.

- PCI Standard Hot Plug Controller (segment B)

- Address Translation Unit (PCI-to-Internal Bus Application Bridge) interfaced to the segment A

- High-Performance, Dual-Ported Memory Controller

- Interrupt Controller with up to17 external interrupt inputs

- Two Direct Memory Access (DMA) Controllers

- Application Accelerator with RAID 6 support

- Messaging Unit

- Peripheral Bus Interface Unit

- Two I<sup>2</sup>C Bus Interface Units

- Two 16550 compatible UARTs with flow control (four pins)

- Eight General Purpose Input Output (GPIO) ports

It is an integrated processor that addresses the needs of intelligent I/O applications and helps reduce intelligent I/O system costs.

PCI Express is an industry standard, high performance, low latency system interconnect. The 80333 PCI Express upstream link is capable of x8 lane widths at 2.5 GHz operation as defined by the *PCI Express Specification*, Revision 1.0a. The addition of the Intel XScale<sup>®</sup> core brings intelligence to the PCI Express-to-PCI Bridges.

The 80333 integrates dual PCI Express-to-PCI Bridges with the ATU as an integrated secondary PCI device. The Upstream PCI Express port implements the PCI-to-PCI Bridge programming model according to the *PCI Express Specification*, Revision 1.0. The Primary Address Translation Unit is compliant with the *PCI-X Specification*, Revision 1.0a definitions of an 'application bridge'.

Figure 1 provides a block diagram of the 80333.

# int<sub>el</sub> Package Information

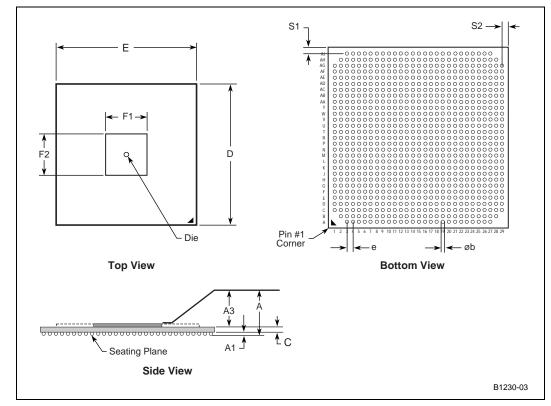

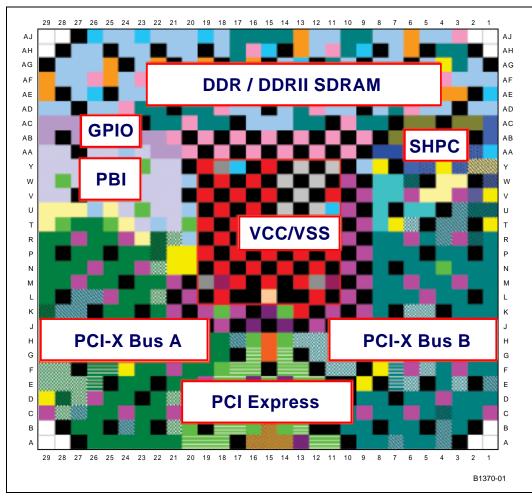

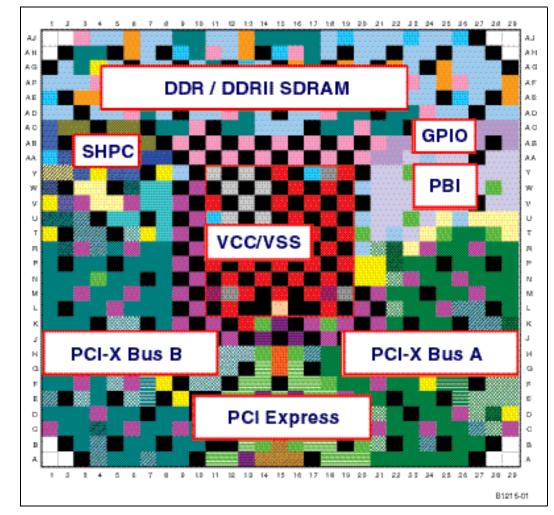

The 80333 is offered in a Flip Chip Ball Grid Array (FCBGA) package. This is a full-array package with 829 ball connections. The mechanical dimensions for this package are provided in the Figure 2 and Table 2. Figure 3 and Figure 4 show the 829 pins of the Flip Chip Ball Grid Array (FCBGA), mapped by pin function. This diagram is helpful in placing components around the 80333 for the layout of a PCB. To simplify routing and minimize the number of cross traces, keep this layout in mind when placing components on your board. The signals, by design, are located on the FCBGA package to simplify signal routing and system implementation.

#### Table 2. FC-style, H-PBGA Package Dimensions

| 829-Pin BGA |            |         |  |

|-------------|------------|---------|--|

| Symbol      | Minimum    | Maximum |  |

| A           | 2.392      | 2.942   |  |

| A1          | 0.50       | 0.70    |  |

| A3          | 0.742      | 0.872   |  |

| b           | 0.61 Ref.  |         |  |

| С           | 1.15       | 1.37    |  |

| D           | 37.45      | 37.55   |  |

| E           | 37.45      | 37.55   |  |

| F1          | 9.88 Ref.  |         |  |

| F2          | 10.16 Ref. |         |  |

| e           | 1.27 Ref.  |         |  |

| S1          | 0.97 Ref.  |         |  |

| S2          | 0.97 Ref.  |         |  |

NOTE: Measurement in millimeters.

### Figure 2. Intel<sup>®</sup> 80333 I/O Processor 829-Ball FCBGA Package Diagram

# intel

### Figure 3. Intel<sup>®</sup> 80333 I/O Processor Ballout (Top View)

### Figure 4. Intel<sup>®</sup> 80333 I/O Processor Ballout (Bottom View)

### 2.1 **Power Plane Layout**

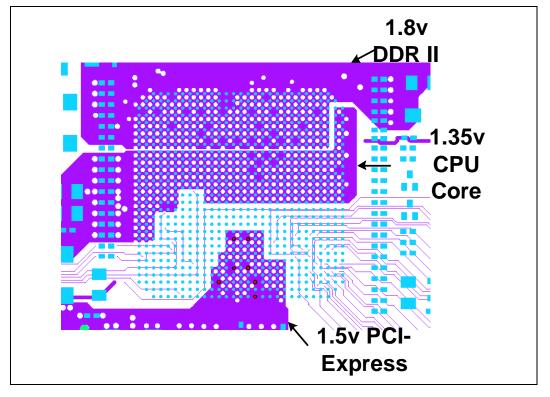

Figure 5 provides the approximate layout of the PCB layers to facilitate the various voltages needed to bias the 80333 package.

Note: The voltage for the PCIX-A bus and PCIX-B bus can be on the same plane.

The 1.5 V PCI-Express interface needs its own voltage regulator (VRM), all to itself. It is allowed no more than 30 mV peak to peak of noise. An alternative is if the core voltage and PCI-Express 1.5V planes are inductively isolated they can share the same regulator. The nominal value of inductance recommended is  $2-4 \mu$ H as shown in Figure 6.

#### Figure 5. Intel<sup>®</sup> 80333 I/O Processor Power Plane Layout

Image: Second second

### Figure 6. Inductively Isolated Split Plane

# intel®

# 2.2 Intel<sup>®</sup> 80333 I/O Processor Applications

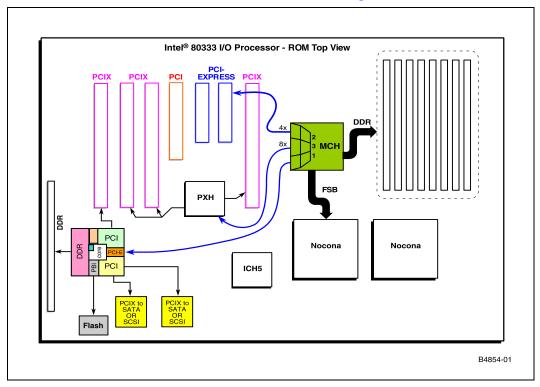

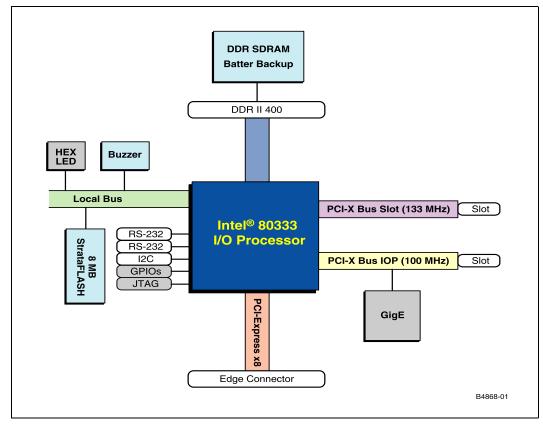

This section provides the block diagrams for 80333 applications. The first consists of a ROMB motherboard application and the second application is a PCI-Express plug-in card application. Figure 7 provides the block diagram of 80333 used in a ROM MCH motherboard application.

Figure 7. Intel<sup>®</sup> 80333 I/O Processor MCH Motherboard Block Diagram

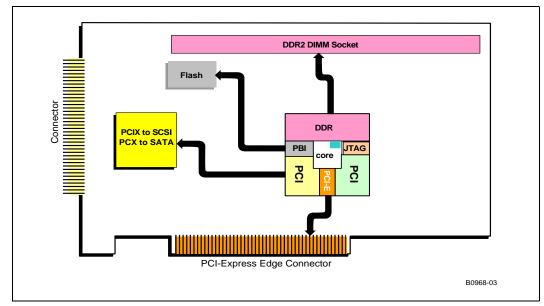

Figure 8 shows 80333 used in a PCI-Express Adapter Card application.

### Figure 8. Intel<sup>®</sup> 80333 I/O Processor PCI-Express Adapter Card Block Diagram

# intel®

This chapter provides the recommended pull-up and pull-down terminations for a 80333 layout. Table 3 lists these 80333 termination values. On a motherboard, the *PCI Local Bus Specification*, Revision 2.3 requires that the PCI signals provide the termination resistors. Due to the fact that 80333 is the central resource for both motherboard and add-in card applications, it is required that both the PCI-A bus and PCI-B bus have pull-ups in each of these applications. Pull-ups on the PCI signals are not required with PCIODT\_EN = 1 (enabled), because they are implemented on the die. Refer to the Table 3 for more information.

#### Table 3. Terminations: Pull-up/Pull-down (Sheet 1 of 5)

| Signal     | Pull-up or Pull-down<br>Resistor Value (in Ohms)                                                                                                 | Comments                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B_HPWRFLT# | No connect*                                                                                                                                      | NOTE: * when Hot Plug is not enabled (internal pull-up is on)                                                                                                     |

| B_HPWREN   | No connect                                                                                                                                       | NOTE: * when Hot Plug is not enabled (internal pull-up is on)                                                                                                     |

| B_HMRL#    | No connect*                                                                                                                                      | <b>NOTE:</b> * when Hot Plug is not enabled (internal pull-up is on)                                                                                              |

| B_HPRSNT2# | No connect*                                                                                                                                      | <b>NOTE:</b> * when Hot Plug is not enabled (internal pull-up is on)                                                                                              |

| B_HPRSNT1# | No connect*                                                                                                                                      | <b>NOTE:</b> * when Hot Plug is not enabled (internal pull-up is on)                                                                                              |

| B_HATNLED# | <ul> <li>If used, connect to<br/>amber or yellow LED</li> <li>Not used -No connect*</li> </ul>                                                   | Parallel Mode Hot-Plug Attention indicator LED signal that is yellow or<br>amber in color<br><b>NOTE:</b> * when Hot Plug is not enabled (internal pull-up is on) |

| B_HPWRLED# | <ul> <li>If used, connect to green LED</li> <li>Not used - No connect*</li> </ul>                                                                | Parallel Mode Hot-Plug Power Indicator LED signal that is green in color.<br>NOTE: * when Hot Plug is not enabled (internal pull-up is on)                        |

| B_HBUTTON# | <ul> <li>If used, connect to<br/>Parallel Mode Hot-Plug<br/>Attention Button input<br/>from the slot.</li> <li>Not used - No connect*</li> </ul> | <b>NOTE:</b> * when Hot Plug is not enabled (internal pull-up is on)                                                                                              |

| B_HRESET#  | This output signal is always<br>'on', therefore, it does not<br>tri-state during boundary<br>scan.                                               |                                                                                                                                                                   |

| Table 3. | Terminations: Pull-up/Pull-down (Sheet 2 of 5) |

|----------|------------------------------------------------|

|----------|------------------------------------------------|

| Signal                         | Pull-up or Pull-down<br>Resistor Value (in Ohms)                                                                                                                                                                                      | Comments                                                                                                                                                                                                                                                                                                                                                                                                     |