# Intel® 81348 I/O Processor

**Design Guide**

May 2007

Order Number: 315053-002US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting Intel's Web Site.

[When the doc contains software source code, include a copy of the software license or a hyperlink to its permanent location.]

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="http://www.intel.com/products/processor\_number">http://www.intel.com/products/processor\_number</a> for details.

Code Names are only for use by Intel to identify products, platforms, programs, services, etc. ("products") in development by Intel that have not been made commercially available to the public, i.e., announced, launched or shipped. They are never to be used as "commercial" names for products. Also, they are not intended to function as trademarks.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead. Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and other countries.

May 2007

Order Number: 315053-002US

\*Other names and brands may be claimed as the property of others.

Copyright © 2007, Intel Corporation. All rights reserved.

# **Contents**

| 1.0 |                 | ut This Document                                 |      |

|-----|-----------------|--------------------------------------------------|------|

|     | 1.2 Inte        | el® 81348 I/O Storage Processor Document Details | 12   |

|     |                 | ut the Intel® 81348 I/O Storage Processor        |      |

| 2.0 |                 | Information                                      |      |

|     | 2.1 Pac         | kage Introduction                                | 15   |

| 3.0 | Board Lay       | yout Guidelines                                  | 17   |

|     |                 | herboard Stack Up Information                    |      |

|     |                 | pter Card Topology                               |      |

|     |                 | Impedance Targets                                |      |

|     | 3.3.            | 1 100 Ohm Differential Trace                     | . 22 |

| 4.0 | Memory (        | Controller                                       | 23   |

|     | 4.1 Ove         | rview                                            | 23   |

|     |                 | R2 533 Layout Guidelines                         |      |

|     | 4.2.            |                                                  |      |

|     | 4.2.            | , ,                                              |      |

|     | 4.2.<br>4.3 DDI | .3 DDR2 533 Embedded Layout Design               |      |

|     | 4.3 DDI<br>4.3. | =                                                |      |

|     |                 | R2 Termination Voltage                           |      |

|     | 4.4.            |                                                  |      |

| 5.0 | DCT Ever        | ess Layout                                       |      |

| 5.0 | -               | ional PCI Express Lane Reversal                  |      |

|     |                 | Express Layout recommendations                   |      |

|     | 5.2.            |                                                  |      |

|     | 5.2.            |                                                  |      |

|     | 5.2.            | 3 Clock Routing Guidelines                       | 51   |

| 6.0 | PCI-X Lav       | yout Guidelines                                  | 53   |

|     |                 | tral Resource/Endpoint Mode Details              |      |

|     | 6.1.            |                                                  |      |

|     | 6.1.            | ··                                               |      |

|     | 6.1.            |                                                  |      |

|     | 6.1.            |                                                  |      |

|     |                 | -X Layout Recommendations                        |      |

|     | 6.2.<br>6.2.    |                                                  |      |

|     | 6.2.            |                                                  |      |

|     | 6.2.            |                                                  |      |

|     | 6.2.            |                                                  | 62   |

|     | 6.2.            |                                                  |      |

|     | 6.2.            | , 5,                                             |      |

|     | 6.2.            |                                                  |      |

|     | 6.2.            | · • · · · · · · · · · · · · · · · · · ·          |      |

|     |                 | 10 Embedded 66 MHz Topology                      |      |

|     |                 | 11 Mixed 66 MHz Topology                         |      |

|     |                 | ·                                                |      |

| 7.0 |                 | S Bus Layout                                     |      |

|     | 7.1 SAS         | S/SATA General Recommendations                   | 69   |

| 8.0  | •     |                                                                              |     |  |  |  |  |

|------|-------|------------------------------------------------------------------------------|-----|--|--|--|--|

|      | 8.1   | Peripheral Bus Signals                                                       |     |  |  |  |  |

|      | 8.2   | PBI Bus Width                                                                |     |  |  |  |  |

|      | 8.3   | Flash Memory Support                                                         |     |  |  |  |  |

|      | 8.4   | PBI Topology Layout Guidelines                                               | 74  |  |  |  |  |

| 9.0  | Powe  | r Delivery                                                                   | 77  |  |  |  |  |

|      | 9.1   | Power Plane Layout                                                           | 78  |  |  |  |  |

|      | 9.2   | Decoupling Recommendations                                                   |     |  |  |  |  |

|      |       | 9.2.1 Customer Reference Board Decoupling Implementation                     | 83  |  |  |  |  |

|      | 9.3   | Power Sequencing                                                             | 84  |  |  |  |  |

|      | 9.4   | Power Failure                                                                | 85  |  |  |  |  |

|      |       | 9.4.1 Non-Battery Backup Circuits                                            | 86  |  |  |  |  |

| 10.0 | JTAG  | Circuitry for Debug                                                          | 87  |  |  |  |  |

|      | 10.1  | Requirements                                                                 |     |  |  |  |  |

|      | 10.2  | JTAG Signals / Header                                                        |     |  |  |  |  |

|      | 10.3  | System Requirements                                                          |     |  |  |  |  |

|      | 10.4  | JTAG Hardware Requirements                                                   |     |  |  |  |  |

|      |       | 10.4.1 Macraigor Raven and WindRiver Systems visionPROBE/visionICE           | 90  |  |  |  |  |

|      |       | 10.4.2 ARM Multi-ICE                                                         | 90  |  |  |  |  |

| 11 0 | Debu  | g and Test                                                                   | 91  |  |  |  |  |

| 11.0 | 11.1  | -                                                                            |     |  |  |  |  |

|      | 11.2  | PCI Express Debugging                                                        |     |  |  |  |  |

|      | 11.2  | 11.2.1 Physical Layer Debugging                                              |     |  |  |  |  |

|      |       | 11.2.2 Data Link and Transaction Layer Testing                               |     |  |  |  |  |

|      |       | 11.2.3 PCI Express Analyzer/Exercisers                                       |     |  |  |  |  |

|      |       | 11.2.4 Mid-bus Probing                                                       |     |  |  |  |  |

|      | 11.3  | SAS Debugging                                                                | 93  |  |  |  |  |

|      | 11.4  | SATA Debugging                                                               | 94  |  |  |  |  |

| 12.0 | Term  | inations                                                                     | 95  |  |  |  |  |

|      | 12.1  | Important Design and Debug Requirements                                      |     |  |  |  |  |

|      | 12.2  | Termination Checklist                                                        |     |  |  |  |  |

|      | 12.3  | Reset Straps                                                                 |     |  |  |  |  |

|      | 12.4  | Configuration Details                                                        |     |  |  |  |  |

|      |       | 12.4.1 PCI-E Mode Only                                                       |     |  |  |  |  |

|      |       | 12.4.2 PCI-X Mode Only                                                       |     |  |  |  |  |

|      |       | 12.4.3 Dual Interface Mode                                                   |     |  |  |  |  |

|      | 12.5  | Analog Filters                                                               | 113 |  |  |  |  |

|      |       | 12.5.1 V <sub>CC1P2PLLS0</sub> , V <sub>CC1P2PLLS1</sub> Filter Requirements | 114 |  |  |  |  |

|      |       | 12.5.2 V <sub>CC1P2PLLP</sub> , V <sub>CC1P2PLLD</sub> Filter Requirements   | 116 |  |  |  |  |

|      |       | 12.5.3 V <sub>CC3P3PLLX</sub> PLL Requirements                               | 118 |  |  |  |  |

|      | 12.6  | PCI Resistor Calibration                                                     |     |  |  |  |  |

|      | 12.7  | PCI Express Resistor Compensation                                            |     |  |  |  |  |

|      | 12.8  | Memory Calibration Circuitry                                                 |     |  |  |  |  |

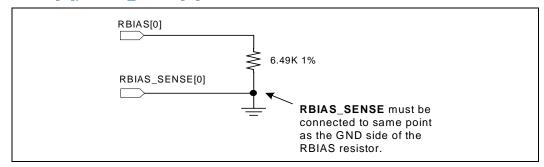

|      | 12.9  | RBIAS Circuit                                                                |     |  |  |  |  |

| 13.0 | -     | ıt Checklist                                                                 |     |  |  |  |  |

|      | 13.1  | Intel® 81348 I/O Processor Layout Checklist                                  | 123 |  |  |  |  |

| 14.0 | Refer | ences                                                                        | 139 |  |  |  |  |

|      | 14.1  | Relevant Documents                                                           |     |  |  |  |  |

|      | 14.2  | Design References                                                            |     |  |  |  |  |

|      | 14.3  | Literature Resources                                                         |     |  |  |  |  |

|      |       |                                                                              |     |  |  |  |  |

#### Contents-81348

May 2007

Order Number: 315053-002US

Intel® 81348 I/O Processor

Design Guide

5

# **Figures**

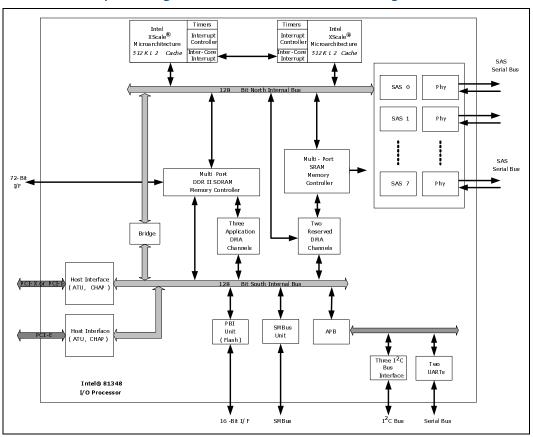

| 1        | Intel® 81348 I/O Storage Processor Functional Block Diagram              |    |

|----------|--------------------------------------------------------------------------|----|

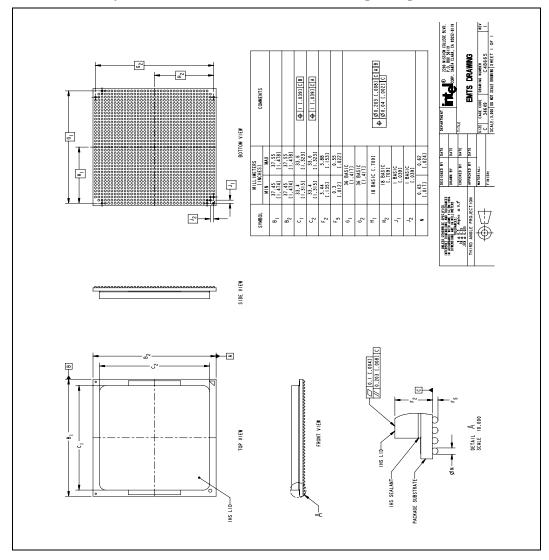

| 2        | Intel® 81348 I/O Processor 1357-ball FCBGA Package Diagram               |    |

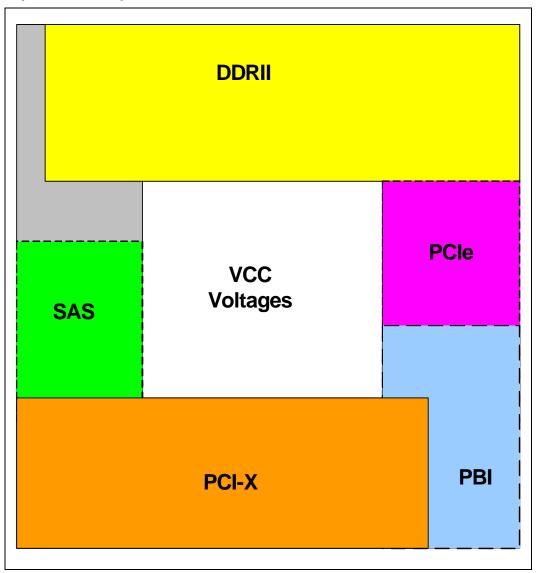

| 3        | Top View Ball Map Interfaces                                             |    |

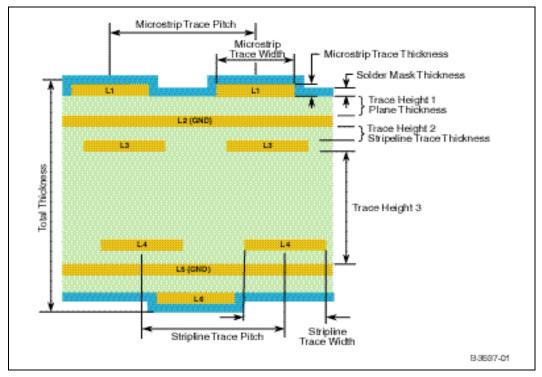

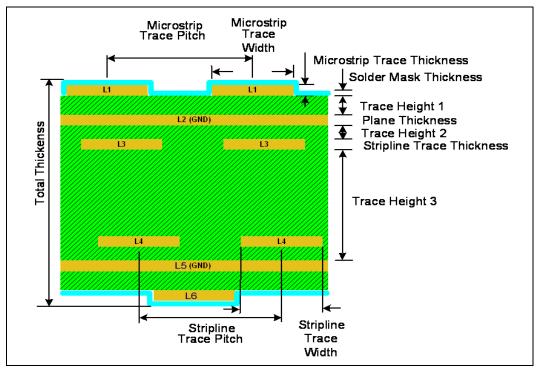

| 4        | Motherboard Stackup Recommendations                                      |    |

| 5        | Adapter Card Stackup                                                     |    |

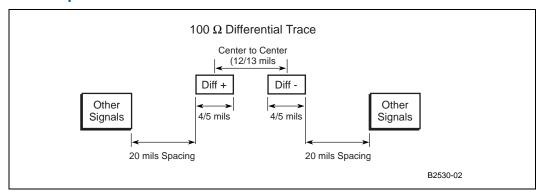

| 6        | An Example of 100 Ohm Differential Trace                                 | 22 |

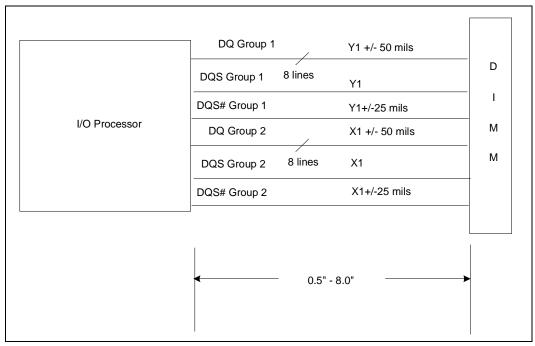

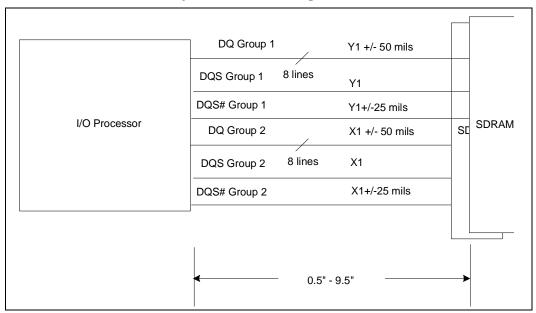

| 7        | DDR2 DIMM Source Synchronous Routing                                     |    |

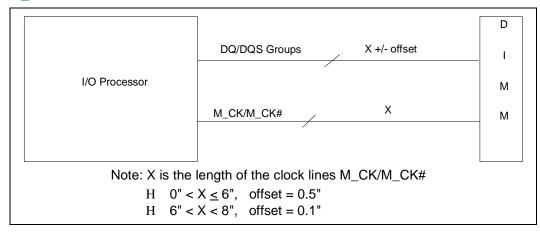

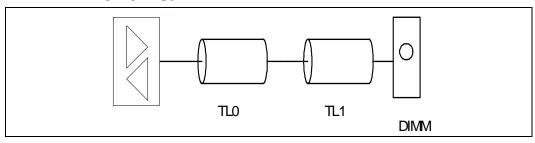

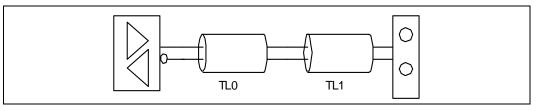

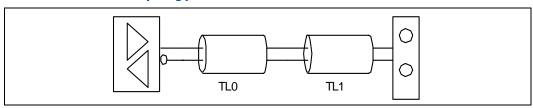

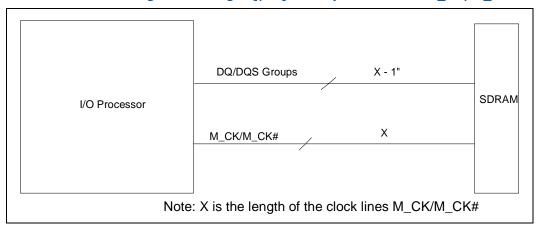

| 8        | DDR2 DIMM Length Matching DQ/DQS Group with Respect to Clocks M_CK/M_CK# | 26 |

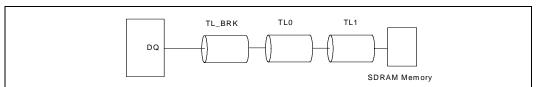

| 9        | DDR2 DIMM DQ Topology                                                    | 27 |

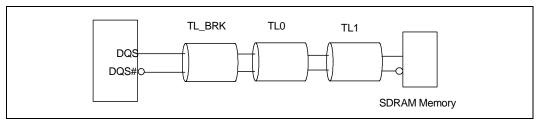

| 10       | DDR2 DIMM DQS Topology                                                   | 27 |

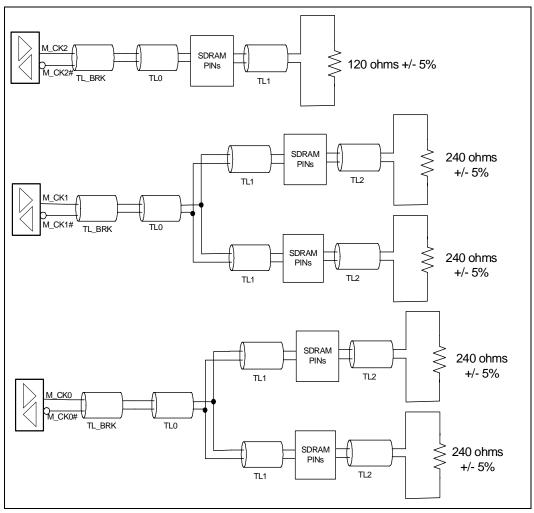

| 11       | DDR2 DIMM Clock Topology                                                 | 29 |

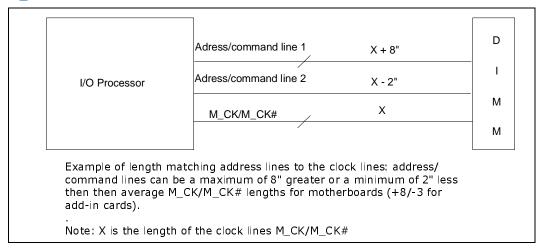

| 12       | DDR2 DIMM Length Matching Address/Command Group to Clocks M_CK/M_CK#     | 31 |

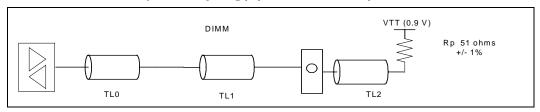

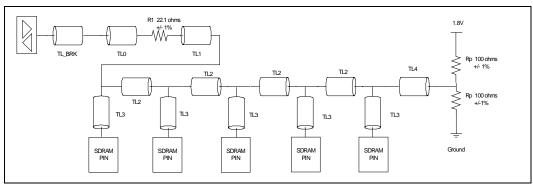

| 13       | DDR2 DIMM Address/CMD Topology (Vtt Termination)                         | 31 |

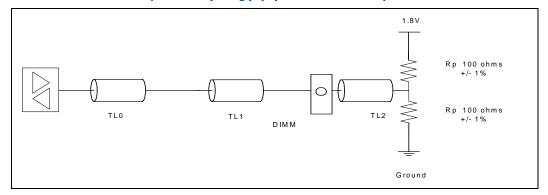

| 14       | DDR2 DIMM Address/CMD Topology (Split Termination)                       |    |

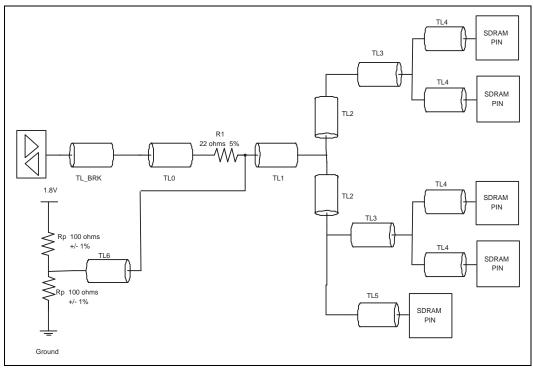

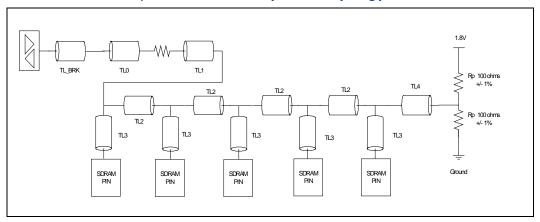

| 15       | DDR2 Embedded Source Synchronous Routing                                 |    |

| 16       | DDR2 Embedded Length Matching DQ/DQS Group with Clocks M_CK/M_CK#        |    |

| 17       | DDR2 Embedded DQ Topology                                                |    |

| 18       | DDR2 Embedded DQS Topology                                               |    |

| 19       | DDR2 Embedded Clock Topology With Five SDRAMs                            |    |

| 20       | DDR2 Embedded Address/CMD Topology (Split Termination)                   |    |

| 21       | DDR2 Embedded CS, ODT and CKE Balanced Topology                          |    |

| 22       | DDR2 Embedded CS, ODT and CKE Daisy Chain Topology                       |    |

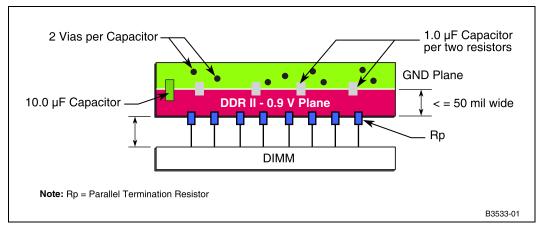

| 23       | Routing Termination Resistors (Top View)                                 |    |

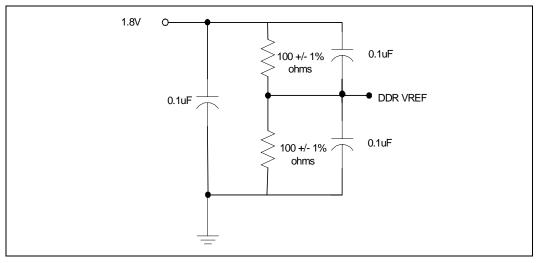

| 24       | DDR V <sub>RFF</sub> Circuit                                             |    |

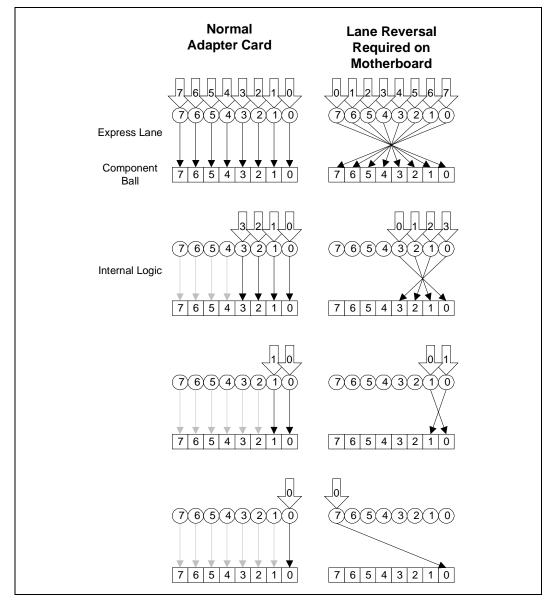

| 25       | PCI Express Lane Reversal To Improve PCB Routing                         |    |

| 26       | Motherboard Topology                                                     |    |

| 27       | Motherboard-Adapter Card Topology                                        |    |

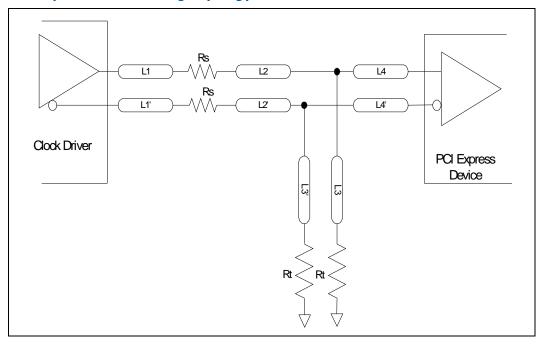

| 28       | PCI Express Clock Routing Topology                                       |    |

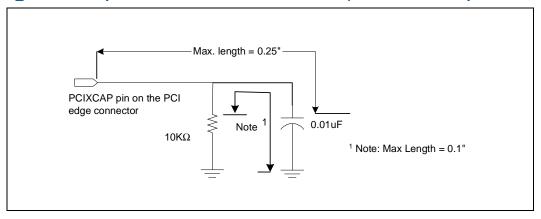

| 29       | P_PCIXCAP Layout Guidelines with Intel® 81348 I/O Processor Adapter card |    |

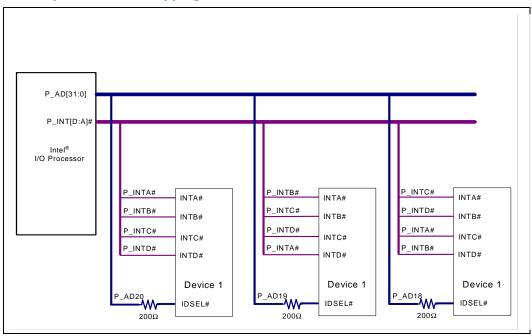

| 30       | Interrupt and IDSEL Mapping                                              |    |

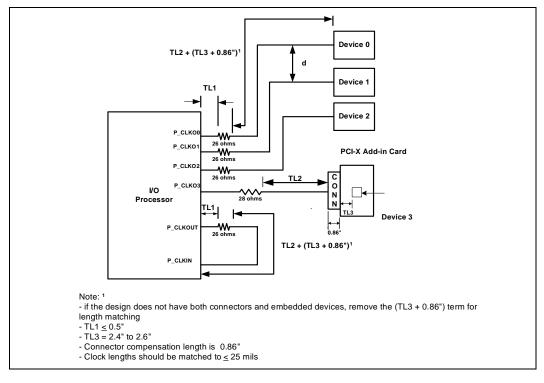

| 31       | PCI Clock Distribution and Matching Requirements                         |    |

| 32       | 133 MHz One Slot Topology                                                |    |

| 33       | Embedded 133 MHz Topology                                                |    |

| 34       | Mixed 133 MHz Topology                                                   |    |

| 35       | 100 MHz Dual Slot Topology                                               |    |

| 36       | Embedded 100 MHz Topology                                                |    |

| 37       | Mixed 100 MHz Topology                                                   |    |

| 38       | 66 MHz Four Slot Topology                                                |    |

| 39       | Embedded 66 MHz Topology                                                 |    |

| 40       | Mixed 66 MHz Topology                                                    |    |

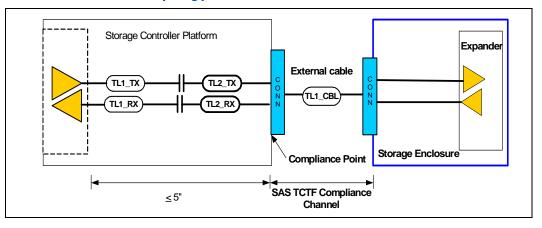

| 41       | SAS Inter-enclosure Topology                                             |    |

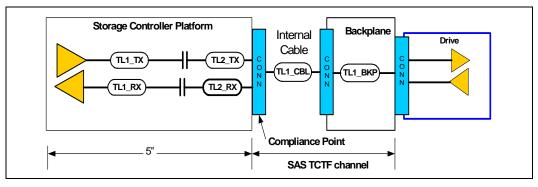

| 42       | SAS Intra-enclosure Topology                                             |    |

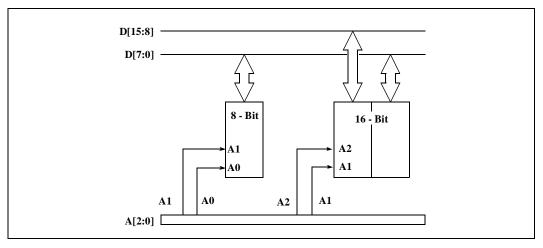

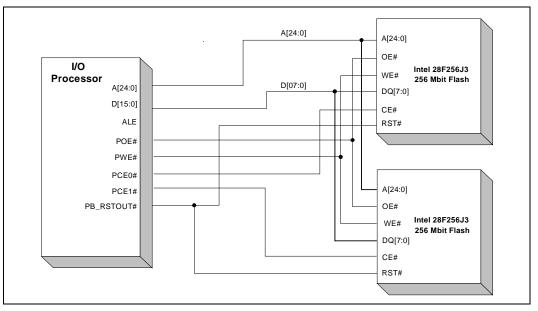

| 43       | Data Width and Low Order Address Lines                                   |    |

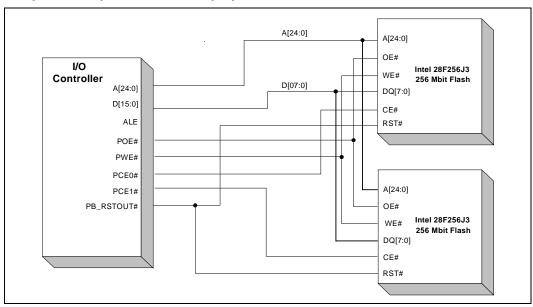

| 44       | Sixty-Four Mbyte Flash Memory System                                     |    |

| 45       | Sixty-Four Mbyte Flash Memory System                                     |    |

|          |                                                                          |    |

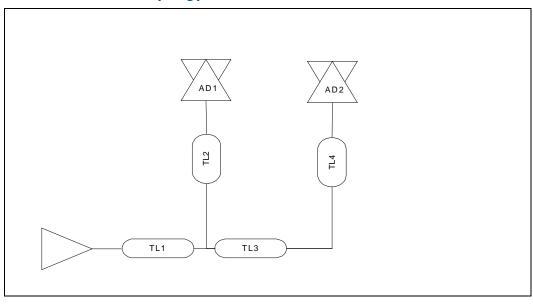

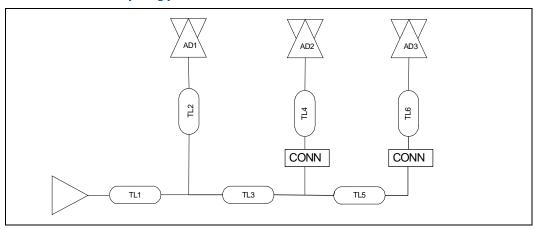

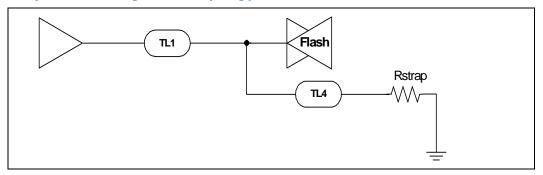

| 46<br>47 | Peripheral Bus Single Load Topology                                      |    |

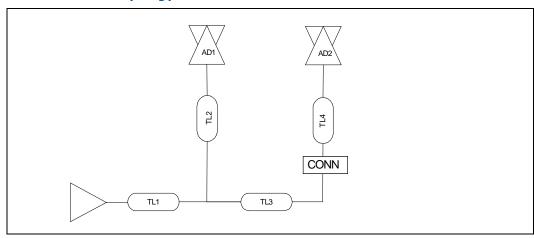

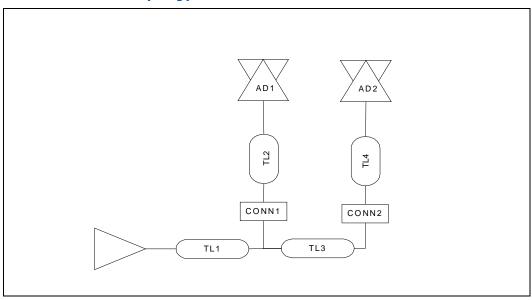

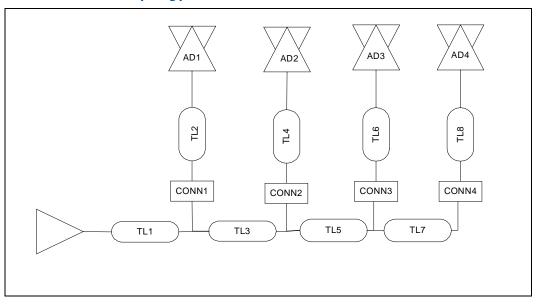

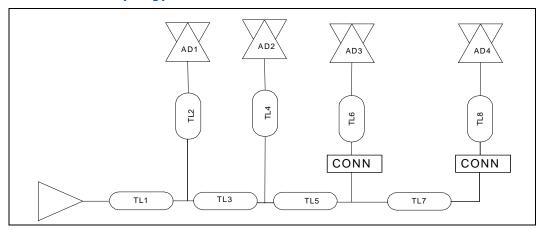

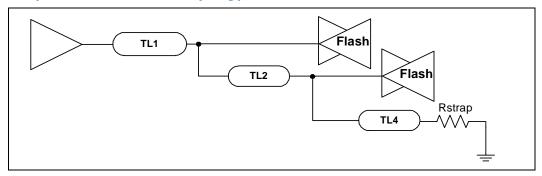

| 47       | Peripheral Bus Dual Load Topology                                        |    |

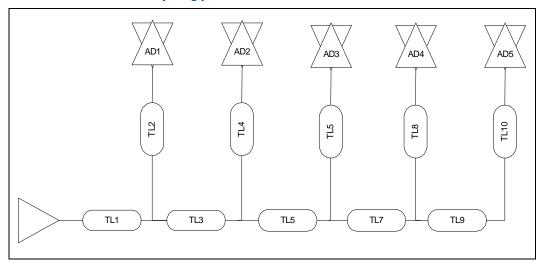

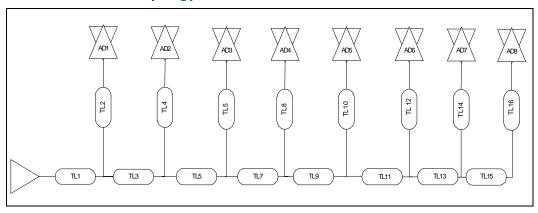

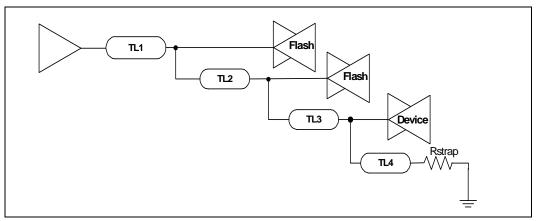

| 48       | Peripheral Bus Three Load Topology                                       |    |

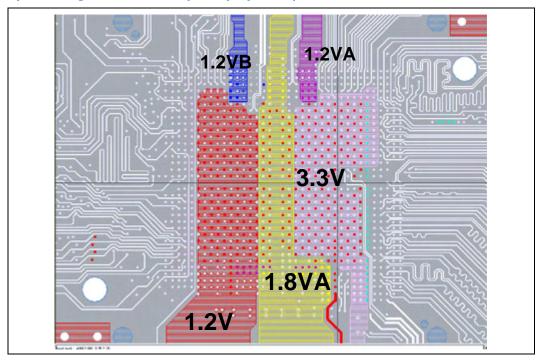

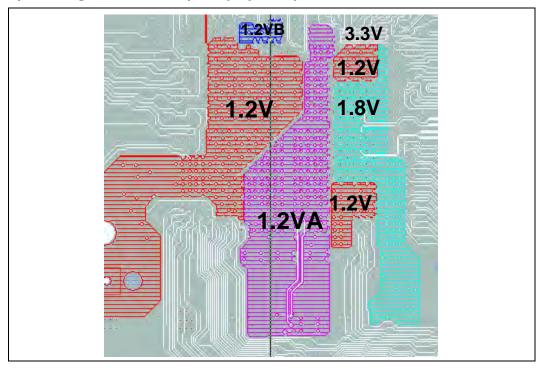

| 50       | Split Voltage Planes for Layer 4 (Top View)                              |    |

| 49       | Split Voltage Planes for Layer 3 (Top View)                              |    |

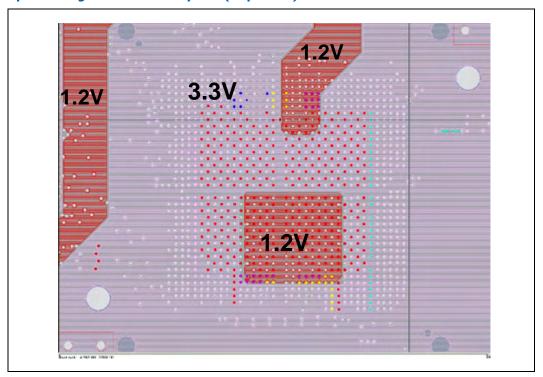

| 51       | Split Voltage Planes for Layer 6 (Top View)                              |    |

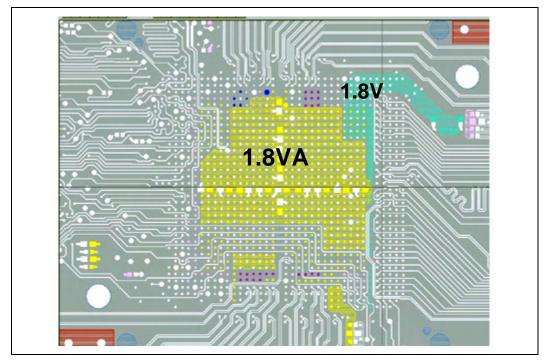

| 52       | Split Voltage Planes for Layer 8 (Top View)                              |    |

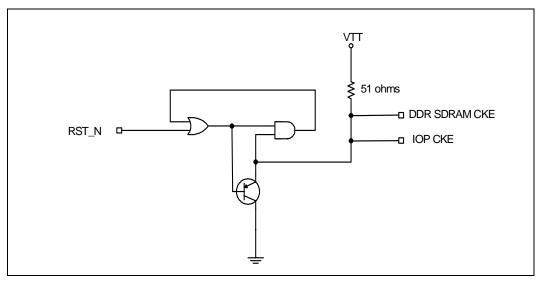

| 53       | SCKE Circuit                                                             | გ5 |

#### Contents-81348

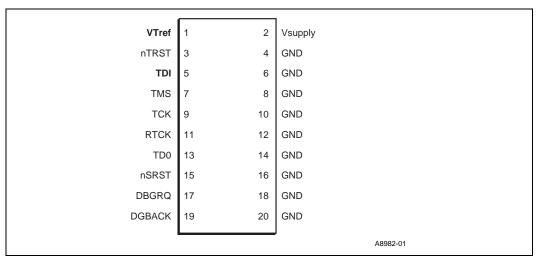

| 54 | JTAG Header Pin Out                                | 88    |

|----|----------------------------------------------------|-------|

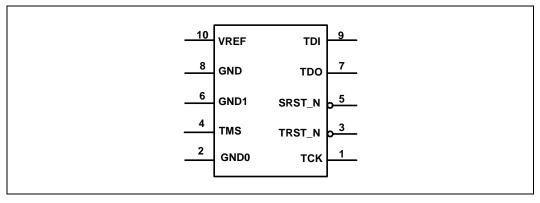

| 55 | Mini JTAG Header Pin Out                           | 88    |

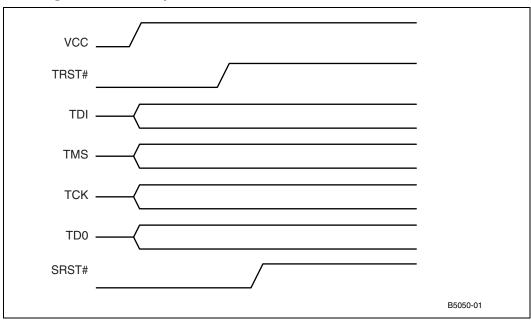

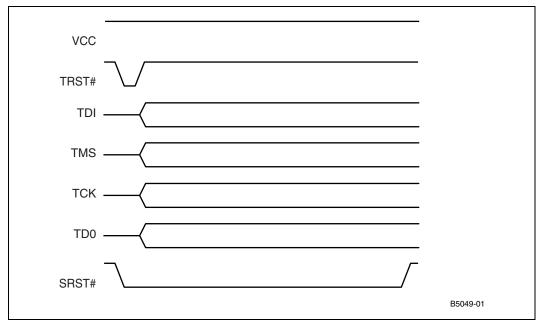

| 56 | JTAG Signals at Powerup                            | 89    |

| 57 | JTAG Signals at Debug Startup                      | 89    |

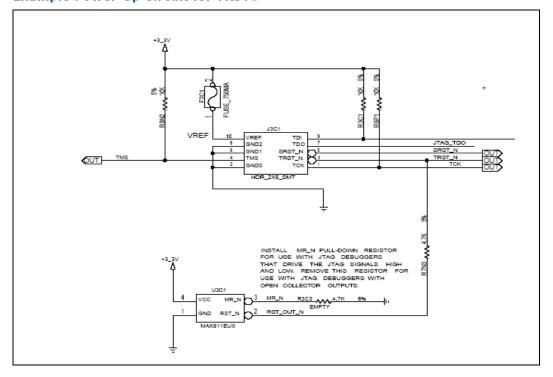

| 58 | Example Power-Up Circuit for TRST#                 | 90    |

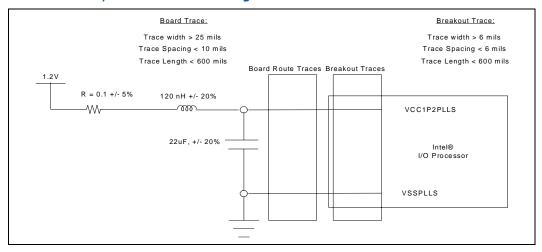

| 59 | VCC1P2PLLS0, VCC1P2PLLS1 Configuration             | . 115 |

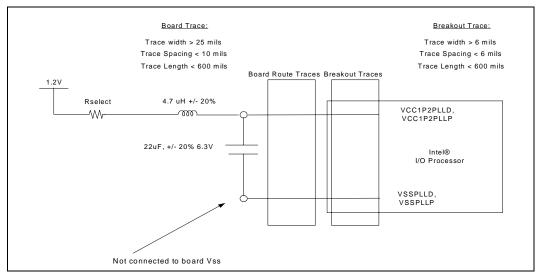

| 60 | VCC1P2PLLD, VCC1P2PLL Lowpass Filter Configuration | . 117 |

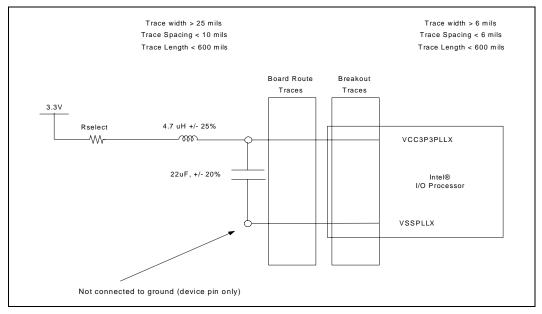

| 61 | VCC3P3PLL Filter Configuration                     | . 119 |

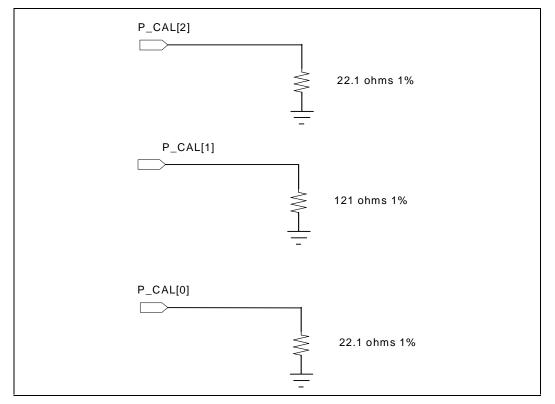

|    | PCI Resistor Calibration                           |       |

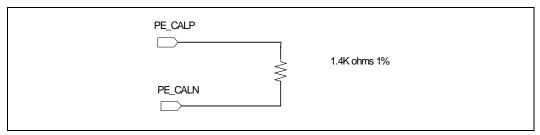

| 63 | PCI Express RCOMP                                  | . 121 |

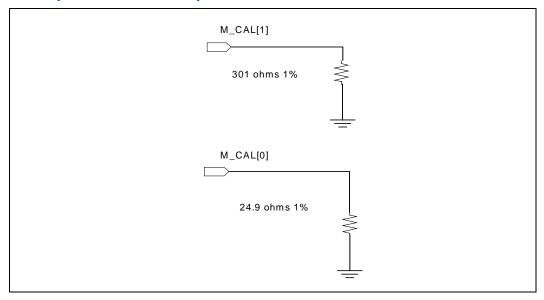

| 64 | Memory Calibration Circuitry                       | . 121 |

|    | RBIAS[0], RBIAS SENSE[0] Connections               |       |

# **Tables**

| Adapter Card Stack Up, Microstrip and Stripline.  Single-ended Trace Parameters  Differential Trace Dimensions.  6 x72 DDR Memory Configuration.  DDR2 DIM Mource Synchronous Routing Recommendations.  DDR2 DIMM Dol Lengths.  DDR2 DIMM DQ Lengths.  DDR2 DIMM Lock Routing Recommendations.  DDR2 DIMM Clock Lengths.  DDR2 DIMM Clock Lengths.  DDR2 DIMM Clock Lengths.  DDR2 DIMM Address/Command/Control Routing Recommendation.  DDR2 Embedded Source Synchronous Routing Recommendation.  DDR2 Embedded Source Synchronous Routing Recommendation.  DDR2 Embedded DQS Lengths.  DDR2 Embedded DQS Lengths.  DDR2 Embedded Clock Routing Recommendations.  DDR2 Embedded Clock Routing Recommendations.  DDR2 Embedded Clock Lengths.  DDR2 Embedded Clock Lengths.  DDR2 Embedded Clock Lengths public Recommendation.  DDR2 Embedded Clock Lengths public Recommendation.  DDR2 Embedded Clock Lengths public Recommendation.  DDR2 Embedded CS, ODT and CKE Routing Recommendation.  DDR2 Embedded CS, ODT and CKE Routing Recommendation.  DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology.  PCI Express Layout for Motherboard.  PCI Expr | 1  | Motherboard Stack Up, Stripline and Microstrip             | 18 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------------------------------------------------|----|

| 3 Single-ended Trace Parameters 4 Differential Trace Dimensions. 5 x64 DDR Memory Configuration. 6 x72 DDR Memory Configuration. 7 DDR2 DIMM Source Synchronous Routing Recommendations 9 DDR2 DIMM DQS Lengths 8 DDR2 DIMM DQS Lengths 10 DDR2 DIMM Clock Routing Recommendations 11 DDR2 DIMM Clock Routing Recommendations 12 DDR2 DIMM Address/Command/Control Routing Recommendation 13 DDR2 DIMM Address/Command/Control Routing Recommendation. 14 DDR2 Embedded Source Synchronous Routing Recommendations 15 DDR2 Embedded DQ Lengths 16 DDR2 Embedded DQ Lengths 17 DDR2 Embedded DQ Lengths 18 DDR2 Embedded Clock Routing Recommendations 19 DDR2 Embedded Clock Routing Recommendations 10 DDR2 Embedded Clock Routing Recommendations 11 DDR2 Embedded Clock Routing Recommendations 12 DDR2 Embedded Clock Routing Recommendations 13 DDR2 Embedded Clock Routing Recommendations 14 DDR2 Embedded Clock Routing Recommendations 15 DDR2 Embedded Clock Routing Recommendation 16 DDR2 Embedded Clock Routing Recommendation 17 DDR2 Embedded CS, ODT and CKE Routing Recommendation 18 DDR2 Embedded CS, ODT and CKE Routing Recommendation 19 DDR2 Embedded CS, ODT and CKE Routing Recommendation 20 DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology 21 DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology 22 PCI Express Layout for A Motherboard 23 DRA2 Embedded CS, ODT and CKE Routing 24 PCI Express Layout for Iokck Routing 25 PCI Stribers Layout for Iokck Routing 26 PCI Express Layout for Clock Routing 27 PCI-X Initialization Pattern 28 PCI-X Initialization Pattern 29 PCI-X REQ#/GNT# Layout Guidelines 20 PCI-X REQ#/GNT# Layout Guidelines 21 DRA2 Embedded Clock Routing 20 PCI-X REQ#/GNT# Layout Guidelines 21 Layout Guidelines 22 PCI-X REQ#/GNT# Layout Guidelines 23 Layout Guidelines Solt Topology 24 Embedded Clock Routing 25 PCI-X REQ#/GNT# Layout Guidelines 26 PCI-X REQ#/GNT# Layout Guidelines 27 PCI-X REQ#/GNT# Layout Guidelines 28 Layout Guidelines Solt Topology 39 Gental Countrol Routing Guidelines Solt Topology 30 Countrol Recommendations  |    |                                                            |    |

| 4 Differential Trace Dimensions.  5 x64 DDR Memory Configuration.  6 x72 DDR Memory Configuration.  7 DDR2 DIMM Source Synchronous Routing Recommendations.  9 DDR2 DIMM DQS Lengths.  10 DDR2 DIMM DQ Lengths.  11 DDR2 DIMM Clock Routing Recommendations.  12 DDR2 DIMM Clock Routing Recommendations.  13 DDR2 DIMM Address/Command/Control Routing Recommendation.  14 DDR2 DIMM Address/Command Lengths.  15 DDR2 Embedded Source Synchronous Routing Recommendations.  16 DDR2 Embedded DQ Lengths.  17 DDR2 Embedded DQ Lengths.  18 DDR2 Embedded Clock Routing Recommendations.  19 DDR2 Embedded Clock Routing Recommendations.  10 DDR2 Embedded Clock Lengths.  10 DDR2 Embedded Clock Lengths.  10 DDR2 Embedded Address/Command/Control Routing Recommendation.  10 DDR2 Embedded Address/Compand/Control Routing Recommendation.  10 DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology.  21 DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology.  22 DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology.  23 DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology.  24 PCI Express Layout for Motherboard.  25 PCI Express Layout for Motherboard.  26 PCI Express Layout for Motherboard.  27 PCI/PCI-X Device Capability Reporting.  28 PCI-X Initialization Pattern.  29 PCI-MCI-X Red-Mc/NT Layout Guidelines.  20 PCI-X REO-Mc/NT Layout Guidelines.  30 PCI-X REO-Mc/NT Layout Guidelines.  31 PCI-X REO-Mc/NT Layout Guidelines.  32 PCI-X REO-Mc/NT Layout Guidelines.  33 MHz Single-Slot Topology.  34 Embedded 130 MHz Topology.  35 Mixed 130 MHz Topology.  36 Mixed 130 MHz Topology.  37 Embedded 100 MHz Topology.  38 Mixed 100 MHz Topology.  39 66 MHz Four Slot Topology.  40 Embedded 66 MHz Topology.  41 Mixed 66 MHz Topology.  42 PSI Routing Guideline Single Load.  43 Interpair (Between Pair) Spacing Requirements.  44 PBI Routing Guidelines for Two Loads.  45 PBI Routing Guidelines for Two Loads.  46 PBI Routing Guidelines for Two Loads.  47 Supply Voltages.  48 Customer Reference Board Layer Stackup.  50 Decoupling Recommendations.  51 Cu |    |                                                            |    |

| 5 x64 DDR Memory Configuration. 7 DDR2 DIMM Source Synchronous Routing Recommendations. 9 DDR2 DIMM DQS Lengths. 10 DDR2 DIMM DQS Lengths. 11 DDR2 DIMM Clock Routing Recommendations. 12 DDR2 DIMM Clock Routing Recommendations. 13 DDR2 DIMM Address/Command/Control Routing Recommendation. 14 DDR2 DIMM Address/Command/Control Routing Recommendation. 15 DDR2 DIMM Address/Command Lengths. 16 DDR2 Embedded DQ Lengths. 17 DDR2 Embedded DQ Lengths. 18 DDR2 Embedded DQ Lengths. 19 DDR2 Embedded Clock Routing Recommendations. 19 DDR2 Embedded Clock Routing Recommendations. 10 DDR2 Embedded Clock Routing Recommendation. 20 DDR2 Embedded Clock Routing Recommendation. 21 DDR2 Embedded Clock Routing Recommendation. 22 DDR2 Embedded Clock Routing Recommendation. 23 DDR2 Embedded CS, ODT and CKE Routing Recommendation. 24 DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology. 25 DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology. 26 PCI Express Layout for a Motherboard. 27 PCI PCI-X Device Capability Reporting. 28 PCI-X Initialization Pattern. 29 PCI Bus Frequency Encoding. 20 PCI-X RCQ#/GNT# Layout Guidelines. 20 PCI-X RCQ#/GNT# Layout Guidelines. 21 PCI-X RCQ#/GNT# Layout Guidelines. 22 PCI-X RCQ#/GNT# Layout Guidelines. 23 DCI-X RCQ#/GNT# Layout Guidelines. 24 PCI-X RCQ#/GNT# Layout Guidelines. 25 PCI-X RCQ#/GNT# Layout Guidelines. 26 PCI-X RCQ#/GNT# Layout Guidelines. 27 PCI-X RCQ#/GNT# Layout Guidelines. 28 PCI-X RCQ#/GNT# Layout Guidelines. 29 PCI-X RCQ#/GNT# Layout Guidelines. 20 PCI-X RCQ#/GNT# Layout Guidelines. 20 PCI-X RCQ#/GNT# Layout Guidelines. 21 PCI-X RCQ#/GNT# Layout Guidelines. 22 PCI-X RCQ#/GNT# Layout Guidelines. 23 Interpair (Between Pair) Spacing Requirements. 24 Embedded 130 MHz Topology. 25 Mixed 133 MHz Topology. 26 Embedded 66 MHz Topology. 27 Embedded 66 MHz Topology. 28 Embedded 67 Embedde |    |                                                            |    |

| 6 x72 DDR Memory Configuration. 7 DDR2 DIMM Source Synchronous Routing Recommendations. 9 DDR2 DIMM DQS Lengths. 8 DDR2 DIMM DQS Lengths. 10 DDR2 DIMM Clock Routing Recommendations. 11 DDR2 DIMM Clock Routing Recommendations. 12 DDR2 DIMM Clock Lengths. 13 DDR2 DIMM Address/Command/Control Routing Recommendation. 14 DDR2 EIMD Address/Command Lengths. 15 DDR2 EIMD Address/Command Lengths. 16 DDR2 Embedded DQ Lengths. 17 DDR2 Embedded DQ Lengths. 18 DDR2 Embedded Clock Routing Recommendations. 19 DDR2 Embedded Clock Routing Recommendations. 19 DDR2 Embedded Clock Lengths. 19 DDR2 Embedded Clock Lengths. 10 DDR2 Embedded Clock Lengths. 10 DDR2 Embedded CS, ODT and CKE Routing Recommendation. 10 DDR2 Embedded CS, ODT and CKE Routing Recommendation. 20 DDR2 Embedded CS, ODT and CKE Routing Recommendation. 21 DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology. 22 DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology. 23 DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology. 24 PCI Express Layout for a Motherboard. 25 PCI Express Layout for NotherboardAdapter Card Topology. 26 PCI Express Layout for Clock Routing. 27 PCI/PCI-X Device Capability Reporting. 28 PCI-X Initialization Pattern. 29 PCI Bus Frequency Encoding. 30 PCI-X Clock Layout Guidelines. 31 PCI-X REQ#/GNT# Layout Guidelines. 31 PCI-X REQ#/GNT# Layout Guidelines. 32 PCI-X REQ#/GNT# Layout Guidelines. 31 SI3 MHz Topology. 32 Embedded 133 MHz Topology. 33 Embedded 100 MHz Topology. 34 Embedded 134 MHz Topology. 35 Mixed 133 MHz Topology. 36 6M Mtz Four Slot Topology. 37 Embedded 166 MHz Topology. 38 Mixed 100 MHz Topology. 39 Embedded 166 MHz Topology. 40 Embedded 66 MHz Topology. 41 Embedded 166 MHz Topology. 42 SAS Compliant Guidelines for Two Loads. 43 PBI Routing Guideline For Two Loads. 44 PBI Routing Guideline For Two Loads. 45 PBI Routing Guideline For Two Loads. 46 PBI Routing Guideline For Three Loads. 47 Supply Voltages. 48 Customer Reference Board Voltage Planes. 49 Customer Reference Board Decoupling Example. 50 Decoupling Recom   |    |                                                            |    |

| DDR2 DIMM Source Synchronous Routing Recommendations DDR2 DIMM DQS Lengths DDR2 DIMM DQS Lengths DDR2 DIMM Clock Routing Recommendations DDR2 DIMM Clock Routing Recommendations DDR2 DIMM Clock Lengths DDR2 DIMM Address/Command/Control Routing Recommendation DDR2 DIMM Address/Command/Control Routing Recommendations DDR2 Embedded Source Synchronous Routing Recommendations DDR2 Embedded DQS Lengths DDR2 Embedded DQS Lengths DDR2 Embedded Clock Routing Recommendations DDR2 Embedded Clock Routing Recommendations DDR2 Embedded Clock Routing Recommendations DDR2 Embedded Address/Command/Control Routing Recommendation DDR2 Embedded Address/Command/Control Routing Recommendation DDR2 Embedded CS, ODT and CKE Routing Recommendation DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology PCI Express Layout for a Motherboard PCI Express Layout for Motherboard PCI Express Layout for Motherboard PCI Express Layout for Motherboard PCI-X Initialization Pattern PCI-X Initialization Pattern PCI-X Clock Layout Guidelines PCI-X Clock Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X Red#/GNT# Layout Guidelines | _  |                                                            |    |

| 9 DDR2 DIMM DQS Lengths 10 DDR2 DIMM Clock Routing Recommendations 11 DDR2 DIMM Clock Lengths 12 DDR2 DIMM Clock Lengths 13 DDR2 DIMM Address/Command/Control Routing Recommendation 14 DDR2 Embedded Source Synchronous Routing Recommendations 15 DDR2 Embedded DQ Lengths 16 DDR2 Embedded DQ Lengths 17 DDR2 Embedded DQS Lengths 18 DDR2 Embedded Clock Routing Recommendations 19 DDR2 Embedded Clock Routing Recommendations 10 DDR2 Embedded Clock Lengths 10 DDR2 Embedded Address/Command/Control Routing Recommendation 10 DDR2 Embedded Address/COM Lengths Topology 11 DDR2 Embedded CS, ODT and CKE Routing Recommendation 12 DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology 13 DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology 14 PCI Express Layout for Motherboard 15 PCI Express Layout for Motherboard 16 PCI Express Layout for Motherboard 17 PCI/PCI-X Device Capability Reporting 18 PCI-X Initialization Pattern 19 PCI Bus Frequency Encoding 19 PCI-X REQ#/GNT# Layout Guidelines 19 PCI-X REQ#/GNT# Layout Guidelines 10 PCI-X REQ#/GNT# Layout Guidelines 10 PCI-X REQ#/GNT# Layout Guidelines 11 DAIN TOPOlogy 12 Embedded 133 MHz Topology 13 Embedded 133 MHz Topology 14 Embedded 134 MHz Topology 15 Mixed 135 MHz Topology 16 MHz Two Slot Topology 17 Embedded 66 MHz Topology 18 Mixed 100 MHz Topology 19 Embedded 66 MHz Topology 10 Embedded 66 MHz Topology 10 Embedded 66 MHz Topology 11 Embedded 100 MHz Topology 12 SAS Compliant Guidelines Single Load 14 PBI Routing Guideline For Twe Loads 15 PBI Routing Guideline For Twe Loads 16 PBI Routing Guideline For Three Loads 17 Supply Voltages 18 Customer Reference Board Layer Stackup 19 Decoupling Recommendations 10 Customer Reference Board Layer Stackup 10 Decoupling Recommendations 11 Decoupling Recommendations 12 Doctore Reference Board Layer Stackup 15 Decoupling Recommendations 15 Customer Reference Board Layer Stackup 15 Decoupling Recommendations                                                                                                                                |    |                                                            |    |

| B DDR2 DIMM Clock Routing Recommendations  10 DDR2 DIMM Clock Lengths  11 DDR2 DIMM Address/Command/Control Routing Recommendation  12 DDR2 DIMM Address/Command Lengths  13 DDR2 Embedded Source Synchronous Routing Recommendations  14 DDR2 Embedded DQL Lengths  15 DDR2 Embedded DQS Lengths  16 DDR2 Embedded DQS Lengths  17 DDR2 Embedded Clock Routing Recommendations  18 DDR2 Embedded Clock Lengths  19 DDR2 Embedded Address/Command/Control Routing Recommendation  10 DDR2 Embedded Address/CMD Lengths Topology  21 DDR2 Embedded Address/CMD Lengths Topology  22 DDR2 Embedded CS, ODT and CKE Routing Recommendation  23 DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology  24 PCI Express Layout for Motherboard  25 PCI Express Layout for Motherboard  26 PCI Express Layout for Motherboard-Adapter Card Topology  27 PCI/PCI-X Device Capability Reporting  28 PCI-X Initialization Pattern  29 PCI Bus Frequency Encoding  30 PCI-X Clock Layout Guidelines  31 PCI-X REQ #/GNT# Layout Guidelines  32 PCI-X REQ #/GNT# Layout Guidelines  33 PCI-X REQ #/GNT# Layout Guidelines  34 PCI-X REQ #/GNT# Layout Guidelines  36 PCI-X REQ #/GNT# Layout Guidelines  37 PCI-X REQ #/GNT# Layout Guidelines  38 PCI-X Topology  49 Embedded 133 MHz Topology  40 Embedded 166 MHz Topology  41 Mixed 66 MHz Topology  42 SAS Compliant Guideline Single Load  43 PBI Routing Guideline Single Load  44 PBI Routing Guideline Single Load  45 PBI Routing Guideline Single Load  46 PBI Routing Guidelines For Twe Loads  47 Supply Voltages  48 Customer Reference Board Voltage Planes  49 Customer Reference Board Layer Stackup  50 Decoupling Recommendations  51 Customer Reference Board Layer Stackup  52 Design and Debug Checklist.                                                                                                                                                                                                                                                                                                                                                          |    |                                                            |    |

| DDR2 DIMM Clock Routing Recommendations  DDR2 DIMM Address/Command/Control Routing Recommendation.  DDR2 DIMM Address/Command Lengths  DDR2 Embedded Source Synchronous Routing Recommendations  DDR2 Embedded DQ Lengths  DDR2 Embedded Clock Routing Recommendations  DDR2 Embedded Address/Command/Control Routing Recommendation  DDR2 Embedded Address/CMD Lengths Topology  DDR2 Embedded CS, ODT and CKE Routing Recommendation  DDR2 Embedded CS, ODT and CKE Lengths Dalay Chain Topology  DDR2 Embedded CS, ODT and CKE Lengths Dalay Chain Topology  PCI Express Layout for Motherboard  PCI Express Layout for Motherboard  PCI Express Layout for Motherboard Adapter Card Topology  PCI CI Express Layout for Motherboard Adapter Card Topology  PCI PCI-X Device Capability Reporting  PCI-X Initialization Pattern  PCI Bus Frequency Encoding  PCI-X Clock Layout Guidelines  PCI-X REQ #/GNT# Layout Guidelines  1 133 M1z Single-Slot Topology  Embedded 133 M1z Topology  Mixed 133 M1z Topology  Mixed 133 M1z Topology  66 M1z Four Slot Topology  Embedded 100 M1z Topology  Mixed 100 M1z Topology  SAS Compliant Guidelines For Two Loads  PBI Routing Guideline Single Load  PBI Routing Guideline For Three Loads  PBI Routing Guidelines For Two Loads  PBI Routing Guidelines For Tree Loads  Customer Reference Board Layer Stackup  Decoupling Recommendations  Customer Reference Board Layer Stackup  Decoupling Recommendations  Customer Reference Board Layer Stackup  Decoupling Recommendations                                                                                                                                                                               |    |                                                            |    |

| DDR2 DIMM Address/Command/Control Routing Recommendation  DDR2 DIMM Address/Command Lengths  DDR2 Embedded Source Synchronous Routing Recommendations.  DDR2 Embedded DQ Lengths  DDR2 Embedded DQ Lengths  DDR2 Embedded Clock Routing Recommendations.  DDR2 Embedded Clock Routing Recommendations.  DDR2 Embedded Clock Routing Recommendations.  DDR2 Embedded Clock Lengths.  DDR2 Embedded Clock Lengths.  DDR2 Embedded Address/CMD Lengths Topology  DDR2 Embedded CS, ODT and CKE Routing Recommendation.  DDR2 Embedded CS, ODT and CKE Routing Recommendation.  DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology.  DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology.  PCI Express Layout for A Motherboard.  PCI Express Layout for Motherboard-Adapter Card Topology.  PCI Express Layout for Clock Routing.  PCI-YCI-X Device Capability Reporting.  PCI-X Initialization Pattern.  PCI Bus Frequency Encoding.  PCI-X REQ #/GNT# Layout Guidelines.  PCI-X REQ #/GNT# Layout  | _  |                                                            |    |

| DDR2 DIMM Address/Command/Control Routing Recommendation DDR2 Embedded Source Synchronous Routing Recommendations DDR2 Embedded DQL Lengths DDR2 Embedded DQS Lengths DDR2 Embedded Clock Routing Recommendations  DDR2 Embedded Clock Routing Recommendations  DDR2 Embedded Clock Lengths  DDR2 Embedded Clock Lengths  DDR2 Embedded Address/CMD Lengths Topology  DDR2 Embedded CS, ODT and CKE Routing Recommendation  DDR2 Embedded CS, ODT and CKE Routing Recommendation  DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology  DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology  PDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology  PCI Express Layout for Anotherboard  PCI Express Layout for Motherboard-Adapter Card Topology.  PCI Express Layout for Motherboard-Adapter Card Topology.  PCI FX Initialization Pattern  PCI/PCI-X Device Capability Reporting  PCI-X Clock Layout Guidelines  PCI-X REQ #/GNT# Layout Guidelines.   |    |                                                            |    |

| DDR2 Embedded Source Synchronous Routing Recommendations.  DDR2 Embedded DQ Lengths  DDR2 Embedded DQ Lengths  DDR2 Embedded DQS Lengths  DDR2 Embedded Clock Routing Recommendations.  DDR2 Embedded Clock Lengths  DDR2 Embedded Clock Lengths  DDR2 Embedded Address/Command/Control Routing Recommendation  DDR2 Embedded Address/CMD Lengths Topology  DDR2 Embedded CS, ODT and CKE Routing Recommendation  DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology  DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology  PCI Express Layout for a Motherboard.  PCI Express Layout for Motherboard-Adapter Card Topology.  PCI Express Layout for Motherboard-Adapter Card Topology.  PCI Express Layout for Cock Routing  PCI-X Initialization Pattern.  PCI Bus Frequency Encoding  PCI-X Clock Layout Guidelines.  PCI-X REQ #/GNT# Layo |    |                                                            |    |

| DDR2 Embedded DQ Lengths DDR2 Embedded DQS Lengths DDR2 Embedded DQS Lengths DDR2 Embedded Clock Routing Recommendations DDR2 Embedded Clock Lengths DDR2 Embedded Clock Lengths DDR2 Embedded Address/Command/Control Routing Recommendation DDR2 Embedded Address/CMD Lengths Topology DDR2 Embedded CS, ODT and CKE Routing Recommendation DDR2 Embedded CS, ODT and CKE Routing Recommendation DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology PCI Express Layout for a Motherboard PCI Express Layout for Rotherboard-Adapter Card Topology PCI Express Layout for Clock Routing PCI-X Initialization Pattern PCI Bus Frequency Encoding PCI-X Initialization Pattern PCI Bus Frequency Encoding PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines DRIAS Mixe Single-Slot Topology Mixed 133 MHz Topology Mixed 133 MHz Topology Mixed 133 MHz Topology Mixed 100 MHz Topology Mixed 66 MHz Topology Mixed 66 MHz Topology Mixed 66 MHz Topology PBI Routing Guidelines Single Load PBI Routing Guidelines For Two Loads PBI Routing Guidelines For Two Loads PBI Routing Guidelines For Two Loads PBI Routing Guidelines For Three Loads Supply Voltages Customer Reference Board Voltage Planes Customer Reference Board Voltage Planes Customer Reference Board Decoupling Example Decoupling Recommendations Customer Reference Board Decoupling Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |                                                            |    |

| 15 DDR2 Embedded DQ Lengths 16 DDR2 Embedded DQS Lengths 17 DDR2 Embedded Clock Routing Recommendations 18 DDR2 Embedded Clock Lengths 19 DDR2 Embedded Address/Command/Control Routing Recommendation 20 DDR2 Embedded Address/CMD Lengths Topology 21 DDR2 Embedded CS, ODT and CKE Routing Recommendation 22 DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology 23 DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology 24 PCI Express Layout for a Motherboard 25 PCI Express Layout for Motherboard-Adapter Card Topology 26 PCI Express Layout for Motherboard-Adapter Card Topology 27 PCI-X Device Capability Reporting 28 PCI-X Initialization Pattern 29 PCI Bus Frequency Encoding 30 PCI-X Clock Layout Guidelines 31 PCI-X REQ#/GNT# Layout Guidelines 32 PCI-X REQ#/GNT# Layout Guidelines 33 133 MHz Single-Slot Topology 34 Embedded 133 MHz Topology 35 Mixed 133 MHz Topology 36 100 MHz Topology 37 Embedded 100 MHz Topology 38 Mixed 100 MHz Topology 40 Embedded 66 MHz Topology 41 Mixed 66 MHz Topology 42 SAS Compliant Guidelines 43 Interpair (Between Pair) Spacing Requirements 44 PBI Routing Guideline Single Load 45 PBI Routing Guideline For Two Loads 46 PBI Routing Guideline For Two Loads 47 Supply Voltages 48 Customer Reference Board Voltage Planes 49 Customer Reference Board Voltage Planes 40 Customer Reference Board Decoupling Example 50 Decoupling Recommendations 51 Customer Reference Board Decoupling Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                                                            |    |

| 16 DDR2 Embedded DQS Lengths 17 DDR2 Embedded Clock Routing Recommendations 18 DDR2 Embedded Clock Lengths 19 DDR2 Embedded Address/Command/Control Routing Recommendation 20 DDR2 Embedded Address/CMD Lengths Topology 21 DDR2 Embedded CS, ODT and CKE Routing Recommendation 22 DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology 23 DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology 24 PCI Express Layout for a Motherboard 25 PCI Express Layout for Motherboard-Adapter Card Topology 26 PCI Express Layout for Routing 27 PCI/PCI-X Device Capability Reporting 28 PCI-X Initialization Pattern 29 PCI-X Initialization Pattern 29 PCI-X Clock Layout Guidelines 30 PCI-X Clock Layout Guidelines 31 PCI-X REQ#/GNT# Layout Guidelines 32 PCI-X REQ#/GNT# Layout Guidelines 33 133 MHz Single-Slot Topology 34 Embedded 133 MHz Topology 35 Mixed 133 MHz Topology 36 100 MHz Two Slot Topology 37 Embedded 100 MHz Topology 38 Mixed 100 MHz Topology 40 Embedded 66 MHz Topology 41 Mixed 66 MHz Topology 42 SAS Compliant Guidelines 43 Interpair (Between Pair) Spacing Requirements 44 PBI Routing Guideline Single Load 45 PBI Routing Guideline For Three Loads 46 PBI Routing Guideline For Three Loads 47 Supply Voltages 48 Customer Reference Board Voltage Planes 49 Customer Reference Board Voltage Planes 50 Decoupling Recommendations 51 Customer Reference Board Decoupling Example 51 Design and Debug Checklist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |                                                            |    |

| DDR2 Embedded Clock Routing Recommendations DDR2 Embedded Clock Lengths DDR2 Embedded Address/Command/Control Routing Recommendation DDR2 Embedded Address/CMD Lengths Topology DDR2 Embedded CS, ODT and CKE Routing Recommendation DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology PDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology PDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology PCI Express Layout for Motherboard. PCI Express Layout for Motherboard. PCI Express Layout for Motherboard PCI Express Layout for Motherboard PCI Express Layout for Clock Routing PCI Express Layout for Clock Routing PCI-X Device Capability Reporting. PCI-X Initialization Pattern PCI Bus Frequency Encoding PCI-X Clock Layout Guidelines PCI-X REQ #/GNT# Layout Guidelines For Topology PCI-X REQ #/GNT# Layout Guidelines For Two Loads PCI-X REQ #/GNT# Layout Guideline For Three Loads PCI-X REQ #/GNT# Layout Guidelines For Two Loads PCI-X REQ #/GNT# Layou |    |                                                            |    |

| DDR2 Embedded Clock Lengths DDR2 Embedded Address/Command/Control Routing Recommendation DDR2 Embedded Address/CMD Lengths Topology DDR2 Embedded CS, ODT and CKE Routing Recommendation DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology PDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology PDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology PCI Express Layout for Motherboard. PCI Express Layout for Motherboard-Adapter Card Topology. PCI Express Layout for Clock Routing PCI-X Initialization Pattern PCI Bus Frequency Encoding PCI-X Clock Layout Guidelines PCI-X REQ#GNT# Layout Guidelines PCI-X Encoded 133 MHz Topology Mixed 133 MHz Topology Mixed 100 MHz Topology Embedded 100 MHz Topology Embedded 66 MHz Topology Mixed 66 MHz Topology PCI-X REQ#GNT# Guidelines Interpair (Between Pair) Spacing Requirements PBI Routing Guideline Single Load PBI Routing Guideline Sor Two Loads PBI Routing Guideline Sor Two Loads PBI Routing Guideline For Three Loads Customer Reference Board Voltage Planes Customer Reference Board Voltage Planes Customer Reference Board Decoupling Example Decoupling Recommendations Customer Reference Board Decoupling Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |                                                            |    |

| DDR2 Embedded Address/Command/Control Routing Recommendation DDR2 Embedded Address/CMD Lengths Topology DDR2 Embedded CS, ODT and CKE Routing Recommendation  DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology  PDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology  PCI Express Layout for A Motherboard-Adapter Card Topology.  PCI Express Layout for Motherboard-Adapter Card Topology.  PCI Express Layout for Clock Routing PCI-X Device Capability Reporting.  PCI-X Initialization Pattern  PCI Bus Frequency Encoding PCI-X Clock Layout Guidelines.  PCI-X REQ#/GNT# Layout Guidelines.  PCI-X REQ#/GNT# Layout Guidelines.  PCI-X REQ#/GNT# Layout Guidelines.  PCI-X REQ#/GNT# Layout Guidelines.  DCI-X REQ#/GNT# Layout Guidel |    |                                                            |    |

| DDR2 Embedded Address/CMD Lengths Topology DDR2 Embedded CS, ODT and CKE Routing Recommendation DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology PCI Express Layout for a Motherboard. PCI Express Layout for Motherboard-Adapter Card Topology. PCI Express Layout for Clock Routing PCI-X Express Layout for Clock Routing PCI-Y PCI-X Device Capability Reporting. PCI-X Initialization Pattern. PCI Bus Frequency Encoding PCI-X Clock Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines SI Robedded 133 MHz Topology SMixed 100 MHz Topology SAS Compliant Guidelines SAS Compliant Guidelines SAS Compliant Guidelines SAS Compliant Guidelines Single Load PBI Routing Guideline For Three Loads Supply Voltages Customer Reference Board Voltage Planes Customer Reference Board Decoupling Example Decoupling Recommendations Customer Reference Board Decoupling Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |                                                            |    |

| DDR2 Embedded CS, ODT and CKE Routing Recommendation DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology PCI Express Layout for a Motherboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19 |                                                            |    |

| DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology PCI Express Layout for a Motherboard. PCI Express Layout for Motherboard-Adapter Card Topology PCI Express Layout for Clock Routing PCI Express Layout for Clock Routing PCI-X Device Capability Reporting. PCI-X Initialization Pattern PCI Bus Frequency Encoding. PCI-X Clock Layout Guidelines. PCI-X REQ#/GNT# Layout Guidelines. PCI-X REQ#/GNT# Layout Guidelines. PCI-X REQ#/GNT# Layout Guidelines. SI Rimedded 133 MHz Topology. SMixed 133 MHz Topology. SMixed 100 MHz Topology. SMixed 100 MHz Topology. SMixed 100 MHz Topology. SMixed 100 MHz Topology. SAS Compliant Guidelines. SAS Compliant Guidelines. Interpair (Between Pair) Spacing Requirements. SAS Compliant Guideline Single Load. PBI Routing Guideline Single Load. PBI Routing Guideline For Three Loads. PBI Routing Guideline For Three Loads. Supply Voltages Customer Reference Board Voltage Planes. Customer Reference Board Layer Stackup. Decoupling Recommendations. Customer Reference Board Decoupling Example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20 |                                                            |    |

| DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology PCI Express Layout for a Motherboard. PCI Express Layout for Motherboard-Adapter Card Topology. PCI Express Layout for Clock Routing PCI Express Layout for Clock Routing PCI Express Layout for Clock Routing PCI Express Layout Ground For Clock Routing PCI Express Layout Guldeling. PCI-X Initialization Pattern PCI Bus Frequency Encoding. PCI-X Clock Layout Guidelines. PCI-X REQ#/GNT# Layout Guidelines. PCI-X RE | 21 | DDR2 Embedded CS, ODT and CKE Routing Recommendation       | 40 |

| PCI Express Layout for a Motherboard PCI Express Layout for Motherboard-Adapter Card Topology PCI Express Layout for Clock Routing PCI-X Device Capability Reporting PCI-Y Device Capability Reporting PCI-X Initialization Pattern PCI Bus Frequency Encoding PCI-X Clock Layout Guidelines PCI-X REQ#/GNT# Layout Guid | 22 | DDR2 Embedded CS, ODT and CKE Lengths Balanced Topology    | 41 |

| PCI Express Layout for Motherboard-Adapter Card Topology. PCI Express Layout for Clock Routing PCI-PCI-X Device Capability Reporting. PCI-X Initialization Pattern PCI Bus Frequency Encoding PCI-X Clock Layout Guidelines. PCI-X REQ#/GNT# Layout Guidelines. PCI-X | 23 | DDR2 Embedded CS, ODT and CKE Lengths Daisy Chain Topology | 42 |

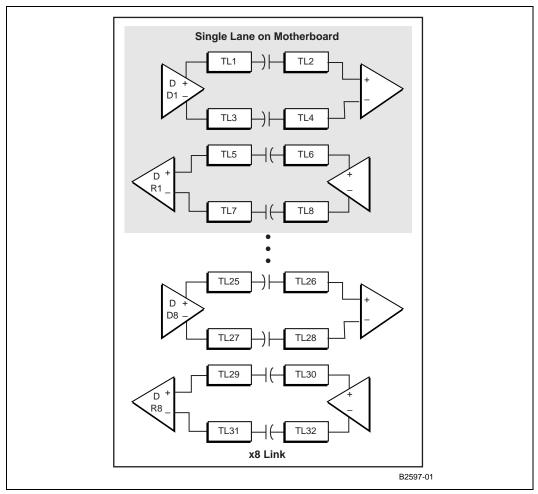

| PCI Express Layout for Motherboard-Adapter Card Topology. PCI Express Layout for Clock Routing PCI-PCI-X Device Capability Reporting. PCI-X Initialization Pattern PCI Bus Frequency Encoding PCI-X Clock Layout Guidelines. PCI-X REQ#/GNT# Layout Guidelines. PCI-X | 24 | PCI Express Layout for a Motherboard                       | 48 |

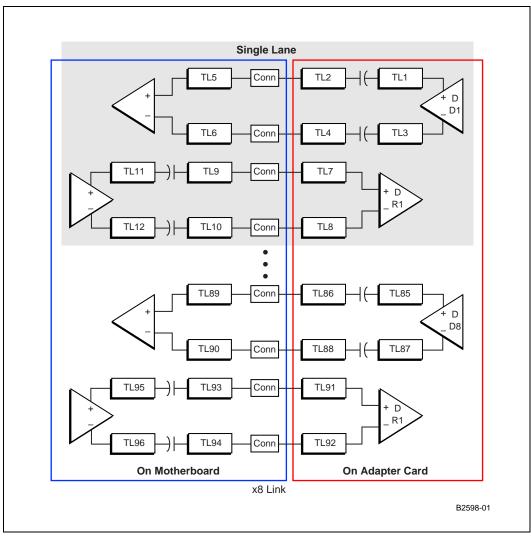

| PCI Express Layout for Clock Routing PCI/PCI-X Device Capability Reporting. PCI-X Initialization Pattern. PCI Bus Frequency Encoding PCI-X Clock Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines Instance of the Mixed Signature of Si | 25 |                                                            |    |

| PCI-Y Initialization Pattern PCI Bus Frequency Encoding PCI-X Clock Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines REQ#/GNT# Layout Guidelines Rembedded 133 MHz Topology Rembedded 133 MHz Topology Rembedded 134 MHz Topology Rembedded 100 MHz Topology Rembedded 100 MHz Topology Rembedded 100 MHz Topology Rembedded 66 MHz Topology Requirements Rembedded 67 MHz Routing Guidelines Respectively Requirements Reference Board Load Respectively Rembedded Repuirements Respectively Rembedded Repuirements Respectively Rembedded Repuirements Respectively Rembedded Repuirements Respectively Respectively Rembedded Repuirements Respectively Rembedded Rembedded Repuirements Respectively Rembedded  | 26 |                                                            |    |

| PCI-X Initialization Pattern PCI Bus Frequency Encoding PCI-X Clock Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines I33 133 MHz Single-Slot Topology Embedded 133 MHz Topology Imbedded 133 MHz Topology Index Ind | 27 |                                                            |    |

| PCI Bus Frequency Encoding PCI-X Clock Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines REMEMED AND SINGLE-Slot Topology REMED AND SINGLE-Slot Topology REMED AND SINGLE-Slot Topology RIVED AND SINGLE-Slot Topology RIVED AND SINGLE-SLOT TOPOLOGY REMED AND SINGLE-SLOT TOPOLOGY REMED AND SINGLE-SLOT TOPOLOGY REMED AND SINGLE-SLOT  | 28 |                                                            |    |

| PCI-X Clock Layout Guidelines PCI-X REQ#/GNT# Layout Guidelines PCI-X REQ# | 29 |                                                            |    |

| PCI-X REQ#/GNT# Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30 |                                                            |    |

| PCI-X REQ#/GNT# Layout Guidelines  133 133 MHz Single-Slot Topology  34 Embedded 133 MHz Topology  35 Mixed 133 MHz Topology  36 100 MHz Two Slot Topology  37 Embedded 100 MHz Topology  38 Mixed 100 MHz Topology  39 66 MHz Four Slot Topology  40 Embedded 66 MHz Topology  41 Mixed 66 MHz Topology  42 SAS Compliant Guidelines  43 Interpair (Between Pair) Spacing Requirements  44 PBI Routing Guideline Single Load  45 PBI Routing Guidelines for Two Loads  46 PBI Routing Guideline for Three Loads  47 Supply Voltages  48 Customer Reference Board Voltage Planes  49 Customer Reference Board Layer Stackup  50 Decoupling Recommendations  51 Customer Reference Board Decoupling Example  52 Design and Debug Checklist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                                                            |    |

| 133 MHz Single-Slot Topology 34 Embedded 133 MHz Topology 35 Mixed 133 MHz Topology 36 100 MHz Two Slot Topology 37 Embedded 100 MHz Topology 38 Mixed 100 MHz Topology 39 66 MHz Four Slot Topology 40 Embedded 66 MHz Topology 41 Mixed 66 MHz Topology 42 SAS Compliant Guidelines 43 Interpair (Between Pair) Spacing Requirements 44 PBI Routing Guideline Single Load 45 PBI Routing Guideline for Three Loads 46 PBI Routing Guideline for Three Loads 47 Supply Voltages 48 Customer Reference Board Voltage Planes 49 Customer Reference Board Layer Stackup 50 Decoupling Recommendations 51 Customer Reference Board Decoupling Example 52 Design and Debug Checklist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |                                                            |    |

| ### Topology ### T |    |                                                            |    |

| Mixed 133 MHz Topology  100 MHz Two Slot Topology  Embedded 100 MHz Topology  Mixed 100 MHz Topology  Embedded 66 MHz Topology  Embedded 66 MHz Topology  Mixed 66 MHz Topology  Interpair (Between Pair) Spacing Requirements  PBI Routing Guideline Single Load  PBI Routing Guidelines for Two Loads  PBI Routing Guideline for Three Loads  Customer Reference Board Voltage Planes  Customer Reference Board Layer Stackup  Decoupling Recommendations  Customer Reference Board Decoupling Example  Design and Debug Checklist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |                                                            |    |

| 100 MHz Two Slot Topology 37 Embedded 100 MHz Topology 38 Mixed 100 MHz Topology 39 66 MHz Four Slot Topology 40 Embedded 66 MHz Topology 41 Mixed 66 MHz Topology 42 SAS Compliant Guidelines 43 Interpair (Between Pair) Spacing Requirements 44 PBI Routing Guideline Single Load 45 PBI Routing Guidelines for Two Loads 46 PBI Routing Guideline for Three Loads 47 Supply Voltages 48 Customer Reference Board Voltage Planes 49 Customer Reference Board Layer Stackup 50 Decoupling Recommendations 51 Customer Reference Board Decoupling Example 52 Design and Debug Checklist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |                                                            |    |

| 37 Embedded 100 MHz Topology 38 Mixed 100 MHz Topology 39 66 MHz Four Slot Topology 40 Embedded 66 MHz Topology 41 Mixed 66 MHz Topology 42 SAS Compliant Guidelines 43 Interpair (Between Pair) Spacing Requirements 44 PBI Routing Guideline Single Load 45 PBI Routing Guidelines for Two Loads 46 PBI Routing Guideline for Three Loads 47 Supply Voltages 48 Customer Reference Board Voltage Planes 49 Customer Reference Board Layer Stackup 50 Decoupling Recommendations 51 Customer Reference Board Decoupling Example 52 Design and Debug Checklist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |                                                            |    |

| Mixed 100 MHz Topology  66 MHz Four Slot Topology  Umbedded 66 MHz Topology  Mixed 66 MHz Topology  SAS Compliant Guidelines  Interpair (Between Pair) Spacing Requirements  PBI Routing Guideline Single Load  PBI Routing Guidelines for Two Loads  PBI Routing Guideline for Three Loads  Customer Reference Board Voltage Planes  Customer Reference Board Layer Stackup  Decoupling Recommendations  Customer Reference Board Decoupling Example  Design and Debug Checklist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |                                                            |    |

| 39 66 MHz Four Slot Topology 40 Embedded 66 MHz Topology 41 Mixed 66 MHz Topology 42 SAS Compliant Guidelines 43 Interpair (Between Pair) Spacing Requirements 44 PBI Routing Guideline Single Load 45 PBI Routing Guidelines for Two Loads 46 PBI Routing Guideline for Three Loads 47 Supply Voltages 48 Customer Reference Board Voltage Planes 49 Customer Reference Board Layer Stackup 50 Decoupling Recommendations 51 Customer Reference Board Decoupling Example 52 Design and Debug Checklist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                                                            |    |