# **External Storage Design**

Customer Reference Board Manual for 8134x I/O Processors

September 2006

Order Number: 315057-001US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, Dialogic, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX2, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetBurst, Intel NetBurst, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel VPro, Intel XScale, IPLink, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2006, Intel Corporation. All Rights Reserved.

## Contents

| 1.0      | Introduction                                                                                                                     |    |

|----------|----------------------------------------------------------------------------------------------------------------------------------|----|

|          | <ol> <li>Document Purpose and Scope</li> <li>Product Descriptions</li> </ol>                                                     |    |

|          | <ul><li>1.2 Product Descriptions</li><li>1.3 Using this Manual</li></ul>                                                         |    |

|          | 1.4 Getting Support                                                                                                              |    |

| 2.0      | Customer Reference Board Features                                                                                                | 11 |

|          | 2.1 81348 I/O Processor Features                                                                                                 |    |

|          | 2.2 External Storage Design CRB Features                                                                                         |    |

| 3.0      | Getting Started                                                                                                                  |    |

|          | <ul><li>3.1 Visual Inspection</li><li>3.2 Hardware Requirements</li></ul>                                                        |    |

|          | 3.3 Set-up and Configuration                                                                                                     |    |

|          | 3.4 Communicating with the CRB                                                                                                   |    |

| 4.0      | Using the CRB as a Software Development Platform                                                                                 | 17 |

|          | 4.1 Third Party Software Support                                                                                                 | 17 |

|          | 4.2 Software Developer Reference Information                                                                                     | 17 |

| 5.0      | Hardware/Architecture Reference                                                                                                  |    |

|          | 5.1 Memory Subsystem                                                                                                             |    |

|          | <ul><li>5.2 Connectors</li><li>5.3 Storage Clock</li></ul>                                                                       |    |

|          | 5.4 PCI Express Clock                                                                                                            |    |

|          | 5.5 Resetting the Board                                                                                                          |    |

|          | 5.6 Switch and Jumper Settings                                                                                                   |    |

|          | 5.7 GPIOs<br>5.8 Audio Buzzer                                                                                                    |    |

|          | 5.9 LEDs                                                                                                                         |    |

| Α        | Advanced Redboot Commands                                                                                                        | 34 |

|          | A.1 Removing the "+FLASH configuration checksum error or invalid key" message                                                    | 35 |

|          | A.2 Rebuilding RedBoot                                                                                                           |    |

|          | <ul><li>A.3 Using RedBoot to Update the RedBoot Image</li><li>A.4 Using RedBoot to Update the Transport Firmware Image</li></ul> |    |

|          | A.5 Initialize the Flash File System                                                                                             |    |

|          | A.6 Display the Current File System in Flash                                                                                     |    |

| в        | Troubleshooting and FAQ                                                                                                          | 45 |

|          | B.1 Common Problems and Possible Solutions                                                                                       |    |

|          | B.2 Frequently Asked Questions                                                                                                   | 45 |

| С        | Bill of Materials                                                                                                                | 46 |

|          | C.1 Key Components<br>C.2 Complete Bill of Materials                                                                             |    |

| <b>D</b> |                                                                                                                                  |    |

| D        | Schematics                                                                                                                       |    |

| E        | Intel® C++ Software Development Tool Suite 2.0 Tutorial                                                                          |    |

|          | E.1 Introduction<br>E.2 Setup                                                                                                    |    |

|          | E.3 New Project Setup                                                                                                            |    |

|          | E.4 RedBoot*                                                                                                                     | 52 |

|          | <ul><li>E.5 Flashing with JTAG</li><li>E.6 Building an Executable File</li></ul>                                                 |    |

|          |                                                                                                                                  | 54 |

|   | E.7  | Touring Some of the Debugger Features       | 54 |

|---|------|---------------------------------------------|----|

|   | E.8  | The Configuration Files behind the GUI      | 56 |

|   | E.9  | Compiling with a makefile                   | 56 |

|   | E.10 | Conclusion                                  | 56 |

| F | Acce | lerated Technology's Nucleus Edge* Tutorial | 58 |

|   | F.1  | Introduction                                | 58 |

|   | F.2  | Purpose                                     | 58 |

|   | F.3  | Setup                                       | 59 |

|   | F.4  | New Project Setup                           | 61 |

|   | F.5  | RedBoot                                     | 62 |

|   | F.6  | Flash Programming                           | 63 |

|   | F.7  | Building an Executable File                 | 64 |

|   | F.8  | Launching and Configuring the Debugger      | 65 |

|   | F.9  | Touring Some of the Debugger Features       | 66 |

|   | F.10 | Compiling with a makefile                   |    |

|   | F.11 | Conclusion                                  | 68 |

|   |      |                                             |    |

## **Figures**

| 1 | External Storage Design CRB                           | 12 |

|---|-------------------------------------------------------|----|

|   | JTAG Adapter                                          |    |

| 3 | Redboot Diagnostics Command and Hardware Test Listing | 19 |

| 4 | External Storage Design CRB Block Diagram             | 24 |

|   | External Storage Design CRB Layout                    |    |

|   | JTAG Port Pin-out                                     |    |

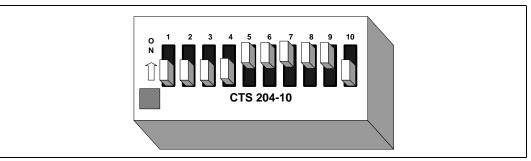

| 7 | DIP Switch SW2G1 10-Position Default Switch Settings  | 30 |

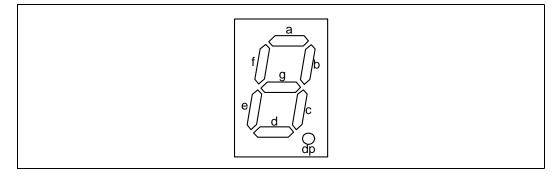

| 8 | Seven-Segment Display                                 | 32 |

|   |                                                       |    |

## **Tables**

| 1  | 8134x I/O Processors Related Documentation List               | 8   |

|----|---------------------------------------------------------------|-----|

| 2  | Terms and Definitions                                         |     |

| 3  | Electronic Information                                        |     |

| 4  | 81348 I/O Processor Features                                  | .11 |

| 5  | External Storage Design CRB Features                          | .13 |

| 6  | Software Tools Vendors and Operating Systems                  | .17 |

| 7  | Redboot Hardware Tests                                        | .19 |

| 8  | Peripheral Bus Memory Map                                     | .20 |

| 9  | RedBoot* Memory Map                                           | .21 |

| 10 | BAT_STAT Register Definition                                  | .26 |

| 11 | PROD_CODE Register Definition                                 |     |

| 12 | BOARD_STEPPING Register Definition                            | .27 |

| 13 | CPLD_FW Register Definition                                   | .27 |

| 14 | Ethernet Connector LED States                                 |     |

| 15 | SW2G1 Default Switch Position Descriptions                    | .30 |

| 16 | External Storage Design CRB Configuration Jumper Descriptions | .31 |

| 17 | BUZZER_CTRL Register                                          | .31 |

| 18 | DISCRETE_LED Register                                         | .31 |

| 19 | SEVEN_SEG_LED Register                                        | .32 |

| 20 | Component Reference                                           |     |

## **Revision History**

| Date           | Revision | Description     |

|----------------|----------|-----------------|

| September 2006 | 001      | Initial release |

## 1.0 Introduction

## 1.1 Document Purpose and Scope

This document describes the External Storage Design Customer Reference Board for 8134x I/O Processors (hereafter referred to as CRB or External Storage Design CRB). The External Storage Design CRB is a development and evaluation platform intended to enable rapid development of hardware and software applications.

This document tells you how to install the board in a server system and establish connections between the CRB and a separate system. Instructions are provided for attaching software debug hardware to the JTAG port on the CRB and loading software into the flash memory or CPLD. You can also use this manual as a reference when you are creating boards for your own custom applications.

This document assumes that you are familiar with installing and using computer boards and drivers, and that you are familiar with industry or Intel standards such as PCI-X, PCI Express, Serial Attached SCSI (SAS) on the 81348 I/O Processor only, JTAG, etc.

Common uses of the CRB development kit include:

- Software Development The board comes pre-loaded with a modified version of Red Hat, Inc.'s RedBoot\* embedded bootstrap and debug environment (this is often referred to as a "bootloader"). RedBoot provides a bootstrap environment, including network downloading and debugging. It also provides a simple flash file system for boot images.

- Software Debug The 8134x processor supports source level software debugging through the use of JTAG hardware and either Intel's XDB or Accelerated Technology, Inc.'s Edge\* debugger applications. See Appendix E or Appendix F for tutorials on using these tools.

- Reference Design This document can also be used as a reference by designers creating boards for custom applications. A high level Bill of Materials is included in this document and schematics are available in a separate document on Intel's Web site.

- *Note:* The design for the External Storage Design CRB does not fully comply with the specifications included in the product Design Guides. When using the CRB as a reference design, specifications in the Design Guide take precedence over anything included in the External Storage Design CRB schematics.

## 1.2 Product Descriptions

The products available from Intel in the 8134x family include:

- Intel® 81348 I/O Processor-based host bus adapter with 8-port SAS/SATA controller.

- Intel® 81341 I/O Processor-based host bus adapter with one processing core.

- Intel® 81342 I/O Processor-based host bus adapter with two processing cores.

- *Note:* Certain information in this manual applies only to specific versions of the product set. The instances in the manual where only specific versions apply are labeled appropriately.

## 1.3 Using this Manual

"Customer Reference Board Features" on page 11 provides an overview of the board and processor features.

"Getting Started" on page 14 describes how to unpack and set up your board for use as a development platform.

"Using the CRB as a Software Development Platform" on page 17 provides reference information for software programmers.

"Hardware/Architecture Reference" on page 24 provides reference material for designers intending to use their package as an example on which to base a custom or derivative design.

## 1.3.1 Related Documents

#### Table 1. 8134x I/O Processors Related Documentation List

| Document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Intel Order Number<br>(or SIG URL)           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Intel® 81348 I/O Processor Developer's Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 315036-001                                   |

| Intel® 81341 and Intel® 81342 I/O Processor Developer's Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 315037-001                                   |

| Intel® 81348 I/O Processor Datasheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 315038-001                                   |

| Intel® 81341 and Intel® 81342 I/O Processor Datasheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 315039-001                                   |

| Intel® 81348 I/O Processor Design Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 315053-001                                   |

| Intel® 81341 and Intel® 81342 I/O Processor Design Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 315054-001                                   |

| Intel® 81348 I/O Processor Specification Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 315041-001                                   |

| Intel® 81341 and Intel® 81342 I/O Processor Specification Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 315042-001                                   |

| Intel <sup>®</sup> Flash Recovery Utility (FRU) Reference Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 274071                                       |

| External Storage Design Schematics for Intel(R) 8134x I/O Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 315366-001                                   |

| IEEE Standard Test Access Port and Boundary-Scan Architecture (IEEE JTAG-1149.1-<br>1990)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | http://www.ieee.org                          |

| PCI Local Bus Specification, Revision 2.3 - PCI Special Interest GroupPCI Express Specification, Revision 1.0a - PCI Special Interest GroupPCI Express Base Specification 1.0a - PCI Special Interest GroupPCI Express Card Electromechanical Specification 1.0a - PCI Special Interest GroupPCI Local Bus Specification, Revision 2.3 - PCI Special Interest GroupPCI-X Specification, Revision 1.0b - PCI Special Interest GroupPCI Bus Power Management Interface Specification, Revision 1.1 - PCI SpecialInterest GroupPCI Bus Hot-Plug Specification, Revision 1.1 - PCI Special Interest Group | http://<br>www.pcisig.com/<br>specifications |

## 1.3.2 Terms Used in this Document

### Table 2.Terms and Definitions (Sheet 1 of 3)

| Acronym/<br>Term | Definition                                                                       |  |

|------------------|----------------------------------------------------------------------------------|--|

| ARM              | Refers to both the microprocessor architecture and the company that licenses it. |  |

| ATU              | Address Translation Unit                                                         |  |

| BSP              | Board Support Package                                                            |  |

| BTB              | Branch Target Buffer                                                             |  |

| CAS              | Column Address Strobe                                                            |  |

| CMD              | Command                                                                          |  |

| CPLD             | Complex Programmable Logic Device                                                |  |

| CPSR             | Current Program Status Register                                                  |  |

| CPU              | Central Processing Unit                                                          |  |

| CRB              | Customer Reference Board                                                         |  |

| DBCON            | Data Breakpoint Control                                                          |  |

| DDR              | Double Data Rate                                                                 |  |

#### Table 2.Terms and Definitions (Sheet 2 of 3)

| Acronym/<br>Term | Definition                                                                                                                                      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DIMM             | Dual Inline Memory Module                                                                                                                       |  |

| DIP              | Dual In-Line Package                                                                                                                            |  |

| DRAM             | Dynamic Random Access Memory                                                                                                                    |  |

| ECC              | Error Correction Code                                                                                                                           |  |

| EDE              | Embedded Development Environment                                                                                                                |  |

| EEPROM           | Electrically Erasable Programmable Read-Only Memory                                                                                             |  |

| ELF              | Executable and Linkable Format                                                                                                                  |  |

| GB               | Gigabite                                                                                                                                        |  |

| GNU              | G N U stands for "GNU's Not Unix." Therefore, the G in "GNU" also stands for "GNU," making the acronym recursive.                               |  |

| GPIO             | General Purpose I/O                                                                                                                             |  |

| HD               | Hard Drive                                                                                                                                      |  |

| HSD              | High-Speed Data                                                                                                                                 |  |

| 1/0              | In/Out                                                                                                                                          |  |

| ICE              | In-Circuit Emulator – A piece of hardware used to mimic all the functions of a microprocessor.                                                  |  |

| IOC              | I/O controller                                                                                                                                  |  |

| IOP              | I/O processor                                                                                                                                   |  |

| JTAG             | Joint Test Action Group – A hardware port supplied on Intel XScale <sup>®</sup> microarchitecture CRBs used for in-depth testing and debugging. |  |

| LAN              | Local Area Network                                                                                                                              |  |

| LED              | Light Emitting Display                                                                                                                          |  |

| MAC              | Media Access Control                                                                                                                            |  |

| MB               | MegaBytes                                                                                                                                       |  |

| MHz              | MegaHertz                                                                                                                                       |  |

| MMU              | Memory Management Unit                                                                                                                          |  |

| OS               | Operating System                                                                                                                                |  |

| PBI              | Peripheral Bus Interface                                                                                                                        |  |

| PBIU             | Peripheral Bus Interface Unit                                                                                                                   |  |

| PCIe             | PCI Express bus                                                                                                                                 |  |

| PCI-X            | PCI-X bus                                                                                                                                       |  |

| PHY              | Physical Layer                                                                                                                                  |  |

| PSU              | Power Supply Unit                                                                                                                               |  |

| R/W              | Read/Write                                                                                                                                      |  |

| RAM              | Random Access Memory                                                                                                                            |  |

| ROM              | Read Only Memory                                                                                                                                |  |

| SAS              | Serial Attached Small Computer Systems Interface (SCSI); 81348 I/O Processor only                                                               |  |

| SATA             | Serial Advanced Technology Attachment                                                                                                           |  |

| SDRAM            | Synchronous Dynamic Random Access Memory                                                                                                        |  |

| SGPIO            | Storage General Purpose I/O                                                                                                                     |  |

#### Table 2.Terms and Definitions (Sheet 3 of 3)

| Acronym/<br>Term Definition        |                                             |

|------------------------------------|---------------------------------------------|

| ТТВ                                | Translation Table Base                      |

| UART                               | Universal Asynchronous Receiver-Transmitter |

| XDB         Intel XScale® Debugger |                                             |

## 1.4 Getting Support

#### Table 3. Electronic Information

| Support Type                             | Location/Contact     |

|------------------------------------------|----------------------|

| The Intel World-Wide Web (WWW) Location: | http://www.intel.com |

| Customer Support (US and Canada):        | 1-916-377-7000       |

## 2.0 Customer Reference Board Features

## 2.1 81348 I/O Processor Features

The 81348 I/O processor takes the next step in integration of storage features. The 81348 I/O processor combines a high performance I/O Processor and an eight-port 3Gbps SAS/SATA I/O controller into a single component. Both the IOP and IOC functions in 8134x utilize the newest core based on Intel XScale® technology. Combining these two capabilities into a single component helps reduce board space and system power while improving performance in comparison to discrete components. In addition to combining two functions into a single component, 8134x makes advances towards end-to-end data protection. 8134x utilizes byte-parity checking on it's internal buses to protect data while it travels through the 8134x. It supports ECC for external memory to detect errors. Also, 8134x includes a hardware RAID 5/6 acceleration engine to improve RAID throughput and protect the user's data in case of a drive error.

8134x has options for both PCIe and PCI-X, offering Root Complexes and Central Resources as well as target mode. It is fully compliant with the *PCI-X* Addendum to the *PCI Local Bus Specification*, Revision 1.0 and *PCI Express Specification*, Revision 1.0a.

The 8134x processor includes eight General Purpose I/O (GPIO) pins, and eight ACTIVITY/STATUS pin pairs which are used for SAS links for activity and status indicators. Each SAS link uses one ACTIVITY/STATUS pin pair.

#### Table 4.81348 I/O Processor Features

| Address Translation Unit                    | Transport DMA Controllers              |

|---------------------------------------------|----------------------------------------|

| Messaging Unit                              | UART Units                             |

| Flash Interface Unit                        | Address and Data Bus Parity Protection |

| Eight SAS Link Engines with integrated PHYs | TPMI (Messaging Interface)             |

| I <sup>2</sup> C Bus Interface Units        | Inter-Processor Communication          |

| Multi-Port SRAM Memory Controller           | Timers                                 |

| Application DMA Controllers                 | Watchdog Timers                        |

| XSI System Controller (north and south)     |                                        |

## 2.2 External Storage Design CRB Features

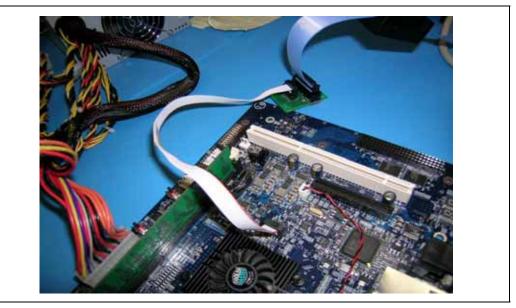

Figure 1 shows the External Storage Design CRB connectors, jumpers and key components.

Figure 1. External Storage Design CRB

Table 5 summarizes the major External Storage Design CRB features.

#### Table 5. External Storage Design CRB Features

| Name                                                                                                 | Description                                                                                                                                                                                                                                                                        |  |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Form Factor                                                                                          | Flex ATX form factor (229mm x 191mm)                                                                                                                                                                                                                                               |  |

| Processor                                                                                            | Integrated 1.2 GHz Intel XScale® Processor                                                                                                                                                                                                                                         |  |

| DRAM 240 pin vertical DIMM – supports up to 2GB<br>• Support for DDRII 400 or 533 MHz or 512 MB DIMM |                                                                                                                                                                                                                                                                                    |  |

| Battery Backup                                                                                       | Battery back up circuitry is provided on the BBU unit which plugs into the PBI slot                                                                                                                                                                                                |  |

| Flash ROM                                                                                            | P30 Flash.                                                                                                                                                                                                                                                                         |  |

| Serial Ports                                                                                         | <ul><li>2 Serial Console Ports</li><li>Stacked DB9 connectors in gasket area</li><li>6-pin header for board to board communication</li></ul>                                                                                                                                       |  |

| JTAG Port                                                                                            | Mini JTAG Header                                                                                                                                                                                                                                                                   |  |

| I2C Ports                                                                                            | <ul><li>3 I2C ports – each port as a 4 pin header</li><li>One header for the SMBus test points and PCIe connection</li></ul>                                                                                                                                                       |  |

| SAS Ports                                                                                            | <ul> <li>81348 I/O Processor assembly option for either:</li> <li>2 internal 4-port SAS/SATA connectors or</li> <li>1 internal 4-port SAS/SATA connector and 1 external 4-port SAS/<br/>SATA connector</li> </ul>                                                                  |  |

| Ethernet Ports                                                                                       | 2 Gigabit Ethernet Ports – RJ45 with integrated LEDs                                                                                                                                                                                                                               |  |

| Compact Flash<br>Port                                                                                | CompactFlash (CF+) Type II connector; supports up to 1G                                                                                                                                                                                                                            |  |

| PCI Express                                                                                          | 1 PCI-Express x8 Slot                                                                                                                                                                                                                                                              |  |

| PCI-X Bus                                                                                            | 64-bit PCI-X slot - 133 MHz                                                                                                                                                                                                                                                        |  |

| On / Off Button                                                                                      | Momentary push button switch <ul> <li>Microcontroller enables controlled power-down</li> </ul>                                                                                                                                                                                     |  |

| Power LED                                                                                            | Power on (green) LED indicator (3.3v)                                                                                                                                                                                                                                              |  |

| HDD LEDs                                                                                             | <ul> <li>Hard drive status and activity LEDs for each SATA port</li> <li>2 2x8 headers for chassis mount HDD LEDs</li> <li>1 aggregated LED header (for ATX front panel header)</li> <li>1 aggregated LED on board</li> </ul>                                                      |  |

| LCD Connector                                                                                        | 1 2x7 connector for a 2 line 40 character LCD                                                                                                                                                                                                                                      |  |

| RTC                                                                                                  | Real time clock                                                                                                                                                                                                                                                                    |  |

| Temperature<br>Sensor                                                                                | Temperature sensor                                                                                                                                                                                                                                                                 |  |

| Enclosure<br>Management                                                                              | 4 fan controllers off the I2C Bus                                                                                                                                                                                                                                                  |  |

| Audible Alarm                                                                                        | Audible buzzer                                                                                                                                                                                                                                                                     |  |

| General Purpose<br>I/O                                                                               | The SGPIO pins are connected to the HDD LED headers. They are also connected through bus isolation switches to the internal wide-port SAS/SATA connectors (81348 I/O Processor). A switch controls whether the SGPIO signals are connected to the wide-port connector or the LEDs. |  |

| Logic Analyzer                                                                                       | Interposer Card may be used for the memory bus – Information<br>supplied separately.<br>PCI-Express analyzer card used for PCI busses.<br>SAS/SATA Analyzers used for the SAS ports                                                                                                |  |

## 3.0 Getting Started

This section tells you how to unpack the CRB and install an ATX power supply to the board.

Once you have completed the setup, refer to "Using the CRB as a Software Development Platform" on page 17 for reference material you can use when configuring the board for a test or development environment.

*Note:* Software updates and additional offerings from vendors can change frequently. To keep up-to-date, please visit http://www.intel-ioprocessortools.com/CRB-registration for the latest updates.

## 3.1 Visual Inspection

*Warning:* Static charges can severely damage the board. Make sure you are properly grounded before removing the board from the anti-static bag.

The first time you unpack the External Storage Design CRB, check to make sure the board was not damaged during shipment. If anything is damaged or missing, contact your Intel representative.

## 3.2 Hardware Requirements

To make full use of the board as a SW development or debug environment you need the following components (these are NOT included in your kit):

- Additional computer system (such as a laptop) with at least one available parallel port and one available serial port (two USB ports). You'll use this system to communicate with the CRB through a serial connection using a terminal program such as Microsoft Windows\* HyperTerminal. The setup instructions in this document assume that you are using a development/debug system in addition to the server system or backplane.

- JTAG Emulator debug device. You can obtain a debugger from the vendors listed in Table 6.

- 20-pin ATX power supply

## 3.3 Set-up and Configuration

The following information is used to set up the External Storage Design CRB board:

- The CRB can be installed in a Micro/Flex ATX chassis or left alone on a bench. A 20-pin ATX power supply is required to power up the board.

- To program and configure the board, connect a serial cable between the board and another system (such as a laptop computer); then you can use connection software running on the laptop to communicate with the board. See Section 3.4 for full details on establishing this connection.

• The software on the board used to operate the board and exercise board features is a bootstrap program called RedBoot. See Section 4.2.1 for more information about the RedBoot operating system.

#### 3.3.1 Installing the External Storage Design CRB into a Micro or Flex ATX Chassis

The External Storage Design CRB is in a standard Flex ATX form factor and fits into a standard Micro or Flex ATX chassis. This board fits into a standard chassis.

#### 3.3.1.1 Connecting an Optional JTAG Debug Device

A JTAG debug device can be connected to the External Storage Design CRB through the 10-pin mini JTAG header (J3C1). A converter board and cable is included in your kit to interface the 10-pin External Storage Design CRB JTAG connector to a conventional 20-pin JTAG connector. You can obtain a JTAG debugger from the vendors listed in Table 11.

Be careful to align the polarizing notch on the 10-pin header shroud with the polarizing feature on the JTAG cable receptacle connector. If the 10-pin mini JTAG cable is plugged in backward a red LED on the JTAG converter board illuminates to indicate a cable polarity problem.

Figure 2 shows the JTAG Adapter board and ribbon cable required to communicate with a JTAG Emulator.

#### 3.3.1.2 Installing Drivers and Firmware

The External Storage Design CRB is shipped loaded with the Redboot\* bootloader, PIC code, and the CPLD pre-programmed. To obtain this code, please contact your Intel Field Representative.

To use some CRB features, such as the SAS ports (81348 I/O Processor only), you need to load appropriate drivers or Transport Firmware on the CRB. These drivers are available from Intel. Contact your Field Sales Representative for more information.

*Note:* Only the 81348-based IOP version of External Storage Design CRB has SAS connectors soldered to the board. If you received an 81341 or 81342 based IOP version of External Storage Design CRB, none of the SAS connectors are populated.

Once you have obtained the Transport Firmware, you can use the SATA or SAS ports as described in the next section.

## 3.4 Communicating with the CRB

When the External Storage Design CRB boots, a Redboot bootloader is loaded into memory and executed. A development/debug system can communicate with the Redboot software through the serial ports. A pair of RJ-11 cables and an RJ-11 to DB9 converter is supplied with the board.

To communicate between a development/debug system and the External Storage Design CRB Redboot software:

- 1. Plug an RJ-11 cable into either RJ-11 connector.

- 2. Plug an RJ-11 to DB9 converter board onto the other end of the RJ-11 cable and into a development/debug computer DB9 serial port connector.

- 3. Start a HyperTerminal (or equivalent) session on the development/debug computer with the following parameters:

Communications Port: Com port connected to the DB9 to RJ-11 converter. Baud Rate: 115200 Data Bits: 8

Parity Bits: None Stop Bits: 1 Flow Control: None

• When the External Storage Design CRB is powered-up, it displays boot-up messages and after approximately 30 seconds displays the Redboot prompt in the HyperTerminal window.

## 3.4.1 Using the Ethernet Port

The CRB has an on-board gigabit Ethernet device and connector. Programmers can use this device for software download via TFTP and for disk management over Ethernet applications.

## 3.4.1.1 Using the Serial ATA or Serial Attached SCSI Ports

The External Storage Design CRB has eight SAS/SATA disk drive ports connected to the 81348 I/O Processor storage interface. The 81384-based IOP version of External Storage Design CRB allows the user to use either the x4 external SAS connector (J9A1) and the x4 internal SAS connector (J9C1) by default. There is a stuffing option on the board which allows a user to use both x4 internal SAS connectors (J9C1 & J9E1). This stuffing option disables the x4 external connector port, however. To use J9C1 & J9E1, the capacitors on the back of the board must be carefully removed and then placed on top of the board on the corresponding capacitors pads which can be referenced by using the schematic. To obtain a schematic of this board, please contact your Intel Representative.

Once the transport firmware has been installed, connect one or more supplied SAS cables to the External Storage Design CRB SAS connectors. Connect the other end(s) to one or more SAS drives. Connect the 4-pin power cable(s) attached to the SAS cables to standard 4-pin power supply peripheral power connectors.

## 4.0 Using the CRB as a Software Development Platform

## 4.1 Third Party Software Support

This build of External Storage Design CRB is using pre-production silicon, and is the first build of boards that has been delivered to OS vendors for software porting. Therefore, there is no commercially available software support for these boards at the time of publishing this manual. Gold releases of software solutions are only publicly available coincident with the production release of the 8134x silicon, and the External Storage Design CRB.

## 4.1.1 Proposed Solutions

Table 6 indicates Software Tools Vendors and Operating Systems that are getting

External Storage Design CRB boards.

#### Table 6. Software Tools Vendors and Operating Systems

| Vendor                     | OS                            |

|----------------------------|-------------------------------|

| Bactrian*                  | JTAG                          |

| American Arium*            | JTAG                          |

| ARM*                       | JTAG                          |

| Embedded Performance Inc.* | JTAG                          |

| GreenHills*                | Integrity RTOS                |

| Macraigor Systems*         | Raven and MpDemon JTAG        |

| Mentor Graphics*           | Nucleus OS and EDGE debugger. |

| TimeSys*                   | Linux OS and Tools            |

| Windriver Systems*         | VxWorks and Vision-ICE JTAG   |

The CRB boards are delivered with the RedBoot\* Bootloader installed in flash memory. Source files for this solution are available on request, and updated binaries are released as bugs are found and fixed.

If you want a status on the porting of a particular solution, or RedBoot information please send an email to crb@intel-ioprocessortools.com.

## 4.1.2 Other Solutions

When your favorite OS or tools company is missing from the list in Table 6, please send an email to crb@intel-ioprocessortools.com requesting that they be added.

## 4.2 Software Developer Reference Information

This section provides reference information for software developers.

## 4.2.1 RedBoot\* Software

Once you see the RedBoot prompt in the HyperTerminal window, you know the board is functioning properly. The RedBoot bootstrap software supports diagnostic tools for testing the memory and basic board features. To access the RedBoot diagnostic features, refer to Section 4.2.1.1. This provides a list of supported commands and syntax. For full details, refer to Appendix A, "Advanced Redboot Commands" for information on Redboot commands including the following:

- "Removing the "+FLASH configuration checksum error or invalid key" message"

- "Rebuilding RedBoot"

- "Using RedBoot to Update the RedBoot Image"

- "Using RedBoot to Update the Transport Firmware Image"

- "Initialize the Flash File System "

- "Display the Current File System in Flash"

Also refer to the RedBoot User's Guide at this link:

http://sources.redhat.com/ecos/docs-latest/redboot/redboot-guide.html

#### 4.2.1.1 Redboot Diagnostics

The CRB comes with RedBoot loaded in the Flash. RedBoot is the RedHat debug monitor which initializes the board and has some debug and diagnostic functions.

- *Note:* Read the RedBoot manual and become familiar with Serial Port applications before performing diagnostics.

- *Note:* The CRB board is shipped preflashed with jumpers and settings set in factory settings. It also is shipped with the necessary cabling hardware (cable and adapter/converter) to perform this procedure.

To perform diagnostics:

- 1. Refer to "Communicating with the CRB" on page 16 for instructions on how to set up the CRB and get to the Redboot prompt.

- 2. At the Redboot prompt, enter the diagnostic command with **DIAG** or **DIA** and the RedBoot Diagnostic function is invoked. The list of Redboot diagnostics displays. Figure 3 shows the diagnostic startup and utilities list.

- 3. Perform the tests that are desired.

#### Figure 3. Redboot Diagnostics Command and Hardware Test Listing

RedBoot> diag

Entering Hardware Diagnostics - Disabling Data Cache!

IQ8134x CRB Hardware Tests

- 1 Memory Tests

- 2 Random-write Memory Tests

- 3 Repeating Memory Tests

- 4 Repeat-On-Fail Memory Test

- 5 Enhanced Memory Tests

- 6 Rotary Switch S1 Test

- 7 7 Segment LED Tests

- 8 i82545 Ethernet Configuration

- 9 Timer Test

- 10 PCI Bus test

- 11 CPU Cache Loop (No return)

- 12 Batch Memory Tests

- 13 Multi-Path Memory Test

- 14 NVRAM Test

- 0 quit

- Enter the menu item number (0 to quit):

The Redboot hardware tests are listed in Table 7.

#### Table 7.Redboot Hardware Tests (Sheet 1 of 2)

| Number                          | Test Name              | Description                                                                                                                                                                                                                                                                                        |

|---------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 Memory Tests                  |                        | Performs Walking One, Zero, 32-bit Address/Address<br>Bar, and 8-bit Address/Address Bar test to selected<br>memory range. Note that Redboot uses memory<br>between 00000000H - 0001C000H. Memory tests<br>should be restricted to addresses above 0001C000H to<br>avoid conflicting with Redboot. |

|                                 |                        | Writes and then verifies a random 32-bit pattern to selected memory range.                                                                                                                                                                                                                         |

| 3                               | Repeating Memory Tests | Performs the Memory Test diag (#1) ad infinitum to selected memory range.                                                                                                                                                                                                                          |

| 4 Repeat-On-Fail Memory<br>Test |                        | Performs Address/Address Bar memory test to the selected memory range in a continuous loop until a failure is encountered and then continually reads/ writes to the failing location ad infinitum.                                                                                                 |

| Number                             | Test Name               | Description                                                                                                                                                                    |

|------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 Enhanced Memory Tests            |                         | Executes a memory diagnostic to the selected memory range with several different memory patterns.                                                                              |

| 6                                  | Rotary Switch S1 Test   | Shows the current location of the rotary switch on the Right 7-segment LED. <sup>1</sup>                                                                                       |

| 7                                  | 7 Segment LED Tests     | Displays 0-F on the left and then right LED.                                                                                                                                   |

| 8 i82545 Ethernet<br>Configuration |                         | Programs the i82545 EEPROM with the desired MAC address.                                                                                                                       |

| 9 Timer Test                       |                         | Outputs a period "." every second.                                                                                                                                             |

| 10                                 | PCI Bus test            | Scans the PCI-X bus for any devices present and prints out device/vendor ID and BAR information.                                                                               |

| 11 CPU Cache Loop (No return)      |                         | Places processor in a tight cache loop with no return.                                                                                                                         |

| 12 Batch Memory Tests              |                         | Executes the Memory Tests Diagnostic (#1) to all available SDRAM addresses.                                                                                                    |

| 13 Multi-Path Memory Test          |                         | Executes a parallel memory test using all 3 ADMA units and a core memory copy.                                                                                                 |

| 14                                 | NVRAM Test <sup>2</sup> | Executes a standard memory test, but also checks if data has already been written in a previous test run to verify if the memory retained its values since the last execution. |

| 0                                  | Quit                    | Exits the application.                                                                                                                                                         |

#### Table 7.Redboot Hardware Tests (Sheet 2 of 2)

1. There is no rotary switch on External Storage Design CRB. If you run this test, a message displays indicating that there is no rotary switch.

2. There is not NVRAM on External Storage Design CRB. Invoking this test displays a message indicating that there is no NVRAM.

## 4.2.2 Reflashing the Memory

The boards are delivered with the latest (at time of the board build) RedBoot\* Bootloader installed in Flash. You can load your own software into memory using a variety of tools. Appendix E provides a tutorial for using Intel's XDB to load custom software onto the CRB. Appendix F provides a tutorial for using Accelerated Technology, Inc.'s Edge software to load custom software onto the CRB.

If these tools are unavailable, you can also use Intel's Flash Recovery Utility that is provided on the CD included in your kit.

#### 4.2.3 Peripheral Bus Memory Map

The Table 8 is the physical memory map of the devices on the 8134x peripheral bus.

#### Table 8.Peripheral Bus Memory Map (Sheet 1 of 2)

| Address Range (in Hex) | Size  | Data Bus Width  | Description              |

|------------------------|-------|-----------------|--------------------------|

| F000 0000 - F1FF FFFF  | 8 MB  | 8-bit or 16-bit | Flash memory (re-mapped) |

| F200 0000 - F200 FFFF  | 64 KB | 8-bit           | Product Code             |

| F201 0000 - F201 FFFF  | 64 KB | 8-bit           | Board Stepping           |

| F202 0000 - F202 FFFF  | 64 KB | 8-bit           | CPLD Firmware Revision   |

| F203 0000 - F203 FFFF  | 64 KB | 8-bit           | Discrete LEDs            |

#### Table 8. Peripheral Bus Memory Map (Sheet 2 of 2)

| Address Range (in Hex) | Size  | Data Bus Width | Description       |

|------------------------|-------|----------------|-------------------|

| F204 0000 - F204 FFFF  | 64 KB | 8-bit          | Hex Display Left  |

| F205 0000 - F205 FFFF  | 64 KB | 8-bit          | Hex Display Right |

| F206 0000 - F206 FFFF  | 64 KB | 8-bit          | Buzzer Control    |

| F300 0000 - F301 0000  | 64 KB | 8-bit          | Compact Flash     |

#### 4.2.4 RedBoot External Storage Design CRB Memory Map

Table 9 lists the memory map established by Redboot when External Storage DesignCRB boots.

#### Table 9. RedBoot\* Memory Map

| Virtual Address | Physical Address<br>(Internal Bus) | Size (MB) | Description                              |

|-----------------|------------------------------------|-----------|------------------------------------------|

| 0x0000000       | 0x0.0000.0000                      | 2048      | SDRAM - 64-bit ECC                       |

| 0x80000000      | 0x1.8000.0000                      | 128       | ATU-X Outbound Memory Translation Window |

| 0x88000000      | 0x2.8800.0000                      | 128       | ATUe Outbound Memory Translation Window  |

| 0x9000000       | 0x0.9000.0000                      | 1         | ATU-X Outbound IO Window                 |

| 0x90100000      | 0x0.9010.0000                      | 1         | ATUe Outbound IO Window                  |

| 0x90200000      |                                    | 254       | Unused                                   |

| 0xA0000000      | 0x0.0000.0000                      | 512       | SDRAM - 64-bit ECC - Uncached Alias      |

| 0xC0000000      | 0x0.C000.0000                      | 1         | Cache Flush, DCache Lock                 |

| 0xC0100000      |                                    | 255       | Unused                                   |

| 0xD0000000      |                                    | 512       | Unused (32-bit ECC not enabled)          |

| 0xF0000000      | 0x0.F000.0000                      | 32        | Flash (PCE0#)                            |

| 0xF2000000      | 0x0.F200.0000                      | 1         | PCE1#                                    |

| 0xF2100000      | 0x0.F200.0000                      | 1         | PCE1# - cached/buffered                  |

| 0xF2100000      |                                    | 14        | Unused                                   |

| 0xF3000000      | 0x0.F300.0000                      | 1         | Compact Flash                            |

| 0xF3100000      |                                    | 204       | Unused                                   |

| 0xFFD00000      | 0x0.FFD0.0000                      | 1         | MMR                                      |

| 0xFFE00000      | 0x0.FFE0.0000                      | 2         | Unused                                   |

## 4.2.5 RedBoot Files Included in the CRB Kit

To obtain the CD that includes a copy of the RedHat eCos for External Storage Design CRB, please contact your Intel Representative.

- The RedBoot initialization code source files from the following location: From the installed directory:

- $..\label{eq:linear} \label{eq:linear} ..\label{eq:linear} \label{eq:linear} \label$

- The RedBoot binary image files (downloadable onto Flash) from the following location:

From the installed directory:

..\RedHat\eCos\loaders\

If you need to rebuild the RedBoot image that comes already loaded onto the board, see "Rebuilding the RedBoot Image" on page 23.

To access GNUPro tools for compiling and building RedBoot, go to the following location on the Intel site:

<u>http://developer.intel.com/design/intelxscale/dev\_tools/031121/index.htm</u>

Also see the RedBoot user's guide:

• <u>http://sources.redhat.com/ecos/docs-latest/redboot/redboot-guide.html</u>

#### 4.2.5.1 Redhat Redboot

RedBoot\* is an acronym for "Red Hat Embedded Debug and Bootstrap", and is the standard embedded system debug/bootstrap environment from Red Hat, replacing the previous generation of debug firmware: CygMon and GDB stubs. It provides a bootstrap environment for a range of embedded operating systems, such as embedded Linux and eCos\*, and includes facilities such as network downloading and debugging. It also provides a simple Flash file system for boot images. RedBoot provides a set of tools for downloading and executing programs on embedded target systems, as well as tools for manipulating the target system's environment. It can be used for both product development (debug support) and for end product deployment (Flash and network booting). Highlights of RedBoot capabilities are:

- Boot scripting support

- Simple command line interface for RedBoot configuration and management, accessible via serial (terminal) or Ethernet (telnet) (see Section 2.6.4, "GNUPro GDB/Insight" on page 26)

- Integrated GDB stubs for connection to a host-based debugger (GBD/Insight) via serial or Ethernet. (Ethernet connectivity is limited to local network only)

- Attribute Configuration user control of aspects such as system time and date (when applicable), default Flash image to boot from, default fail-safe image, static IP address, etc.

- · Configurable and extensible, specifically adapted to the target environment

- Network bootstrap support including setup and download, via BOOTP, DHCP and TFTP

- X/Y-Modem support for image download via serial

- Power On Self Test

#### 4.2.6 RedBoot External Storage Design CRB Initialization Sequence

In order to set the ECC bits correctly, the DDR memory system must be written to with a known value. This process requires writing to the entire DDR memory intended for use. The following explains the sequence for memory initialization by RedBoot on a External Storage Design CRB board with an ECC DIMM.

Initialization Sequence:

- 1. Disable interrupts. (Technically they are disabled at reset, but for soft reset this is included.

- 2. Init PBIU (Peripheral Bus Interface Unit) chip selects.

- 3. Enable I cache.

- 4. Move Flash to 0xF0000000.

- 5. Set TTB and Enable MMU.

- 6. Lock data cache as temporary RAM to create stack space for c-function calls.

- 7. Read SDRAM SPD device for memory parameters.

- 8. Set Memory Parameters.

- 9. Enable SDRAM.

- 10. Scrub SDRAM by writing zeros to all locations in order to initialize the ECC fields in the memory.

- 11. Delete the temporary data cache RAM.

- 12. Enable ECC.

- 13. Copy page table entries to SDRAM.

- 14. Update TTB register.

- 15. Initialize UART.

- 16. Load GigE Ethernet driver.

## 4.2.7 Rebuilding the RedBoot Image

Refer to Appendix A for information on this procedure.

#### 4.2.8 Software Reset

On the External Storage Design CRB board S7G1 is the physical reset button which sends a reset signal to the entire board. A software reset through JTAG exhibits the same behavior.

## 5.0 Hardware/Architecture Reference

This document can be used as a reference by designers creating boards for custom applications. A high level Bill of Materials is included in "Bill of Materials" on page 46 and schematics are available in a separate document on an Intel Representative.

*Note:* The design for the External Storage Design CRB may not fully comply with the specifications included in the product Design Guides. When using the CRB as a reference design, specifications in the Design Guide take precedence over anything included in the External Storage Design CRB schematics.

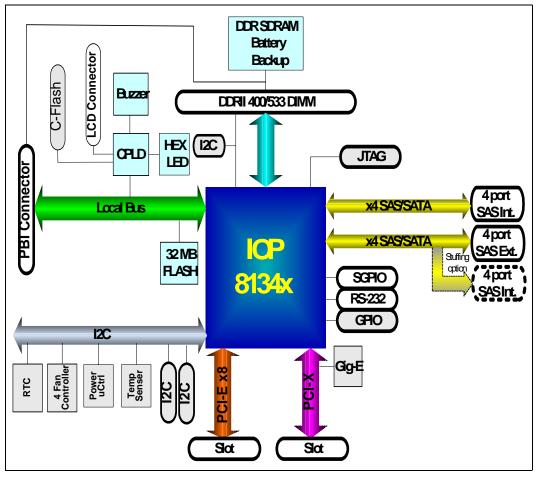

Figure 4 shows a diagram of the External Storage Design CRB connectors, jumpers and key components.

## Figure 4. External Storage Design CRB Block Diagram

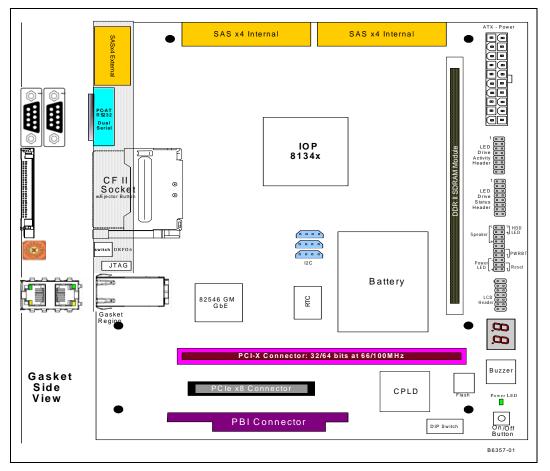

#### Figure 5. External Storage Design CRB Layout

## 5.1 Memory Subsystem

The External Storage Design CRB memory subsystem has the following features:

- One DDRII SDRAM DIMM socket supporting the following configurations:

- 400 MHz or 533 MHz DIMM

- Registered or unbuffered DIMM

- With or without ECC

- CAS latency of 3, 4 or 5

- Single-sided or double-sided DIMM

- I<sup>2</sup>C bus 2 connected to SDRAM for serial presence detection

## 5.1.1 DDR SDRAM

The 8134x CRBs have one DDRII SDRAM module connector. This connector must also allow for installing a DDRII analyzer card (i.e., must provide enough mechanical clearance). The connector is a 240-pin DDR II DIMM connector.

The DDR SDRAM interface consists of a 64-bit wide data path to support up to 3.2 Gbytes/s throughput. An 8-bit Error Correction Code (ECC) is stored into the DDRII SDRAM array along with the data and is checked when the data is read.

The External Storage Design CRB features a single 240-pin right-angled DIMM connector. The 3-bit base SPD address is set for binary '000', so the complete SPD address is binary '1010000'. The 81348 component supports registered or unbuffered DIMMs, memory speeds of 400 MHz or 533 MHz, in sizes ranging from 256 MB up to 2 GB. Memory device widths of x8 or x16 are supported.

## 5.1.2 Flash ROM

On the External Storage Design CRB, two Flash devices are populated: 28F256P30T (U2B1) and 28F640J3C125 (U2C1). By default, the 28F256P30T (U2B1) is physically connected to the PBI bus through chip enable 0 (CE0). To enable customer code development dependent on the J3 Flash, rework is available to disable the P30 device and enable the J3 device.

The width of the PBI bus on External Storage Design CRB is 16-bit and cannot be changed.

To disable the P30 and enable the J3, please contact your Intel Representative for the latest schematic and rework instructions.

*Note:* The J3 Flash is being discontinued.

### 5.1.3 CPLD

The CRB contains the CPLD for monitoring and controlling various board features. The CPLD is preprogrammed at the factory with support for debug LEDs, buzzer, compact Flash, and backup battery. To obtain a copy of this code, please contact your Intel representative.

#### 5.1.3.1 CPLD Register Descriptions

Table 10 through Table 13 show the CPLD register definitions. The read/write column indicates whether the bits are read only (R) or can be read and written (R/W). Writes have no effect on bits that are read only.

Table 10 defines the Battery Status Register bits.

#### Table 10. BAT\_STAT Register Definition

| Bit | Read/<br>Write | Name               | Definition                                                                             |

|-----|----------------|--------------------|----------------------------------------------------------------------------------------|

| 0   | R              | Battery Present    | No DDR backup battery.<br>DDR backup battery is present.                               |

| 1   | R              | Battery Charged    | DDR backup battery is not fully charged.<br>DDR backup battery is fully charged.       |

| 2   | R              | Battery Discharged | DDR backup battery is not fully discharged.<br>DDR backup battery is fully discharged. |

| 3   | R/W            | Battery Enable     | Disable DDR backup battery.<br>Enable DDR backup battery.                              |

| 4-7 |                | Reserved           | Undefined                                                                              |

Table 11 defines the Product Code Register bits.

#### Table 11. PROD\_CODE Register Definition

| Bit | Read/<br>Write | Name         | Definitions                                                                                                                                      |

|-----|----------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-0 | R              | Product SKU  | Identifies variants within a family of products. This<br>register is hardcoded.<br>Product SKU definitions:<br>0x4 = External Storage Design CRB |

| 7-4 | R              | Product Code | Identifies the product. This value is hard coded in the<br>CPLD firmware.<br>0x6 = External Storage Design CRB                                   |

Table 12 defines the Board Stepping Register bits.

#### Table 12. BOARD\_STEPPING Register Definition

| Bite | Read/<br>Write | Name               | Definition                                                                                                 |

|------|----------------|--------------------|------------------------------------------------------------------------------------------------------------|

| 3-0  | R              | Board Rework Level | Identifies rework completed on the board. This register is hardcoded.<br>0x4 = External Storage Design CRB |

| 7-4  | R              | Board Stepping     | Identifies the board stepping. This register is<br>hardcoded.<br>0x4 = External Storage Design CRB         |

Table 13 defines the CPLD Firmware Revision Register bits.

#### Table 13.CPLD\_FW Register Definition