# Intel<sup>®</sup> 80331 I/O Processor

**Developer's Manual**

October 2003

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel® internal code names are subject to change.

THIS SPECIFICATION, THE Intel® 80331 I/O Processor IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

Copyright © Intel Corporation, 2003

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, Commerce Cart, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantIP, Intel, Intel Iogo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel Inside, Intel Inside, Intel Inside, Intel NetStructure, Intel Play, Intel Play Iogo, Intel Pocket Concert, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel WebOutfitter, Intel Xeon, Intel XScale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo, NetPort, NetportExpress, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, ProShare, RemoteExpress, Screamline, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, This Way In, TokenExpress, Trillium, Vivonic, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries

\*Other names and brands may be claimed as the property of others.

2 October, 2003 Document Number: 273942-002

| 1 | Intro | duction            |                                                         | 35 |  |

|---|-------|--------------------|---------------------------------------------------------|----|--|

|   | 1.1   | About <sup>1</sup> | About This Document                                     |    |  |

|   |       | 1.1.1              | How To Read This Document                               | 35 |  |

|   |       | 1.1.2              | Other Relevant Documents                                |    |  |

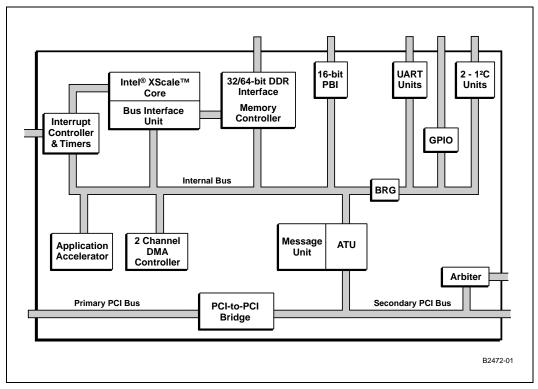

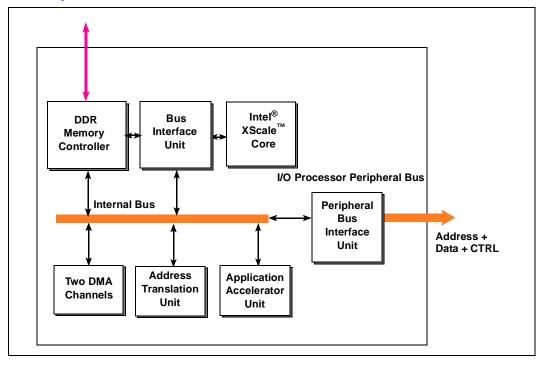

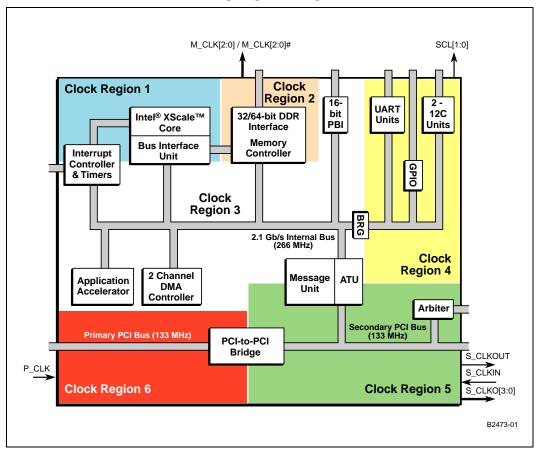

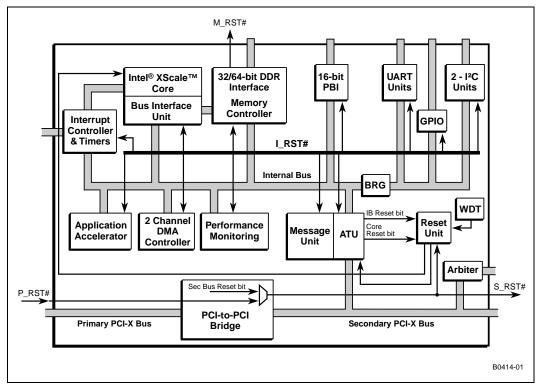

|   | 1.2   | About t            | the Intel <sup>®</sup> 80331 I/O Processor              | 36 |  |

|   | 1.3   | Feature            | es                                                      | 38 |  |

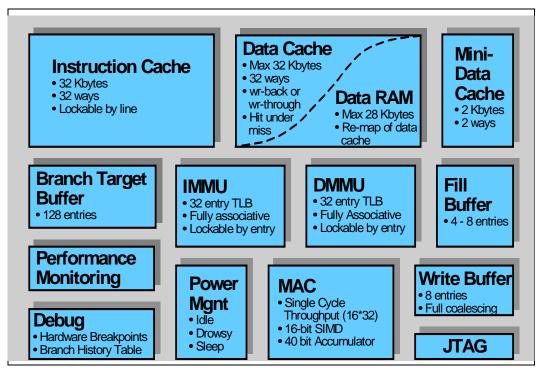

|   |       | 1.3.1              | Intel <sup>®</sup> XScale <sup>™</sup> Core             | 38 |  |

|   |       | 1.3.2              | PCI-to-PCI Bridge Unit                                  |    |  |

|   |       | 1.3.3              | Address Translation Units                               | 39 |  |

|   |       | 1.3.4              | Memory Controller                                       | 39 |  |

|   |       | 1.3.5              | Application Accelerator Unit                            | 39 |  |

|   |       | 1.3.6              | Peripheral Bus Interface                                | 39 |  |

|   |       | 1.3.7              | DMA Controller                                          | 39 |  |

|   |       | 1.3.8              | I <sup>2</sup> C Bus Interface Unit                     | 40 |  |

|   |       | 1.3.9              | Messaging Unit                                          | 40 |  |

|   |       | 1.3.10             | Internal Bus                                            | 40 |  |

|   |       | 1.3.11             | UART Unit                                               | 40 |  |

|   |       | 1.3.12             | Interrupt Controller Unit                               | 40 |  |

|   |       | 1.3.13             | GPIO                                                    | 40 |  |

|   | 1.4   | Termin             | ology and Conventions                                   | 41 |  |

|   |       | 1.4.1              | Representing Numbers                                    | 41 |  |

|   |       | 1.4.2              | Fields                                                  | 41 |  |

|   |       | 1.4.3              | Specifying Bit and Signal Values                        | 41 |  |

|   |       | 1.4.4              | Signal Name Conventions                                 | 42 |  |

|   |       | 1.4.5              | Terminology                                             | 42 |  |

| 2 | PCI-  | to-PCI B           | ridge                                                   | 43 |  |

|   | 2.1   | Introdu            | iction                                                  | 43 |  |

|   |       | 2.1.1              | Product Overview                                        |    |  |

|   |       | 2.1.2              | Features List                                           |    |  |

|   |       | 2.1.3              | Related External Specifications                         |    |  |

|   | 2.2   |                    | peration                                                |    |  |

|   |       | 2.2.1              | RESET                                                   |    |  |

|   |       | 2.2.2              | Pre-Boot Component Initialization                       |    |  |

|   |       | 2.2.3              | Pin Strap Configuration                                 |    |  |

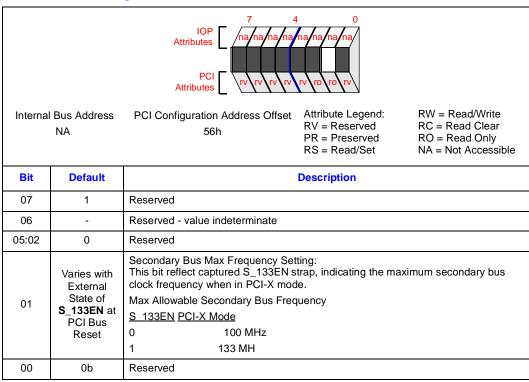

|   |       |                    | 2.2.3.1 Secondary Bus Maximum Allowable Frequency       |    |  |

|   |       |                    | 2.2.3.2 Bridge Disable                                  |    |  |

|   |       |                    | 2.2.3.3 Arbiter and Central Resource                    | 46 |  |

|   |       | 2.2.4              | Bus Mode and Frequency Initialization                   | 46 |  |

|   |       |                    | 2.2.4.1 Primary Bus Mode and Frequency Initialization   | 47 |  |

|   |       |                    | 2.2.4.2 Secondary Bus Mode and Frequency Initialization | 47 |  |

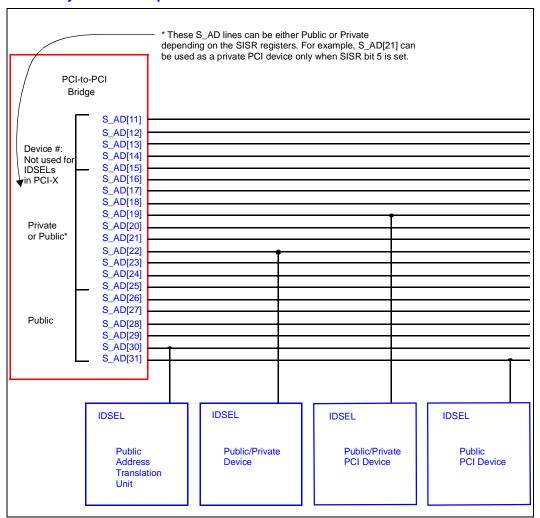

|   |       | 2.2.5              | Private Devices on the Secondary Interface              | 49 |  |

|   |       |                    | 2.2.5.1 Private Type 0 Commands on Secondary Interface  |    |  |

|   |       |                    | 2.2.5.2 Private Memory Space                            |    |  |

|   |       | 2.2.6              | Device Select Timing                                    |    |  |

|   |       | 2.2.7              | 64-Bit Operation                                        |    |  |

|   |       | 2.2.8              | PCI Power Management Support                            | 51 |  |

| 2.2.9    | Overview   | v of Bus Transactions                                  |    |

|----------|------------|--------------------------------------------------------|----|

|          | 2.2.9.1    | PCI-to-PCI                                             | 52 |

|          | 2.2.9.2    | PCI to PCI-X                                           | 53 |

|          | 2.2.9.3    | PCI-X to PCI                                           | 53 |

|          | 2.2.9.4    | PCI-X to PCI-X                                         | 53 |

| 2.2.10   | Bus Inter  | face Data Flow                                         | 54 |

|          | 2.2.10.1   |                                                        |    |

|          |            | 2.2.10.1.1As the PCI Target                            | 54 |

|          |            | 2.2.10.1.2As the PCI-X Target                          |    |

|          |            | 2.2.10.1.3PCI-X Receiving Data                         |    |

|          | 2.2.10.2   |                                                        |    |

|          |            | 2.2.10.2.1As the PCI Master                            |    |

|          |            | 2.2.10.2.2As the PCI-X Master                          |    |

| 2.2.11   | Exclusive  | e Access                                               |    |

|          |            | ional PCI Mode                                         |    |

|          |            | Posted Memory Write Transactions                       |    |

|          |            | Fast Back-to-Back Transactions                         |    |

|          |            | Write Flow-Through                                     |    |

|          |            | Delayed Write Transactions                             |    |

|          | 2.2.12.7   | 2.2.12.4.1Delayed Write Transaction Time-out Errors    | 07 |

|          |            | on the Destination Bus                                 | 57 |

|          |            | 2.2.12.4.2Delayed Write Transaction Time-out Errors    | 07 |

|          |            | on the Origination Bus                                 | 57 |

|          | 2 2 1 2 5  | Read Transactions                                      | 58 |

|          | 2.2.12.0   | 2.2.12.5.1Delayed Read Transactions                    |    |

|          |            | 2.2.12.5.2Non-prefetchable Reads                       |    |

|          |            | 2.2.12.5.3Read Flow Through                            |    |

|          |            | 2.2.12.5.4Prefetching                                  |    |

|          | 2.2.12.6   | Transaction Ordering                                   | 62 |

| 2 2 13   |            | us Mode                                                |    |

|          |            | Attributes                                             |    |

|          |            | Special Notes for Burst Transactions                   |    |

|          |            | Split Transactions                                     |    |

|          | 2.2.10.0   | 2.2.13.3.1Completer Attributes                         | 64 |

|          |            | 2.2.13.3.2Requirements for Accepting Split Completions |    |

|          |            | 2.2.13.3.3Split Completion Messages                    | 64 |

|          | 2.2.13.4   | Transaction Ordering                                   | 65 |

|          |            | Transaction Termination as a PCI-X Target              |    |

|          |            | 2.2.13.5.1Retry                                        |    |

|          |            | 2.2.13.5.2Split Response                               | 66 |

|          |            | 2.2.13.5.2Split Response                               | 66 |

|          | 2.2.13.6   | Bridge Buffer Requirements                             | 66 |

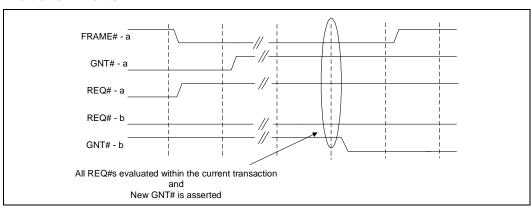

| Arbitrat |            |                                                        |    |

| 2.3.1    |            | on Events                                              |    |

| _        | 2.3.1.1    | Arbitrating in Traffic                                 |    |

|          | 2.3.1.2    | Bus Parking                                            |    |

|          | 2.3.1.3    | Grant Time-Out                                         |    |

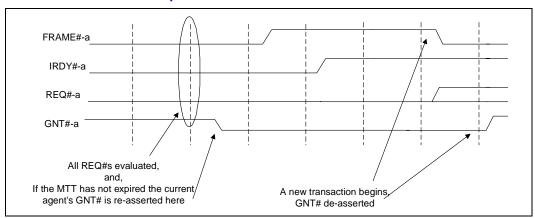

| 2.3.2    |            | Insaction Timer (MTT)                                  |    |

| 2.0.2    | 2.3.2.1    | MTT Rules                                              |    |

| 2.3.3    |            | ventional Mode Arbitration                             |    |

|          |            |                                                        |    |

| 2.3.4    |            | bitration                                              |    |

|          | 2.3.4.1    | Fair Internal Arbitration                              | 12 |

| <b>.</b> | 2.3.4.2    | Retry or Disconnected Request                          |    |

| ⊨rror D  | etection a | ind Reporting                                          | 73 |

2.3

2.4

|     | 2.4.1   | Normal C                                    | Operation                                                              | 73              |  |  |  |

|-----|---------|---------------------------------------------|------------------------------------------------------------------------|-----------------|--|--|--|

|     | 2.4.2   | Respons                                     | e Enabled                                                              | 74              |  |  |  |

|     | 2.4.3   |                                             | # Assertion                                                            |                 |  |  |  |

| 2.5 | Prograi |                                             | erface                                                                 |                 |  |  |  |

|     | 2.5.1   | Standard PCI Configuration Header Registers |                                                                        |                 |  |  |  |

|     |         | (Offset 00                                  | 0H-3FH)                                                                | 76              |  |  |  |

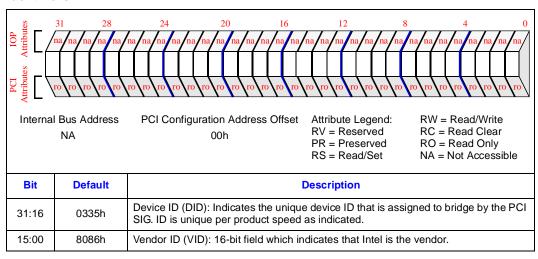

|     |         | 2.5.1.1                                     | Identifiers - ID                                                       |                 |  |  |  |

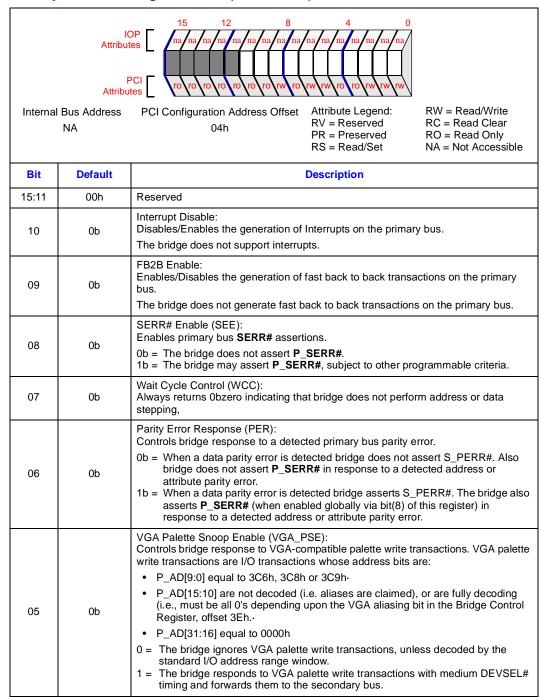

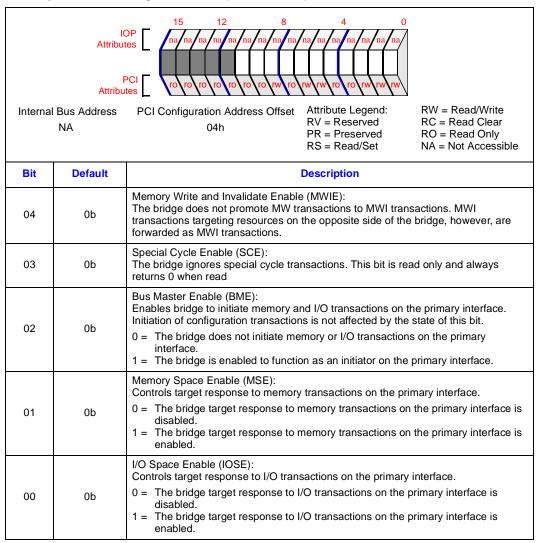

|     |         | 2.5.1.2                                     |                                                                        |                 |  |  |  |

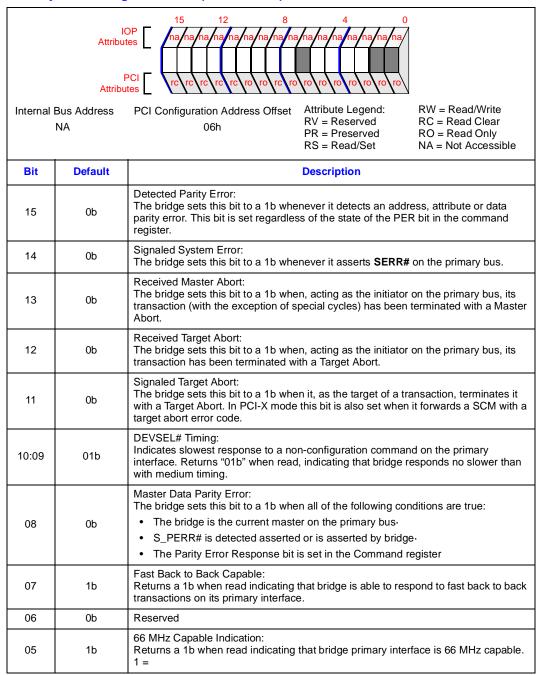

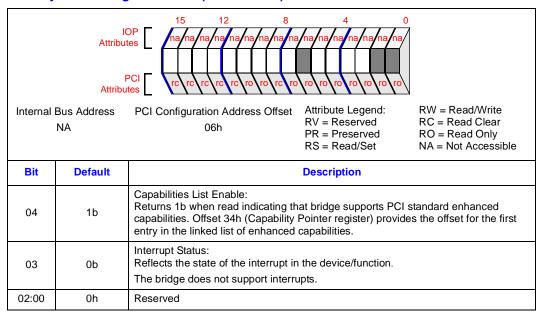

|     |         | 2.5.1.3                                     | Primary Status Register - PSR                                          |                 |  |  |  |

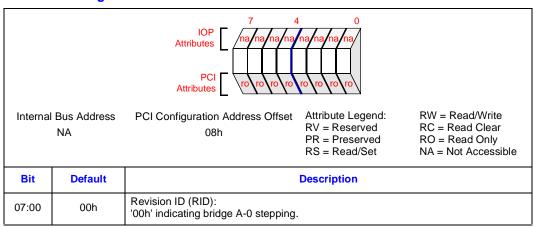

|     |         | 2.5.1.4                                     | Revision ID Register - RID                                             | 82              |  |  |  |

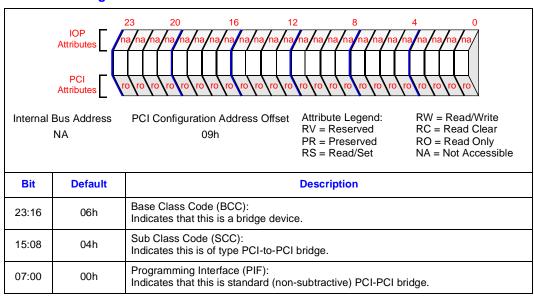

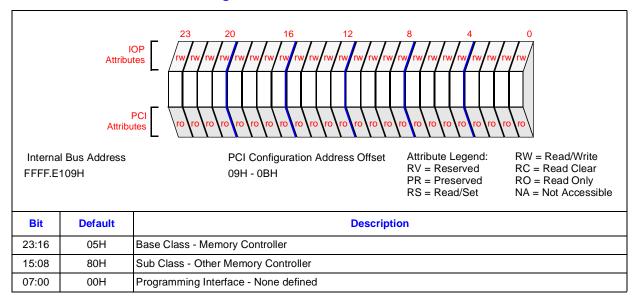

|     |         | 2.5.1.5                                     | Class Code Register - CCR                                              | 83              |  |  |  |

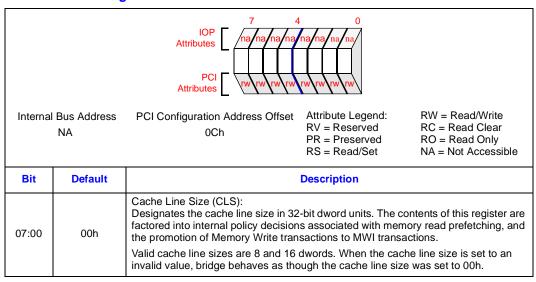

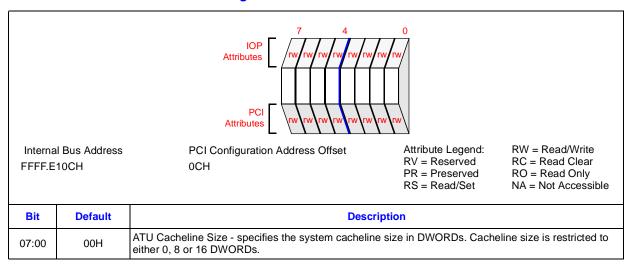

|     |         | 2.5.1.6                                     | Cacheline Size Register - CLSR                                         | 84              |  |  |  |

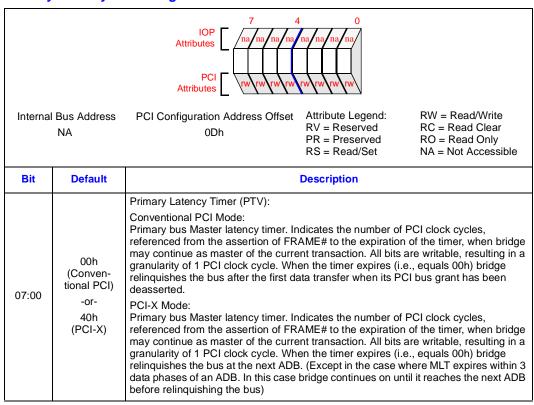

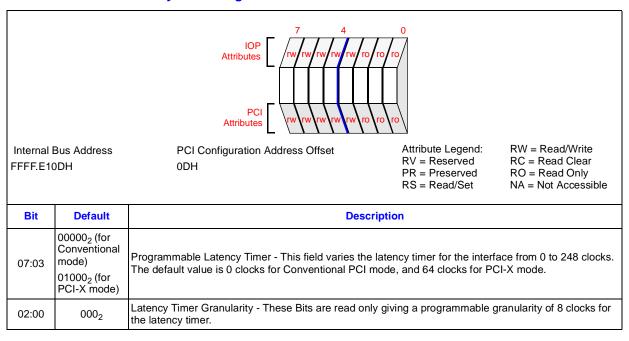

|     |         | 2.5.1.7                                     | Primary Latency Timer Register - PLTR                                  | 85              |  |  |  |

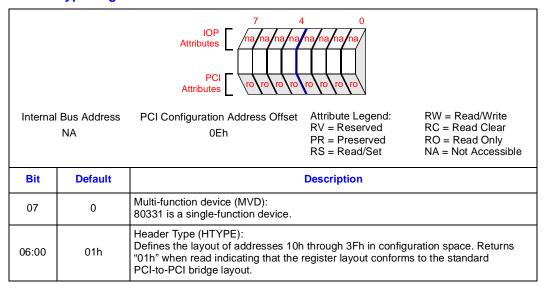

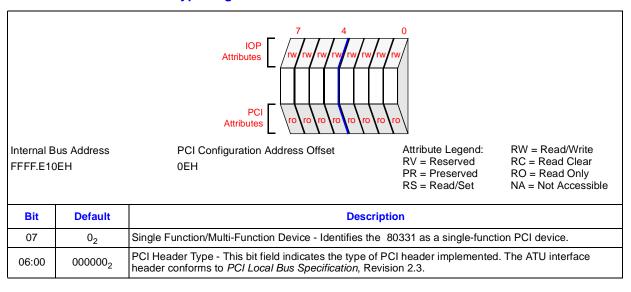

|     |         | 2.5.1.8                                     | Header Type Register - HTR                                             | 86              |  |  |  |

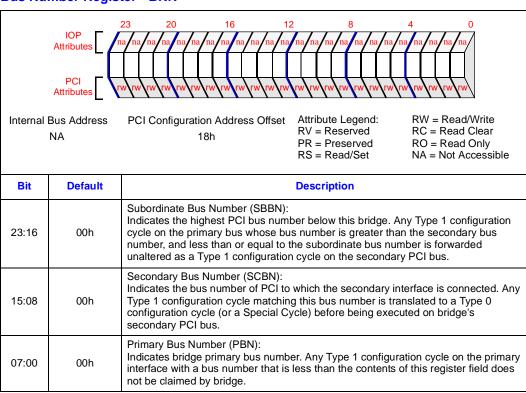

|     |         | 2.5.1.9                                     | Bus Number Register - BNR                                              |                 |  |  |  |

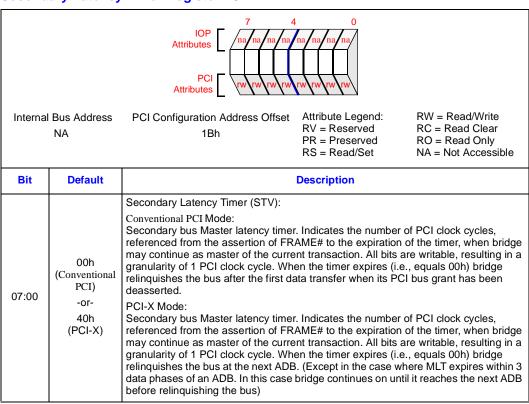

|     |         | 2.5.1.10                                    | , ,                                                                    |                 |  |  |  |

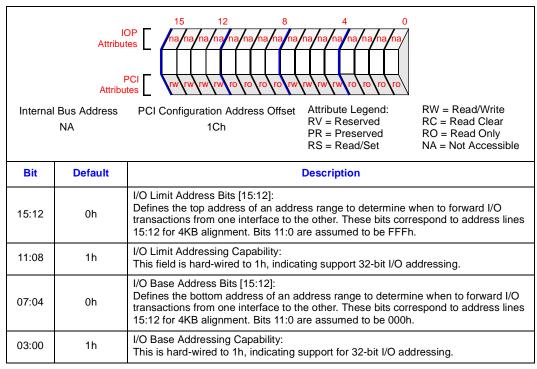

|     |         |                                             | I/O Base and Limit Register - IOBL                                     |                 |  |  |  |

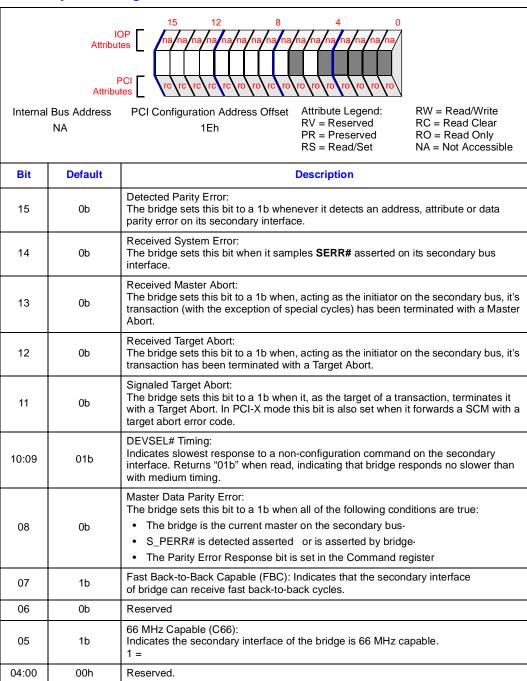

|     |         |                                             | Secondary Status Register - SSR                                        |                 |  |  |  |

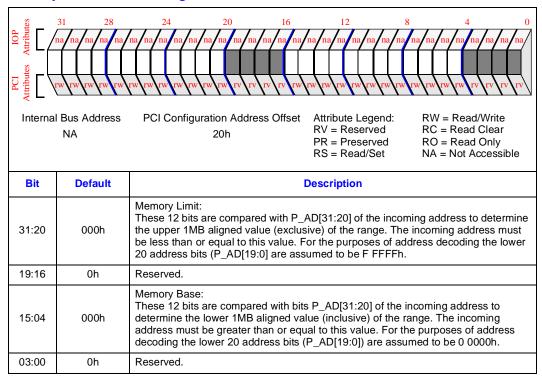

|     |         |                                             | Memory Base and Limit Register - MBL                                   |                 |  |  |  |

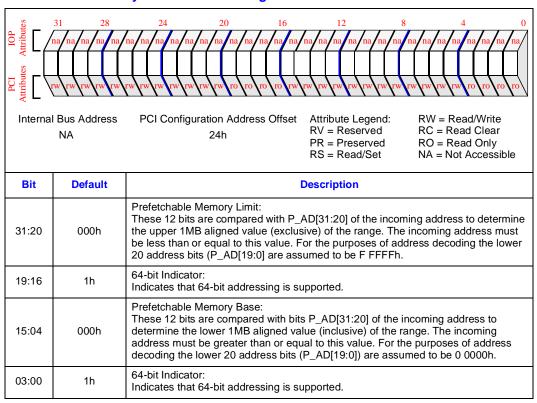

|     |         |                                             | Prefetchable Memory Base and Limit Register - PMBL                     |                 |  |  |  |

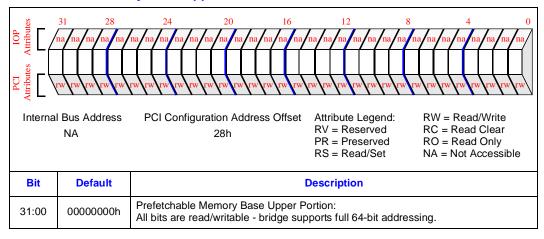

|     |         |                                             | Prefetchable Memory Base Upper 32 Bits - PMBU32                        |                 |  |  |  |

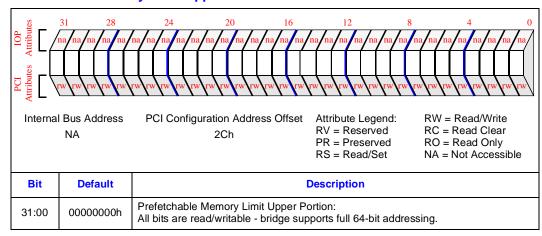

|     |         |                                             | Prefetchable Memory Limit Upper 32 Bits - PMLU32                       |                 |  |  |  |

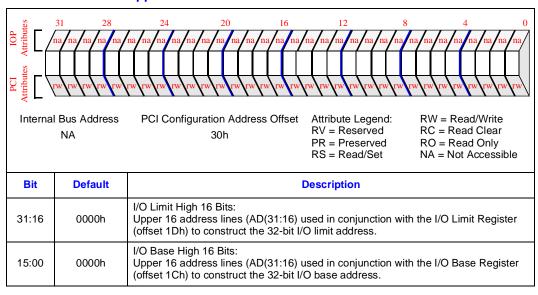

|     |         |                                             | I/O Base and Limit Upper 16 Bits - IOBLU16                             |                 |  |  |  |

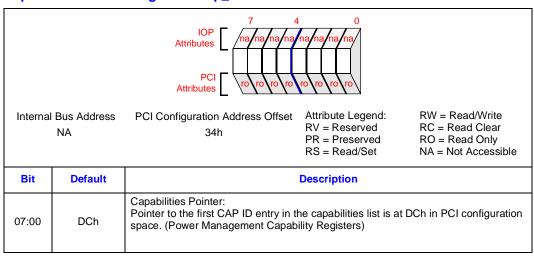

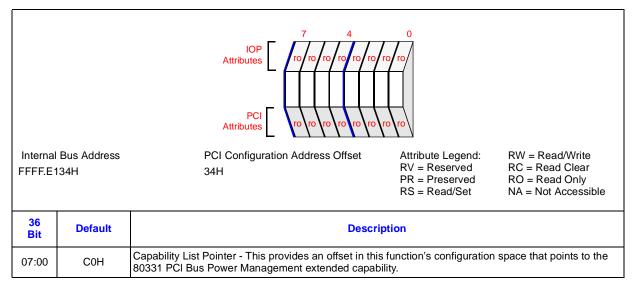

|     |         |                                             | Capabilities Pointer Register - Cap_Ptr                                |                 |  |  |  |

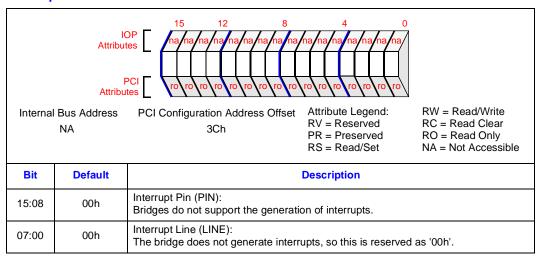

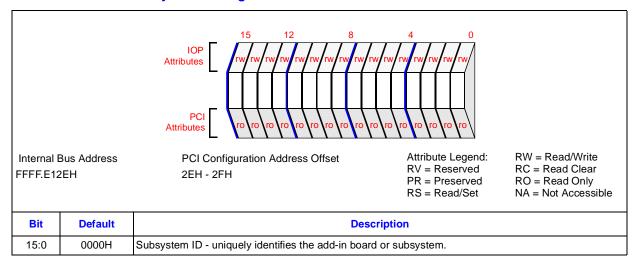

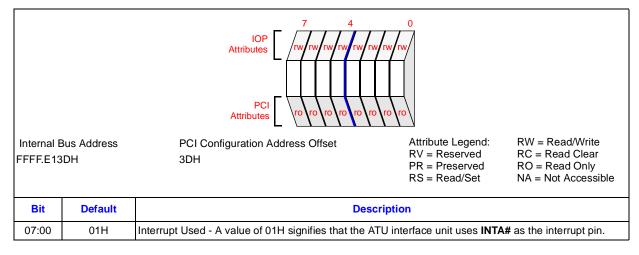

|     |         | 2.5.1.19                                    | Interrupt Information - INTR                                           | 91              |  |  |  |

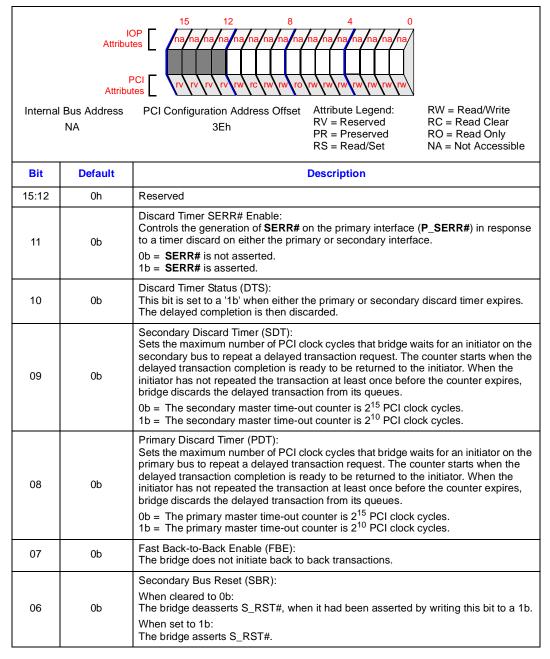

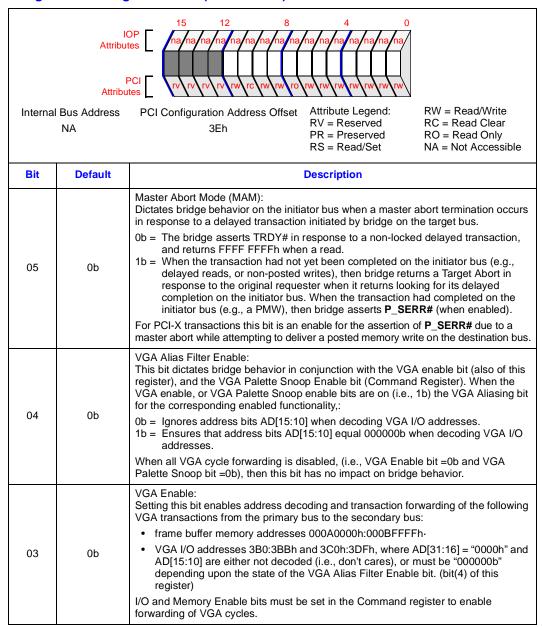

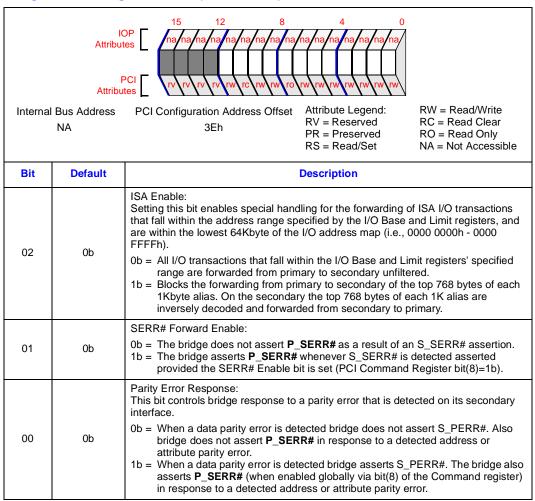

|     | 0.5.0   |                                             | Bridge Control Register - BCR                                          |                 |  |  |  |

|     | 2.5.2   |                                             | pecific Registers                                                      |                 |  |  |  |

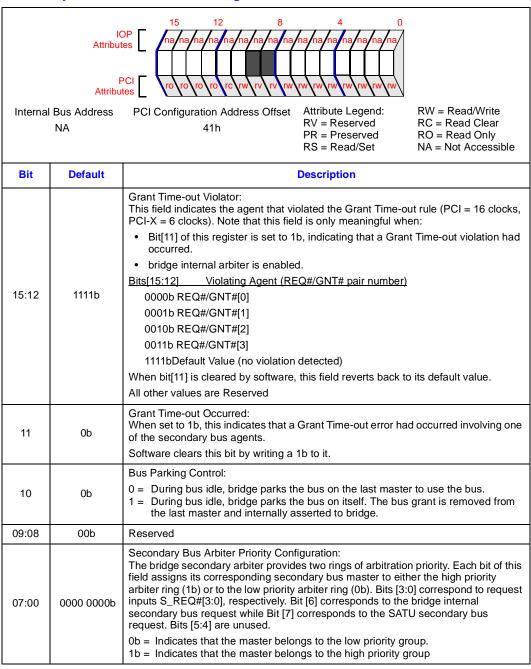

|     |         | 2.5.2.1                                     | Secondary Arbiter Control/Status Register - SACSR                      |                 |  |  |  |

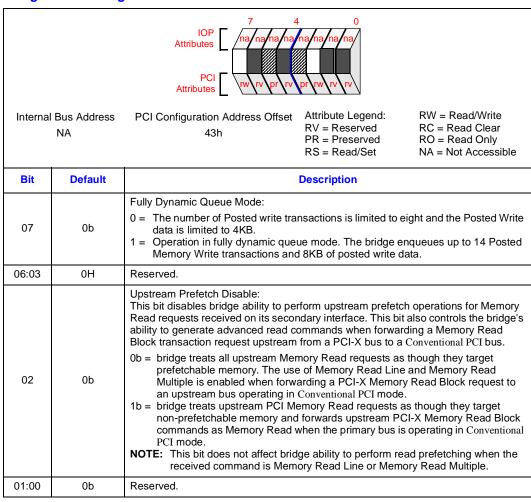

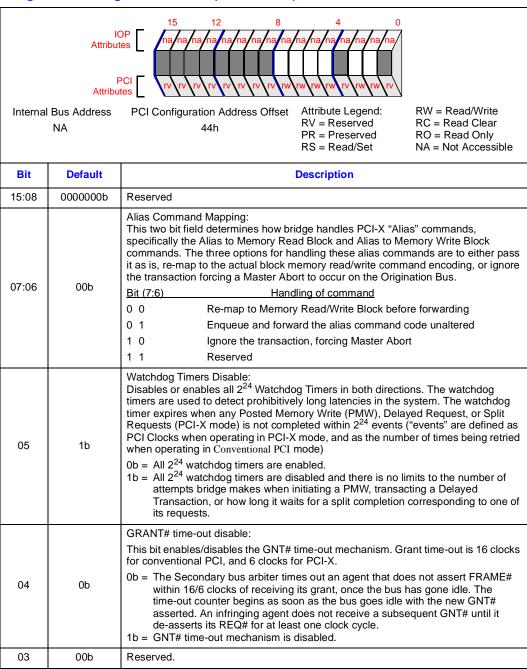

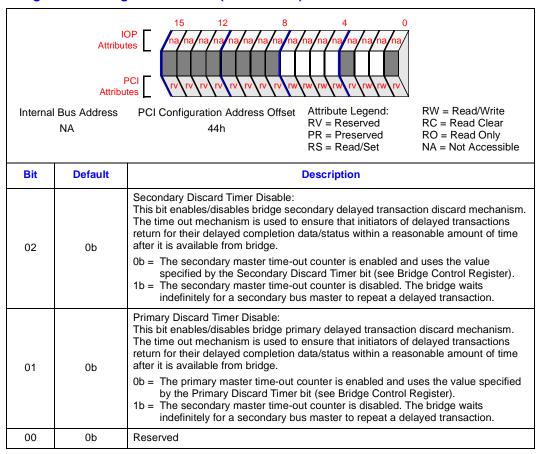

|     |         | 2.5.2.2                                     | Bridge Control Register 0 - BCR0                                       |                 |  |  |  |

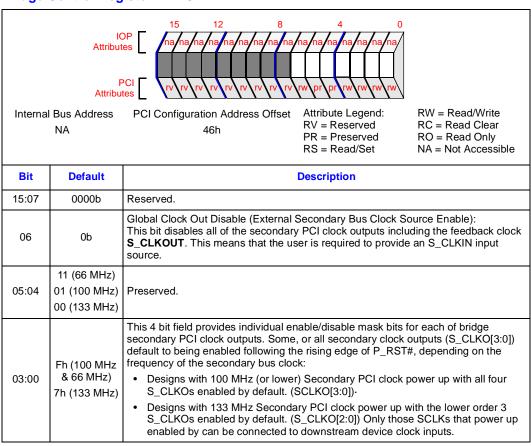

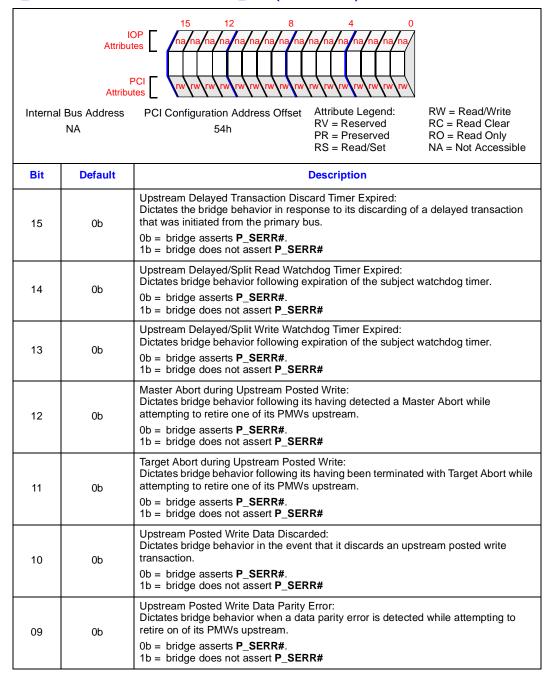

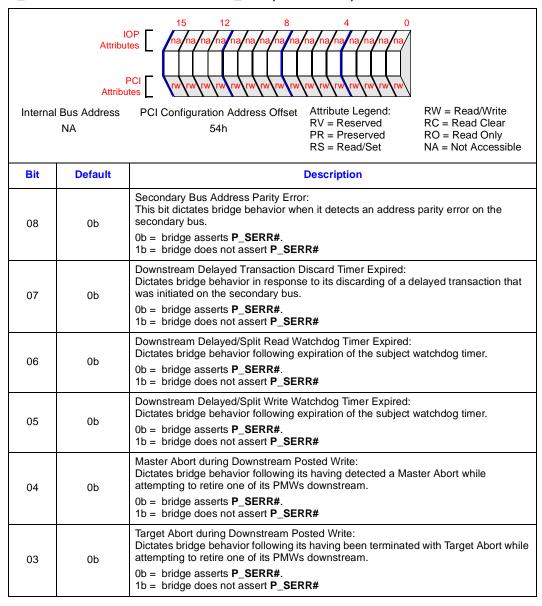

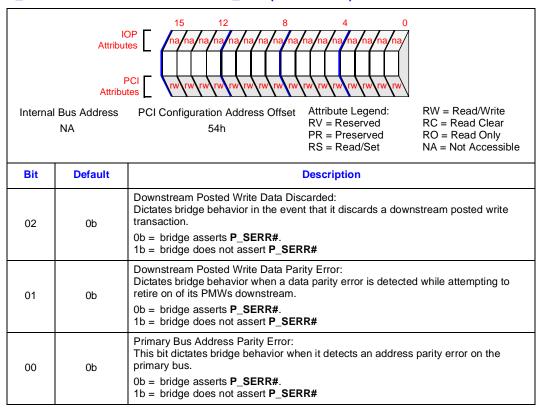

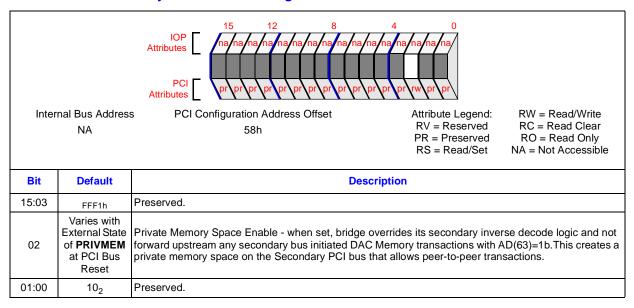

|     |         | 2.5.2.3                                     | Bridge Control Register 1 - BCR1                                       |                 |  |  |  |

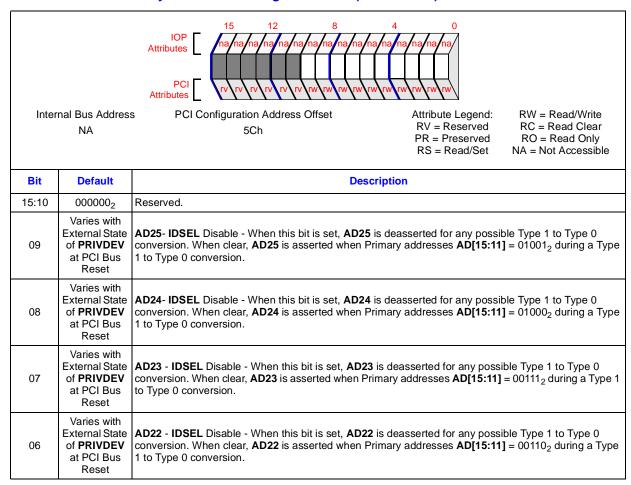

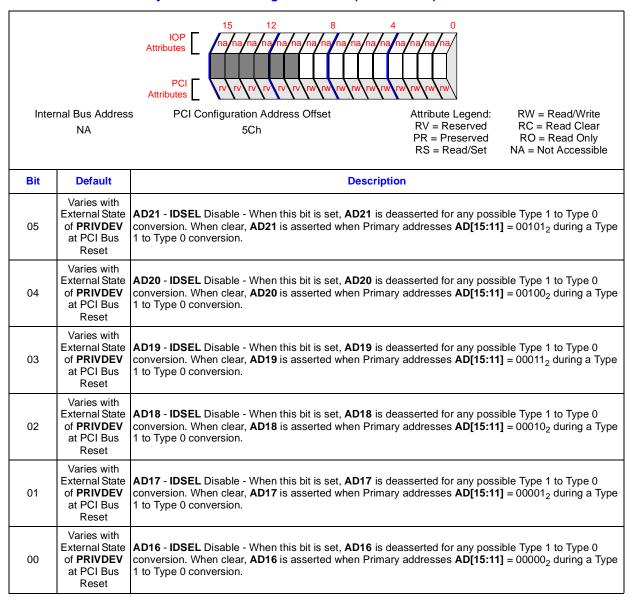

|     |         | 2.5.2.4                                     | Bridge Control Register 2 - BCR2                                       |                 |  |  |  |

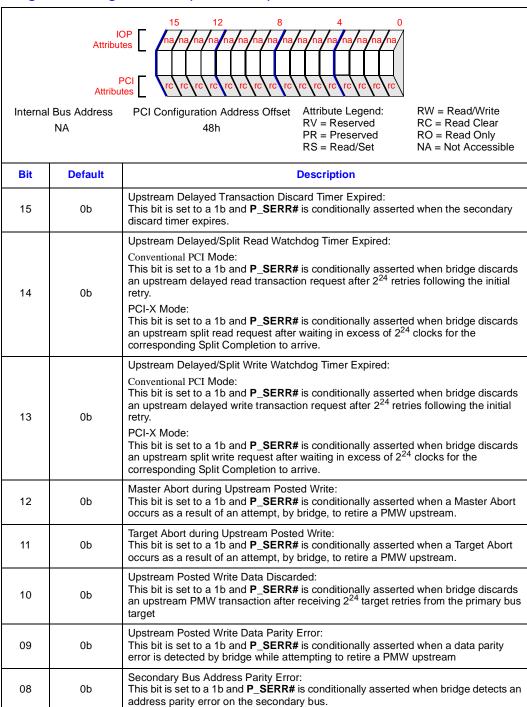

|     |         | 2.5.2.5                                     | Bridge Status Register - BSR                                           | 107             |  |  |  |

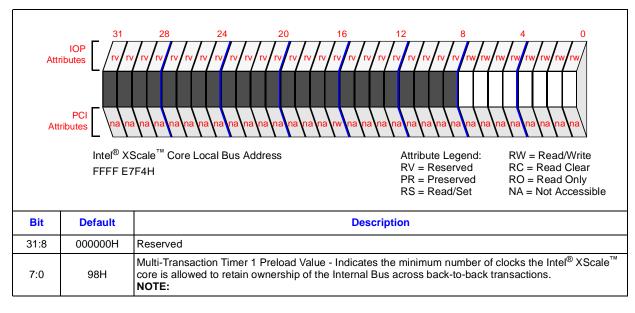

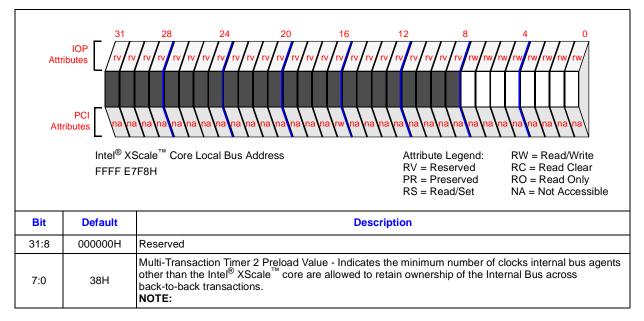

|     |         | 2.5.2.6                                     | Bridge Multi-Transaction Timer Register - BMTTR                        | 108             |  |  |  |

|     |         | 2.5.2.7                                     | Read Prefetch Policy Register - RPPR                                   |                 |  |  |  |

|     |         | 2.5.2.8<br>2.5.2.9                          | P_SERR# Assertion Control - SERR_CTL                                   | <u>/</u><br>115 |  |  |  |

|     |         | 2.5.2.9                                     | Pre-Boot Status Register - PBSRSecondary Decode Enable Register - SDER |                 |  |  |  |

|     |         | 2.5.2.10                                    |                                                                        |                 |  |  |  |

|     | 2.5.3   | -                                           | nded Capabilities List                                                 |                 |  |  |  |

|     | 2.5.5   |                                             |                                                                        |                 |  |  |  |

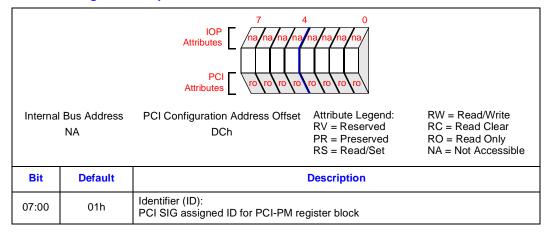

|     |         | 2.5.3.1                                     | PCI Bus Power Management                                               |                 |  |  |  |

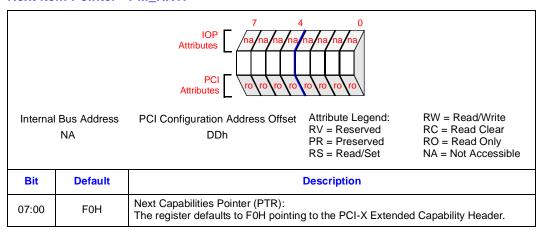

|     |         |                                             | 2.5.3.1.2 Next Item Pointer - PM_NXTP                                  |                 |  |  |  |

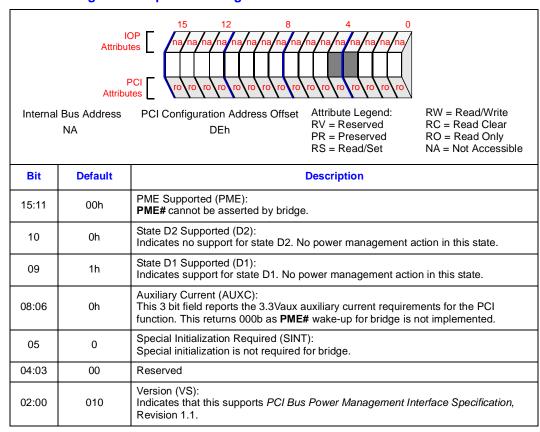

|     |         |                                             | 2.5.3.1.3 Power Management Capabilities Register - PMCR                |                 |  |  |  |

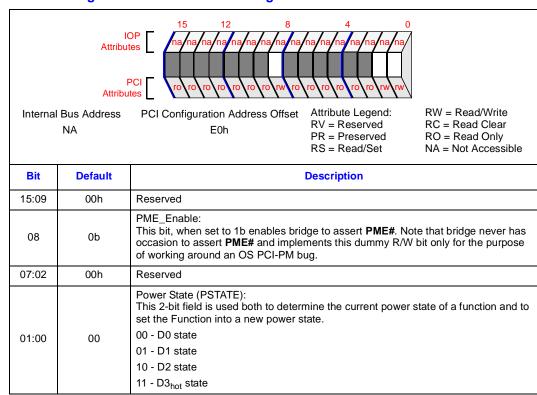

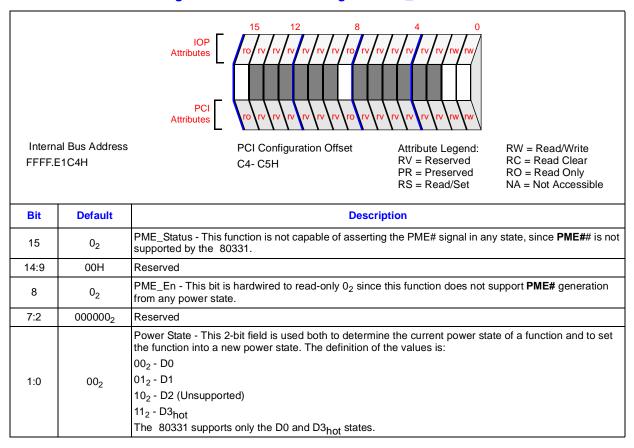

|     |         |                                             | 2.5.3.1.4 Power Management Control / Status Register - PMCSR           |                 |  |  |  |

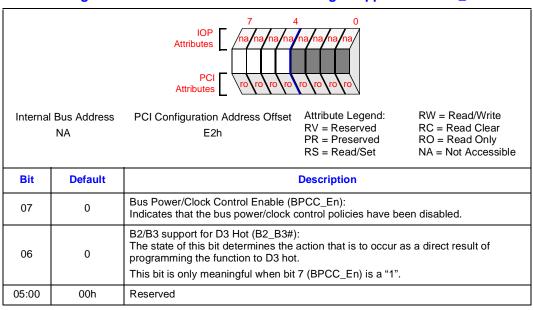

|     |         |                                             | 2.5.3.1.5 Power Management Control / Status PCI-to-PCI Bridge Sup      |                 |  |  |  |

|     |         |                                             | - PMCSR_BSE                                                            |                 |  |  |  |

|     |         |                                             | 2.5.3.1.6 Power Management Data Register - PMDR                        | 12              |  |  |  |

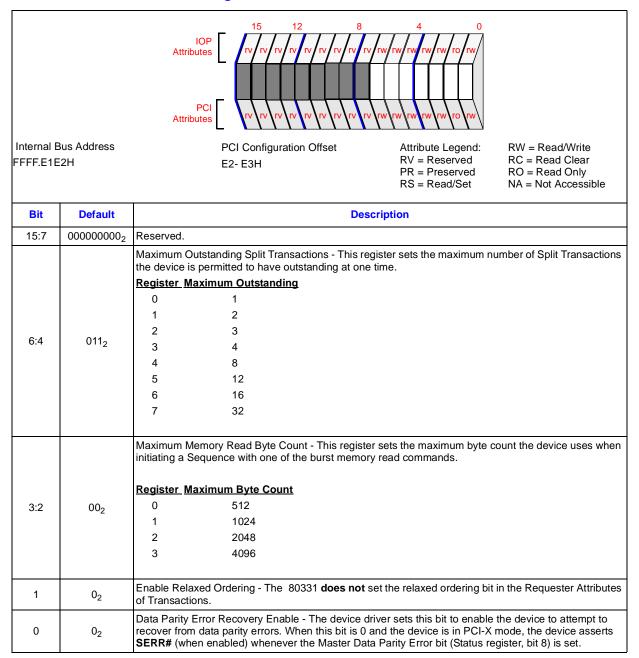

|     |         | 2.5.3.2                                     | PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0a.      |                 |  |  |  |

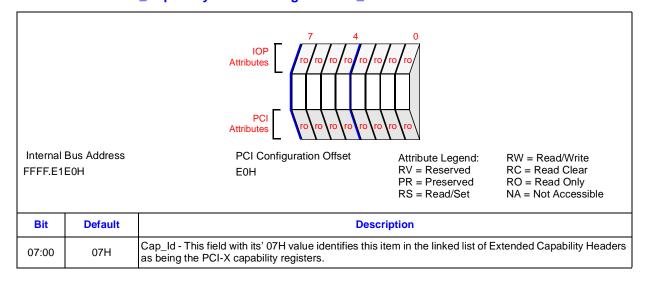

|     |         | 2.0.0.2                                     | 2.5.3.2.1 PCI-X Capabilities Identifier - PX_CAPID                     |                 |  |  |  |

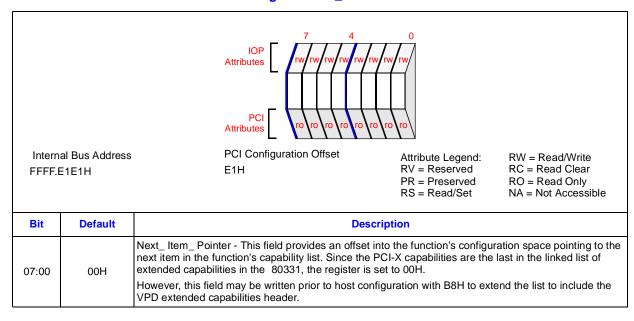

|     |         |                                             | 2.5.3.2.2 Next Item Pointer - PX_NXTP                                  | 127             |  |  |  |

|     |         |                                             | 2.5.3.2.3 PCI-X Secondary Status - PX_SSTS                             | . 128           |  |  |  |

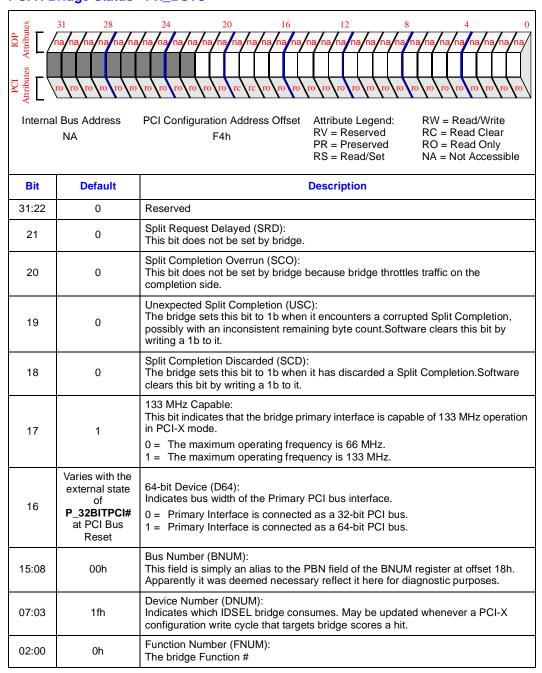

|     |         |                                             | 2.5.3.2.4 PCI-X Bridge Status - PX_BSTS                                |                 |  |  |  |

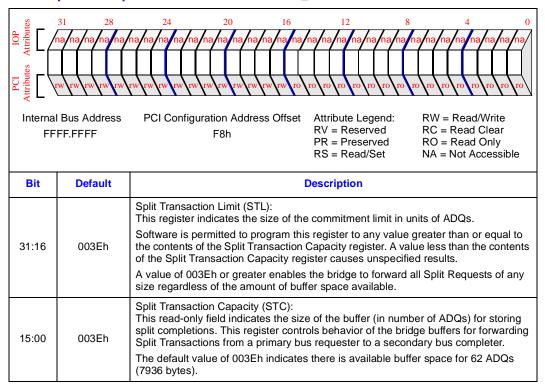

|     |         |                                             | 2.5.3.2.5 PCI-X Upstream Split Transaction Control - PX_USTC           | . 130           |  |  |  |

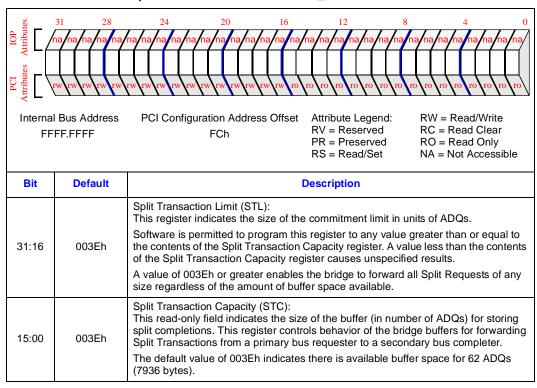

|     |         |                                             | 2.5.3.2.6 PCI-X Downstream Split Transaction Control - PX_DSTC         | 131             |  |  |  |

|     |         |                                             |                                                                        | -               |  |  |  |

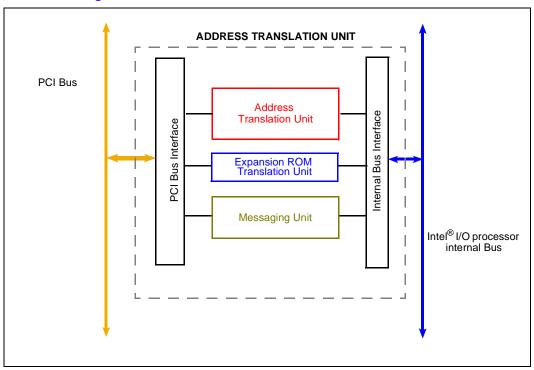

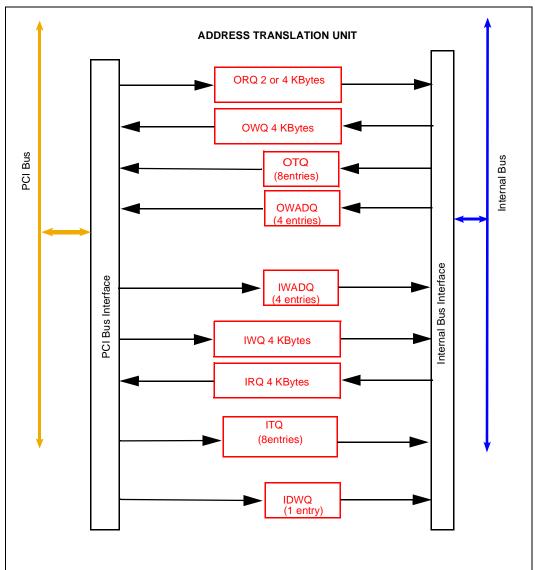

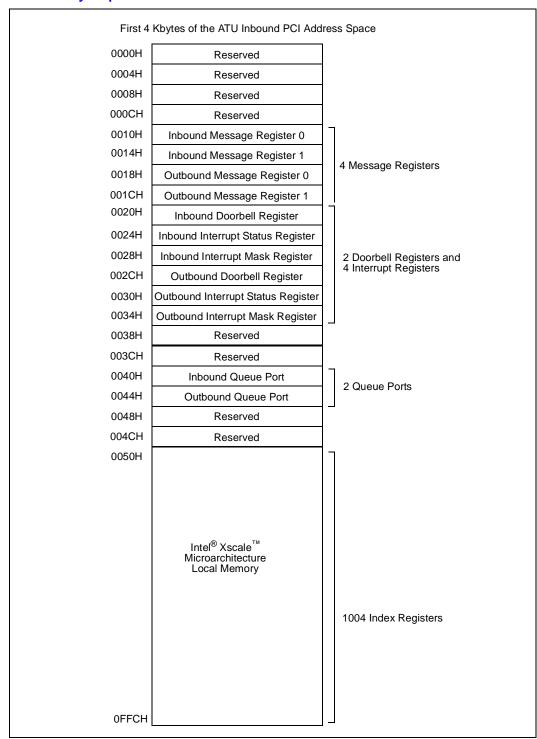

| 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3 | Addr | ess Tra | nslation l           | Jnit                                                         | 133 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|---------|----------------------|--------------------------------------------------------------|-----|

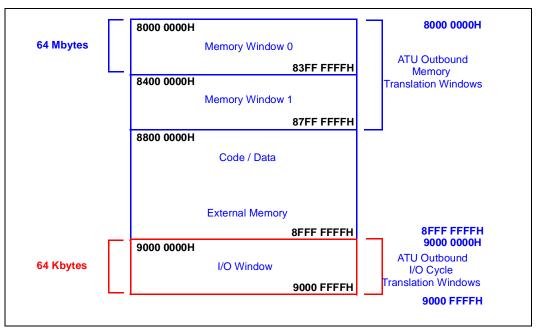

| 3.2. ATU Address Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 3.1  | Overvi  | ew                   |                                                              | 133 |

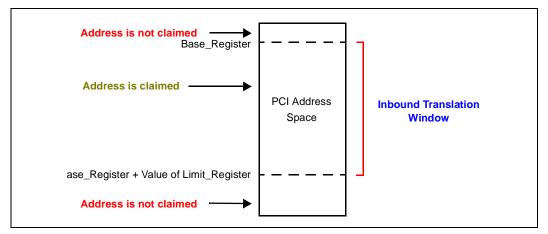

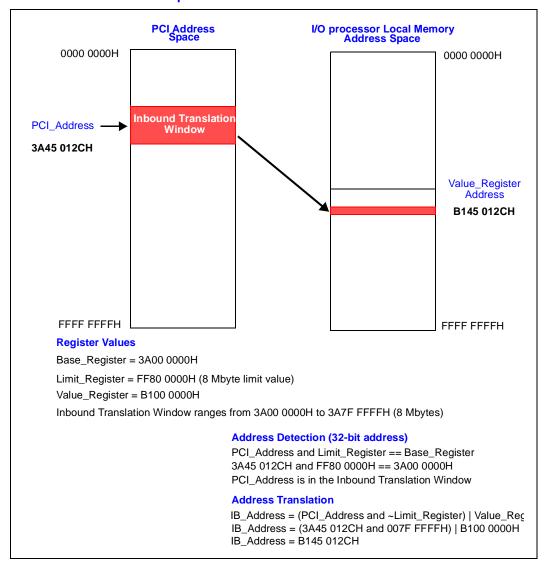

| 3.2.1.1 Inbound Address Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 3.2  |         |                      |                                                              |     |

| 3.2.1.1 Inbound Address Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      | 3.2.1   | Inbound              | Transactions                                                 | 138 |

| 3.2.1.2 Inbound Write Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |      |         |                      |                                                              |     |

| 3.2.1.4   Inbound Configuration Cycle Translation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      |         | 3.2.1.2              |                                                              |     |

| 3.2.1.5 Discard Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      |         | 3.2.1.3              | Inbound Read Transaction                                     | 144 |

| 3.2.2   Outbound Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |         | 3.2.1.4              | Inbound Configuration Cycle Translation                      | 147 |

| Internal Bus Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      |         | 3.2.1.5              | Discard Timers                                               | 148 |

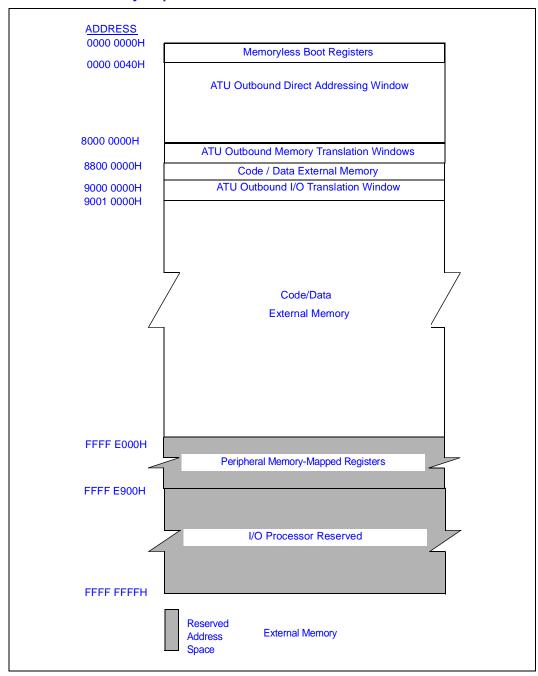

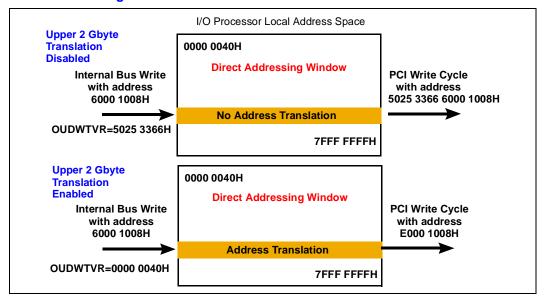

| Internal Bus Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      | 3.2.2   | Outbour<br>Internal  | nd Transactions- Single Address Cycle (SAC) Bus Transactions | 149 |

| Internal Bus Transactions   150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |         | 3.2.2.1              | Internal Bus Transactions                                    |     |

| (SAC) Transactions.       155         3.2.3 Outbound Write Transaction.       156         3.2.4 Outbound Write Transaction.       157         3.2.5 Outbound Configuration Cycle Translation.       160         3.3 Messaging Unit.       161         3.4 Expansion ROM Translation Unit       162         3.5 ATU Queue Architecture.       163         3.5.1 Inbound Queues       163         3.5.1.1 Inbound Write Queue Structure       163         3.5.1.2 Inbound Read Queue Structure       164         3.5.1.3 Inbound Delayed Write Queue.       165         3.5.1.4 Inbound Transaction Queues Command Translation Summary.       165         3.5.2 Outbound Queues       166         3.5.3 Transaction Ordering       167         3.5.3.1 Transaction Ordering Summary.       170         3.6.1 Private Device Control.       172         3.6.2 Private Memory Space       173         3.7.1 Address and Attribute Parity Errors on the PCI Interface       175         3.7.2 Data Parity Errors on the PCI Interface       176         3.7.2.1.1 Immediate Data Transfer       177         3.7.2.1.2 Split Response Termination       178         3.7.2.2 MSI Outbound Writes that are not MSI (Message Signaled Interrupts)       179         3.7.2.2.1 Inmediate Data Transfer<      |   |      |         | 3.2.2.2              | Internal Bus Transactions                                    |     |

| 3.2.2.4 Outbound DMA Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |      |         | 3.2.2.3              |                                                              | 155 |

| 3.2.4       Outbound Configuration Cycle Translation.       159         3.2.5       Outbound Configuration Cycle Translation.       160         3.3       Messaging Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      |         | 3.2.2.4              | Outbound DMA Transactions                                    | 156 |

| 3.2.5       Outbound Configuration Cycle Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      | 3.2.3   | Outbour              | nd Write Transaction                                         | 157 |

| 3.2.5 Outbound Configuration Cycle Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      | 3.2.4   | Outbour              | nd Read Transaction                                          | 159 |

| 3.3       Messaging Unit       161         3.4       Expansion ROM Translation Unit       162         3.5       ATU Queue Architecture       163         3.5.1       Inbound Queues       163         3.5.1.2       Inbound Write Queue Structure       164         3.5.1.3       Inbound Delayed Write Queue       165         3.5.1.4       Inbound Transaction Queues Command Translation Summary       165         3.5.2       Outbound Queues       166         3.5.3       Transaction Ordering       167         3.5.3       Transaction Ordering Summary       170         3.6       Private Device Control       172         3.6.1       Private Memory Space       173         3.7       ATU Error Conditions       174         3.7.1       Address and Attribute Parity Errors on the PCI Interface       175         3.7.2       Data Parity Errors on the PCI Interface       176         3.7.2.1       Outbound Read Request Data Parity Errors       177         3.7.2.1.1       Immediate Data Transfer       177         3.7.2.2.2       Outbound Writes that are not MSI (Message Signaled Interrupts)       178         3.7.2.2.1       Outbound Read Completions Data Parity Errors       181         3                                                                        |   |      | 3.2.5   |                      |                                                              |     |

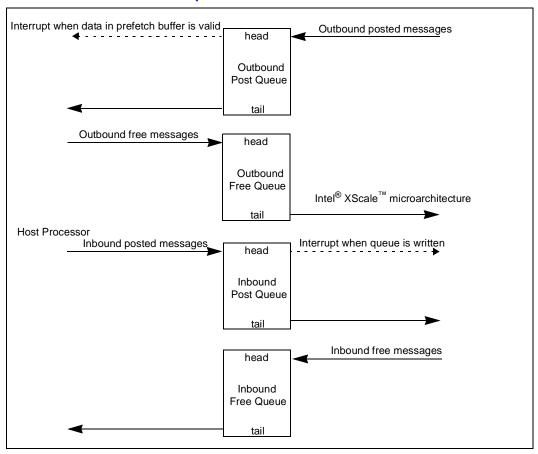

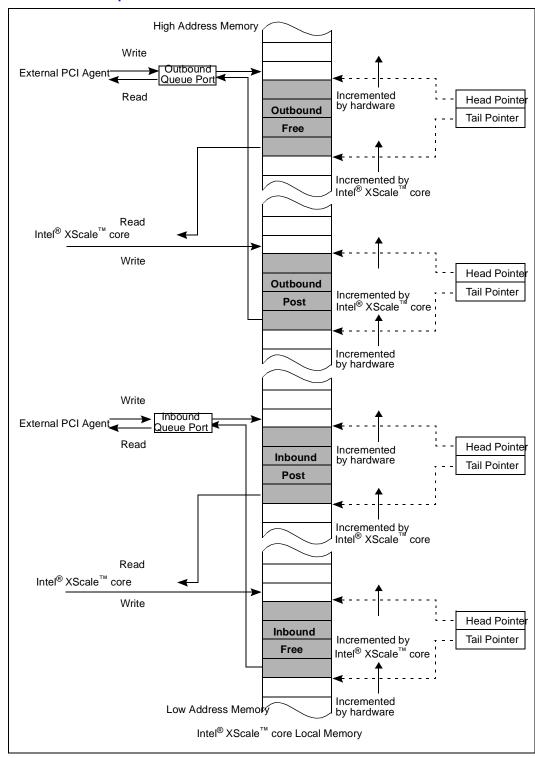

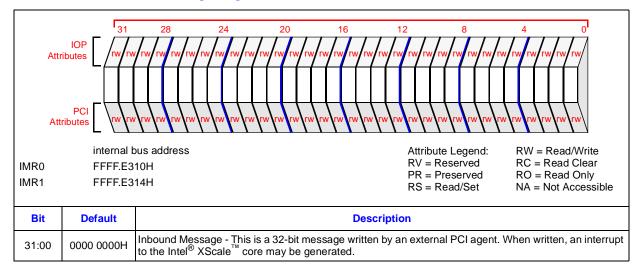

| 3.4       Expansion ROM Translation Unit       162         3.5       ATU Queue Architecture       163         3.5.1       Inbound Queues       163         3.5.1.2       Inbound Write Queue Structure       164         3.5.1.3       Inbound Pead Queue Structure       164         3.5.1.4       Inbound Delayed Write Queue       165         3.5.2       Outbound Queues       166         3.5.3       Transaction Ordering       167         3.5.3.1       Transaction Ordering Summary       170         3.6       Private Device Control       172         3.6.1       Private Type 0 Commands on the Secondary Interface       172         3.6.2       Private Memory Space       173         3.7       ATU Error Conditions       174         3.7.1       Address and Attribute Parity Errors on the PCI Interface       175         3.7.2       Data Parity Errors on the PCI Interface       176         3.7.2.1       Outbound Read Request Data Parity Errors       177         3.7.2.1.2       Split Response Termination       178         3.7.2.2.1       Outbound Write Request Data Parity Errors       179         3.7.2.2.2       MSI Outbound Writes that are not MSI       179         3.7.2.2.3 <td></td> <td>3.3</td> <td>Messa</td> <td></td> <td></td> <td></td>        |   | 3.3  | Messa   |                      |                                                              |     |

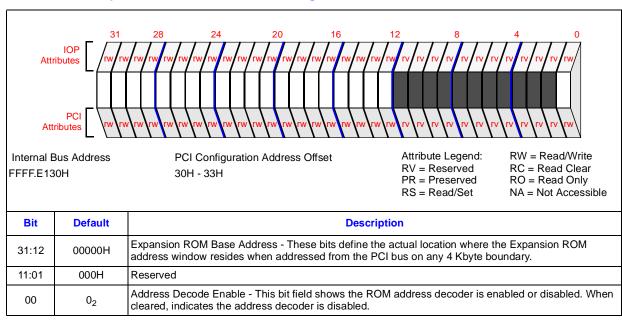

| 3.5       ATU Queue Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 3.4  |         |                      |                                                              |     |

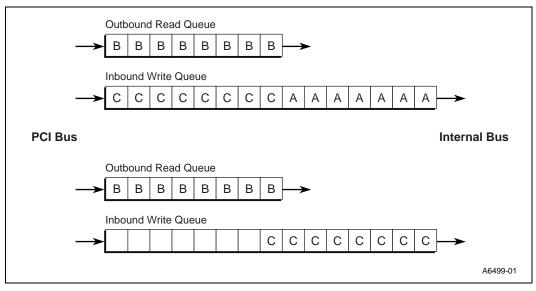

| 3.5.1.1 Inbound Write Queue Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 3.5  | •       |                      |                                                              |     |

| 3.5.1.1 Inbound Write Queue Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      | 3.5.1   | Inbound              | Queues                                                       | 163 |

| 3.5.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      |         |                      |                                                              |     |

| 3.5.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      |         | 3.5.1.2              |                                                              |     |

| 3.5.1.4   Inbound Transaction Queues Command Translation Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |      |         | 3.5.1.3              |                                                              |     |

| 3.5.3       Transaction Ordering Summary       170         3.6       Private Device Control       172         3.6.1       Private Type 0 Commands on the Secondary Interface       172         3.6.2       Private Memory Space       173         3.7       ATU Error Conditions       174         3.7.1       Address and Attribute Parity Errors on the PCI Interface       175         3.7.2       Data Parity Errors on the PCI Interface       176         3.7.2.1       Outbound Read Request Data Parity Errors       177         3.7.2.1.2       Split Response Termination       178         3.7.2.2.1       Outbound Write Request Data Parity Errors       179         3.7.2.2.1       Outbound Writes that are not MSI       (Message Signaled Interrupts)       179         3.7.2.2.2       MSI Outbound Writes       180         3.7.2.3       Inbound Read Completions Data Parity Errors       181         3.7.2.4       Inbound Configuration Write Completion Message Data Parity Errors 181         3.7.2.5       Inbound Read Request Data Parity Errors       181         3.7.2.5.1       Immediate Data Transfer       181         3.7.2.5.2       Split Response Termination       181         3.7.2.6       Inbound Write Request Data Parity Errors       181     <       |   |      |         | 3.5.1.4              | Inbound Transaction Queues Command Translation Summary       | 165 |

| 3.5.3.1   Transaction Ordering Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      | 3.5.2   | Outbour              | nd Queues                                                    | 166 |

| 3.6       Private Device Control       172         3.6.1       Private Type 0 Commands on the Secondary Interface       172         3.6.2       Private Memory Space       173         3.7       ATU Error Conditions       174         3.7.1       Address and Attribute Parity Errors on the PCI Interface       175         3.7.2       Data Parity Errors on the PCI Interface       176         3.7.2.1       Outbound Read Request Data Parity Errors       177         3.7.2.1.2       Split Response Termination       178         3.7.2.2.1       Outbound Write Request Data Parity Errors       179         3.7.2.2.1       Outbound Writes that are not MSI (Message Signaled Interrupts)       179         3.7.2.2.2       MSI Outbound Writes       180         3.7.2.3       Inbound Read Completions Data Parity Errors       181         3.7.2.4       Inbound Configuration Write Completion Message Data Parity Errors 181       181         3.7.2.5.1       Immediate Data Transfer       181         3.7.2.5.2       Split Response Termination       181         3.7.2.5.2       Split Response Termination       181         3.7.2.6       Inbound Write Request Data Parity Errors       181         3.7.2.7       Outbound Read Completion Data Parity Errors       182<  |   |      | 3.5.3   | Transac              | tion Ordering                                                | 167 |

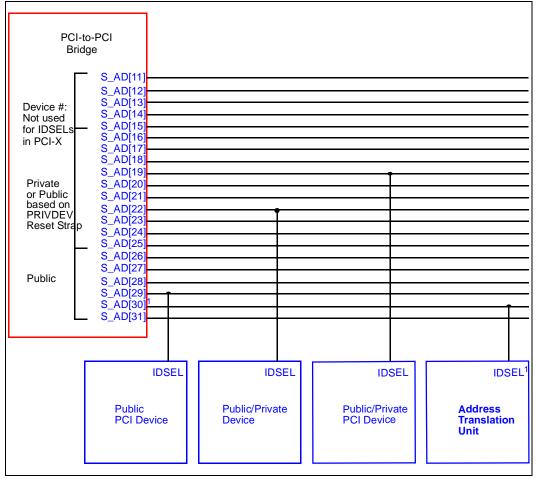

| 3.6.1       Private Type 0 Commands on the Secondary Interface       172         3.6.2       Private Memory Space       173         3.7       ATU Error Conditions       174         3.7.1       Address and Attribute Parity Errors on the PCI Interface       175         3.7.2       Data Parity Errors on the PCI Interface       176         3.7.2.1       Outbound Read Request Data Parity Errors       177         3.7.2.1.1 Immediate Data Transfer       177         3.7.2.2.2 Split Response Termination       178         3.7.2.2.1 Outbound Write Request Data Parity Errors       179         3.7.2.2.1 Outbound Writes that are not MSI       (Message Signaled Interrupts)       179         3.7.2.2.2 MSI Outbound Writes       180         3.7.2.3       Inbound Read Completions Data Parity Errors       181         3.7.2.4       Inbound Configuration Write Completion Message Data Parity Errors 181       181         3.7.2.5       Inbound Read Request Data Parity Errors       181         3.7.2.5.1 Immediate Data Transfer       181         3.7.2.6       Inbound Write Request Data Parity Errors       181         3.7.2.6       Inbound Read Completion Data Parity Errors       181         3.7.2.7       Outbound Read Completion Data Parity Errors       182 |   |      |         | 3.5.3.1              | Transaction Ordering Summary                                 | 170 |

| 3.6.2       Private Memory Space       173         3.7       ATU Error Conditions       174         3.7.1       Address and Attribute Parity Errors on the PCI Interface       175         3.7.2       Data Parity Errors on the PCI Interface       176         3.7.2.1       Outbound Read Request Data Parity Errors       177         3.7.2.1.1       Immediate Data Transfer       179         3.7.2.2.2       Outbound Write Request Data Parity Errors       179         3.7.2.2.1       Outbound Writes that are not MSI       (Message Signaled Interrupts)       179         3.7.2.2.2       MSI Outbound Writes       180         3.7.2.3       Inbound Read Completions Data Parity Errors       181         3.7.2.4       Inbound Configuration Write Completion Message Data Parity Errors 181       3.7.2.5         3.7.2.5.1       Immediate Data Transfer       181         3.7.2.5.2       Split Response Termination       181         3.7.2.6       Inbound Write Request Data Parity Errors       181         3.7.2.6       Inbound Write Request Data Parity Errors       181         3.7.2.7       Outbound Read Completion Data Parity Errors       182                                                                                                                    |   | 3.6  | Private | Device C             | Control                                                      | 172 |

| 3.6.2       Private Memory Space       173         3.7       ATU Error Conditions       174         3.7.1       Address and Attribute Parity Errors on the PCI Interface       175         3.7.2       Data Parity Errors on the PCI Interface       176         3.7.2.1       Outbound Read Request Data Parity Errors       177         3.7.2.1.1       Immediate Data Transfer       179         3.7.2.2.2       Outbound Write Request Data Parity Errors       179         3.7.2.2.1       Outbound Writes that are not MSI       (Message Signaled Interrupts)       179         3.7.2.2.2       MSI Outbound Writes       180         3.7.2.3       Inbound Read Completions Data Parity Errors       181         3.7.2.4       Inbound Configuration Write Completion Message Data Parity Errors 181       3.7.2.5         3.7.2.5.1       Immediate Data Transfer       181         3.7.2.5.2       Split Response Termination       181         3.7.2.6       Inbound Write Request Data Parity Errors       181         3.7.2.6       Inbound Write Request Data Parity Errors       181         3.7.2.7       Outbound Read Completion Data Parity Errors       182                                                                                                                    |   |      | 3.6.1   | Private <sup>-</sup> | Type 0 Commands on the Secondary Interface                   | 172 |

| 3.7       ATU Error Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      | 3.6.2   |                      |                                                              |     |

| 3.7.1       Address and Attribute Parity Errors on the PCI Interface       175         3.7.2       Data Parity Errors on the PCI Interface       176         3.7.2.1       Outbound Read Request Data Parity Errors       177         3.7.2.1.1 Immediate Data Transfer       178         3.7.2.2       Outbound Write Request Data Parity Errors       179         3.7.2.2.1 Outbound Writes that are not MSI       (Message Signaled Interrupts)       179         3.7.2.2.2 MSI Outbound Writes       180         3.7.2.3 Inbound Read Completions Data Parity Errors       181         3.7.2.4 Inbound Configuration Write Completion Message Data Parity Errors 181         3.7.2.5 Inbound Read Request Data Parity Errors       181         3.7.2.5.1 Immediate Data Transfer       181         3.7.2.5.2 Split Response Termination       181         3.7.2.6 Inbound Write Request Data Parity Errors       181         3.7.2.7 Outbound Read Completion Data Parity Errors       182                                                                                                                                                                                                                                                                                                     |   | 3.7  | ATU E   |                      |                                                              |     |

| 3.7.2       Data Parity Errors on the PCI Interface       176         3.7.2.1       Outbound Read Request Data Parity Errors       177         3.7.2.1.1 Immediate Data Transfer       177         3.7.2.1.2 Split Response Termination       178         3.7.2.2.2 Outbound Write Request Data Parity Errors       179         3.7.2.2.1 Outbound Writes that are not MSI       (Message Signaled Interrupts)       179         3.7.2.2.2 MSI Outbound Writes       180         3.7.2.3 Inbound Read Completions Data Parity Errors       181         3.7.2.4 Inbound Configuration Write Completion Message Data Parity Errors 181       3.7.2.5 Inbound Read Request Data Parity Errors       181         3.7.2.5.1 Immediate Data Transfer       181         3.7.2.5.2 Split Response Termination       181         3.7.2.6 Inbound Write Request Data Parity Errors       181         3.7.2.7 Outbound Read Completion Data Parity Errors       182                                                                                                                                                                                                                                                                                                                                           |   |      | 3.7.1   | Address              | and Attribute Parity Errors on the PCI Interface             | 175 |

| 3.7.2.1       Outbound Read Request Data Parity Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      | 3.7.2   |                      | · · · · · · · · · · · · · · · · · · ·                        |     |

| 3.7.2.1.1 Immediate Data Transfer       177         3.7.2.1.2 Split Response Termination       178         3.7.2.2 Outbound Write Request Data Parity Errors       179         3.7.2.2.1 Outbound Writes that are not MSI       179         (Message Signaled Interrupts)       179         3.7.2.2.2 MSI Outbound Writes       180         3.7.2.3 Inbound Read Completions Data Parity Errors       181         3.7.2.4 Inbound Configuration Write Completion Message Data Parity Errors 181       181         3.7.2.5 Inbound Read Request Data Parity Errors       181         3.7.2.5.1 Immediate Data Transfer       181         3.7.2.5 Split Response Termination       181         3.7.2.6 Inbound Write Request Data Parity Errors       181         3.7.2.7 Outbound Read Completion Data Parity Errors       182                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |         |                      |                                                              |     |

| 3.7.2.1.2 Split Response Termination       178         3.7.2.2.1 Outbound Write Request Data Parity Errors       179         3.7.2.2.1 Outbound Writes that are not MSI       (Message Signaled Interrupts)       179         3.7.2.2.2 MSI Outbound Writes       180         3.7.2.3 Inbound Read Completions Data Parity Errors       181         3.7.2.4 Inbound Configuration Write Completion Message Data Parity Errors 181         3.7.2.5 Inbound Read Request Data Parity Errors       181         3.7.2.5.1 Immediate Data Transfer       181         3.7.2.5.2 Split Response Termination       181         3.7.2.6 Inbound Write Request Data Parity Errors       181         3.7.2.7 Outbound Read Completion Data Parity Errors       182                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      |         |                      |                                                              |     |

| 3.7.2.2.1 Outbound Writes that are not MSI (Message Signaled Interrupts)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      |         |                      |                                                              |     |

| (Message Signaled Interrupts)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |         | 3.7.2.2              | Outbound Write Request Data Parity Errors                    | 179 |

| 3.7.2.22 MSI Outbound Writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      |         |                      |                                                              |     |

| 3.7.2.3 Inbound Read Completions Data Parity Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      |         |                      | (Message Signaled Interrupts)                                | 179 |