# intel®

# Intel<sup>®</sup> IQ80331 I/O Processor Evaluation Platform

Board Manual - DDR-II 400 MHz SDRAM

September 2004

Document Number: 273948-004US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 80331 I/O Processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright© Intel Corporation, September 2004

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, Commerce Cart, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetStructure, Intel Play, Intel Play logo, Intel Pocket Concert, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel WebOutfitter, Intel Xeon, Intel XScale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo, NetPort, NetportExpress, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, ProShare, RemoteExpress, Screamline, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, This Way In, TokenExpress, Trillium, Vivonic, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

ARM\* and ARM Powered logo marks (the ARM marks) are trademarks of ARM, Ltd., and Intel uses these marks under license from ARM, Ltd. \*Other names and brands may be claimed as the property of others.

| 1 | Intro      | duction                                                                          | 9  |

|---|------------|----------------------------------------------------------------------------------|----|

|   | 1.1<br>1.2 | Document Purpose and Scope                                                       |    |

|   | 1.3        | Electronic Information                                                           |    |

|   | 1.4        | Component References                                                             |    |

|   | 1.5        | Terms and Definitions                                                            |    |

|   | 1.6        | Intel <sup>®</sup> 80331 I/O Processor                                           |    |

|   | 1.7        | Intel <sup>®</sup> IQ80331 I/O Processor Evaluation Platform Board Features      |    |

| 2 | Getti      | ing Started                                                                      | 15 |

|   | 2.1        | Kit Contents                                                                     | 15 |

|   | 2.2        | Hardware Installation                                                            | 15 |

|   |            | 2.2.1 First-Time Installation and Test                                           | 15 |

|   |            | 2.2.2 Power and Backplane Requirements                                           |    |

|   | 2.3        | Factory Settings                                                                 |    |

|   | 2.4        | Development Strategy                                                             |    |

|   |            | 2.4.1 Supported Tool Buckets                                                     |    |

|   |            | 2.4.2 Contents of the Flash                                                      |    |

|   | 2.5        | Target Monitors                                                                  |    |

|   | -          | 2.5.1 Red Hat RedBoot                                                            |    |

|   | 2.6        | Host Communications Examples                                                     |    |

|   |            | 2.6.1 Serial-UART Communication                                                  |    |

|   |            | 2.6.2 JTAG Debug Communication                                                   |    |

|   |            | 2.6.3 Ethernet Communication                                                     |    |

|   |            | 2.6.4 GNUPro GDB/Insight                                                         |    |

|   |            | 2.6.4.1 Communicating with RedBoot                                               |    |

|   |            | 2.6.4.2 Connecting with GDB                                                      |    |

| 3 | Hard       | Iware Reference Section                                                          | 23 |

|   | 3.1        | Functional Diagram                                                               | 23 |

|   | 3.2        | Board Form-Factor/Connectivity                                                   |    |

|   | 3.3        | Power                                                                            |    |

|   | 3.4        | Memory Subsystem                                                                 | 25 |

|   |            | 3.4.1 DDRII SDRAM                                                                |    |

|   |            | 3.4.1.1 Battery Backup                                                           |    |

|   |            | 3.4.2 Flash Memory Requirements                                                  |    |

|   | 3.5        | Interrupt Routing                                                                |    |

|   | 3.6        | Intel <sup>®</sup> Q80331 I/O Processor Evaluation Platform Board Peripheral Bus |    |

|   |            | 3.6.1 Flash ROM                                                                  |    |

|   |            | 3.6.2 UART                                                                       |    |

|   |            | 3.6.3 Non-Volatile RAM                                                           | 29 |

|   |            | 3.6.4 Audio Buzzer                                                               |    |

|   |            | 3.6.5 HEX Display                                                                |    |

|   |            | 3.6.6 Rotary Switch                                                              |    |

|   |            | 3.6.7 Battery Status                                                             |    |

|   | 3.7        | Debug Interface                                                                  |    |

|   |        | 3.7.1          |                       |           |                                                                  |      |

|---|--------|----------------|-----------------------|-----------|------------------------------------------------------------------|------|

|   |        | 3.7.2          |                       |           |                                                                  |      |

|   | 0.0    |                | 3.7.2.1               |           |                                                                  |      |

|   | 3.8    |                |                       |           |                                                                  |      |

|   | 3.9    |                |                       | •         |                                                                  |      |

|   |        | 3.9.1          |                       |           | an Viewel                                                        |      |

|   |        | 3.9.2          |                       |           | gs - Visual                                                      |      |

|   |        | 3.9.3<br>3.9.4 | •                     | •         |                                                                  |      |

|   |        | 3.9.4<br>3.9.5 |                       |           | ut/Output Header                                                 |      |

|   |        | 3.9.5<br>3.9.6 |                       |           | f Switches/Jumpers                                               |      |

|   |        | 5.9.0          | 3.9.6.1               |           | C1                                                               |      |

|   |        |                | 5.9.0.1               | 3.9.6.1.1 | S7C1-1: SECONDARY BUS SPEED -                                    | . 55 |

|   |        |                |                       | 0.0.0.1.1 | associated net PD_PBI_AD3                                        | 35   |

|   |        |                |                       | 3.9.6.1.2 | S7C1-2: RESET - associated net PD_AD5                            | .35  |

|   |        |                |                       | 3.9.6.1.3 | S7C1-3: RETRY - associated net PD_AD6                            | .35  |

|   |        |                |                       | 3.9.6.1.4 | S7C1-4: BRIDGE ENABLE - associated net PD_AD0                    | .35  |

|   |        |                |                       | 3.9.6.1.5 | Switch S7C1- 5: PRIVATE DEVICES -                                |      |

|   |        |                |                       |           | associated net PD_A0                                             | .36  |

|   |        |                |                       | 3.9.6.1.6 | Switch S7C1 - 6: PRIVATE MEMORY -                                | ~~   |

|   |        |                |                       | 3.9.6.1.7 | associated net PD_A1<br>Switch S7C1 - 7: PRIMARY PCI BUS WIDTH - | .36  |

|   |        |                |                       | 5.9.0.1.7 | associated net PD_PBI_A2                                         | 36   |

|   |        |                |                       | 3.9.6.1.8 | Switch S7C1- 8/9                                                 |      |

|   |        |                |                       | 3.9.6.1.9 | Switch S7C1- 10: FLASH WIDTH - associated net P3_3V              |      |

|   |        |                | 3.9.6.2               |           | B1- UART U1 RXD ENABLE                                           |      |

|   |        |                | 3.9.6.3               | Jumper J1 | B2 - JTAG COMMUNICATION OPTIONS                                  | .38  |

|   |        |                | 3.9.6.4               | Jumper J1 | D2 - UART TRANSCEIVER ENABLE                                     | . 38 |

|   |        |                | 3.9.6.5               | Jumper J9 | C1 - BUZZER VOLUME                                               | . 39 |

| 4 | Softw  | are Ref        | erence                |           |                                                                  | .40  |

|   | 4.1    | DRAM           |                       |           |                                                                  | 40   |

|   | 4.2    |                |                       |           | al Bus                                                           |      |

|   | 7.2    | 4.2.1          |                       | •         |                                                                  |      |

|   |        | 4.2.2          |                       |           | ory Map                                                          |      |

|   | 4.3    |                |                       |           | P) Examples                                                      |      |

|   |        | 4.3.1          |                       |           | cessor Memory Map                                                |      |

|   |        | 4.3.2          | Intel <sup>®</sup> IQ | 80331 Mem | ory Map for RedBoot                                              | .44  |

|   |        | 4.3.3          |                       |           | for RedBoot                                                      |      |

|   |        | 4.3.4          | Intel <sup>®</sup> IQ | 80331 DDR | Memory Initialization Sequence for RedBoot                       | .46  |

| Α | IQ803  | 21 and         |                       |           | ıs                                                               |      |

| в | Gettir | ng Starte      | ed and De             | ebugger   |                                                                  | .50  |

|   | B.1    | Introdu        | ction                 |           |                                                                  | .50  |

|   | -      | B.1.1          |                       |           |                                                                  |      |

|   |        | B.1.2          |                       |           | and Software                                                     |      |

|   |        | -              | B.1.2.1               | •         | Information                                                      |      |

|   |        | B.1.3          |                       |           |                                                                  |      |

|   | B.2    |                |                       |           |                                                                  |      |

|   |        | В.2.1          |                       |           |                                                                  |      |

|   |        | B.2.2          |                       | •         |                                                                  |      |

# intel

| B.3 | New P   | roject Setup                                          | 54 |

|-----|---------|-------------------------------------------------------|----|

|     | B.3.1   | Creating a New Project                                | 54 |

|     | B.3.2   | Configuration                                         | 55 |

| B.4 | Flashir | ng with JTAG                                          | 56 |

|     | B.4.1   | Overview                                              | 56 |

|     | B.4.2   | Using Flash Programmer                                | 57 |

| B.5 |         | ging Out of Flash                                     |    |

| B.6 | Buildin | g an Executable File From Example Code                | 59 |

| B.7 | Runnir  | ng the Code Lab Debugger                              | 60 |

|     | B.7.1   | Launching and Configuring Debugger                    |    |

|     | B.7.2   | Manually Loading and Executing an Application Program | 60 |

|     | B.7.3   | Displaying Source Code                                |    |

|     | B.7.4   | Using Breakpoints                                     | 61 |

|     | B.7.5   | Stepping Through the Code                             | 62 |

|     | B.7.6   | Setting Code Lab Debug Options                        |    |

| B.8 | Explor  | ing the Code Lab Debug Windows                        |    |

|     | B.8.1   | Toolbar Icons                                         |    |

|     | B.8.2   | Workspace Window                                      |    |

|     | B.8.3   | Source Code                                           |    |

|     | B.8.4   | Four Debug and Console Windows                        |    |

|     | B.8.5   | Memory Window                                         |    |

|     | B.8.6   | Registers Window                                      |    |

|     | B.8.7   | Watch Window                                          |    |

|     | B.8.8   | Variables Window                                      |    |

| B.9 | Debug   | ging Basics                                           | 65 |

|     | B.9.1   | Overview                                              |    |

|     | B.9.2   | Hardware and Software Breakpoints                     |    |

|     |         | B.9.2.1 Software Breakpoints                          |    |

|     |         | B.9.2.2 Hardware Breakpoints                          |    |

|     | B.9.3   | C.9.3 Exceptions/Trapping                             | 66 |

# Figures

| 1  | Intel <sup>®</sup> 80331 I/O Processor Block Diagram                                       | 13 |

|----|--------------------------------------------------------------------------------------------|----|

| 2  | Serial-UART Communication                                                                  |    |

| 3  | JTAG Debug Communication                                                                   | 18 |

| 4  | Communication via Ethernet                                                                 | 19 |

| 5  | Functional Block Diagram                                                                   | 23 |

| 6  | Board Form Factor                                                                          | 24 |

| 7  | Intel <sup>®</sup> IQ80331 I/O Processor Evaluation Platform Board Peripheral Bus Topology | 27 |

| 8  | Flash Connection on Peripheral Bus                                                         | 28 |

| 9  | JTAG Port Pin-out                                                                          |    |

| 10 | RESET Sources                                                                              | 32 |

| 11 | Default Switch Settings                                                                    |    |

| 12 | Flash Connection to Peripheral Bus                                                         | 41 |

| 13 | Intel <sup>®</sup> 80331 I/O Processor Memory Map                                          | 43 |

| 14 | Intel <sup>®</sup> 80331 I/O Processor Hardware Setup Flow Chart                           | 52 |

| 15 | Software Flow Diagram                                                                      |    |

|    |                                                                                            |    |

# Tables

| 1  | Intel <sup>®</sup> 80331 I/O Processor Related Documentation List                                             | 9  |

|----|---------------------------------------------------------------------------------------------------------------|----|

| 2  | Electronic Information                                                                                        | 9  |

| 3  | Component Reference                                                                                           | 10 |

| 4  | Terms and Definitions                                                                                         | 11 |

| 5  | Summary of Features                                                                                           |    |

| 6  | Form-Factor/Connectivity Features                                                                             | 24 |

| 7  | Power Features                                                                                                | 24 |

| 8  | Flash Memory Requirements                                                                                     |    |

| 9  | External Interrupt Routing to Intel <sup>®</sup> 80331 I/O Processor                                          | 26 |

| 10 | Peripheral Bus Features                                                                                       | 27 |

| 11 | Flash ROM Features                                                                                            | 28 |

| 12 | Rotary Switch Requirements                                                                                    | 29 |

| 13 | Battery Status Buffer Requirements                                                                            |    |

| 14 | Reset Requirements/Schemes                                                                                    | 32 |

| 15 | Switch Summary                                                                                                |    |

| 16 | Switch S7C1                                                                                                   |    |

| 17 | Jumper Summary                                                                                                |    |

| 18 | Connector Summary                                                                                             |    |

| 19 | GPIO Header Definition                                                                                        |    |

| 20 | S7C1-1: SECONDARY BUS SPEED: Settings and Operation Mode                                                      |    |

| 21 | Switch S7C1-2: RESET: Settings and Operation Mode                                                             |    |

| 22 | Switch S7C1-3: RETRY: Settings and Operation Mode                                                             |    |

| 23 | S7C1-4: BRIDGE ENABLE: Settings and Operation Mode                                                            |    |

| 24 | Switch S7C1- 5: PRIVATE DEVICES: Settings and Operation Mode                                                  |    |

| 25 | Switch S7C1 - 6: PRIVATE MEMORY: Settings and Operation Mode                                                  |    |

| 26 | Switch S7C1 - 7: PRIMARY PCI BUS WIDTH: Settings and Operation Mode                                           |    |

| 27 | Switch S7C1 - 10: FLASH WIDTH: Settings and Operation Mode                                                    |    |

| 28 | Jumper J1B1: Descriptions                                                                                     |    |

| 29 | Jumper J1B1: Settings and Operation Mode                                                                      |    |

| 30 | Jumper J1B2: Descriptions                                                                                     | 38 |

| 31 | Jumper J1B2: Settings and Operation Mode                                                                      |    |

| 32 | Jumper J1D2: Descriptions                                                                                     |    |

| 33 | Jumper J1D2: Settings and Operation Mode                                                                      |    |

| 34 | Jumper J9C1: Descriptions                                                                                     |    |

| 35 | Jumper J9C1: Settings and Operation Mode                                                                      |    |

| 36 | Peripheral Bus Memory Map                                                                                     |    |

| 37 | Intel <sup>®</sup> IQ80310 and Intel <sup>®</sup> IQ80331 I/O Processor Evaluation Platform Board Comparisons |    |

| 38 | Related Documents                                                                                             | 51 |

# **Revision History**

| Date           | Revision | Description                                                   |

|----------------|----------|---------------------------------------------------------------|

| September 2004 | 004      | Updated Switch and Jumper settings, Various Typo corrections. |

| April 2004     | 003      | Revised for DDR-II 400 MHz SDRAM feature.                     |

| April 2004     | 002      | Revised Appendix B.                                           |

| December 2003  | 001      | Initial Release.                                              |

# Introduction

1

# 1.1 Document Purpose and Scope

This document describes the Intel<sup>®</sup> IQ80331 I/O processor evaluation platform board (IQ80331) using DDR-II 400 MHz SDRAM. The IQ80331 is intended for rapid intelligent I/O development. The design is based on the Intel<sup>®</sup> 80331 I/O processor (80331), which is a multi-function device, that integrates the Intel XScale<sup>®</sup> core (ARM\* architecture compliant) with intelligent peripherals, including a PCI bus application bridge. For more information on the 80331, please see <a href="http://developer.intel.com/design/iio/iop331.htm">http://developer.intel.com/design/iio/iop331.htm</a>.

# 1.2 Related Documents

### Table 1. Intel<sup>®</sup> 80331 I/O Processor Related Documentation List

| Document                                                                                                    | Number                                |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Intel <sup>®</sup> 80331 I/O Processor Developer's Manual                                                   | 273942                                |

| Intel <sup>®</sup> 80331 I/O Processor Datasheet                                                            | 273943                                |

| Intel <sup>®</sup> 80331 I/O Processor Design Guide                                                         | 273823                                |

| Intel <sup>®</sup> 80331 I/O Processor Specification Update                                                 | 273930                                |

| Intel <sup>®</sup> 80331 I/O Processor JTAG Support White Paper                                             | 273961                                |

| Intel <sup>®</sup> 80331 I/O Processor Product Brief                                                        | 253413                                |

| Intel <sup>®</sup> 80321 Software Conversion to the Intel <sup>®</sup> 80331 I/O Processor Application Note | 273914                                |

| Intel <sup>®</sup> Flash Recovery Utility (FRU) Reference Manual                                            | 273551                                |

| PCI Local Bus Specification, Revision 2.3                                                                   | http://www.pcisig.com/specifications  |

| PCI-X Addendum to the PCI Local Bus Specification, Revision 1.0a                                            | - mup.//www.pcisig.com/specifications |

Intel documentation is available from the local Intel Sales Representative or Intel Literature Sales. To obtain Intel literature write to or call:

Intel Corporation Literature Sales P.O. Box 5937 Denver, CO 80217-9808 (1-800-548-4725) or visit the Intel website at http://www.intel.com

# **1.3 Electronic Information**

### Table 2. Electronic Information

| Support Type                             | Location/Contact     |

|------------------------------------------|----------------------|

| The Intel World-Wide Web (WWW) Location: | http://www.intel.com |

| Customer Support (US and Canada):        | 1-916-377-7000       |

# 1.4 Component References

Table 3 provides additional information on the major components of the IQ80331.

### Table 3.Component Reference

| Component                             | Part Number         | Additional Information                                                                                                                                                                                                                                   |

|---------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel StrataFlash®<br>Memory          | 28F640J3C           | Manufacturer: Intel Corporation     URL: <u>http://developer.intel.com/design/flcomp/prodbref/298044.htm</u>                                                                                                                                             |

| Intel® Gigabit Ethernet<br>Controller | 82545EM             | Manufacturer: Intel Corporation     URL: <u>http://developer.intel.com/design/network/products/lan/controllers/8</u> <u>2545.htm</u>                                                                                                                     |

| Rotary Switch                         | DR FC 16            | <ul> <li>Manufacturer: Grayhill*</li> <li>URL:<br/><u>http://embrace.grayhill.com/embrace/Item/ASP/Item-Detail.asp?Par</u><br/><u>tNo=94HAB16W&amp;CatalogGroupID=Series94HBinaryCoded&amp;Group</u><br/><u>DisplayLabel=&amp;RestSes=No</u> </li> </ul> |

| Hex Display                           | HDSP-A103           | <ul> <li>Manufacturer: Agilent Technologies*</li> <li>URL:<br/><u>http://www.semiconductor.agilent.com/cgi-bin/morpheus/home/hom</u><br/><u>e.jsp?pSection=LED</u></li> </ul>                                                                            |

| AudioBuzzer                           | DMT 1206 SMT        | <ul> <li>Manufacturer: RDI*</li> <li>URL:<br/><u>http://www.rdi-electronics.com/products/Audio/DMT-1206-SMT.html</u></li> </ul>                                                                                                                          |

| NVSRAM                                | STK14C88-3 N 35     | Manufacturer: SIMTEK*     URL:<br><u>http://www.simtek.com/product-information/datasheets/256K-PDF/S</u><br><u>TK14C88-3.pdf</u>                                                                                                                         |

| CPLD                                  | XC9572XL - 10TQ100C | Manufacturer: XILINK*     URL: <u>http://www.xilinx.com/bvdocs/publications/ds057.pdf</u>                                                                                                                                                                |

| Temperature Sensor                    | LM75CIMX-3          | Manufacturer: National*     URL: <u>http://www.national.com/pf/LM/LM75.html</u>                                                                                                                                                                          |

| Programmable Reset IC                 | MAX6306UK29D3       | Manufacturer: Maxim*     URL: <u>http://www.maxim-ic.com/quick_view2.cfm/qv_pk/1524</u>                                                                                                                                                                  |

| Registered Buffer                     | IDT74SSTU32864BF    | Manufacturer: IDT* (Integrated Device Technology)     URL: <u>http://www1.idt.com/pcms/products.taf?catID=97&amp;genID=74SSTU3     2864</u>                                                                                                              |

| Programmable PLL                      | IDTCSPU877BV        | Manufacturer: IDT* (Integrated Device Technology     URL:<br><u>http://www1.idt.com/pcms/products.taf?catID=112&amp;genID=CSPU87</u><br><u>Z</u>                                                                                                         |

| 256 bit 1-wire EEPROM                 | DS2430A_TSOC        | Manufacturer: Maxim*     URL: <u>http://www.maxim-ic.com/quick_view2.cfm?qv_pk=2913</u>                                                                                                                                                                  |

| 3.3V Transceiver                      | MAX561              | Manufacturer: Maxim*     URL: <u>http://www.maxim-ic.com/quick_view2.cfm?qv_pk=1544</u>                                                                                                                                                                  |

| Battery Charger                       | ADP3801             | Manufacturer: Analog Devices*     URL: <u>http://www.analog.com/UploadedFiles/Data_Sheets/308746738AD</u> <u>P3801_2_0.pdf</u>                                                                                                                           |

# intel

# 1.5 Terms and Definitions

### Table 4.Terms and Definitions

| Acronym/Term | Definition                                                                                                                                       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| ARM          | Refers to both the microprocessor architecture and the company that licenses it.                                                                 |

| IOP          | I/O processor                                                                                                                                    |

| ICE          | In-Circuit Emulator – A piece of hardware used to mimic all the functions of a microprocessor.                                                   |

| JTAG         | Joint Test Action Group – A hardware port supplied on Intel XScale® microarchitecture evaluation boards used for in-depth testing and debugging. |

| PPCI-X       | Primary PCI-X.                                                                                                                                   |

| PSU          | Power Supply Unit                                                                                                                                |

| SPCI-X       | Secondary PCI-X.                                                                                                                                 |

# 1.6 Intel<sup>®</sup> 80331 I/O Processor

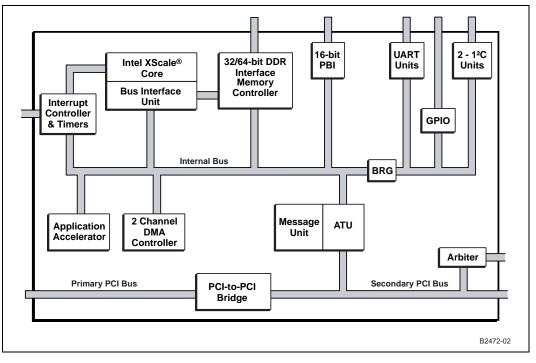

The 80331 combines the Intel XScale® core with powerful new features to create an intelligent I/O processor. This multi-function PCI device integrates a PCI-to-PCI Bridge and is fully compliant with the *PCI Local Bus Specification*, Revision 2.3, the *PCI-X Addendum to the PCI Local Bus Specification*, Revision 1.0a, and the *PCI Bridge Specification*, Revision 1.1.

The 80331 consolidates into a single system:

- Intel XScale® core

- PCI-to-PCI Bridge supporting PCI-X interfaces on the Primary and Secondary bus

- Address Translation Unit (ATU)

- High-Performance Memory Controller

- Interrupt Controller with 13 external interrupt inputs

- Two Direct Memory Access (DMA) Controller

- Peripheral Bus Interface (PBI) Unit

- Performance Monitor Unit (PMU)

- Application Accelerator Unit (AAU)

- Two I<sup>2</sup>C Bus Interface Units (BIU)

- Two 16550 Compatible UARTs with flow control (4 pins)

- Eight General Purpose Input Output (GPIO) Ports

For more in depth information in regards to the 80331, please see the Intel<sup>®</sup> 80331 I/O Processor Developer's Manual.

# intel

Figure 1. Intel<sup>®</sup> 80331 I/O Processor Block Diagram

The 80331 is an integrated processor that addresses the needs of intelligent I/O applications and helps reduce intelligent I/O system costs.

The instruction cache is 32 Kbytes (KB) in size and is 32-way set associative. Also, the core processor includes a data cache that is 32 KB and is 32-way set associative and a mini data cache that is 2 KB and is 2-way set associative.

The 80331 dual-ported memory controller can be configured for DDR SDRAM at 333 MHz (with a core processor speed of 500 MHz or 667 MHz) and Double Data Rate (DDR-II) SDRAM at 400 MHz (with a core processor speed of 500 Mhz, or 800 MHz). However, this manual only covers the configuration for DDR-II SDRAM at 400 MHz and with a core processor speeds of 500 MHz or 800 MHz.

# 1.7 Intel<sup>®</sup> IQ80331 I/O Processor Evaluation Platform Board Features

| Feature              | Definition                                                                                                                                                                                   |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Battery Backup Unit: | Battery back up circuit for SDRAM – 64 MB for 18 hours.                                                                                                                                      |

| Ethernet             | Intel® 82545EM Gigabit Ethernet Controller                                                                                                                                                   |

| Flash ROM:           | 8 MB Flash ROM 3.3 V – 16-bit Flash I/F.                                                                                                                                                     |

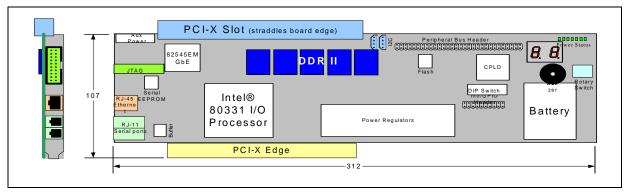

| Form Factor:         | PCI-X card (312 X 107 mm)                                                                                                                                                                    |

| General Purpose I/O: | GPIO Pins are used as described in the appropriate section in this document                                                                                                                  |

| Hex Display:         | Two 7-segment Hex LED displays.                                                                                                                                                              |

| JTAG Port:           | ARM compliant JTAG Header.                                                                                                                                                                   |

| Logic Analyzer:      | Logic analyzer connectors on the DDR-II SDRAM 400 MHzinterface.<br>Interposer Card may be used for the memory bus – Information supplied separately.                                         |

| Memory:              | 256 MB (512 Mb x 16) DDR-II SDRAM 400 MHz soldered onto the board.<br>ECC<br>Registered                                                                                                      |

| Onboard Power:       | Board sources +1.25 V, +2.5 V, +3.3 V, +5 V, +12 V, and -12 V from primary PCI connector.<br>All core voltages are derived from 3.3 V supply.<br>Auxiliary power for the Secondary PCI slot. |

| Power LED:           | Power on (green).                                                                                                                                                                            |

| Primary PCI:         | 64 bits 3.3 V <sup>a</sup> 133/100/66 MHz PCI-X or PCI 66 MHz                                                                                                                                |

| Secondary PCI:       | 1 x 64-bit PCI-X connector - 133 MHz.<br>Intel® 82545EM Gigabit Ethernet Controller also on the Secondary PCI.                                                                               |

| Serial Port:         | Dual RJ11 serial port connectors. The 80331 has two integrated UART serial ports which are 16550 compatible.                                                                                 |

### Table 5.Summary of Features

a. Please note that the Intel<sup>®</sup> IQ80331 I/O processor evaluation platform board is **NOT** 5 V tolerant.

# int<sub>e</sub>l *Getting Started*

# 2

The Intel® IQ80331 I/O processor evaluation platform board (IQ80331) is a software development environment for Intel<sup>®</sup> 80331 I/O processor<sup>1</sup> (80331).

### 2.1 Kit Contents

The IQ80331 Kit contains the following items:

- IQ80331 with 400 MHz DDR-II SDRAM.

- Code|Lab\* Development Environment from Accelerated Technology Incorporated\* (ATI).

- JTAG MPDemon Emulation unit.

- Serial Cable and RJ11 Adapter.

### 2.2 Hardware Installation

Warning: Static charges can severely damage the boards. Be sure to properly ground before removing the board from the anti-static bag.

### 2.2.1 **First-Time Installation and Test**

For first-time installation, visually inspect the IQ80331 for any damage made during shipment. Follow the host system manufacturer instructions for installing a PCI adapter. The board is a full-length PCI/PCI-X adapter and requires a PCI/PCI-X slot free from obstructions.

### 2.2.2 Power and Backplane Requirements

The IQ80331 requires a 3.3 V supply coming through the PCI/PCI-X primary connector. The board can be plugged into either a backplane or a desktop 64-bit PCI/PCI-X slot. When using a backplane, an ATX rated power supply is required. The IO80331 only draws from the 3.3 V line of the power supply. Most ATX power supply units (PSUs) regulate off the 5 V signal. When there is nothing drawing from the 5 V signal most ATX PSU do not supply the 3.3 V correctly. To overcome this, it is recommended to put a load on the 5 V line of the PSU. An old IDE Hard drive can be used for this.

- The PCI buses on the IQ80331 are **NOT** 5 V tolerant. The primary PCI bus **MUST** be plugged into Warning: a 3.3 V PCI/PCI-X slot.

- Caution: When plugging the power supply into the backplane, make sure that the power supply is disconnected from the mains. Most ATX PSUs supply 5 V standby current even when turned Off, backplane damage is possible.

The IQ80331 has an auxiliary power receptacle (J1A1, see Section 3.9.4, "Connector Summary") that is used to power the secondary PCI-X slot. This connector is compatible with a standard ATX hard drive power connector.

Caution: Before connecting power to the entire system, verify that the auxiliary system power to the secondary PCI-X slot and the main power to the IQ80331 are both connected. Both power rails should come up at the same time. When there is not a card plugged into the secondary PCI-X slot, then the auxiliary power can be left unconnected.

<sup>1.</sup> ARM\* architecture compliant.

# 2.3 Factory Settings

Make sure that the switch/jumper settings are set to proper positions as explained in Section 3.9, "Switches and Jumpers" on page 33.

# 2.4 Development Strategy

# 2.4.1 Supported Tool Buckets

For developing and debugging software application, the production version of the IQ80331 kit includes the Code|Lab Development Environment. Support for the Code|Lab development environment is available from ATI. Please refer to the enclosed package.

The kit also contains evaluation copies for several Software Development Tools. These tools are for evaluation purposes and do not include any support. Please contact the vendor directly for additional information and support. They include, but not limited to:

- RedHat\* GNUPro\* tools

- ARM RealView Developer Suite

- WindRiver\* VxWorks\* RTOS and Tornado\* Development Tools

- Wasabi Systems NetBSD\* ODS

- TimeSys\* Linux\* RTOS

- ATI, Nucleus Plus\* RTOS and Development Tools

It is recommended to frequently check with the Intel Development Tools web site located at <u>http://www.intel-ioprocessortools.com/kshowcase/view/</u> for current software and vendor updates.

# 2.4.2 Contents of the Flash

The production version of the board contains an image for RedHat\* RedBoot target monitor.

# intel

# 2.5 Target Monitors

# 2.5.1 Red Hat RedBoot

RedBoot is an acronym for "Red Hat Embedded Debug and Bootstrap", and is the standard embedded system debug/bootstrap environment from Red Hat, replacing the previous generation of debug firmware: CygMon and GDB stubs. It provides a bootstrap environment for a range of embedded operating systems, such as embedded Linux and eCos\*, and includes facilities such as network downloading and debugging. It also provides a simple Flash file system for boot images.

RedBoot provides a set of tools for downloading and executing programs on embedded target systems, as well as tools for manipulating the target system's environment. It can be used for both product development (debug support) and for end product deployment (Flash and network booting).

Here are some highlights of RedBoot capabilities:

- Boot scripting support.

- Simple command line interface for RedBoot configuration and management, accessible via serial (terminal) or Ethernet (telnet) (see Section 2.6.4, "GNUPro GDB/Insight" on page 19).

- Integrated GDB stubs for connection to a host-based debugger (GBD/Insight) via serial or Ethernet. (Ethernet connectivity is limited to local network only).

- Attribute Configuration user control of aspects such as system time and date (when applicable), default Flash image to boot from, default fail-safe image, static IP address, etc.

- Configurable and extensible, specifically adapted to the target environment.

- Network bootstrap support including setup and download, via BOOTP, DHCP and TFTP.

- X/Y-Modem support for image download via serial port.

- Power On Self Test.

intel

# 2.6 Host Communications Examples

How to communicate to the host.

# 2.6.1 Serial-UART Communication

Using a serial connection, while the IQ80331 is in a backplane or a host computer.

Figure 2. Serial-UART Communication

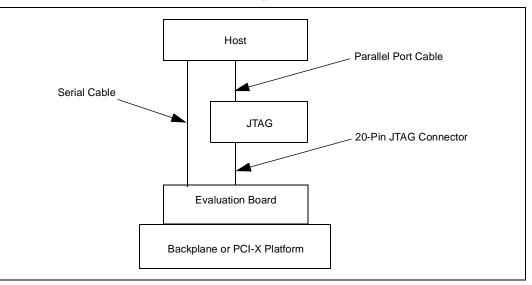

# 2.6.2 JTAG Debug Communication

Using a JTAG Emulator, while the IQ80331 is plugged into a backplane or a host computer:

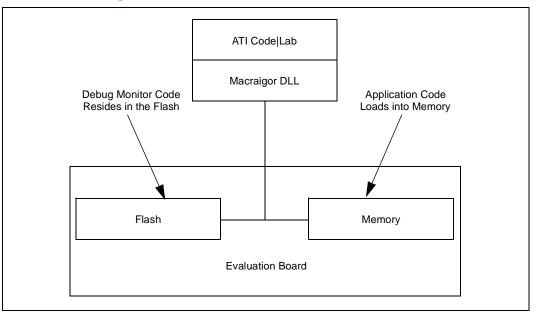

Figure 3. JTAG Debug Communication

# 2.6.3 Ethernet Communication

A standard network cable can be used to access the IQ80331 Ethernet connection. Redboot allows remote booting off a BOOTP server, Figure 4.

### Figure 4. Communication via Ethernet

# 2.6.4 GNUPro GDB/Insight

## 2.6.4.1 Communicating with RedBoot

Hardware Setup:

- Host with UNIX\*/Linux\* or Win32\* installed.

- IQ80331 with serial cable.

- Redhat RedBoot monitor Flashed to the platform board.

Recommended Mapping of UART Ports to Host Com Ports:

• Host port connected to the platform board UART.

The following communication tools can be used:

- Win32 using HyperTerminal\*.

- UNIX using Kermit\*.

- Linux using Minicom\*.

- Solaris\* using Tip\*.

RedBoot Monitor startup:

Description: Terminal emulator runs on host and communicates with the board via the serial cable.

Start: Power up the IQ80331. While the 'reset' is asserted, the two 7-segment LEDs sequentially display "SL" (Scrub loop) and then "A1". When RedBoot is successfully booted, then it displays the characters "A1" on the LEDs. When the final state of "A1" does not occur, then cycle the power again.

The time for reset is approximately 1 or 2 seconds.

Win32 on Host Connecting with HyperTerminal\*.

To bring up a HyperTerminal session on a Win32 platform: Go to Start, Programs, Accessories, Communications, HyperTerminal.

- HyperTerminal setup screens:

- "Connection Description" Panel:

- Enter name.

- "Connect To" Panel:

- Select host com2 port (or whichever port is being used).

- Port Settings:

- Bits per second: 115200

- Data Bits: 8

- Parity: none

- Stop Bits: 1

- Flow Control: none

- Start HyperTerminal:

- Select Call from HyperTerminal panel.

- Reset or power up IQ80331 board.

- The Host screen reads:

```

RedBoot(tm) debug environment - built dd:mm:yy, Mon dd 2004

Platform: IQ80331

Copyright (C) 2004, Red Hat, Inc.

RAM: 0xa0000000-0xa2000000

FLASH: 0x00000000 - 0x00800000, 64 blocks of 0x00020000 bytes each.

IP: 192.168.0.1, Default server: 0.0.0.0

RedBoot>

```

For further information on the GDB/Insight Debugger, refer to the content of the GNUPro CD and/or the GNUPro Debugging Tools manual. This setup assumes that RedBoot\* is Flashed on the board.

## 2.6.4.2 Connecting with GDB

Below are the GDB commands entered from the command prompt. Be sure system path is set to access "xscale-elf-gdb.exe". File name in example "hello". Bold type represents input by user:

### >xscale-elf-gdb -nw hello<sup>1</sup>

• Start GDB executable, loads debug information and symbols.

### (GDB) set remotebaud 115200

• Set baud rate for the IQ80331.

### Connect COM port:

- When using Windows command prompt: (GDB) target remote com1

- (GDB) target remote com

Example: screen output from board to host (GDB) target remote com1:

Remote debugging using com1.

(GDB)

• When using Linux (GDB) target remote /dev/ttyS0

### (GDB) load

• Load the program to the board, may have to wait a few seconds.

### (GDB) break main

• Set breakpoint at main.

### (GDB) continue

- Start the program using 'continue' verse the usual 'run'.

- Program hits break at main() and wait.

<sup>1.</sup> To be supplied separately.

This Page Left Intentionally Blank

# Hardware Reference Section

# 3.1 Functional Diagram

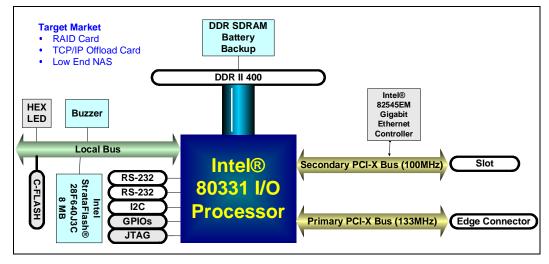

Figure 5 shows the functional block for the IQ80331.

### Figure 5. Functional Block Diagram

# 3.2 Board Form-Factor/Connectivity

Table 6 summarizes the form-factor and connectivity features for the IQ80331.

### Table 6.Form-Factor/Connectivity Features

| Description                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The Intel <sup>®</sup> IQ80331 I/O processor evaluation platform board is a 64-bit PCI card with form factor depicted by Figure 6.                                                           |

| The IQ80331 connects to the Primary PCI-X (PPCI-X) bus a PCI-X.                                                                                                                              |

| The IQ80331 has one PCI-X expansion slot.                                                                                                                                                    |

| The IQ80331 has two serial ports and one RJ-45 Ethernet port.                                                                                                                                |

| The IQ80331 has one JTAG port compliant with ARM Multi-ICE 20-pin connector standard. The JTAG is targeted for the Intel XScale® core and the CPLD, and is used for software debug purposes. |

### Figure 6. Board Form Factor

# 3.3 Power

The IQ80331 draws power from the PCI-X bus. The power requirements for the IQ80331 are shown in Table 7 below. The numbers do not include the power required by a PCI-X card mounted on the expansion slot.

### Table 7. Power Features

| Voltage Rails | Typical Current | Maximum Current |  |

|---------------|-----------------|-----------------|--|

| +3.3 V        | TBD mA          | 6237 mA         |  |

| +5 V          | TBD mA          | 6 mA            |  |

| +12 V         | TBD mA          | 103 mA          |  |

*Note:* Maximum values were calculated, not measured. Does not include additional power required by a PCI-X card mounted on the expansion slot.

# 3.4 Memory Subsystem

The memory subsystem consists of the DDR-II SDRAM as well as the Flash memory.

# 3.4.1 DDRII SDRAM

The DDR-II SDRAM interface consists of a 64-bit wide data path to support up to 3.2 Gbytes/sec throughput. An 8-bit Error Correction Code (ECC) is stored into the DDR-II SDRAM array along with the data and is checked when the data is read.

The Intel<sup>®</sup> IQ80331 I/O processor evaluation platform board features on board registered DDR-II 400 MHz SDRAM, arranged 512 Mbit x16 in density (256 MB), and with ECC.

## 3.4.1.1 Battery Backup

Battery backup is provided to save any information in DDR during a power failure. The evaluation board contains a 4 V Li-ion battery, a charging circuit and a regulator circuit.

DDR-II technology provides enabling data preservation through the self-refresh command. When the processor receives an active Primary PCI-X reset, the self-refresh command issues, driving SCKE signals low. Upon seeing this condition, the board logic circuit holds SCKE low before the processor loses power. Batteries maintain power to DDR-II and logic, to ensure self-refresh mode. When the circuit detects PRST# returning to inactive state, the circuit releases the hold on SCKE. Removing the battery can disable the battery circuit. When the battery remains in the platform and it is de-powered and/or removed from the chassis, the battery maintains DDR-II for about four hours. Once power is reapplied, the battery is fully charged.

The CPLD contains information in regards to the battery status. Please see Section 3.6.7, "Battery Status" on page 30 for more details.

# 3.4.2 Flash Memory Requirements

Total Flash memory size is 8 MB.

### Table 8. Flash Memory Requirements

| Description                                                                                                 |

|-------------------------------------------------------------------------------------------------------------|

| Intel <sup>®</sup> IQ80331 I/O processor evaluation platform board Total Flash size is 8 MB                 |

| IQ80331 Flash technology is based on Intel StrataFlash <sup>®</sup> family                                  |

| IQ80331 Flash uses a 16-bit interface                                                                       |

| IQ80331 Flash utilizes the 80331 Peripheral Bus                                                             |

| IQ80331 May be programmed using the PCI-X interface – Flash Recovery Utility (FRU) Utility                  |

| IQ80331 May be programmed using a RAM based software target monitor – Redhat RedBoot and ARM Firmware Suite |

| IQ80331 May be programmed using a JTAG emulation/debug device                                               |

# 3.5 Interrupt Routing

The IQ80331 Interrupt routing.

# Table 9. External Interrupt Routing to Intel<sup>®</sup> 80331 I/O Processor

| Interrupt | System Resource               |

|-----------|-------------------------------|

| HPI#      | Temperature Sensor, Header    |

| S_INTA#   | PCI-X Slot INTB#, Header      |

| S_INTB#   | PCI-X Slot INTC#, Header      |

| S_INTC#   | PCI-X Slot INTD#, Header      |

| S_INTD#   | PCI-X Slot INTA#, Header      |

| P_INTA#   | PCI-X Card Edge INTA#, Header |

| P_INTB#   | PCI-X Card Edge INTB#, Header |

| P_INTC#   | PCI-X Card Edge INTC#, Header |

| P_INTD#   | PCI-X Card Edge INTD#, Header |

# 3.6 Intel<sup>®</sup> IQ80331 I/O Processor Evaluation Platform Board Peripheral Bus

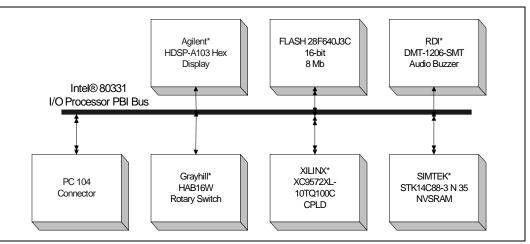

The IQ80331 populates the peripheral bus as depicted by Figure 7.

## Figure 7. Intel<sup>®</sup> IQ80331 I/O Processor Evaluation Platform Board Peripheral Bus Topology

The devices on the bus include Flash ROM, audio buzzer, CPLD, HEX display, NVSRAM, and rotary switch.

### Table 10.Peripheral Bus Features

| Description                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------|

| The bus width can be 8-bit or 16-bit and runs at 66 MHz.                                                            |

| The bus is utilized for attaching debug and Flash devices.                                                          |

| The interfaces/devices that are utilized include an audio buzzer, CPLD, a rotary switch, a HEX Display, and NVSRAM. |

intel

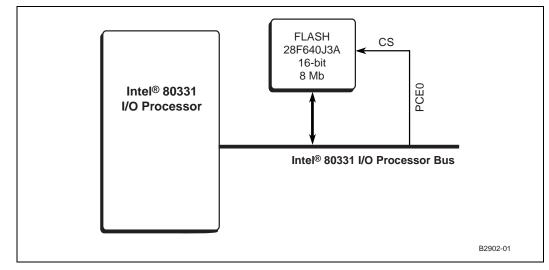

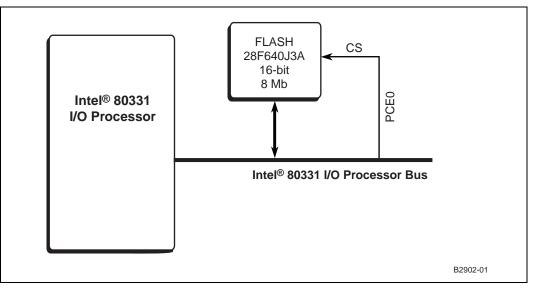

# 3.6.1 Flash ROM

### Table 11.Flash ROM Features

| Description                                                                    |

|--------------------------------------------------------------------------------|

| Flash is an Intel StrataFlash <sup>®</sup> technology – Part number: 28F640J3C |

| Flash size is 8 MB                                                             |

| The connection to the peripheral bus is depicted by Figure 8                   |

### Figure 8. Flash Connection on Peripheral Bus

# 3.6.2 UART

The 80331 has two integrated UARTs. Each asynchronous serial port supports all the functions of a 16550 UART. The UART signals are connected to a dual RS-232 buffer and then to a RJ-11 serial port connector mounted on the bracket of the evaluation board. The serial ports and GPIO signals are muxed on the same pins. Jumper J1D2, located next to the serial port buffer can disable the buffer to allow the signals to be used as GPIO signals. Please see Section 3.9.3, "Jumper Summary" on page 34 for more details.

# 3.6.3 Non-Volatile RAM

In addition to the 8 MB Flash device, the Intel<sup>®</sup> IQ80331 I/O processor evaluation platform board has a separate 32 K x 8 non-volatile RAM device on the peripheral bus. The NVRAMs address range is from CE87 0000 to CE87 FFFF (in hex). Please see Section 4.2.2, "Peripheral Bus Memory Map" on page 42 for more details.

# 3.6.4 Audio Buzzer

The IQ80331 has an audio buzzer that is turned on and off by writing to the Buzzer Control Register located in the CPLD. Jumper J9C2 enables the buzzer and jumper J9C1 adjusts the volume. Please see Section 3.9.3, "Jumper Summary" on page 34 for more details. The audio buzzer's address range is from CE86 0000 to CE86 FFFF (in hex). Please see Section 4.2.2, "Peripheral Bus Memory Map" on page 42 for more details.

# 3.6.5 HEX Display

The two pairs of Agilent\* HDSP-A103 seven segment LEDs are used for displaying POST codes or other software generated debug codes. Both HEX displays are individually addressed. The left HEX display address range is CE84 0000 to CE84 FFFF (in hex). The right HEX display address range is CE85 0000 to CE85 FFFF (in hex). Please see Section 4.2.2, "Peripheral Bus Memory Map" on page 42 for more details.

# 3.6.6 Rotary Switch

The IQ80331 provides a Rotary Switch for the user to select from different boot-up flavors. Please see Section 4.2.2, "Peripheral Bus Memory Map" on page 42 for more details on addressing the rotary switch.

### Table 12. Rotary Switch Requirements

| Description                                                   |  |  |  |  |  |

|---------------------------------------------------------------|--|--|--|--|--|

| Rotary switch has a 4-bit resolution (16 positions).          |  |  |  |  |  |

| The connection to the peripheral bus is depicted by Figure 7. |  |  |  |  |  |

# **3.6.7 Battery Status**

A CPLD on the Intel<sup>®</sup> IQ80331 I/O processor evaluation platform board provides the following status for the battery. Please see Section 4.2.2, "Peripheral Bus Memory Map" on page 42 for more details on addressing the CPLD.

Table 13.

Battery Status Buffer Requirements

| віт | Read/<br>Write | Name               | Description                                                                                                    |

|-----|----------------|--------------------|----------------------------------------------------------------------------------------------------------------|

| 0   | R              | Battery Present    | <ul> <li>0 = No backup battery</li> <li>1 = Battery backup is present</li> </ul>                               |

| 1   | R              | Battery Charged    | <ul> <li>0 = Battery is not fully charged</li> <li>1 = Battery is fully charged</li> </ul>                     |

| 2   | R              | Battery Discharged | <ul> <li>0 = Battery backup is not fully discharged</li> <li>1 = Battery backup is fully discharged</li> </ul> |

| 3   | R/W            | Battery Enable     | <ul> <li>0 = Disable battery backup</li> <li>1 = Enable battery backup</li> </ul>                              |

| 4-7 | N/A            | Reserved           | Undefined                                                                                                      |

# 3.7 Debug Interface

# 3.7.1 Console Serial Port

The platform has two serial ports for debug purposes as described in Section 3.6, "Intel<sup>®</sup> IQ80331 I/O Processor Evaluation Platform Board Peripheral Bus" on page 27.

# 3.7.2 JTAG Debug

The IQ80331 has a 20-pin JTAG connector that is in compliant with ARM\* Multi-ICE guidelines.

## **3.7.2.1 JTAG Port**

### Figure 9. JTAG Port Pin-out

| VTref  | 1           | 2  | Vsupply  |

|--------|-------------|----|----------|

| nTRST  | 3           | 4  | GND      |

| TDI    | 5           | 6  | GND      |

| TMS    | 7           | 8  | GND      |

| TCK    | 9           | 10 | GND      |

| RTCK   | 11          | 12 | GND      |

| TDO    | 13          | 14 | GND      |

| nSRST  | 15          | 16 | GND      |

| DBGRQ  | 17          | 18 | GND      |

| DBGACI | <b>〈</b> 19 | 20 | GND      |

|        |             |    | A9457-01 |

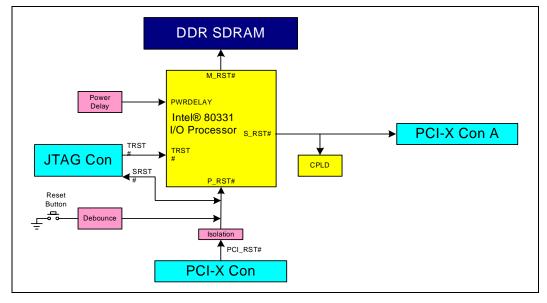

# 3.8 Board Reset Scheme

Figure 10 depicts the reset scheme for the IQ80331. Table 14 list the reset schemes for the IQ80331.

### Table 14. Reset Requirements/Schemes

| Description                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------|

| Primary PCI reset, resets all devices on the board. It occurs during the power-up.                                                    |

| The SRST signal from the JTAG connector is a bi-directional signal that can force a reset similar to the power-up reset on the board. |

### Figure 10. RESET Sources

# 3.9 Switches and Jumpers

# 3.9.1 Switch Summary

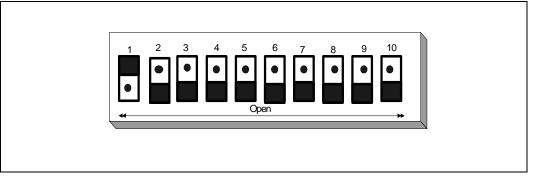

Please note that the term 'open' refers to the individual pins of Switch S7C1being pushed in at the bottom (small dot on pin away from the 'open' label on the switch). The term 'closed' refers to the pin being pushed in at the top. Please see Figure 11, "Default Switch Settings" on page 33, for more details.

### Table 15. Switch Summary

| Switch  | Association | Description                                          | Factory<br>Default |

|---------|-------------|------------------------------------------------------|--------------------|

| S7C1-1  | SPCI-X Bus  | Sets secondary PCI bus to 100 MHz                    | Closed             |

| S7C1-2  | IOP         | Reset: Sets IOP Reset-Mode operation                 | Open               |

| S7C1-3  | IOP         | Retry: ATU/PCI configuration cycle-Mode operation    | Open               |

| S7C1-4  | PPCI-X Bus  | BRG_EN: Enables or disables bridge                   | Open               |

| S7C1-5  | SPCI-X Bus  | PRIVDEV: Enables private or normal devices           | Open               |

| S7C1-6  | SPCI-X Bus  | PRIVMEM: Enables normal or private memory addressing | Open               |

| S7C1-7  | PPCI-X Bus  | Enables 64-bit or 32-bit on primary PCI-X bus        | Open               |

| S7C1-8  |             | Spare                                                | Open               |

| S7C1-9  |             | Spare                                                | Open               |

| S7C1-10 | Flash       | Sets flash width (x8 or x16) Enable                  | Open               |

# 3.9.2 Default Switch Settings - Visual

### Table 16. Switch S7C1

| Closed | Open |

|--------|------|------|------|------|------|------|------|------|------|

| S7C1   | S7C1 | S7C1 | S7C1 | S7C1 | S7C1 | S7C1 | S7C1 | S7C1 | S7C1 |

| 1      | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   |

### Figure 11. Default Switch Settings

# 3.9.3 Jumper Summary

### Table 17.Jumper Summary

| Jumper | Description     | Factory Default |

|--------|-----------------|-----------------|

| J1B1   | U1_EN_N bypass  | Open            |

| J1B2   | JTAG 2x4 Header | 1-2, 7-8        |

| J1D2   | UART Enable     | Open            |

| J9C1   | Buzzer Volume   | Open            |

# 3.9.4 Connector Summary

### Table 18.Connector Summary

| Connector                          | Description                                                                                                          |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| J1A1                               | Secondary PCI-X Expansion Slot Power. Please see Section 2.2.2, "Power and Backplane Requirements" for more details. |

| J1B1, J1B2,<br>J1D2, J9C1          | Jumper Settings. Please see Section 3.9.3, "Jumper Summary" on page 34 for more details.                             |

| J1D1                               | RJ45 Network Connector for GbE NIC.                                                                                  |

| J1E1                               | UART Headers.                                                                                                        |

| J2C1                               | Interrupt Header                                                                                                     |

| J1E2                               | RJ11 Dual Serial Port Connector.                                                                                     |

| J1E3                               | Edge connector for primary PCI-X Bus.                                                                                |

| J2A1                               | Secondary PCI-X Expansion bus Slot.                                                                                  |

| J2D1                               | Power header for fan.                                                                                                |

| J4M1, J4N1,<br>J5M1, J5N1,<br>J5N2 | Agilent mictor connectors - no pop                                                                                   |

| J6A1, J6A2                         | I <sup>2</sup> C 4 pin connectors.                                                                                   |

| J7C1                               | CPLD Header.                                                                                                         |

| J8B1                               | Not populated.                                                                                                       |

| J8D1                               | Power header for battery.                                                                                            |

| J9A1                               | PC104 Mod connector, can NOT be used with standard PC104 applications. This is not a PC104 valid connector.          |

# 3.9.5 General Purpose Input/Output Header

The following table in Section 19, "GPIO Header Definition" on page 34 shows the GPIO signal assignments. The GPIO signals are muxed with the serial port signals. The serial port must be disabled to use the GPIO signals.

### Table 19.GPIO Header Definition

| Pin | Signal | Pin | Signal |

|-----|--------|-----|--------|

| 1   | GPIO0  | 5   | GPIO4  |

| 2   | GPIO1  | 6   | GPIO5  |

| 3   | GPIO2  | 7   | GPIO6  |

| 4   | GPIO3  | 8   | GPIO7  |

# 3.9.6 Detail Descriptions of Switches/Jumpers

## 3.9.6.1 Switch S7C1

This switch allows the user to enable or disable various features. All associated nets can be cross-referenced from the Intel<sup>®</sup> IQ80331 Evaluation Platform Board Schematics.

### 3.9.6.1.1 S7C1-1: SECONDARY BUS SPEED associated net PD\_PBI\_AD3

This switch allows the user to force the secondary PCI-X bus to run at 133 MHz or 100 MHz. However, since the 82545EM resides on the secondary PCI-X bus, it is unlikely that an additional device plugged into the secondary PCI-X slot could run at 133 MHz.

### Table 20. S7C1-1: SECONDARY BUS SPEED: Settings and Operation Mode

| S7C1-1 | Operation Mode                                   |

|--------|--------------------------------------------------|

| Open   | Enables 133 MHz on secondary bus                 |

| Closed | Enables 100 MHz on secondary bus (Default mode). |

### 3.9.6.1.2 S7C1-2: RESET - associated net PD\_AD5

RESET MODE is latched at the de-asserting edge of P\_RST# and it determines when the 80331 is held in reset until the Intel XScale® core Reset bit is cleared in the PCI Configuration and Status Register. When the core is held in reset, the LEDs (DS9A1 and DS9A2)are not illuminated.

### Table 21. Switch S7C1-2: RESET: Settings and Operation Mode

| S7C1-2 | Operation Mode                                                |

|--------|---------------------------------------------------------------|

| Open   | Don't hold in reset - enables core to execute (Default mode). |

| Closed | Hold in reset.                                                |

### 3.9.6.1.3 S7C1-3: RETRY - associated net PD\_AD6

RETRY is latched at the de-asserting edge of P\_RST# and it determines when the Primary PCI interface disable PCI configuration cycles by signaling a Retry until the Configuration Cycle Retry bit is cleared in the PCI Configuration and Status Register.

### Table 22. Switch S7C1-3: RETRY: Settings and Operation Mode

| S7C1-3 | Operation Mode                                                  |

|--------|-----------------------------------------------------------------|

| Open   | Retry enabled - use when booting in a host (Default mode).      |

| Closed | Configuration retry disabled - use when booting in a backplane. |

### 3.9.6.1.4 S7C1-4: BRIDGE ENABLE - associated net PD\_AD0

This switch allows the user to enable or disable the PCI-X to PCI-X bridge inside the I/O processor.

### Table 23. S7C1-4: BRIDGE ENABLE: Settings and Operation Mode

| S7C1-4 | Operation Mode                |

|--------|-------------------------------|

| Open   | Bridge enabled(Default mode). |

| Closed | Bridge disabled.              |

### 3.9.6.1.5 Switch S7C1- 5: PRIVATE DEVICES associated net PD\_A0

This switch allows the user to enable a private device on the secondary PCI-X bus.

*Note:* Please note, Redboot expects private devices to be enabled. If this switch is not properly set correctly with Redboot running, then the Redboot kernel crashes when the software addresses the GigE device. When the kernel crashes, garbage is seen on the serial port. Try properly setting this switch, and resetting the system.

### Table 24. Switch S7C1- 5: PRIVATE DEVICES: Settings and Operation Mode

| S7C1-5 | Operation Mode                                    |

|--------|---------------------------------------------------|

| Open   | Enables private devices (Default Mode).           |

| Closed | Disables private devices. All devices are public. |

### 3.9.6.1.6 Switch S7C1 - 6: PRIVATE MEMORY associated net PD\_A1

This allows 80331 to hide devices in PCI-X by enabling private memory spaces.

*Note:* Again, Redboot expects this switch to be open.

### Table 25. Switch S7C1 - 6: PRIVATE MEMORY: Settings and Operation Mode

| S7C1-6 | Operation Mode                                               |

|--------|--------------------------------------------------------------|

| Open   | Private memory enable on secondary PCI-X bus (Default mode). |

| Closed | Normal addressing mode.                                      |

### 3.9.6.1.7 Switch S7C1 - 7: PRIMARY PCI BUS WIDTH associated net PD\_PBI\_A2

This allows 80331 to force the secondary PCI-X bus to operate in 32-bit or 64-bit mode.

### Table 26. Switch S7C1 - 7: PRIMARY PCI BUS WIDTH: Settings and Operation Mode

| S7C1-7 | Operation Mode                                           |

|--------|----------------------------------------------------------|

| Open   | Enables 64-bit Secondary PCI-X bus width (Default mode). |

| Closed | Enables 32-bit Secondary PCI-X bus width.                |

### 3.9.6.1.8 Switch S7C1- 8/9

These switches (S7C1-8 and S7C1-9) are spares and should be left open.

#### 3.9.6.1.9 Switch S7C1- 10: FLASH WIDTH - associated net P3\_3V

This switch allows the user to choose 8-bit or 16-bit Flash.

#### Table 27. Switch S7C1 - 10: FLASH WIDTH: Settings and Operation Mode

| S7C1-10 | Operation Mode                      |  |  |

|---------|-------------------------------------|--|--|

| Open    | Enables 8-bit Flash (Default mode). |  |  |

| Closed  | Enables 16-bit Flash.               |  |  |

#### 3.9.6.2 Jumper J1B1- UART U1 RXD ENABLE

Install this jumper to disable UART U1 RXD. The associated net is U1\_EN\_N.

Table 28.Jumper J1B1: Descriptions

| Jumper | Description         | Factory Default |

|--------|---------------------|-----------------|

| J1B1   | UART U1 RXD disable | Open            |

Table 29.

Jumper J1B1: Settings and Operation Mode

|   | J1B2     | Operation Mode                              |  |

|---|----------|---------------------------------------------|--|

|   | NC       | UART transceiver enabled (Factory Default). |  |

| ĺ | Pins 1,2 | UART transceiver disabled.                  |  |

#### 3.9.6.3 Jumper J1B2 - JTAG COMMUNICATION OPTIONS

#### Table 30. Jumper J1B2: Descriptions

| Jumper | Description       | Factory Default |

|--------|-------------------|-----------------|

| J1B2   | JTAG 2 x 4 Header | 1-2, 7-8        |

#### Table 31. Jumper J1B2: Settings and Operation Mode

| Pins | Operation Mode                                                                       |  |

|------|--------------------------------------------------------------------------------------|--|

| 1-2  | JTAG communication to IOP only (Factory Default).                                    |  |

| 3-4  | JTAG communication to IOP and GigE                                                   |  |

| 5-6  | Spare                                                                                |  |

| 7-8  | Connects TRST_N through a 1 K ohm resistor, pulled down to ground (Factory Default). |  |

#### 3.9.6.4 Jumper J1D2 - UART TRANSCEIVER ENABLE

Install J1D2 to enable UART transceiver.

#### Table 32.Jumper J1D2: Descriptions

| Jumper | Description              | Factory Default |

|--------|--------------------------|-----------------|

| J1D2   | UART transceiver disable | Open            |

#### Table 33. Jumper J1D2: Settings and Operation Mode

| J1D2     | Operation Mode                              |  |

|----------|---------------------------------------------|--|

| NC       | ART transceiver disabled (Factory Default). |  |

| Pins 1,2 | UART transceiver enabled.                   |  |

### 3.9.6.5 Jumper J9C1 - BUZZER VOLUME

#### Table 34. Jumper J9C1: Descriptions

| Jumper | Description   | Factory Default |

|--------|---------------|-----------------|

| J9C1   | Buzzer Volume | Open            |

#### Table 35. Jumper J9C1: Settings and Operation Mode

| J9C1     | Operation Mode                      |  |

|----------|-------------------------------------|--|

| Pins 1,2 | Buzzer Volume LOUD.                 |  |

| Pins 2,3 | Buzzer Volume QUIET.                |  |

| NC       | Buzzer Volume OFF(Factory Default). |  |

int<sub>el</sub>®

# Software Reference

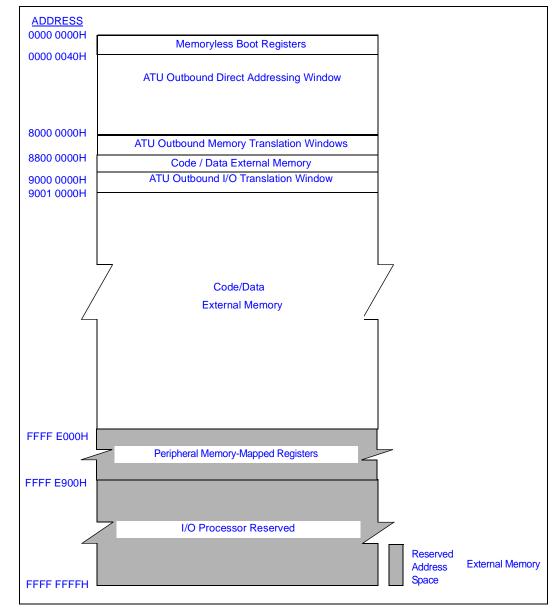

#### 4.1 DRAM

For DDR SDRAM and DDR-II sizes and configurations that the Intel<sup>®</sup> 80331 I/O processor supports, please see section 8.3.3 of the Intel<sup>®</sup> 80331 I/O Processor Developer's Manual. This section also contains multiple examples of Address Register Programming.

See the Intel<sup>®</sup> 80331 I/O Processor Design Guide, section 7.1, Table 16 for supported DDR and SDRAM configurations.

For all registers relating to DRAM and other MCU related registers, see Section 8.7, Table 234 of the Intel<sup>®</sup> 80331 I/O Processor Developer's Manual.

#### 4.2 **Components on the Peripheral Bus**

The 80331 has a peripheral bus which contains the following peripheral devices:

- · Flash ROM

- CPLD

- · Audio Buzzer

- · Rotary Switch