# intel®

# Intel<sup>®</sup> 80331 I/O Processor

**Application Accelerator Unit D-0 Addendum**

January, 2005

Document Number: 304496001US

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel<sup>®</sup> internal code names are subject to change.

THIS SPECIFICATION, THE Intel<sup>®</sup> 80331 I/O Processor IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

#### Copyright © Intel Corporation, 2005

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, Commerce Cart, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantIP, Intel, Intel logo, Intel 366, intel486, Intel740, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel Nete IstrataFlash, Intel Packet Concert, Intel SingleDriver, Intel SprateGitep, Intel StrataFlash, Intel reamStation, Intel WebOutfitter, Intel Xeon, Intel XScale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo, NetPort, NetportExpress, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, ProShare, RemoteExpress, Screamline, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, This Way In, TokenExpress, Trillium, Vivonic, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

| 1 | Арріі | lication Accelerator Unit                                  | 9  |

|---|-------|------------------------------------------------------------|----|

|   | 1.1   | Overview                                                   | 9  |

|   | 1.2   | Theory of Operation                                        |    |

|   | 1.3   | Hardware-Assist XOR Unit                                   |    |

|   |       | 1.3.1 Data Transfer                                        |    |

|   |       | 1.3.2 Chain Descriptors                                    |    |

|   |       | 1.3.2.1 Principle / Four-Source Descriptor Format          |    |

|   |       | 1.3.2.2 Eight-Source Descriptor Format                     |    |

|   |       | 1.3.2.3 Sixteen-Source Descriptor Format                   |    |

|   |       | 1.3.2.4 Thirty-two-Source Descriptor Format                |    |

|   |       | 1.3.2.5 Dual-XOR-Transfer Descriptor Format                |    |

|   |       | 1.3.2.6 P+Q Three-Source Descriptor Format                 |    |

|   |       | 1.3.2.7 P+Q Six-Source Descriptor Format                   | 25 |

|   |       | 1.3.2.8 P+Q Twelve-Source Descriptor Format                |    |

|   |       | 1.3.2.9 P+Q Sixteen-Source Descriptor Format               |    |

|   |       | 1.3.3 Descriptor Summary                                   |    |

|   |       | 1.3.4 Descriptor Chaining                                  |    |

|   | 1.4   | AA Descriptor Processing                                   |    |

|   |       | 1.4.1 Scatter Gather Transfers                             |    |

|   |       | 1.4.2 Synchronizing a Program to Chained Operation         |    |

|   |       | 1.4.3 Appending to The End of a Chain                      |    |

|   | 1.5   | AA Operations                                              |    |

|   |       | 1.5.1 AA Addressing                                        |    |

|   |       | 1.5.2 XOR Operation                                        |    |

|   |       | 1.5.3 XOR Operation with P+Q RAID-6 Mode                   |    |

|   |       | 1.5.4 Dual-XOR Operation                                   |    |

|   |       | 1.5.5 Zero Result Buffer Check                             |    |

|   |       | 1.5.6 Zero Result Buffer Check with P+Q RAID-6             |    |

|   |       | 1.5.7 Memory Block Fill Operation                          |    |

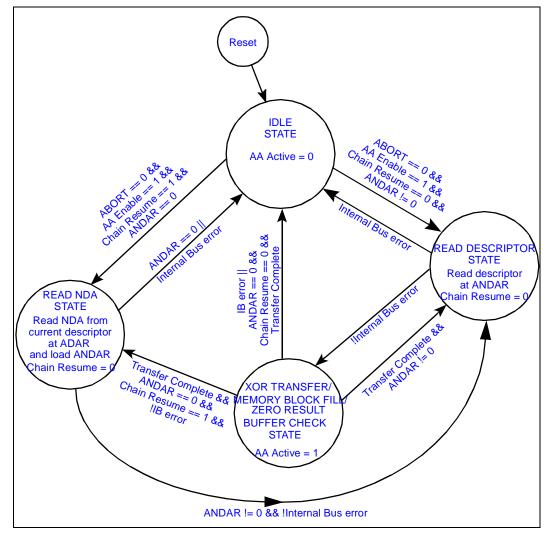

|   | 1.6   | Programming Model State Diagram                            |    |

|   | 1.7   | Application Accelerator Priority                           |    |

|   | 1.8   | Packing and Unpacking                                      |    |

|   | 1.0   |                                                            |    |

|   | 1.0   |                                                            |    |

|   | 1.9   | Programming the Application Accelerator                    |    |

|   |       | 1.9.1 Application Accelerator Initialization               |    |

|   |       | 1.9.2 Suspending and Resuming the Application Accelerat    |    |

|   |       | 1.9.3 Appending Descriptor for XOR Operations              |    |

|   |       | 1.9.4 Appending Descriptor for Dual XOR Operations         |    |

|   |       | 1.9.5 Appending Descriptor for Memory Block Fill Operation |    |

|   |       | 1.9.6 Appending Descriptor for Zero Result Buffer Check    |    |

|   | 1.10  |                                                            |    |

|   | 1.11  | Error Conditions                                           | 67 |

|   | 1.12  | Power-up/Default Status                                    | 68 |

|   | 1.13  |                                                            |    |

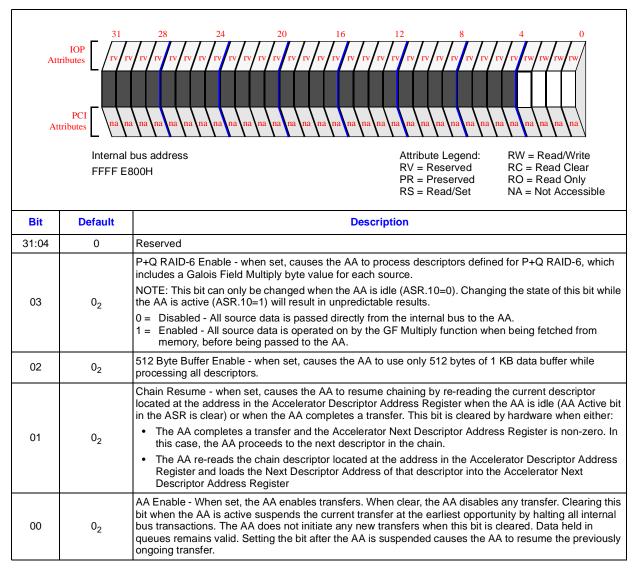

|   |       | 1.13.1 Accelerator Control Register - ACR                  | 69 |

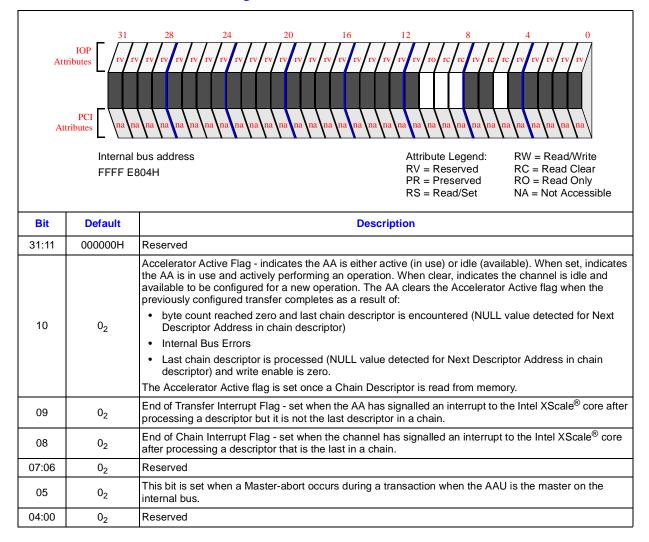

|   |       | 1.13.2 Accelerator Status Register - ASR                   |    |

|   |       | 1.13.3 Accelerator Descriptor Address                      |    |

| <ul> <li>1.13.4 Accelerator Next Descriptor Address<br/>Register - ANDAR.</li> <li>1.13.5 Data / Source Address Register1 - D/SAR1/PQSAR1</li> <li>1.13.6 Source Address Registers 232 - SAR232</li> </ul> | 73<br>74 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.13.5 Data / Source Address Register1 - D/SAR1/PQSAR1                                                                                                                                                     | 73<br>74 |

| 8                                                                                                                                                                                                          | 74       |

| 1.13.6 Source Address Registers 232 - SAR232                                                                                                                                                               |          |

|                                                                                                                                                                                                            |          |

| 1.13.7 P+Q RAID-6 Source Address Registers 216 -                                                                                                                                                           |          |

| PQSAR216                                                                                                                                                                                                   | 6        |

| 1.13.8 P+Q RAID-6 Galois Field Multiplier Registers 15                                                                                                                                                     |          |

| - GFMR15                                                                                                                                                                                                   | 77       |

| 1.13.9 Destination Address Register - DAR                                                                                                                                                                  | 79       |

| 1.13.10 Accelerator Byte Count Register - ABCR                                                                                                                                                             | 30       |

| 1.13.11 Accelerator Descriptor Control Register - ADCR                                                                                                                                                     | 31       |

| 1.13.12 Extended Descriptor Control Register 0 - EDCR0                                                                                                                                                     |          |

| 1.13.13 Extended Descriptor Control Register 1 - EDCR1                                                                                                                                                     |          |

| 1.13.14 Extended Descriptor Control Register 2 - EDCR2                                                                                                                                                     |          |

# Figures

| 1  | Application Accelerator Block Diagram                                   |    |

|----|-------------------------------------------------------------------------|----|

| 2  | Principle / Four Source Descriptor Format                               | 14 |

| 3  | Chain Descriptor Format for Eight Source Addresses (XOR Function)       | 15 |

| 4  | Chain Descriptor Format for Sixteen Source Addresses (XOR Function)     | 16 |

| 5  | Chain Descriptor Format for Thirty Two Source Addresses (XOR Function)  | 19 |

| 6  | Chain Descriptor Format for Dual-XOR-transfer                           | 22 |

| 7  | P+Q Base Chain Descriptor Format                                        |    |

| 8  | P+Q Chain Descriptor Format for Six Source Addresses (XOR Function)     | 25 |

| 9  | P+Q Chain Descriptor Format for Twelve Source Addresses (XOR Function)  | 26 |

| 10 | P+Q Chain Descriptor Format for Sixteen Source Addresses (XOR Function) | 29 |

| 11 | XOR Chaining Operation                                                  |    |

| 12 | Example of Gather Chaining for Four Source Blocks                       |    |

| 13 | Synchronizing to Chained AA Operation                                   |    |

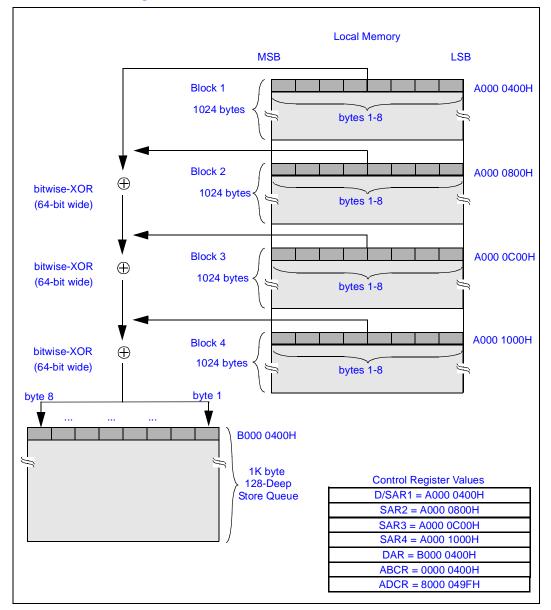

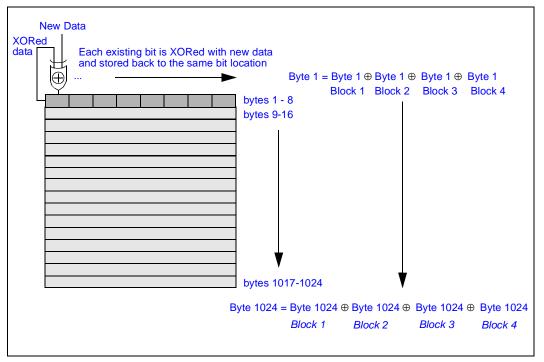

| 14 | The Bit-wise XOR Algorithm                                              |    |

| 15 | Hardware Assist XOR Unit                                                |    |

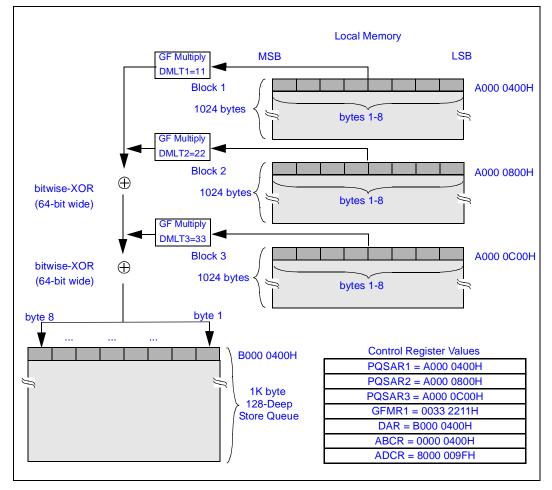

| 16 | The Bit-wise XOR Algorithm including the P+Q RAID-6 Mode                |    |

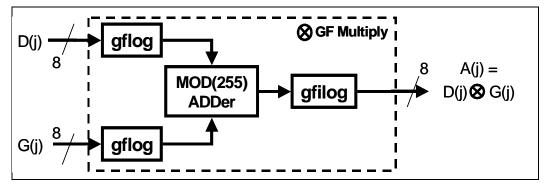

| 17 | GF Multiply Function                                                    |    |

| 18 | Galois Field Logarithm Transformation Table                             |    |

| 19 | Galois Field Inverse Logarithm Transformation table                     |    |

| 20 | P+Q RAID-6 Generation Equation                                          |    |

| 21 | The Bit-wise Dual-XOR Algorithm                                         |    |

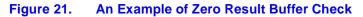

| 22 | An example of Zero Result Buffer Check                                  |    |

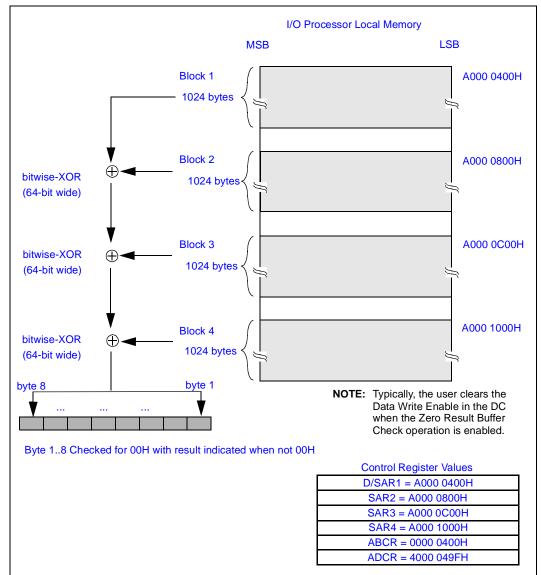

| 23 | An example of Zero Result Buffer Check with P+Q RAID-6                  |    |

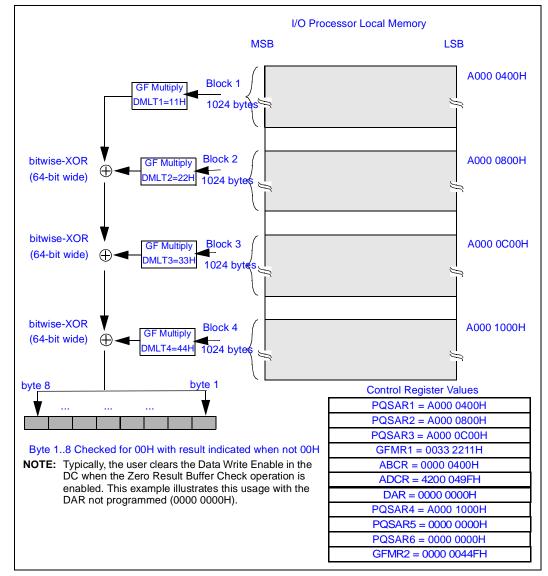

| 24 | Example of a Memory Block Fill Operation                                |    |

| 25 | Application Accelerator Programming Model State Diagram                 |    |

| 26 | Optimization of an Unaligned Data Transfer                              |    |

| 27 | Pseudo Code: Application Accelerator Initialization                     |    |

| 28 | Pseudo Code: Application Accelerator Chain Resume Initialization        |    |

| 29 | Pseudo Code: Suspend Application Accelerator                            |    |

| 30 | Pseudo Code: XOR Transfer Operation                                     |    |

| 31 | Pseudo Code: Dual XOR Transfer Operation                                |    |

| 32 | Pseudo Code: Memory Block Fill Operation                                |    |

| 33 | Pseudo Code: Zero Result Buffer Check Operation                         | 65 |

# **Tables**

| 1  | Register Description                                 | 12   |

|----|------------------------------------------------------|------|

| 2  | Register Description<br>Descriptor Summary           | 33   |

| 3  | AA Operation and Command Combination Summary         | . 41 |

| 4  | Typical AA Operation and Addressing Summary          | . 42 |

| 5  | AA Interrupts                                        | .66  |

| 6  | Application Accelerator Unit Registers               | .68  |

| 7  | Accelerator Control Register - ACR                   |      |

| 8  | Accelerator Status Register - ASR                    | .70  |

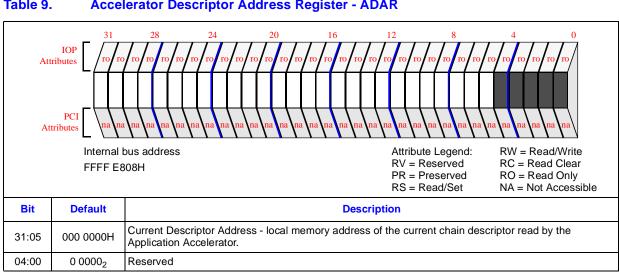

| 9  | Accelerator Descriptor Address Register - ADAR       |      |

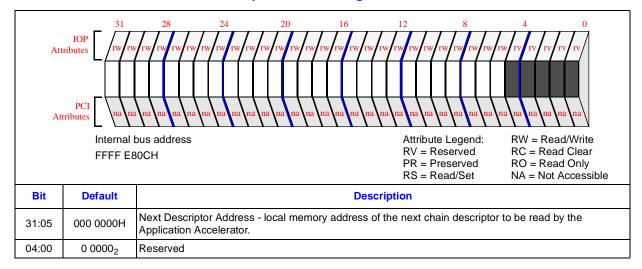

| 10 | Accelerator Next Descriptor Address Register - ANDAR | .72  |

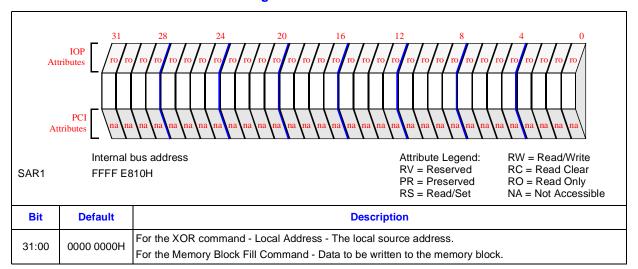

| 11 | Data / Source Address Register - SAR1/PQSAR1         | .73  |

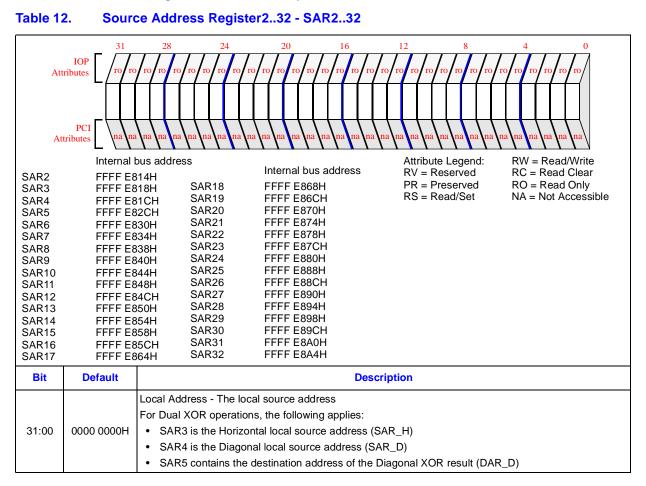

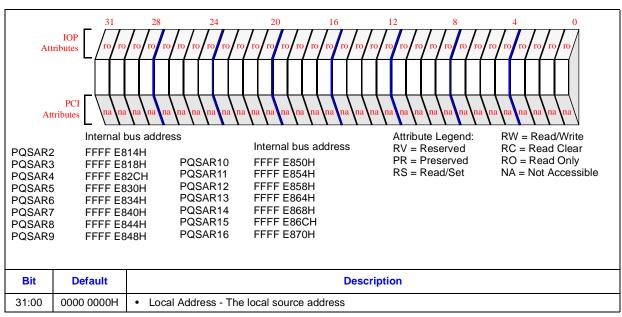

| 12 | Source Address Register232 - SAR232                  | .75  |

| 13 | P+Q RAID-6 Source Address Registers 216 - PQSAR216   |      |

| 14 | Galois Field Multiplier Registers 15 - GFMR15        | .77  |

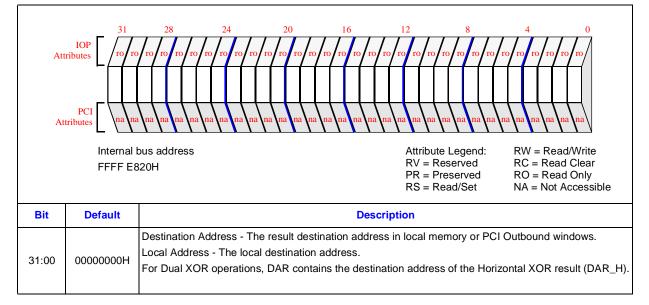

| 15 | Destination Address Register - DAR                   |      |

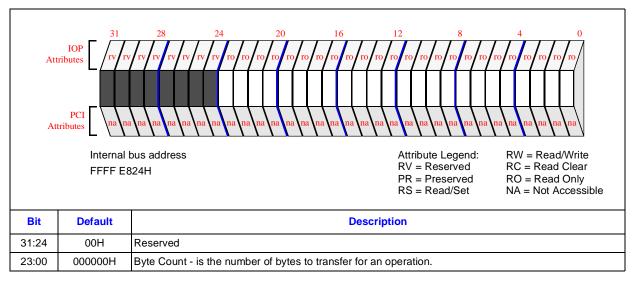

| 16 | Accelerator Byte Count Register - ABCR               |      |

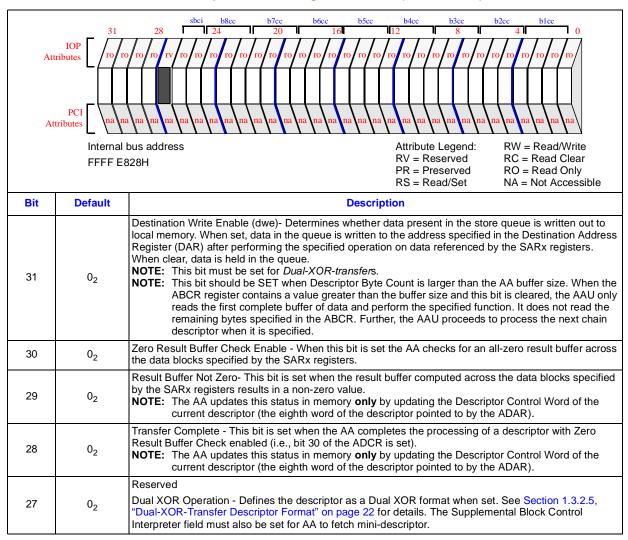

| 17 | Accelerator Descriptor Control Register - ADCR       | . 81 |

| 18 | Extended Descriptor Control Register 0 - EDCR0       | . 85 |

| 19 | Extended Descriptor Control Register 1 - EDCR1       | . 87 |

| 20 | Extended Descriptor Control Register 2 - EDCR2       | .89  |

|    |                                                      |      |

# **Revision History**

| Date         | Revision | Description                         |

|--------------|----------|-------------------------------------|

| January 2005 | 001      | Initial Developer Web Site Release. |

Intel<sup>®</sup> 80331 I/O Processor Application Accelerator Unit D-0 Addendum Contents

intel

This Page Left Intentionally Blank

# **Application Accelerator Unit**

1

This chapter describes the integrated Application Accelerator (AA) Unit. The operation modes, setup, external interface, and implementation of the AA unit are detailed in this chapter.

## 1.1 Overview

The Application Accelerator provides low-latency, high-throughput data transfer capability between the AA unit and Intel<sup>®</sup> 80331 I/O processor (80331) local memory. It executes data transfers to and from 80331 local memory, checks for all-zero result across local memory blocks, performs memory block fills, and provides the necessary programming interface. The Application Accelerator performs the following functions:

- Transfers data (read) from memory controller.

- Performs an optional boolean operation (XOR) on read data.

- Transfers data (write) to memory controller or PCI.

- Checks for All-zero result across local memory blocks.

- Performs memory block fills.

- Optional Dual-XOR for RAID-6 application single strip write.

- Optional Galois Field (GF) Multiply calculation for P+Q RAID-6 in conjunction with XOR operations.

The AA unit features:

- 1Kbyte/512-byte store queue.

- Utilization of the 80331 memory controller Interface.

- $2^{32}$  addressing range on the 80331 local memory interface.

- Hardware support for unaligned data transfers for the internal bus.

- Fully programmable from the Intel XScale<sup>®</sup> core.

- Support for automatic data chaining for gathering and scattering of data blocks.

- Support for writing a constant value to a memory block (block fill).

- Support for writing descriptor status to local memory.

- Hardware to perform Galois Field (GF) Multiply function on the Source Data Streams during an XOR operation, when enabled.

## 1.2 Theory of Operation

The Application Accelerator is a master on the internal bus and performs data transfers to and from local memory. It does not interface to the PCI bus. AA uses direct addressing for memory controller.

The AA implements XOR algorithm in hardware. It performs XOR operation on multiple blocks of source (incoming) data and stores result back in 80331 local memory. The source and destination addresses are specified through chain descriptors resident in 80331 local memory. A Dual-XOR operation is also supported for optimized processing of two different, but related XOR operations in a single operation. The AA can also check for all-zero result across local memory blocks or fill a memory block with arbitrary data. Figure 1 shows a block diagram of the AA unit. The AA can also perform memory-to-memory transfers of data blocks controlled by 80331 memory controller unit.

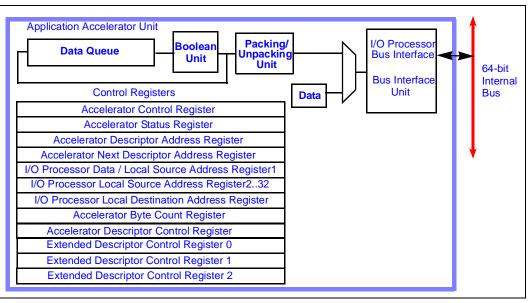

#### Figure 1. Application Accelerator Block Diagram

AA programming interface is accessible from the internal bus through a memory-mapped register interface. Data for XOR operation is configured by writing source addresses, destination address, number of bytes to transfer, and various control information into a local memory chain descriptor. Chain descriptors are described in detail in Section 1.3.2, "Chain Descriptors" on page 13.

The AA unit contains a hardware data packing and unpacking unit. This unit enables data transfers from and to unaligned addresses in 80331 local memory. All combinations of unaligned data are supported with the packing and unpacking unit. Data is held internally in the AA until ready to be stored back to local memory. This is done using a 1KByte/512Byte holding queue. Data to be written back to 80331 local memory can either be aligned or unaligned.

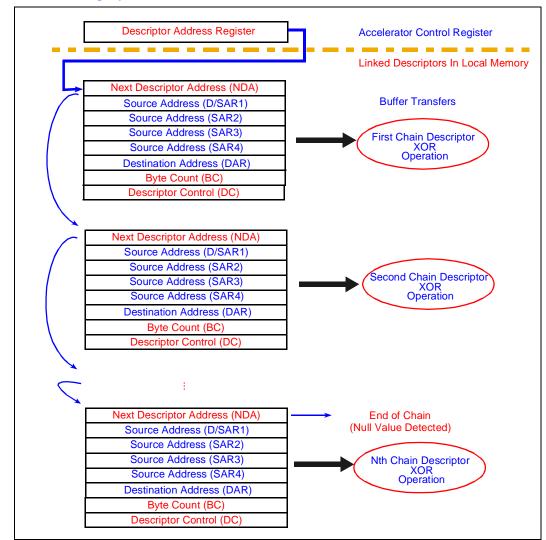

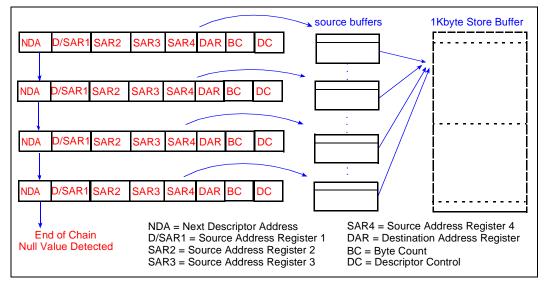

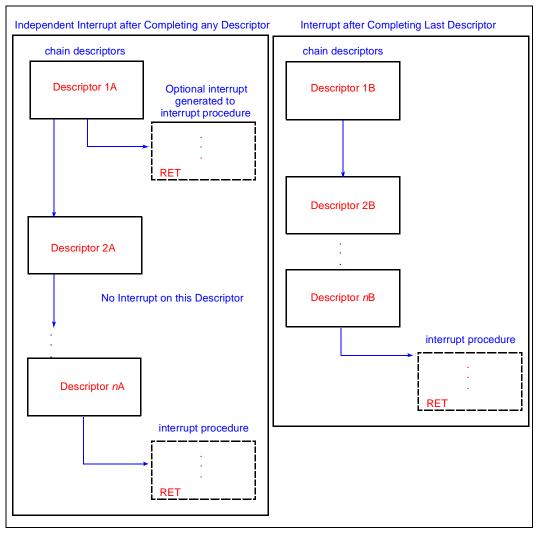

Each chain descriptor contains necessary information for initiating an XOR operation on blocks of data specified by the source addresses. The AA unit supports chaining. Chain descriptors that specify the source data to be XORed can be linked together in 80331 local memory to form a linked list.

Similar to XOR operations, AA can be programed to compute parity across multiple memory blocks specified by chain descriptors. In addition, AA is also used for memory block fills. A Dual-XOR operation is available for use when calculating two parity blocks for a RAID-6 single strip write.

In conjunction with the XOR and Dual-XOR operations, a GF Multiply calculation can be applied to source data in support of P+Q RAID-6. The AA will perform a GF Multiply between source data and a control byte for each source before the XOR operation when enabled. P+Q RAID-6 is enabled through an enable bit in the Section 1.13.1, "Accelerator Control Register - ACR" (bit 3).

## 1.3 Hardware-Assist XOR Unit

The AAU implements the XOR algorithm in hardware. It performs the XOR operation on multiple blocks of source (incoming) data and stores the result back in 80331 local memory.

- The process of reading source data, executing the XOR algorithm, and storing the XOR data will hereafter is referred to as *XOR-transfer*.

- The operation of two *XOR-transfers* defined in a single descriptor will hereafter be referred to as *Dual-XOR transfer*.

- The process of reading or writing data will hereafter is referred to as *data transfer*.

Source and destination addresses specified through chain descriptors resident in 80331 local memory.

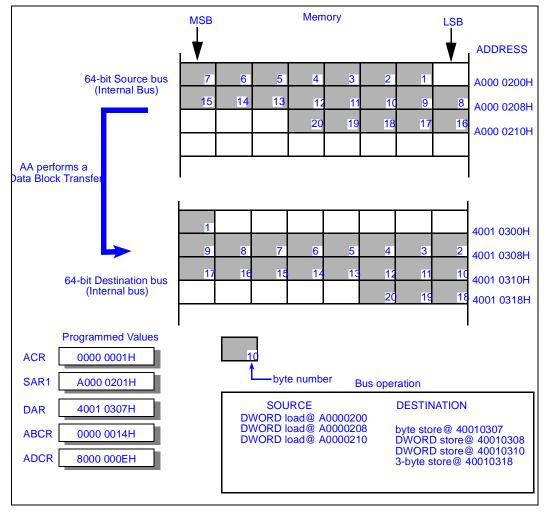

#### 1.3.1 Data Transfer

All transfers are configured and initiated through a set of memory-mapped registers and one or more chain descriptors located in local memory. A transfer is defined by the source address, destination address, number of bytes to transfer, and control values. These values are loaded in the chain descriptor before a transfer begins. Table 1 describes the registers that need to be configured for any operation.

When P+Q RAID-6 is enabled, the GF Multiplier bytes also act as control values in the data transfer.

| Register                                     | Abbreviation          | Description                                                                |

|----------------------------------------------|-----------------------|----------------------------------------------------------------------------|

| Accelerator Control Register                 | ACR                   | Application Accelerator Control Word                                       |

| Accelerator Status Register                  | ASR                   | Application Accelerator Status Word                                        |

| Accelerator Descriptor Address Register      | ADAR                  | Address of Current Chain Descriptor                                        |

| Accelerator Next Descriptor Address Register | ANDAR                 | Address of Next Chain Descriptor                                           |

| Data / Source Address Register1              | D/SAR1                | Data to be written or Local memory addresses of source data                |

| Source Address Register 232                  | SAR2 SAR32            | Local memory addresses of source data                                      |

| P+Q RAID-6 Source Address Register 216       | PQSAR2<br>PQSAR16     | Local memory addresses of source data when operating in<br>P+Q RAID-6 mode |

| P+Q RAID-6 GF Multiplier Register 15,D       | GFMR1 GFMR5,<br>GFMRD | P+Q RAID-6 GF Multiplier bytes<br>when operating in P+Q RAID-6 mode        |

| Destination Address Register                 | DAR                   | Address of result data                                                     |

| Accelerator Byte Count Register              | ABCR                  | Number of Bytes to transfer                                                |

| Data Register                                | DR                    | Data to be written to the destination                                      |

| Accelerator Descriptor Control Register      | ADCR                  | Chain Descriptor Control Word                                              |

#### Table 1. Register Description

### 1.3.2 Chain Descriptors

All transfers are controlled by chain descriptors located in local memory. A chain descriptor contains the necessary information to complete one transfer. A single transfer has only one chain descriptor in memory. Chain descriptors can be linked together to form more complex operations.

*Warning:* Chain descriptors can only be located in DDR SDRAM memory in order for the AAU to function properly. Location of the chain descriptors anywhere else (e.g., either on the Peripheral Bus or on PCI) is not supported and the results would be unpredictable.

To perform a transfer, one or more chain descriptors must first be written to 80331 local memory. The words of a descriptor are contiguous in local memory. Descriptors can be different sizes, each dependent on the number of sources being addressed by the operation. The sizes supported by the Application Accelerator are four, eight, sixteen and thirty-two sources. The alignment of the descriptor in local memory is dependent on the descriptor size and is defined for each in the following sections. Not all sources must be used in a given descriptor.

Descriptor formats for P+Q RAID-6 enabled operation are defined separately. When P+Q RAID-6 is enabled, only the P+Q RAID-6 descriptor formats are valid.

#### 1.3.2.1 Principle / Four-Source Descriptor Format

Figure 2 shows the format of an individual chain descriptor. This four-source descriptor is the smallest supported descriptor. The four-source descriptor requires eight contiguous words in 80331 local memory and is required to be aligned on an 8-word boundary. All eight words are required.

#### Figure 2. Principle / Four Source Descriptor Format

| Chain Descriptor in Local Memory | Description                                              |

|----------------------------------|----------------------------------------------------------|

| Next Descriptor Address (NDA)    | Address of Next Chain Descriptor                         |

| Source Address (D/SAR1)          | Immediate Data or Source Address for first block of data |

| Source Address (SAR2)            | Source Address for second block of data                  |

| Source Address (SAR3)            | Source Address for third block of data                   |

| Source Address (SAR4)            | Source Address for fourth block of data                  |

| Destination Address (DAR)        | Destination Address                                      |

| Byte Count (BC)                  | Number of bytes                                          |

| Descriptor Control (DC)          | Descriptor Control                                       |

Each word in the chain descriptor is analogous to control register values. Bit definitions for the words in the chain descriptor are the same as for the control registers.

- First word is local memory address of next chain descriptor. A value of zero specifies the end of the chain. This value is loaded into the Accelerator Next Descriptor Address Register. Because chain descriptors must be aligned on a minimum 8-word boundary, the unit may ignore bits 04:00 of this address.

- Second word is address of the first block of data resident in local memory, or immediate data when performing a Memory Block Fill. This value is loaded into the Data / Source Address Register 1.

- Third word is the address of the second block of data resident in local memory. This address is driven on the internal bus. This value is loaded into the Source Address Register 2.

- Fourth word is the address of the third block of data resident in local memory. This address is driven on the internal bus. This value is loaded into the Source Address Register 3.

- Fifth word is the address of the fourth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into the Source Address Register 4.

- Sixth word is the destination address where data is stored in local memory or PCI. This address is driven on the internal bus. This value is loaded into the Destination Address Register.

- Seventh word is the Byte Count value. This value specifies the number of bytes of data in the current chain descriptor. This value is loaded into the Accelerator Byte Count Register.

- Eighth word is the Descriptor Control Word. This word configures the Application Accelerator for one operation. This value is loaded into the Accelerator Descriptor Control Register.

There are no data alignment requirements for any source addresses or destination address. However, maximum performance is obtained from aligned transfers, especially small transfers. See Section 1.4.

Refer to Section 1.13 for additional description on the control registers.

#### 1.3.2.2 Eight-Source Descriptor Format

To perform an *XOR-transfer* with up to eight source blocks of data, a special chain descriptor needs to be configured:

- The first part is the four-source descriptor (referred to as the *principal-descriptor*) containing the address of the first 4 source data blocks along with other information.

- The second part (*mini-descriptor*) contains 4, DWORDs containing the address of the additional four (SAR5 SAR8) source data blocks. The mini-descriptor is written to a contiguous address immediately following the principal descriptor.

To perform a transfer, both parts (principal and mini-descriptor) must be written to local memory. Figure 3 shows the format of this eight-source descriptor. The eight-source descriptor requires twelve contiguous words in local memory and is required to be aligned on an 16-word boundary. All twelve words are required.

#### Figure 3. Chain Descriptor Format for Eight Source Addresses (XOR Function)

| ain Descriptor in I/O Processor Memory | Description                             |

|----------------------------------------|-----------------------------------------|

| Next Descriptor Address (NDA)          | Address of Next Chain Descriptor        |

| Source Address (D/SAR1)                | Source Address for first block of data  |

| Source Address (SAR2)                  | Source Address for second block of data |

| Source Address (SAR3)                  | Source Address for third block of data  |

| Source Address (SAR4)                  | Source Address for fourth block of data |

| Destination Address (DAR)              | Destination Address of XOR-ed data      |

| Byte Count (BC)                        | Number of bytes to XOR                  |

| Descriptor Control (DC)                | Descriptor Control                      |

| Source Address (SAR5)                  | Source Address for fifth data block     |

| Source Address (SAR6)                  | Source Address for sixth data block     |

| Source Address (SAR7)                  | Source Address for seventh data block   |

| Source Address (SAR8)                  | Source Address for eighth data block    |

- The first eight words are defined in the four-source descriptor definition. See Section 1.3.2.1, "Principle / Four-Source Descriptor Format" for the definition of these words.

- The ninth word (1st word of mini-descriptor) is the address of the fifth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR5.

- The tenth word (2nd word of mini-descriptor) is the address of the sixth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR6.

- The eleventh word (3rd word of mini-descriptor) is the address of the seventh block of data resident in local memory. This address is driven on the internal bus. This value is loaded SAR7.

- The twelfth word (4th word of mini-descriptor) is the address of the eighth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 8.

#### 1.3.2.3 Sixteen-Source Descriptor Format

To perform an *XOR-transfer* with up to sixteen source blocks of data, a special chain descriptor needs to be configured:

- The first part (*principal-descriptor*) contains the address of the first 4 source data blocks along with other information.

- The second part (*mini-descriptor*) contains four, DWORDs containing the address of the additional four (SAR5 SAR8) source data blocks. The mini-descriptor is written to a contiguous address immediately following the principal descriptor.

- The third part (*extended-descriptor 0*) contains nine, DWORDs containing the address of the additional eight (SAR9 SAR16) source data blocks and the command/control for these data blocks. The extended-descriptor 0 is written to a contiguous address immediately following the mini descriptor.

To perform a transfer, all three parts (principal descriptor, mini-descriptor and extended-descriptor 0) must be written to local memory. Figure 4 shows the format of this configuration. Every descriptor requires twenty one contiguous words in local memory and is required to be aligned on an 32-word boundary. All twenty one words are required.

#### Figure 4. Chain Descriptor Format for Sixteen Source Addresses (XOR Function)

| Next Descriptor Address (NDA)        | Address of Next Chain Descriptor            |

|--------------------------------------|---------------------------------------------|

| Source Address (D/SAR1)              | Source Address for first block of data      |

| Source Address (SAR2)                | Source Address for second block of data     |

| Source Address (SAR3)                | Source Address for third block of data      |

| Source Address (SAR4)                | Source Address for fourth block of data     |

| Destination Address (DAR)            | Destination Address of XOR-ed data          |

| Byte Count (BC)                      | Number of bytes to XOR                      |

| Descriptor Control (DC)              | Descriptor Control                          |

| Source Address (SAR5)                | Source Address for fifth data block         |

| Source Address (SAR6)                | Source Address for sixth data block         |

| Source Address (SAR7)                | Source Address for seventh data block       |

| Source Address (SAR8)                | Source Address for eighth data block        |

| Extended Descriptor Control 0 (EDC0) | Extended Descriptor 0 control               |

| Source Address (SAR9)                | Source Address for ninth block of data      |

| Source Address (SAR10)               | Source Address for tenth block of data      |

| Source Address (SAR11)               | Source Address for eleventh block of data   |

| Source Address (SAR12)               | Source Address for twelfth block of data    |

| Source Address (SAR13)               | Source Address for thirteenth block of data |

| Source Address (SAR14)               | Source Address for fourteenth block of data |

| Source Address (SAR15)               | Source Address for fifteenth block of data  |

# intel

- The first eight words are defined in the four-source descriptor definition. See Section 1.3.2.1, "Principle / Four-Source Descriptor Format" for the definition of these words.

- Words nine through twelve are defined in the eight-source descriptor definition. See Section 1.3.2.2, "Eight-Source Descriptor Format" for the definition of these words.

- The thirteenth word (1st word of extended-descriptor 0) is the Extended Descriptor Control Word 0. This word configures the Application Accelerator for one operation. The value is loaded into the Extended Descriptor Control Register 0.

- The fourteenth word (2nd word of extended-descriptor 0) is the address of the ninth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 9.

- The fifteenth word (3rd word of extended-descriptor 0) is the address of the tenth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 10.

- The sixteenth word (4th word of extended-descriptor 0) is the address of the eleventh block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 11.

- The seventeenth word (5th word of extended-descriptor 0) is the address of the twelfth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 12.

- The eighteenth word (6th word of extended-descriptor 0) is the address of the thirteenth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 13.

- The nineteenth word (7th word of extended-descriptor 0) is the address of the fourteenth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 14.

- The twentieth word (8th word of extended-descriptor 0) is the address of the fifteenth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 15.

- The twenty first word (9th word of extended-descriptor 0) is the address of the sixteenth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 16.

#### 1.3.2.4 Thirty-two-Source Descriptor Format

To perform an *XOR-transfer* with up to thirty two source blocks of data, a special chain descriptor needs to be configured:

- The first part (*principal-descriptor*) contains the address of the first 4 source data blocks along with other information.

- The second part (*mini-descriptor*) contains four, DWORDs containing the address of the additional four (SAR5 SAR8) source data blocks. The mini-descriptor is written to a contiguous address immediately following the principal descriptor.

- The third part (*extended-descriptor 0*) contains nine, DWORDs containing the address of the additional eight (SAR9 SAR16) source data blocks and the command/control for these data blocks. The extended-descriptor 0 is written to a contiguous address immediately following the mini descriptor.

- The fourth part (*extended-descriptor 1*) contains nine, DWORDs containing the address of the additional eight (SAR17 SAR24) source data blocks and the command/control for these data blocks. The extended-descriptor 1 is written to a contiguous address immediately following extended-descriptor 0.

- The fifth part (*extended-descriptor 2*) contains nine, DWORDs containing the address of the additional eight (SAR25 SAR32) source data blocks and the command/control for these data blocks. The extended-descriptor 2 is written to a contiguous address immediately following extended-descriptor 1.

To perform a transfer, all five parts (principal descriptor, mini-descriptor, extended-descriptor 0, extended-descriptor 1, and extended-descriptor 2) must be written to local memory. Figure 5 shows the format of this configuration. The full descriptor requires thirty nine contiguous words in local memory and is required to be aligned on an 64-word boundary. All thirty nine words are required.

#### Figure 5. Chain Descriptor Format for Thirty Two Source Addresses (XOR Function)

| in Descriptor in I/O Processor Memory | Description                                                                                 |  |

|---------------------------------------|---------------------------------------------------------------------------------------------|--|

| Next Descriptor Address (NDA)         | Address of Next Chain Descriptor                                                            |  |

| Source Address (D/SAR1)               | Source Address for first block of data                                                      |  |

| Source Address (SAR2)                 | Source Address for second block of data                                                     |  |

| Source Address (SAR3)                 | Source Address for third block of data                                                      |  |

| Source Address (SAR4)                 | Source Address for fourth block of data                                                     |  |

| Destination Address (DAR)             | Destination Address of XOR-ed data                                                          |  |

| Byte Count (BC)                       | Number of bytes to XOR                                                                      |  |

| Descriptor Control (DC)               | Descriptor Control                                                                          |  |

| Source Address (SAR5)                 | Source Address for fifth data block                                                         |  |

| Source Address (SAR6)                 | Source Address for sixth data block                                                         |  |

| Source Address (SAR7)                 | Source Address for seventh data block                                                       |  |

| Source Address (SAR8)                 | Source Address for eighth data block                                                        |  |

| Extended Descriptor Control 0 (EDC0)  | Extended Descriptor 0 control                                                               |  |

| Source Address (SAR9)                 | Source Address for ninth block of data                                                      |  |

| Source Address (SAR10)                | Source Address for tenth block of data                                                      |  |

| Source Address (SAR11)                | Source Address for eleventh block of data                                                   |  |

| Source Address (SAR12)                | Source Address for twelfth block of data                                                    |  |

| Source Address (SAR13)                | Source Address for thirteenth block of data                                                 |  |

| Source Address (SAR14)                | Source Address for fourteenth block of data                                                 |  |

| Source Address (SAR15)                | Source Address for fifteenth block of data                                                  |  |

| Source Address (SAR16)                | Source Address for sixteenth block of data                                                  |  |

| Extended Descriptor Control 1 (EDC1)  | Extended Descriptor 1 control                                                               |  |

| Source Address (SAR17)                | Source Address for seventeenth block of data                                                |  |

| Source Address (SAR18)                | Source Address for eighteenth block of data                                                 |  |

| Source Address (SAR19)                | Source Address for nineteenth block of data                                                 |  |

| Source Address (SAR20)                |                                                                                             |  |

| Source Address (SAR21)                | Source Address for twentieth block of data<br>Source Address for twenty first block of data |  |

| Source Address (SAR22)                | Source Address for twenty list block of data                                                |  |

| Source Address (SAR23)                | Source Address for twenty second block of data                                              |  |

| Source Address (SAR24)                | Source Address for twenty fund block of data                                                |  |

| Extended Descriptor Control 2 (EDC2)  | Extended Descriptor 2 control                                                               |  |

| Source Address (SAR25)                | Source Address for twenty fifth block of data                                               |  |

| Source Address (SAR26)                | Source Address for twenty sixth block of data                                               |  |

| Source Address (SAR27)                | Source Address for twenty seventh block of data                                             |  |

| Source Address (SAR28)                | Source Address for twenty eighth block of data                                              |  |

| Source Address (SAR29)                | Source Address for twenty ninth block of data                                               |  |

| Source Address (SAR30)                | Source Address for thirtieth block of data                                                  |  |

| Source Address (SAR31)                | Source Address for thirty first block of data                                               |  |

| Source Address (SAR32)                | Source Address for thirty second block of data                                              |  |

- The first eight words are defined in the Four-source descriptor definition. See Section 1.3.2.1, "Principle / Four-Source Descriptor Format" for the definition of these words.

- Words nine through twelve are defined in the Eight-source descriptor definition. See Section 1.3.2.2, "Eight-Source Descriptor Format" for the definition of these words.

- Words thirteen through twenty-one are defined in the Sixteen-source descriptor definition. See Section 1.3.2.3, "Sixteen-Source Descriptor Format" for the definition of these words.

- The twenty second word (1st word of extended-descriptor 1) is the Extended Descriptor Control Word 1. This word configures the Application Accelerator for one operation. The value is loaded into the Extended Descriptor Control Register 1.

- The twenty third word (2nd word of extended-descriptor 1) is the address of the seventeenth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR17.

- The twenty fourth word (3rd word of extended-descriptor 1) is the address of the eighteenth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 18.

- The twenty fifth word (4th word of extended-descriptor 1) is the address of the nineteenth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 19.

- The twenty sixth word (5th word of extended-descriptor 1) is the address of the twentieth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 20.

- The twenty seventh word (6th word of extended-descriptor 1) is the address of the twenty first block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 21.

- The twenty eighth word (7th word of extended-descriptor 1) is the address of the twenty second block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 22.

- The twenty ninth word (8th word of extended-descriptor 1) is the address of the twenty third block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 23.

- The thirtieth word (9th word of extended-descriptor 1) is the address of the twenty fourth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 24.

- The thirty first word (1st word of extended-descriptor 2) is the Extended Descriptor Control Word 2. This word configures the Application Accelerator for one operation. The value is loaded into the Extended Descriptor Control Register 2.

- The thirty second word (2nd word of extended-descriptor 2) is the address of the twenty fifth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 25.

- The thirty third word (3rd word of extended-descriptor 2) is the address of the twenty sixth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 26.

- The thirty fourth word (4th word of extended-descriptor 2) is the address of the twenty seventh block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 27.

- The thirty fifth word (5th word of extended-descriptor 2) is the address of the twenty eighth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 28.

- The thirty sixth word (6th word of extended-descriptor 2) is the address of the twenty ninth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 29.

- The thirty seventh word (7th word of extended-descriptor 2) is the address of the thirtieth block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 30.

- The thirty eighth word (8th word of extended-descriptor 2) is the address of the thirty first block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 31.

- The thirty ninth word (9th word of extended-descriptor 2) is the address of the thirty second block of data resident in local memory. This address is driven on the internal bus. This value is loaded into SAR 32.

#### 1.3.2.5 Dual-XOR-Transfer Descriptor Format

To perform a *Dual-XOR-transfer*, a special chain descriptor needs to be configured:

- The descriptor contains addresses for 4 source data blocks and 2 destination data buffers along with other information.

- This descriptor format is only valid when the *Dual-XOR-transfer* Enable bit (bit 27) in the Descriptor Control word is set.

- The format is based on the Eight Source Descriptor for *XOR-transfers*, and the control registers of the corresponding words take on a different meaning when processing this descriptor.

Figure 6 shows the format of this *Dual-XOR-transfer* descriptor. The *Dual-XOR-transfer* descriptor requires nine contiguous words in local memory and is required to be aligned on an 16-word boundary. All nine words are required.

#### Figure 6. Chain Descriptor Format for Dual-XOR-transfer

| ain Descriptor in I/O Processor Memory | Description                                   |

|----------------------------------------|-----------------------------------------------|

| Next Descriptor Address (NDA)          | Address of Next Chain Descriptor              |

| Source Address (SAR1)                  | Source Address for first block of data        |

| Source Address (SAR2)                  | Source Address for second block of data       |

| Horizontal Source Address (SAR_H)      | Source Address for Horizontal data            |

| Diagonal Source Address (SAR_D)        | Source Address for Diagonal data              |

| Horizontal Destination Address (DAR_H) | Destination Address of Horizontal XOR-ed data |

| Byte Count (BC)                        | Number of bytes to XOR                        |

| Descriptor Control (DC)                | Descriptor Control                            |

| Diagonal Destination Address (DAR_D)   | Destination Address for Diagonal XOR-ed data  |

Each word in the chain descriptor is analogous to control register values. Bit definitions for the words in the chain descriptor are the same as for the control registers.

- First word is local memory address of next chain descriptor. A value of zero specifies the end of the chain. This value is loaded into the Accelerator Next Descriptor Address Register. Because chain descriptors must be aligned on a minimum 8-word boundary, the unit may ignore bits 04:00 of this address.

- Second word is the address of the first block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into the Data / Source Address Register 1 (SAR1).

- Third word is the address of the second block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into the Source Address Register 2 (SAR2)

- Fourth word is the address of the third block of data resident in local memory. This address will be driven on the internal bus. This source is referred to as the Horizontal source, and is associated with the Horizontal Destination for the *Dual-XOR-transfer*. This value is loaded into the Horizontal Source Address Register (SAR3/SAR\_H).

- Fifth word is the address of the fourth block of data resident in local memory. This address will be driven on the internal bus. This source is referred to as the Diagonal source, and is associated with the Diagonal Destination for the *Dual-XOR-transfer*. This value is loaded into the Diagonal Source Address Register 4 (SAR4/SAR\_D).

# intel

- Sixth word is the destination address where the first XOR result will be stored in local memory. This address will be driven on the internal bus. This destination is referred to as the Horizontal Destination, and is associated with the Horizontal Source for the *Dual-XOR-transfer*. This value is loaded into the Destination Address Register (DAR/DAR\_H).

- Seventh word is the Byte Count value. This value specifies the number of bytes of data in the current chain descriptor. This value is loaded into the Accelerator Byte Count Register.

- Eighth word is the Descriptor Control Word. This word configures the Application Accelerator for one operation. This value is loaded into the Accelerator Descriptor Control Register.

- The ninth word is the destination address where the second XOR result will be stored in local memory. This address will be driven on the internal bus. This destination is referred to as the Diagonal Destination, and is associated with the Diagonal Source for the *Dual-XOR-transfer*. This value is loaded into the Diagonal Destination Address Register (SAR5/DAR\_D).

There are no data alignment requirements for any source addresses. While the destinations addresses (Horizontal and Diagonal) also have no data alignment requirements relative to memory, the alignment of the Horizontal and Diagonal destination addresses must match (relative to 16 Byte address).

Refer to Section 1.13 for additional description on the control registers.

#### 1.3.2.6 P+Q Three-Source Descriptor Format

Figure 7 shows the format of an individual chain descriptor when P+Q RAID-6 is enabled. This three-source descriptor is the smallest supported descriptor for P+Q RAID-6 operations. The three-source descriptor requires eight contiguous words in 80331 local memory and is required to be aligned on an 8-word boundary. All eight words are required.

#### Figure 7. P+Q Base Chain Descriptor Format

| Chain Descriptor in Local Memory | Description                                              |

|----------------------------------|----------------------------------------------------------|

| Next Descriptor Address (NDA)    | Address of Next Chain Descriptor                         |

| Source Address (D/PQSAR1)        | Immediate Data or Source Address for first block of data |

| Source Address (PQSAR2)          | Source Address for second block of data                  |

| Source Address (PQSAR3)          | Source Address for third block of data                   |

| Data Multiplier Values (PQMR1)   | Data Multiplier Values for Sources 1 through 3           |

| Destination Address (DAR)        | Destination Address                                      |

| Byte Count (BC)                  | Number of bytes                                          |

| Descriptor Control (DC)          | Descriptor Control                                       |

Each word in the chain descriptor is analogous to control register values. Bit definitions for the words in the chain descriptor are the same as for the control registers.

- First word is local memory address of next chain descriptor. A value of zero specifies end of chain. Value is loaded into the Accelerator Next Descriptor Address Register. Because chain descriptors must be aligned on a minimum 8-word boundary, unit may ignore bits 04:00 of this address.

- Second word is address of the first block of data resident in local memory, or immediate data when performing a Memory Block Fill. This value is loaded into the Data / P+Q RAID-6 Source Address Register 1 (D/PQSAR1).

- Third word is address of second block of data resident in local memory. This address is driven on the internal bus. This value is loaded into the P+Q RAID-6 Source Address Register 2 (PQSAR2).

- Fourth word is address of third block of data resident in local memory and is driven on the internal bus. This value is loaded into P+Q RAID-6 Source Address Register 3 (PQSAR3).

- Fifth word contains Data Multiplier Values (DMLTx) for source addresses 1 through 3. These bytes are used as control input for GF Multiply of corresponding source. The respective byte will be driven to the GF Multiply when source data is being fetched. The lowest order byte of this word contains the data multiplier for source address 1, the second byte for source address 2, the third byte for source address 3, and the highest order byte is not used and is reserved. This value is loaded into the P+Q RAID-6 GF Multiply Multiplier Register 1 (GFMR1).

- Sixth word is the destination address where data will be stored in local memory. This address will be driven on the internal bus. This value is loaded into the Destination Address Register.

- Seventh word is the Byte Count value. This value specifies the number of bytes of data in the current chain descriptor. This value is loaded into the Accelerator Byte Count Register.

- Eighth word is the Descriptor Control Word. This word configures the Application Accelerator for one operation. This value is loaded into the Accelerator Descriptor Control Register.

There are no data alignment requirements for any source addresses or destination address. However, maximum performance is obtained from aligned transfers, especially small transfers. See Section 1.4.

Refer to Section 1.13 for additional description on the control registers.

#### 1.3.2.7 P+Q Six-Source Descriptor Format

To perform an P+Q RAID-6 *XOR-transfer* with up to six source blocks of data, a special chain descriptor needs to be configured:

- First part: three-source descriptor (referred to as *principal-descriptor*) containing source address and data multiplier values of first 3 source data blocks along with other information.

- Second part: (*mini-descriptor*) contains 4 DWORDs containing the address of the additional three source data blocks and Data Multiplier values. The mini-descriptor is written to a contiguous address immediately following the principal descriptor.

To perform a transfer, both parts (principal and mini-descriptor) must be written to local memory. Figure 8 shows the format of this eight-source descriptor. The six-source descriptor requires twelve contiguous words in local memory and is required to be aligned on an 16-word boundary. All twelve words are required.

#### Figure 8. P+Q Chain Descriptor Format for Six Source Addresses (XOR Function)

| hain Descriptor in I/O Processor Memory | Description                                    |

|-----------------------------------------|------------------------------------------------|

| Next Descriptor Address (NDA)           | Address of Next Chain Descriptor               |

| Source Address (PQSAR1)                 | Source Address for first block of data         |

| Source Address (PQSAR2)                 | Source Address for second block of data        |

| Source Address (PQSAR3)                 | Source Address for third block of data         |

| Data Multiplier Values (GFMR1)          | Data Multiplier Values for Sources 1 through 3 |

| Destination Address (DAR)               | Destination Address of XOR-ed data             |

| Byte Count (BC)                         | Number of bytes to XOR                         |

| Descriptor Control (DC)                 | Descriptor Control                             |

| Source Address (PQSAR4)                 | Source Address for fourth data block           |

| Source Address (PQSAR5)                 | Source Address for fifth data block            |

| Source Address (PQSAR6)                 | Source Address for sixth data block            |

| Data Multiplier Values (GFMR2)          | Data Multiplier Values for Sources 4 through 6 |

- The first eight words are defined in the three-source descriptor definition. See Section 1.3.2.1 for the definition of these words.

- The ninth word (1st word of mini-descriptor) is the address of the fourth block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into PQSAR4.

- The tenth word (2nd word of mini-descriptor) is the address of the fifth block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into PQSAR5.

- The eleventh word (3rd word of mini-descriptor) is the address of the sixth block of data resident in local memory. This address will be driven on the internal bus. This value is loaded PQSAR6

- The twelfth word contains the Data Multiplier Values (DMLT) for source addresses 4 through 6. These bytes are used as the control input for the GF Multiply of the corresponding source. The respective byte will be driven to the GF Multiply when source data is being fetched. The lowest order byte of this word contains the data multiplier for source address 4, the second byte for source address 5, the third byte for source address 6, and the highest order byte is not used and is reserved. This value is loaded into the P+Q RAID-6 GF Multiply Multiplier Register 2 (GFMR2).

#### 1.3.2.8 P+Q Twelve-Source Descriptor Format

To perform an *XOR-transfer* with a GF Multiply data multiplier on up to twelve source blocks of data, a special chain descriptor needs to be configured:

- The first part (*principal-descriptor*) contains the address of the first 3 source data blocks and data multiplier values along with other information.

- The second part (*mini-descriptor*) contains four, DWORDs containing the address of the additional three source data blocks and data multiplier values. The mini-descriptor is written to a contiguous address immediately following the principal descriptor.

- The third part (*extended-descriptor 0*) contains nine, DWORDs containing the address of the additional six source data blocks and data multiplier values. The extended-descriptor 0 is written to a contiguous address immediately following the mini descriptor.

To perform a transfer, all three parts (principal descriptor, mini-descriptor and extended-descriptor 0) must be written to local memory. Figure 9 shows the format of this configuration. Every descriptor requires twenty one contiguous words in local memory and is required to be aligned on an 32-word boundary. All twenty one words are required.

#### Figure 9. P+Q Chain Descriptor Format for Twelve Source Addresses (XOR Function)

| Chain Descriptor in Intel XScale <sup>®</sup> Core Memory Description |                                                  |  |  |  |  |  |

|-----------------------------------------------------------------------|--------------------------------------------------|--|--|--|--|--|

| Next Descriptor Address (NDA)                                         | Address of Next Chain Descriptor                 |  |  |  |  |  |

| Source Address (D/PQSAR1)                                             | Source Address for first block of data           |  |  |  |  |  |

| Source Address (PQSAR2)                                               | Source Address for second block of data          |  |  |  |  |  |

| Source Address (PQSAR3)                                               | Source Address for third block of data           |  |  |  |  |  |

| Data Multiplier Values (GFMR1)                                        | Data Multiplier Values for Sources 1 through 3   |  |  |  |  |  |

| Destination Address (DAR)                                             | Destination Address of XOR-ed data               |  |  |  |  |  |

| Byte Count (BC)                                                       | Number of bytes to XOR                           |  |  |  |  |  |

| Descriptor Control (DC)                                               | Descriptor Control                               |  |  |  |  |  |

| Source Address (PQSAR4)                                               | Source Address for fourth data block             |  |  |  |  |  |

| Source Address (PQSAR5)                                               | Source Address for fifth data block              |  |  |  |  |  |

| Source Address (PQSAR6)                                               | Source Address for sixth data block              |  |  |  |  |  |

| Data Multiplier Values (GFMR2                                         | Data Multiplier Values for Sources 4 through 6   |  |  |  |  |  |

| Extended Descriptor Control 0 (EDC0)                                  | Extended Descriptor 0 control                    |  |  |  |  |  |

| Source Address (PQSAR7)                                               | Source Address for seventh block of data         |  |  |  |  |  |

| Source Address (PQSA8)R                                               | Source Address for eighth block of data          |  |  |  |  |  |

| Source Address (PQSAR9)                                               | Source Address for ninth block of data           |  |  |  |  |  |

| Data Multiplier Values (GFMR3)                                        | Data Multiplier Values for Sources 7 through 9   |  |  |  |  |  |

| Source Address (PQSAR10)                                              | Source Address for tenth block of data           |  |  |  |  |  |

| Source Address (PQSAR11)                                              | Source Address for eleventh block of data        |  |  |  |  |  |

| Source Address (PQSAR12)                                              | Source Address for twelfth block of data         |  |  |  |  |  |

| Data Multiplier Values (GFMR4)                                        | Data Multiplier Values for Sources 10 through 12 |  |  |  |  |  |

# intel

- The first eight words are defined in the three-source descriptor definition. See Section 1.3.2.6, "P+Q Three-Source Descriptor Format" for the definition of these words.

- Words nine through twelve are defined in the six-source descriptor definition. See Section 1.3.2.7, "P+Q Six-Source Descriptor Format" for the definition of these words.

- The thirteenth word (1st word of extended-descriptor 0) is the Extended Descriptor Control Word 0. This word configures the Application Accelerator for one operation. The value is loaded into the Extended Descriptor Control Register 0.

- The fourteenth word (2nd word of extended-descriptor 0) is the address of the seventh block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into PQSAR7.

- The fifteenth word (3rd word of extended-descriptor 0) is the address of the eighth block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into PQSAR8.

- The sixteenth word (4th word of extended-descriptor 0) is the address of the ninth block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into PQSAR9.

- The seventeenth word (5th word of extended-descriptor 0) contains the Data Multiplier Values (DMLTx) for source addresses 7 through 9. These bytes are used as the control input for the TDIfn of the corresponding source. The respective byte will be driven to the GF Multiply when source data is being fetched. The lowest order byte of this word contains the data multiplier for source address 7, the second byte for source address 8, the third byte for source address 9, and the highest order byte is not used and is reserved. This value is loaded into the P+Q RAID-6 GF Multiply Multiplier Register 3 (GFMR3).

- The eighteenth word (6th word of extended-descriptor 0) is the address of the tenth block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into PQSAR10.

- The nineteenth word (7th word of extended-descriptor 0) is the address of the eleventh block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into PQSAR11.

- The twentieth word (8th word of extended-descriptor 0) is the address of the twelfth block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into PQSAR12.

- The twenty first word (9th word of extended-descriptor 0) contains the Data Multiplier Values (DMLTx) for source addresses 10 through 12. These bytes are used as the control input for the GF Multiply of the corresponding source. The respective byte will be driven to the GF Multiply when source data is being fetched. The lowest order byte of this word contains the data multiplier for source address 10, the second byte for source address 11, the third byte for source address 12, and the highest order byte is not used and is reserved. This value is loaded into the P+Q RAID-6 GF Multiply Multiplier Register 4 (GFMR4).

#### 1.3.2.9 P+Q Sixteen-Source Descriptor Format

To perform an P+Q RAID-6 *XOR-transfer* with up to sixteen source blocks of data, a special chain descriptor needs to be configured:

- The first part (*principal-descriptor*) contains the address of the first 3 source data blocks (PQSAR1 PQSAR3) and data multiplier values along with other information.

- The second part (*mini-descriptor*) contains four, DWORDs containing the address of the additional three (PQSAR4 PQSAR6) source data blocks and data multiplier values. The mini-descriptor is written to a contiguous address immediately following the principal descriptor.

- The third part (*extended-descriptor 0*) contains nine, DWORDs containing the address of the additional six (PQSAR7 PQSAR12) source data blocks and data multiplier values. The extended-descriptor 0 is written to a contiguous address immediately following the mini descriptor.

- The fourth part (*extended-descriptor 1*) contains nine, DWORDs containing the address of the additional four (PQSAR13 PQSAR16) source data blocks and data multiplier values along with the command/control for these data blocks. The extended-descriptor 1 is written to a contiguous address immediately following extended-descriptor 0.

To perform a transfer, all four parts (principal descriptor, mini-descriptor, extended-descriptor 0, and extended-descriptor 1) must be written to local memory. Figure 10 shows the format of this configuration. The full descriptor requires twenty-seven contiguous words in local memory and is required to be aligned on an 32-word boundary. All twenty-seven words are required.

#### Figure 10. P+Q Chain Descriptor Format for Sixteen Source Addresses (XOR Function)

| Chain Descriptor in I/O Processor Memory | Description                                      |

|------------------------------------------|--------------------------------------------------|

| Next Descriptor Address (NDA)            | Address of Next Chain Descriptor                 |

| Source Address (D/PQSAR1)                | Source Address for first block of data           |

| Source Address (PQSAR2)                  | Source Address for second block of data          |

| Source Address (PQSAR3)                  | Source Address for third block of data           |

| Data Multiplier Values (GFMR1)           | Data Multiplier Values for Sources 1 through 3   |

| Destination Address (DAR)                | Destination Address of XOR-ed data               |

| Byte Count (BC)                          | Number of bytes to XOR                           |

| Descriptor Control (DC)                  | Descriptor Control                               |

| Source Address (PQSAR4)                  | Source Address for fourth data block             |

| Source Address (PQSAR5)                  | Source Address for fifth data block              |

| Source Address (PQSAR6)                  | Source Address for sixth data block              |

| Data Multiplier Values (GFMR2)           | Data Multiplier Values for Sources 4 through 6   |

| Extended Descriptor Control 0 (EDC0)     | Extended Descriptor 0 control                    |

| Source Address (PQSAR7)                  | Source Address for seventh block of data         |

| Source Address (PQSAR8)                  | Source Address for eighth block of data          |

| Source Address (PQSAR9)                  | Source Address for ninth block of data           |

| Data Multiplier Values (GFMR3)           | Data Multiplier Values for Sources 4 through 9   |

| Source Address (PQSAR10)                 | Source Address for tenth block of data           |

| Source Address (PQSAR11)                 | Source Address for eleventh block of data        |

| Source Address (PQSAR12)                 | Source Address for twelfth block of data         |

| Data Multiplier Values (GFMR4)           | Data Multiplier Values for Sources 10 through 12 |

| Reserved                                 | Reserved - not used                              |

| Source Address (PQSAR13)                 | Source Address for thirteenth block of data      |

| Source Address (PQSAR14)                 | Source Address for fourteenth block of data      |

| Source Address (PQSAR15)                 | Source Address for fifteenth block of data       |

| Source Address (PQSAR16)                 | Source Address for sixteenth block of data       |

| Data Multiplier Values (GFMR5)           | Data Multiplier Values for Sources 13 through 16 |

- The first eight words are defined in the three-source descriptor definition. See Section 1.3.2.6, "P+Q Three-Source Descriptor Format" for the definition of these words.

- Words nine through twelve are defined in the six-source descriptor definition. See Section 1.3.2.7, "P+Q Six-Source Descriptor Format" for the definition of these words.

- Words thirteen through twenty-one are defined in the Twelve-source descriptor definition. See Section 1.3.2.8, "P+Q Twelve-Source Descriptor Format" for the definition of these words.

- The twenty second word (1st word of extended-descriptor 1) is reserved and not used by the AA in the processing of this descriptor.

- The twenty third word (2nd word of extended-descriptor 1) is the address of the thirteenth block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into PQSAR12.

- The twenty fourth word (3rd word of extended-descriptor 1) is the address of the fourteenth block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into PQSAR12.

- The twenty fifth word (4th word of extended-descriptor 1) is the address of the fifteenth block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into PQSAR12.

- The twenty sixth word (5th word of extended-descriptor 1) is the address of the sixteenth block of data resident in local memory. This address will be driven on the internal bus. This value is loaded into PQSAR12.

- The twenty seventh word (6th word of extended-descriptor 1) contains the Data Multiplier Values (DMLTx) for source addresses 13 through 16. These bytes are used as the control input for the GF Multiply of the corresponding source. The respective byte will be driven to the GF Multiply when source data is being fetched. The lowest order byte of this word contains the data multiplier for source address 13, the second byte for source address 14, the third byte for source address 15, and the highest order byte for source address 16. This value is loaded into the P+Q RAID-6 GF Multiply Multiplier Register 5 (GFMR5).

- *Note:* The highest order byte (bits[31:24]) is unused in other Data Multiplier words GFMR[4:1], but is defined in GFMR5.

# 1.3.3 Descriptor Summary

Table 2 summarizes the content of the descriptors defined in previous sections.

| Register Address | 4-Source XOR | 8-Source XOR | 16-Source XOR | 32-Source XOR | Dual XOR | P+Q 3-Source | P+Q 6-Source | P+Q 12-Source | P+Q 16-Source |

|------------------|--------------|--------------|---------------|---------------|----------|--------------|--------------|---------------|---------------|

| FFFF<br>E80Ch    | NDA          | NDA          | NDA           | NDA           | NDA      | NDA          | NDA          | NDA           | NDA           |

| FFFF<br>E810h    | SAR1         | SAR1         | SAR1          | SAR1          | SAR1     | SAR1         | SAR1         | SAR1          | SAR1          |

| FFFF<br>E814h    | SAR2         | SAR2         | SAR2          | SAR2          | SAR2     | SAR2         | SAR2         | SAR2          | SAR2          |

| FFFF<br>E818h    | SAR3         | SAR3         | SAR3          | SAR3          | SAR_H    | SAR3         | SAR3         | SAR3          | SAR3          |

| FFFF<br>E81Ch    | SAR4         | SAR4         | SAR4          | SAR4          | SAR_D    | GFMR1        | GFMR1        | GFMR1         | GFMR1         |

| FFFF<br>E820h    | DAR          | DAR          | DAR           | DAR           | DAR_H    | DAR          | DAR          | DAR           | DAR           |

| FFFF<br>E824h    | BC           | BC           | BC            | BC            | BC       | BC           | BC           | BC            | BC            |

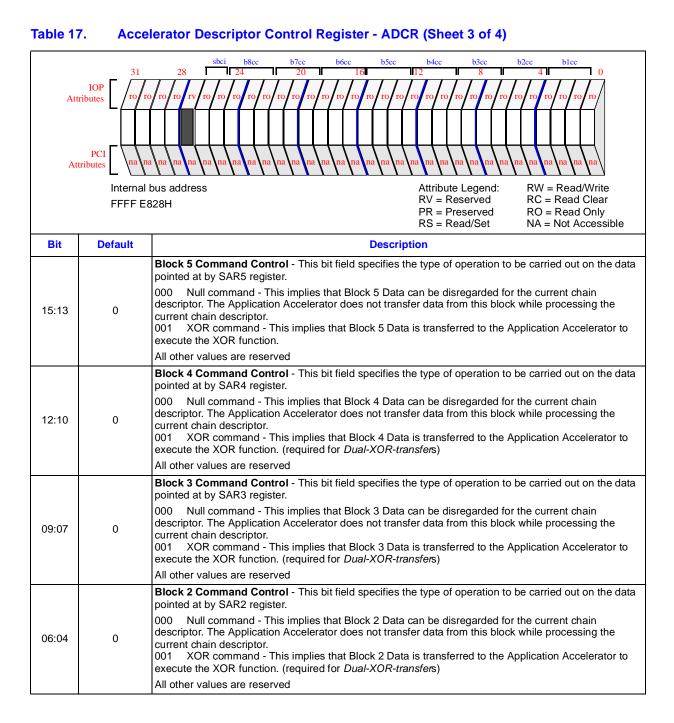

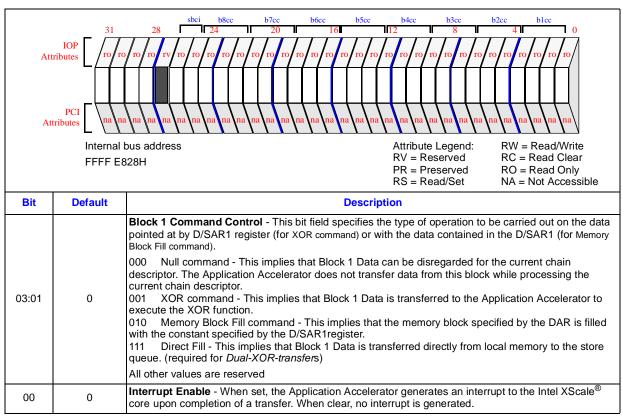

| FFFF<br>E828h    | DC           | DC           | DC            | DC            | DC       | DC           | DC           | DC            | DC            |