### Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache Dual Processor Platform Design Guide

June 2001

Document Number 249658-001

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

The Pentium<sup>®</sup> III Processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

Pentium<sup>®</sup> III Processor is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries. \*Other names and brands may be claimed as the property of others.

# intപ്രം Contents

| 1 | Desi | gn Guide Introduction                                                               | 1-1                                                                       |

|---|------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|   | 1.1  | Audience                                                                            | 1-1                                                                       |

|   | 1.2  | Related Documents                                                                   |                                                                           |

|   | 1.3  | Conventions and Terminology                                                         |                                                                           |

|   | 1.4  | State of the Data                                                                   | 1-3                                                                       |

| 2 | Gene | eral Design Considerations                                                          |                                                                           |

|   | 2.1  | Nominal Board Stackup                                                               |                                                                           |

|   | 2.2  | Socket 370 Component Keepout                                                        | 2-2                                                                       |

| 3 | Proc | essor Host Bus Design                                                               | 3-1                                                                       |

|   | 3.1  | Initial Timing Analysis                                                             | 3-1                                                                       |

|   | 3.2  | General Topology and Layout Guidelines                                              | 3-2                                                                       |

|   | 3.3  | Terminator-less T Topology                                                          |                                                                           |

|   | 3.4  | Wired-OR Signal Considerations                                                      |                                                                           |

|   | 3.5  | Simulation Methodology                                                              |                                                                           |

|   | 3.6  | Trace Routing                                                                       |                                                                           |

|   | 3.7  | Layout Rules for AGTL Signals                                                       |                                                                           |

|   |      | <ul> <li>3.7.1 Ground Reference</li></ul>                                           |                                                                           |

|   |      | <ul><li>3.7.2 Reference Plane Splits</li><li>3.7.3 CPU Connector Breakout</li></ul> |                                                                           |

|   |      | 3.7.4 Minimizing Crosstalk                                                          |                                                                           |

|   | 3.8  | Layout Rules for Non-AGTL (CMOS) Signals                                            |                                                                           |

|   | 3.9  | Undershoot/Overshoot Requirements                                                   |                                                                           |

|   | 3.10 | Debug Port Routing Guidelines                                                       |                                                                           |

|   |      | 3.10.1 Target System Implementation                                                 | 3-9                                                                       |

| 4 | Cloc | king                                                                                | 4-1                                                                       |

|   | 4.1  | General Clocking Considerations                                                     | 4-1                                                                       |

|   | 4.2  | Single Ended Host Bus Clocking Routing                                              |                                                                           |

|   |      | 4.2.1 CLKREF Filter Implementation                                                  |                                                                           |

|   |      | 4.2.2 Single-Ended Clocking BSEL[1:0] Implementation                                |                                                                           |

|   | 4.3  | Differential Host Bus Clocking Routing                                              |                                                                           |

|   |      | 4.3.1 Differential Clocking Topology                                                | 3-4<br>3-7<br>3-7<br>3-7<br>3-7<br>3-7<br>3-7<br>3-7<br>3-7<br>3-7<br>3-7 |

|   |      | 4.3.2 Differential Clocking BSEL[1:0] Implementation                                |                                                                           |

|   | 4.4  | Debug Port Host Clock Connection                                                    |                                                                           |

|   | 4.5  | Clock Driver Decoupling and Power Delivery                                          | 4-8                                                                       |

| 5 | Powe | er                                                                                  | 5-1                                                                       |

|   | 5.1  | Terminology                                                                         |                                                                           |

|   | 5.2  | Typical Power Delivery                                                              |                                                                           |

|   | 5.3  | Dual Processor Power Requirements                                                   |                                                                           |

|   |      | 5.3.1 Voltage Tolerance                                                             |                                                                           |

|   |      | 5.3.2 Multiple Voltages                                                             |                                                                           |

|   |      | 5.3.3 Voltage Sequencing                                                            |                                                                           |

|   | 5.4  | Meeting Power Requirements<br>5.4.1 Supplying Voltage                               |                                                                           |

|   |      | 5.4.1 Supplying Voltage                                                             |                                                                           |

|   |            | 5.4.2 Decoupling Technology and Transient Response    |     |  |  |

|---|------------|-------------------------------------------------------|-----|--|--|

|   | 5.5        | Recommendations                                       |     |  |  |

|   |            | 5.5.1 Decoupling Guidelines                           |     |  |  |

|   |            | 5.5.2 Processor PLL Filter Recommendations            | 5-8 |  |  |

| 6 | Ther       | mals                                                  | 6-1 |  |  |

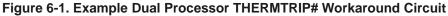

|   | 6.1        | THERMTRIP# Requirements                               | 6-1 |  |  |

|   | 6.2        | THERMTRIP# Erratum                                    | 6-1 |  |  |

| 7 | Proc       | essor Migration Considerations                        | 7-1 |  |  |

|   | 7.1        | Overview                                              | 7-1 |  |  |

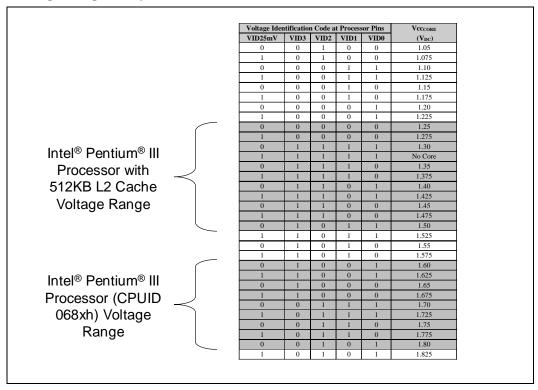

|   | 7.2        | Implement VRM 8.5                                     |     |  |  |

|   |            | 7.2.1 VRM 8.5 Voltage Range                           | 7-1 |  |  |

|   |            | 7.2.2 Active Voltage Positioning                      | 7-2 |  |  |

|   |            | 7.2.3 VRM 8.5 Modules                                 |     |  |  |

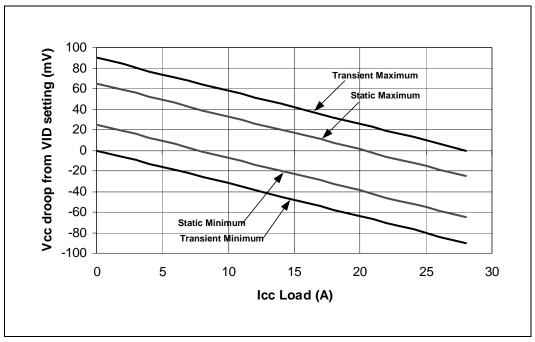

|   | 7.3        | Package Changes (FC-PGA2)                             |     |  |  |

|   | 7.4        | Pinout Changes                                        |     |  |  |

|   | 7.5        | Dual Processor Specific Pin Recommendations           |     |  |  |

|   |            | 7.5.1 DETECT (AF36)                                   |     |  |  |

|   |            | 7.5.2 RESET2 (AJ3)                                    |     |  |  |

|   | 7.0        | 7.5.3 KEY (AM2)                                       |     |  |  |

|   | 7.6        | AGTL Bus Transition                                   |     |  |  |

|   | 7.7        | Host Bus Layout Changes                               |     |  |  |

|   | 7.8<br>7.9 | Single Ended Clocking Support                         |     |  |  |

|   | 7.9        | VID & BSEL Signals<br>7.9.1 Power On Sequence         |     |  |  |

|   |            | 7.9.2 Signalling Changes                              |     |  |  |

|   |            | 7.9.3 Legacy Clock Driver Support                     |     |  |  |

|   | 7.10       | PICCLK Voltage Change                                 |     |  |  |

|   | 7.11       | ITP Changes                                           |     |  |  |

|   | 7.12       | Logic Analyzer Interface                              |     |  |  |

| 8 | Syste      | em Design Checklist                                   | 8-1 |  |  |

|   | 8.1        | Introduction                                          | 8-1 |  |  |

|   | 8.2        | Design Checklist Summary                              |     |  |  |

|   | 8.3        | Host Interface AGTL Bus and AGTL Signals              |     |  |  |

|   | 8.4        | CMOS (Non-AGTL) Signals                               |     |  |  |

|   | 8.5        | TAP/ITP Checklist for 370-Pin Socket Processors       |     |  |  |

|   | 8.6        | Miscellaneous Checklist for 370-Pin Socket Processors |     |  |  |

## Index of Figures

| 2-1  | Sample Board Stackup                                  | 2-1  |

|------|-------------------------------------------------------|------|

| 2-2  | Socket 370 Component Keepout                          |      |

| 2-3  | Socket 370 Volumetric Keepout                         | 2-3  |

| 3-1  | System Bus T-Topology                                 | 3-3  |

| 3-2  | Terminator-less System Bus T Topology                 | 3-4  |

| 3-3  | Wired-OR Termination Topology                         | 3-6  |

| 3-4  | Simple Terminations                                   | 3-10 |

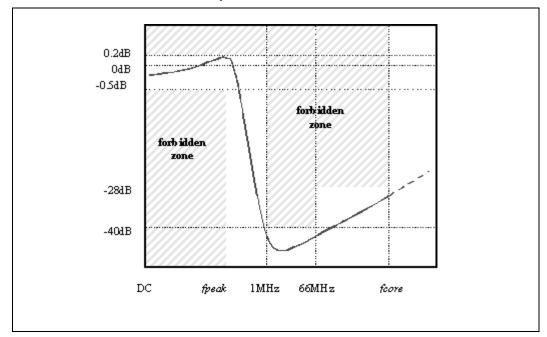

| 3-5  | TCK Termination, DP System                            | 3-11 |

| 3-6  | PRDYx# Signal Termination                             | 3-12 |

| 3-7  | RESET# Signal Termination                             | 3-12 |

| 3-8  | JTAG Signals TDI/TDO for Processor Only               | 3-14 |

| 3-9  | TDO 3-Pin Jumper Bypass                               | 3-15 |

| 3-10 | 4-Pin Jumper Bypass                                   | 3-15 |

| 4-1  | Host Bus Clock Connections                            | 4-2  |

| 4-2  | Single Ended Clocking Topology - CPU                  | 4-3  |

| 4-3  | Single Ended Clocking Topology - Chipset              | 4-3  |

| 4-4  | CLKREF Filter Implementation                          | 4-4  |

| 4-5  | Single Ended Clock BSEL Circuit                       |      |

| 4-6  | Differential Clocking Topology                        |      |

| 4-7  | Differential Clock BSEL Circuit                       |      |

| 4-8  | Debug Port Differential Host Clock Implementation     |      |

| 5-1  | Ideal Processor Power Supply Scheme                   |      |

| 5-2  | Power Distribution for a DP System Motherboard        |      |

| 5-3  | Detailed Power Distribution Model for System with VRM |      |

| 5-4  | VRM 8.5 Board Power Distribution Model                |      |

| 5-5  | 1206 Capacitor Pad and Via Layouts                    |      |

| 5-6  | PGA370 Decoupling Capacitor Placement                 |      |

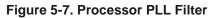

| 5-7  | Processor PLL Filter                                  |      |

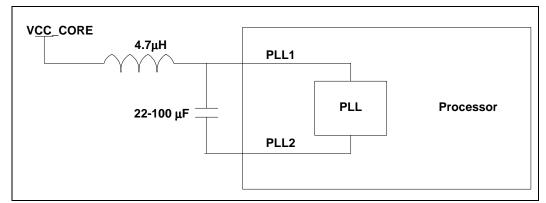

| 5-8  | PLL Power Low Pass Filter Response                    | 5-9  |

| 6-1  | Example Dual Processor THERMTRIP# Workaround Circuit  | 6-2  |

| 7-1  | Voltage Range Comparison                              |      |

| 7-2  | Active Voltage Positioning Operating Parameters       |      |

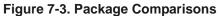

| 7-3  | Package Comparisons                                   | 7-4  |

| 7-4  | Electrical Keying Mechanism                           |      |

| 7-5  | SE Clocking Implementation                            | 7-8  |

|      |                                                       |      |

### **Index of Tables**

| 3-1  | System Timing Equations                                            | 3-1  |

|------|--------------------------------------------------------------------|------|

| 3-2  | System Timing Terms                                                |      |

| 3-3  | System Bus Timing Parameters                                       |      |

| 3-4  | Sample CPU to CPU flight time calculations                         |      |

| 3-5  | Trace Lengths for T Topology (ServerWorks Chipset)                 |      |

| 3-6  | Component Values for T Topology                                    |      |

| 3-7  | Trace Lengths for Terminator-less T Topology (ServerWorks Chipset) |      |

| 3-8  | Component Values for Terminator-less T Topology                    |      |

| 3-9  | Wired-OR Values                                                    |      |

| 3-10 | System Signal Layout Guidelines                                    | 3-10 |

| 3-11 | JTAG Signal Layout Guidelines                                      | 3-11 |

| 3-12 | Execution Signals Routing Guidelines                               | 3-11 |

| 3-13 | Debug Port Termination Requirement                                 |      |

| 3-14 | Routing Guidelines                                                 |      |

| 4-1  | Component Values for SE Clocking Topology - CPU                    | 4-3  |

| 4-2  | Component Values for SE Clocking Topology - Chipset                |      |

| 4-3  | CLKREF Component Values                                            | 4-5  |

| 4-4  | Component Values for Differential Clocking                         | 4-6  |

| 5-1  | Bulk Capacitance Recommendations                                   | 5-6  |

| 5-2  | Vcc <sub>CORE</sub> High Frequency Capacitance Recommendations     | 5-7  |

| 6-1  | THERMTRIP# Timing Requirements                                     | 6-1  |

| 7-1  | Pin Differences List                                               | 7-4  |

| 7-2  | Signalling Parameter Comparisons                                   | 7-6  |

| 8-1  | AGTL Signals                                                       | 8-1  |

| 8-2  | CMOS Signals                                                       | 8-2  |

| 8-3  | TAP/ITP Signals                                                    | 8-3  |

| 8-4  | Clock Signals                                                      | 8-4  |

| 8-5  | Miscellaneous Signals                                              | 8-4  |

| 8-6  | Power Signals                                                      | 8-5  |

#### **Revision History**

| Revision | Draft/Changes   | Date      |

|----------|-----------------|-----------|

| -001     | Initial Version | June 2001 |

This page intentionally left blank

# Design Guide Introduction

This design guide documents Intel's design recommendations for dual-processor systems based on the Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache and the Intel<sup>®</sup> Pentium<sup>®</sup> III Processor (CPUID 068xh) with AGTL signalling capability for use with the ServerWorks\* HE-SL chipset. In addition to providing motherboard design recommendations such as layout and routing guidelines, this document will also address possible system design issues such as processor power delivery, layout considerations for mechanical pieces, EMI design impacts and system bus decoupling.

Please note that this document describes the design recommendations that are driven by the Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache's specifications. Because of this, the recommendations explicity mentioned the Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache in most places. The Intel<sup>®</sup> Pentium<sup>®</sup> III Processor (CPUID 068xh) with AGTL signalling capability is compatible with systems designed to the recommendations in this document and will operate in its AGTL compatible mode when placed in the system.

Carefully follow the design information, board schematics, debug recommendations and system checklist presented in this document. These design guidelines have been developed to ensure maximum flexibility for board designers while reducing the risk of board related issues. The design information provided in this document falls into one of the two categories below.

- **Design Recommendations** are items based on Intel's simulations and lab experience to date and are strongly recommended, if not necessary, to meet the timing and signal quality specifications.

- **Design Considerations** are suggestions for platform design that provide one way to meet the design recommendations. They are based on the reference platforms designed by Intel. They should be used as an example, but may not be applicable to your particular design.

### 1.1 Audience

This document is targeted at the following audience:

- Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache system developers;

- System developers modifying an existing PGA370 socket dual-processing platform to be Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache ready.

### 1.2 Related Documents

The reader of this specification should also be familiar with the material and concepts presented in the following documents <sup>1,2</sup>:

| Document                                                    | Intel Order Number |

|-------------------------------------------------------------|--------------------|

| P6 Family of Processors Hardware Developer's Manual         | 244001             |

| IA-32 Processors and Related Products 1999 Databook         | 243565             |

| 370-Pin Socket (PGA370) Design Guidelines                   | 244410             |

| Intel® Pentium® III Processor with 512KB L2 Cache Datasheet | 249657             |

| Document                                                                       | Intel Order Number |

|--------------------------------------------------------------------------------|--------------------|

| Intel® Pentium® III Processor in the FC-PGA2 Package Thermal Design Guidelines | 249660             |

| VRM 8.5 DC-DC Converter Design Guidelines                                      | 249659             |

| Intel® Pentium® III Processor with 512KB L2 Cache Bus Terminator Design Guide  | 249661             |

| Intel® Pentium® III Processor (CPUID 06Bxh) BSDL Files                         |                    |

| Intel® Pentium® III Processor with 512KB L2 Cache DP I/O Buffer Models         |                    |

#### NOTE:

- 1. Unless otherwise noted, this reference material can be found on the Intel Developer's Website located at http:// developer.intel.com.

- 2. For a complete listing of Intel® Pentium® III processor reference material, please refer to the Intel Developer's Website at http://developer.intel.com/design/PentiumIII/

### 1.3 Conventions and Terminology

For this document, the following terminology applies.

- Intel<sup>®</sup> Pentium<sup>®</sup> III Processor (CPUID 068xh) with AGTL Capability Intel<sup>®</sup> Pentium<sup>®</sup> III Processor based on Intel's 0.18-micron technology with AGTL (1.25 V<sub>TT</sub>) interface support. This processor contains 256KB of L2 cache and is dual-processor capable.

- Intel® Pentium® III Processor with 512KB L2 Cache Intel<sup>®</sup> Pentium<sup>®</sup> III Processor based on Intel's 0.13-micron (i.e. 1.25V V<sub>TT</sub> / AGTL) technology. This processor contains 512KB of L2 cache and is dual-processor capable.

- PGA370 socket 370-pin Zero Insertion Force (ZIF) socket which a FC-PGA or FC-PGA2 packaged processor plugs into.

- **FC-PGA** Flip Chip Pin Grid Array. The package technology used on Intel<sup>®</sup> Pentium<sup>®</sup> III Processor (CPUID 068xh) for the PGA370 socket. The FC-PGA package has the processor die exposed.

- FC-PGA2 Flip Chip Pin Grid Array 2. The package technology used on the Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache and some Intel<sup>®</sup> Pentium<sup>®</sup> III Processors (CPUID 068xh) for the PGA370 socket. The FC-PGA2 package contains an Integrated Heat Spreader which covers the processor die.

- Keep-out zone The area on or near a FC-PGA packaged processor that system designs can not utilize.

- **Processor** For this document, the term processor is the generic form of the Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache for the PGA370 socket in the FC-PGA2 package.

- Integrated Heat Spreader (IHS) The Integrated Heat Spreader (IHS) is a metal cover on the die and it is an integral part of the CPU. The IHS promotes heat spreading away from the die backside to ease thermal constraints.

- AGTL compatible processor Generic term for Intel<sup>®</sup> Pentium<sup>®</sup> III Processors which are compatible with AGTL signalling voltage levels (1.25V). These processors are the Intel<sup>®</sup> Pentium<sup>®</sup> III Processor (CPUID 068xh) with AGTL Capability and the Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache.

- **AGTL+ only processor** Generic term for Intel<sup>®</sup> Pentium<sup>®</sup> III Processors which can only use AGTL+ signalling voltage levels (1.5V). These processors are Intel<sup>®</sup> Pentium<sup>®</sup> III Processors (CPUID 068xh) which do not have AGTL compatibility.

### 1.4 State of the Data

The data contained within this document are based on near-production validation testing and silicon characterization.

This page intentionally left blank

### **General Design Considerations**

This section documents motherboard layout and routing guidelines for Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache platforms. This section does not discuss the functional aspects of any bus, or the layout guidelines for an add-in device.

If the guidelines listed in this document are not followed, it is very important that thorough signal integrity and timing simulations are completed for each design. Even when the guidelines are followed, critical signals are recommended to be simulated to ensure proper signal integrity and flight time. Any deviation from the guidelines should be simulated.

The trace impedance typically noted (i.e.,  $60\Omega +/-15\%$ ) is the "nominal" trace impedance for a 5-mil wide trace. That is, the impedance of the trace when not subjected to the fields created by changing current in neighboring traces. When calculating flight times, it is important to consider the minimum and maximum impedance of a trace based on the switching of neighboring traces. Using wider spaces between the traces can minimize this trace-to-trace coupling. In addition, these wider spaces reduce settling time.

Coupling between two traces is a function of the coupled length, the distance separating the traces, the signal edge rate, and the degree of mutual capacitance and inductance. In order to minimize the effects of trace-to-trace coupling, the routing guidelines documented in this section should be followed.

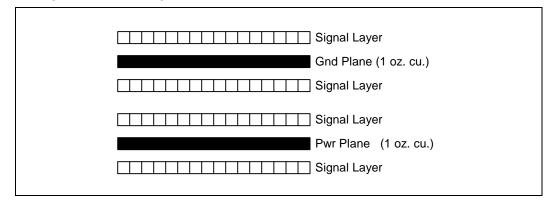

### 2.1 Nominal Board Stackup

An example of a 6-layer stack-up is shown in Figure 2-1. The impedance of all the signal layers should be  $60\Omega$  +/- 15%. A lower trace impedance reduces signal edge rates, overshoot, and undershoot, and has less crosstalk than a higher trace impedance. A higher trace impedance increases edge rates and may slightly decrease signal flight times. Please note that thicker core may help reduce board warpage issues.

Additional guidelines on board stack-up, placement, and layout include the following.

- The board impedance (Z) should be between 55  $\Omega$  and 75  $\Omega$  (65  $\Omega$  ± 15% is recommended).

- The dielectric process variation in the PCB fabrication should be minimized.

- The ground plane should not be split on the ground plane layer.

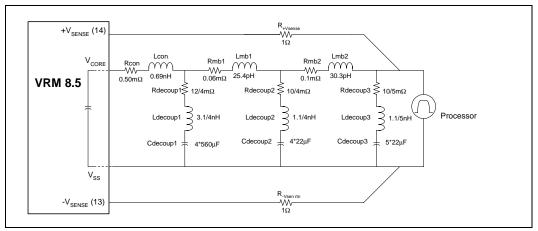

- Keep vias for decoupling capacitors as close to the capacitor pads as possible.

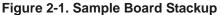

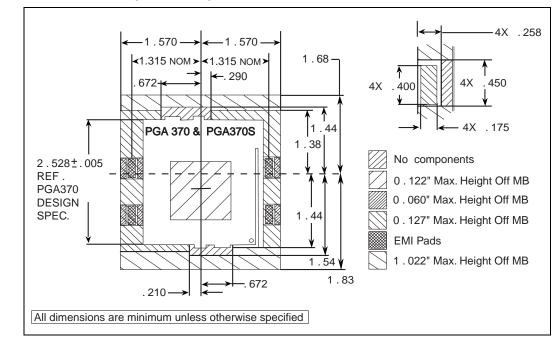

### 2.2 Socket 370 Component Keepout

Figure 2-2. Socket 370 Component Keepout

Figure 2-3. Socket 370 Volumetric Keepout

This page intentionally left blank

### **Processor Host Bus Design**

### 3.1 Initial Timing Analysis

To determine the available flight time window, perform an initial timing analysis. Analysis of setup and hold conditions will determine the minimum and maximum flight time bounds for the system bus. Use the following equations to establish the system flight time limits.

#### Table 3-1. System Timing Equations

|                                                                                                                                  | Equation         |

|----------------------------------------------------------------------------------------------------------------------------------|------------------|

| $T_{flight,min} >= T_{hold} - T_{co,min} + T_{skew}$                                                                             |                  |

| T <sub>flight,max</sub> <= T <sub>cycle</sub> - T <sub>co,max</sub> - T <sub>su</sub> - T <sub>skew</sub> - T <sub>jit</sub> - T | Г <sub>аdj</sub> |

#### Table 3-2. System Timing Terms

| Term                                                                                                  | Description                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>cycle</sub>                                                                                    | System cycle time, defined as the reciprocal of the frequency.                                                                                                                                                                                                                                                    |

| T <sub>flight,min</sub>                                                                               | Minimum system flight time.                                                                                                                                                                                                                                                                                       |

| T <sub>flight,max</sub>                                                                               | Maximum system flight time.                                                                                                                                                                                                                                                                                       |

| T <sub>co,max</sub>                                                                                   | Maximum driver delay from input clock to output data.                                                                                                                                                                                                                                                             |

| T <sub>co,min</sub>                                                                                   | Minimum driver delay from input clock to output data.                                                                                                                                                                                                                                                             |

| T <sub>su</sub>                                                                                       | Minimum setup time. Defined as the time for which the input data must be valid prior to the input clock.                                                                                                                                                                                                          |

| T <sub>hold</sub>                                                                                     | Minimum hold time. Defined as the time for which the input data must remain valid after the input clock.                                                                                                                                                                                                          |

| T <sub>skew</sub>                                                                                     | Clock generator skew. Defined as the maximum delay variation between output clock signals from the system clock generator, the maximum delay variation between clock signals due to system board variation and chipset loading variation, and skew due to delay in the PGA370 socket.                             |

| T <sub>jit</sub> Clock jitter. Defined as the maximum edge to edge variation in a given clock signal. |                                                                                                                                                                                                                                                                                                                   |

| T <sub>adj</sub>                                                                                      | Multi-bit timing adjustment factor. This term accounts for the additional delay that occurs in the network when multiple data bits switch in the same cycle. The adjustment factor includes such mechanisms as package and PCB crosstalk, high inductance current return paths, and simultaneous switching noise. |

Component timings for the Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache are available in the *Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache Datasheet*. Please contact your chipset vendor for documentation concerning the chipset component timing.

Recommended values for system timings are contained in Table 3-3. Skew and jitter values for the clock generator device come from the clock driver datasheet. The PCB skew specification is based on the results of extensive simulations at Intel. The  $T_{adj}$  value is based on Intel's experience with systems that use previous generations of processors.

#### Table 3-3. System Bus Timing Parameters

| Timing Term             | Value |

|-------------------------|-------|

| T <sub>skew</sub> [ns]  | 0.250 |

| T <sub>jit</sub> [ns]   | 0.2   |

| T <sub>adj</sub> [ns]   | 0.5   |

| T <sub>cycle</sub> [ns] | 7.5   |

The flight time requirements for CPU to CPU transfers that result from using the component timing specifications and recommended system timings are summarized in Table 3-4. All component values should be verified against the latest specifications before proceeding with analysis.

#### Table 3-4. Sample CPU to CPU flight time calculations

| Driver | Receiver | Calculation                                                               |  |

|--------|----------|---------------------------------------------------------------------------|--|

| CPU    | CPU      | T <sub>flight,min</sub> >= 1.0 - 0.4 + 0.25 = 0.85 ns                     |  |

| CPU    | CPU      | T <sub>flight,max</sub> <= 7.5 - 3.25 - 0.95 - 0.25 - 0.2 - 0.5 = 2.35 ns |  |

### 3.2 General Topology and Layout Guidelines

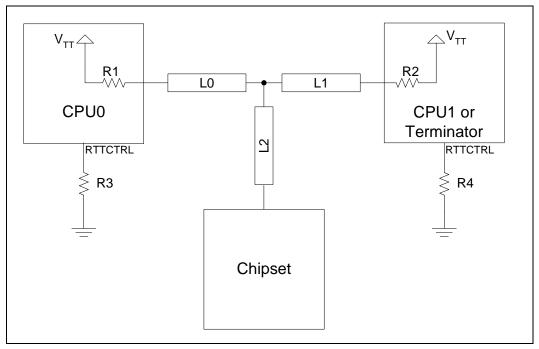

Intel is recommending that all Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache dual-processing platforms use a system bus T-topology. Figure 3-1 shows a high level diagram of this topology. The pull-up resistors shown inside the processor packages are the processor's on-die AGTL termination. Since the processor has on-die termination, a dual processor capable system must either have two processors installed, or one processor and one terminator.

Figure 3-1. System Bus T-Topology

Table 3-5 contains the length specifications for the segments of the T-topology. Please note that lengths L0 and L1 must be length matched to within 0.25 inches. Table 3-6 contains the component values which should be used for this topology.

| Table 3-5. Trace Lengths | for T Topology   | (ServerWorks | Chipset) |

|--------------------------|------------------|--------------|----------|

| Table e el made Longine  | , ioi i iopology |              | ompoor   |

| Segment | Min Length (inches) | Max Length (inches) |

|---------|---------------------|---------------------|

| LO      | 3.25                | 3.75                |

| L1      | 3.25                | 3.75                |

| L2      | 1.75                | 2.5                 |

#### Table 3-6. Component Values for T Topology

| Reference    | Value | Tolerance |

|--------------|-------|-----------|

| R1 (on chip) | 68Ω   | 10%       |

| R2 (on chip) | 68Ω   | 10%       |

| R3           | 68Ω   | 1%        |

| R4           | 68Ω   | 1%        |

### 3.3 Terminator-less T Topology

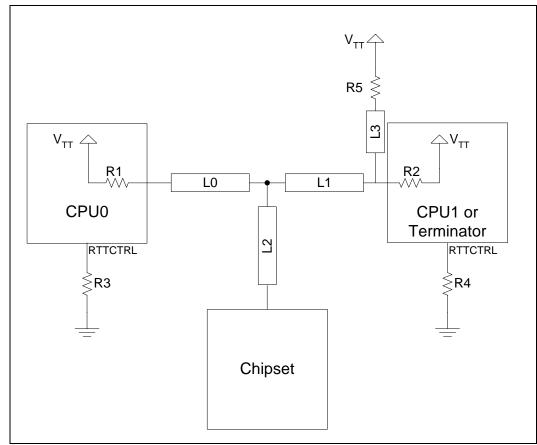

For dual processor platform designs without a terminator, the following new T topology is recommended. A new segment (L3) with a pull-up resistor to Vtt has been added to provide termination when the CPU1 socket is not populated. The L3 segment should be connected as close to the CPU1 pin as possible, preferably after the L1 segment connects to the CPU1 pin. The R4 value for CPU1 uses a  $100\Omega$  resistor pulled down to Vss instead of the  $68\Omega$  that is normally recommended. CPU0's R3 value should remain  $68\Omega$ .

**Please Note: Intel will not be validating the terminator-less T topology design**. This design is based on extensive simulation results that have been performed by Intel. It is provided as a reference for designs seeking to not require a terminator when the system is operating with one processor. Intel recommends that any implementation of this topology be simulated and validated carefully.

Figure 3-2. Terminator-less System Bus T Topology

| Segment | Min Length (inches) | Max Length (inches) |

|---------|---------------------|---------------------|

| LO      | 3.25                | 3.75                |

| L1      | 3.25                | 3.75                |

| L2      | 1.75                | 2.5                 |

| L3      | 0.0                 | 1.0                 |

#### Table 3-7. Trace Lengths for Terminator-less T Topology (ServerWorks Chipset)

| Table 3-8. Component Values for Terminator-less T Topolog | Table 3-8. | Component | Values for | <b>Terminator-less</b> | T Topology |

|-----------------------------------------------------------|------------|-----------|------------|------------------------|------------|

|-----------------------------------------------------------|------------|-----------|------------|------------------------|------------|

| Reference    | Value | Tolerance |

|--------------|-------|-----------|

| R1 (on chip) | 68Ω   | 10%       |

| R2 (on chip) | 100Ω  | 15%       |

| R3           | 68Ω   | 1%        |

| R4           | 100Ω  | 1%        |

| R5           | 100Ω  | 10%       |

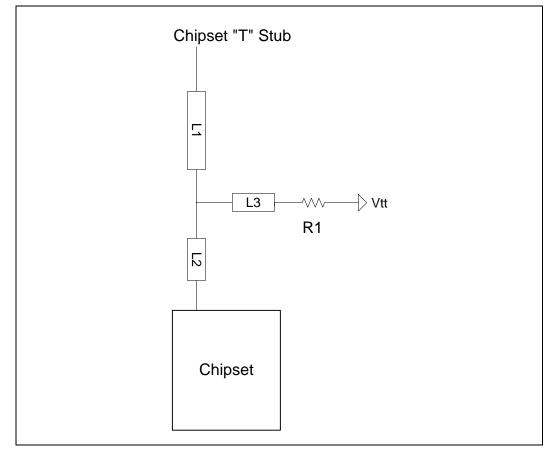

### 3.4 Wired-OR Signal Considerations

The Wired-OR signals of the processor's host bus require additional consideration. The Wired-OR signals in an Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache system are HIT#, HITM#, BNR#, AERR#, BERR#, and BINIT#. The Wired-OR signals may be driven by multiple bus agents at the same time, such as both processors asserting the HIT# signal to signify a cache hit on a line they both contain. With multiple driving agents, these signals are susceptible to being overdriven which results in excessive overshoot and ringback on these signals.

Terminating the Wired-OR signals at the chipset branch of the T topology will reduce the effect of multiple driving agents on these signals. Intel recommends that system designers carefully examine the signal integrity of these signals and optionally implement the circuit shown in Figure 3-3. This recommendation will work correctly for systems designed with the standard T topology or the terminator-less T topology.

Please note that the incorporation of Wired-OR termination is optional. Intel has not seen any failures on systems which do not implement the Wired-OR termination recommendations. Therefore, systems which are already in the latter phases of design may wish to forego implementing these recommendations until an opportunity presents itself to incorporate them. However, it is the responsibility of the system designer to ensure that the signal quality of these signals meet the component specifications.

#### Table 3-9. Wired-OR Values

| Item | Value                 | Notes                                                                                                                   |

|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| L1   | 1.75 to 2.5 inches    | Same as L2 lengths in Section 3.2 and Section 3.3                                                                       |

| L2   | Less than 0.25 inches | Should be as short as possible. Optimal case is to make this value zero, making the L3 stub come after the chipset pin. |

| L3   | Less than 1.5 inches  |                                                                                                                         |

| R1   | 100 to 220 Ω          | The range of values has trade-offs in flight time and dampening effects. 150 $\Omega$ +/- 10% is a base recommendation. |

Please note that the value range for R1 present a set of trade-offs for flight time and dampening effects. Choosing a value near the upper end of the range (around  $200\Omega$ ) will impact the flight times the least, but will also provide minimal dampening. Choosing a value at the lower end of the range (around  $100\Omega$ ) will provide optimal dampening but has a larger impact on the signal flight times. Intel recommends a value of  $150\Omega + 10\%$  as a reasonable trade-off between dampening and flight time.

### 3.5 Simulation Methodology

Analog simulations are recommended for high-speed system bus designs. Start simulations prior to layout. Pre-layout simulations provide a detailed picture of the working "solution space" that meets flight time and signal quality requirements. By basing board layout guidelines on the solution space, the iterations between layout and post-layout simulations can be reduced.

Intel recommends running simulations at the device pads for signal quality and at the device pins for timing analysis. However, simulation results at the device pins may be used later to correlate simulation performance against actual system measurements.

Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache DP I/O buffer models are available from the Intel Developer website.

### 3.6 Trace Routing

The following guidelines should be followed when routing the AGTL host bus signal traces:

- Traces should have an impedance of  $60\Omega$  +/- 15%

- The nominal trace width should be 5 mils.

- The L0 and L1 lengths in Table 3-5 should be matched to within 0.25 inches.

- Minimize the number of vias and layer transitions.

### 3.7 Layout Rules for AGTL Signals

#### 3.7.1 Ground Reference

It is strongly recommended that AGTL signals be routed on the signal layer next to the ground layer (referenced to ground). It is important to provide effective signal return path with low inductance. The best signal routing is directly adjacent to a solid GND plane with no splits or cuts. Eliminate parallel traces between layers not separated by a power or ground plane.

### 3.7.2 Reference Plane Splits

Splits in reference planes disrupt signal return paths and increase overshoot/undershoot due to significantly increased inductance. For optimal signal integrity, high-speed signals should not be routed over power plane splits.

### 3.7.3 CPU Connector Breakout

It is strongly recommended that AGTL signals do not traverse multiple signal layers. Intel recommends breaking out all signals from the connector on the same layer. If routing is tight, breakout from the connector on the opposite routing layer over a ground reference and cross over to main signal layer near the CPU connector.

Note: Following the above layout rules is critical for AGTL signal integrity.

#### 3.7.4 Minimizing Crosstalk

The following general rules will minimize the impact of crosstalk in the high speed AGTL bus design:

- Maximize the space between traces. Maintain a minimum of 10 mils (assuming a 5 mil trace) between trace edges wherever possible. It may be necessary to use tighter spacing when routing between component pins. When traces have to be close and parallel to each other, minimize the distance that they are close together, and maximize the distance between the sections when the spacing restrictions relaxes.

- Avoid parallelism between signals on adjacent layers if there is no AC reference plane between them. As a rule of thumb, route adjacent layers orthogonally.

- Since AGTL is a low signal swing technology, it is important to isolate AGTL signals from other signals by at least 25 mils. This will avoid coupling from signals that have larger voltage swings, such as 3.3 V system memory.

- Select a board stack-up that minimizes the coupling between adjacent signals. Minimize the nominal characteristic impedance within the AGTL specification. This can be done by minimizing the height of the trace from its reference plane, which minimizes the crosstalk.

- Route AGTL address, data and control signals in separate groups to minimize crosstalk between groups. Keep at least 25 mils between each group of signals.

- Minimize the dielectric used in the system. This makes the traces closer to their reference plane and thus reduces the crosstalk magnitude.

- Minimize the dielectric process variation used in the PCB fabrication.

- Minimize the cross sectional area of the traces. This can be done by narrower traces and/or by using thinner copper, but the trade-off for this smaller cross sectional area is a higher trace resistivity that can reduce the falling edge noise margin because of the I\*R loss along the trace.

### 3.8 Layout Rules for Non-AGTL (CMOS) Signals

The following layout rules should be used for all CMOS signals:

- The trace impedance should be  $60\Omega$  +/- 15%.

- External termination resistors should be placed in the middle of the trace to prevent long reflection times and reduce reflection ledges.

- Do not route CMOS traces next to AGTL traces. Switching noise on the AGTL traces may attack the nearby CMOS traces.

- Route a CMOS trace on one signal layer. If layer switching is unavoidable, try minimize the number of layer switches.

- Try to use only one reference plane for a trace (either Vcc or Vss).

- Although CMOS signals are slow, they may still have speed path problems. This is especially true for APIC clock and APIC data. Try to avoid long routes.

### 3.9 Undershoot/Overshoot Requirements

Overshoot (or undershoot) is the absolute value of the maximum voltage above the nominal high voltage or below VSS. The overshoot guideline limits transitions beyond VCC or VSS due to the fast signal edge rates. The processor can be damaged by repeated overshoot events on buffers if the charge is large enough (i.e., if the overshoot is great enough). Determining the impact of an overshoot/undershoot condition requires knowledge of the magnitude, the pulse direction and the activity factor (AF). Permanent damage to the processor is the likely result of excessive overshoot/undershoot. Violating the overshoot/undershoot guideline will also make satisfying the ringback specification difficult.

When performing simulations to determine impact of overshoot and undershoot, ESD diodes must be properly characterized. ESD protection diodes do not act as voltage clamps and will not provide overshoot or undershoot protection. ESD diodes modeled within Intel I/O buffer models do not clamp undershoot or overshoot and will yield correct simulation results. If other I/O buffer models are being used to characterize the processor performance, care must be taken to ensure that ESD models do not clamp extreme voltage levels. Intel I/O buffer models also contain I/O capacitance characterization. Therefore, removing the ESD diodes from an I/O buffer model will impact results and may yield excessive overshoot/undershoot.

Refer to the latest *Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache Datasheet* for detailed undershoot/overshoot requirements.

### 3.10 Debug Port Routing Guidelines

This section describes the processor debug port, in-target probe (ITP) platform design guidelines. The data in this chapter must be used with the information found in the "Debug Tool Specifications" chapter of the *Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache Datasheet* to complete the design and layout of the debug port.

### 3.10.1 Target System Implementation

The implementation guidelines given in this section will ensure a fully functional ITP debug system. The signals involved in the ITP debug system are high speed signals and must be routed with high speed design considerations in mind. The implementation offers flexibility in areas such as JTAG routing (i.e., scan chain), addition of non-ITP compliant parts, and clock rate. However, the implementation is not flexible in system and execution signal connections.

Intel will use an ITP for internal debug and system validation and recommends that all system designs include a debug port.

#### 3.10.1.1 Signal Layout Guidelines

The Debug Port (TAP) is a part of the processor scan chain. It will need to be connected to the bus clock and system bus signals. This implies that the designer will place the Debug Port within 12 inches of the nearest processor.

There are three signal groups within the debug port as mentioned in the *Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache Datasheet.* Each group has a different set of layout requirements. The system signals are special ITP-specific signals and are both inputs and outputs. The JTAG signals are system

resources and may be shared with local JTAG tools. Input and output signals are available. The execution signals are a combination of CMOS and AGTL level signals. They are both inputs and outputs to the ITP.

The ITP TCK and TMS signals must be routed with a maximum trace resistance of 2.0 ohm to reduce the amount of DC shifting on these signals. This is due to the small termination values that are recommended for these signals.

#### 3.10.1.1.1 System Signal Layout Guidelines

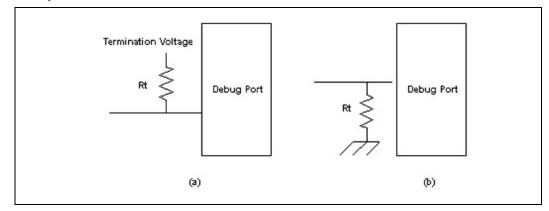

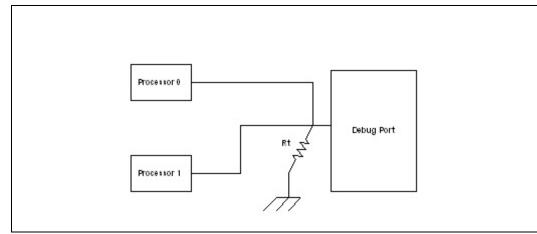

Table 3-10 provides the system signal layout guidelines. See Table 3-13 for termination values.

Table 3-10. System Signal Layout Guidelines

| Signal                      | Routing Notes                                                                                                | Sample Layout |

|-----------------------------|--------------------------------------------------------------------------------------------------------------|---------------|

| POWERON                     | Route with normal trace 2 to 6 inches to the debug port connector                                            | Figure 3-4a   |

| BCLK, BCLK#                 | Refer to BCLK system requirements documentation<br>for proper termination values and routing<br>requirements | N/A           |

| DBRESET#, BSEN#,<br>DBINST# |                                                                                                              | Figure 3-4a   |

Figure 3-4. Simple Terminations

#### 3.10.1.1.2 JTAG Signal Layout Guidelines

Reflections on TCK that cause mid-threshold ringing will render the primary system debug tool inoperative. Simulate the behavioral model, and verify signal integrity using your system bus signal analysis tools. The following table provides the JTAG signal layout guidelines. It is highly recommended that TCK be simulated to ensure proper signal quality is maintained.

#### Table 3-11. JTAG Signal Layout Guidelines

| Signal        | Routing Notes                                                                                                                                | Sample Layout |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| тск           | Critical JTAG signals which requires timing and signal integrity considerations, driver is 74VCX16245 with external edge rate control on TCK | Figure 3-5    |

| TMS, TDI, TDO | Critical JTAG signal which requires timing and signal integrity considerations. ITP driver is 74VCX16245. TMS must be routed with TCK.       | Figure 3-4a   |

| TRST#         | On target resistors should be used to force TRST# assertion (low).                                                                           | Figure 3-4b   |

Figure 3-5. TCK Termination, DP System

#### 3.10.1.1.3 Execution Signal Layout Guidelines

#### Table 3-12. Execution Signals Routing Guidelines

| Signal | Routing Notes                                                                                                                | Sample Layout |

|--------|------------------------------------------------------------------------------------------------------------------------------|---------------|

| PREQx# | AGTL signal routing guidelines apply                                                                                         | Figure 3-4a   |

| PRDYx# |                                                                                                                              | Figure 3-6    |

| RESET# | The flight time of the RESET# signal from the closest processor must be added to the arrival time of BCLK at the Debug Port. | Figure 3-7    |

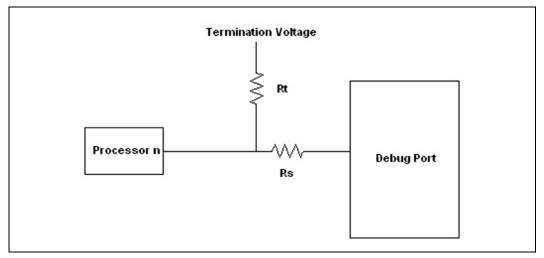

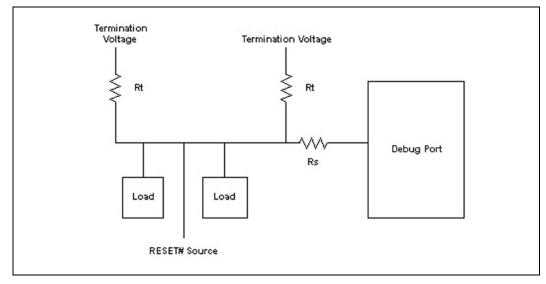

Figure 3-6. PRDYx# Signal Termination

Figure 3-7. RESET# Signal Termination

#### 3.10.1.2 Signal Termination Requirements

Table 3-13 lists signal termination requirements for the debug port signals.

| Table 3-13. Debug Port Termination Requirement | Table 3-13. | Debua | Port | Termination | Requirement |

|------------------------------------------------|-------------|-------|------|-------------|-------------|

|------------------------------------------------|-------------|-------|------|-------------|-------------|

| Signal            | Signal Termination Value (Rt)                                                                                      | Termination<br>Value (Rs) | Termination<br>Voltage |

|-------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------|

| System Signal     |                                                                                                                    |                           |                        |

| POWERON           | 1.5 ΚΩ                                                                                                             | N/A                       | V <sub>TT</sub>        |

| BCLK, BCLK#       | BCLK, BCLK# Refer to BCLK system requirements documentation for proper termination values and routing requirements |                           |                        |

| BSEN#             | 240 Ω                                                                                                              | N/A                       | V <sub>CC</sub>        |

| DBRESET#          | 240 Ω                                                                                                              | N/A                       | V <sub>CC</sub>        |

| DBINST#           | 10 ΚΩ                                                                                                              | N/A                       | V <sub>CC</sub>        |

| JTAG Signals      |                                                                                                                    |                           |                        |

| тск               | 39 Ω                                                                                                               |                           | GND                    |

| TDI               | 200 - 300 Ω                                                                                                        | N/A                       | VCC <sub>CMOS1.5</sub> |

| TDO               | 150 Ω                                                                                                              | N/A                       | VCC <sub>CMOS1.5</sub> |

| TMS               | 39 Ω                                                                                                               | N/A                       | VCC <sub>CMOS1.5</sub> |

| TRST#             | 500 - 680 Ω                                                                                                        | N/A                       | GND                    |

| Execution signals |                                                                                                                    |                           |                        |

| RESET#            | Match to AGTL characteristic<br>impedance                                                                          | 240 Ω                     | V <sub>TT</sub>        |

| PREQx#            | 200 - 300 Ω                                                                                                        | N/A                       | Vcc <sub>CMOS1.5</sub> |

| PRDYx#            | Match to AGTL characteristic impedance                                                                             | 240 Ω                     | V <sub>TT</sub>        |

#### 3.10.1.3 Routing Guidelines

#### Table 3-14. Routing Guidelines

| Parameter                                                               | Reference<br>Figure | Description                                                                                                            |

|-------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------|

| тск                                                                     | Figure 3-5          | 1" max from debug port to RT AND 12" max from debug port to processor VERY SENSITIVE TO NOISE please route accordingly |

| TMS, TDO, TDI,<br>POWERON,<br>DBRESET#,<br>BSEN#,<br>DBINST#,<br>PREQx# | Figure 3-4 <b>a</b> | 1" max from debug port to RT AND 12" max from debug port to processor                                                  |

Table 3-14. Routing Guidelines

| Parameter | Reference<br>Figure | Description                                                                                                                 |

|-----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------|

| TRST#     | Figure 3-4b         | 1" max from debug port to RT AND 12" max from debug port to processor                                                       |

| PRDYx#    | Figure 3-6          | 1" max from debug port to RS AND 1" max from debug port to RT<br>AND 12" max from debug port to processor (AGTL guidelines) |

| RESET#    | Figure 3-7          | 1" max from debug port to RS AND 1" max from debug port to RT AND 12" max from debug port to processor                      |

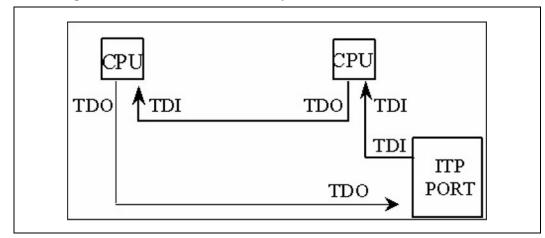

#### 3.10.1.4 System Implementation

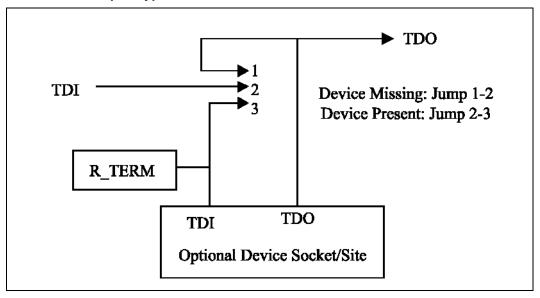

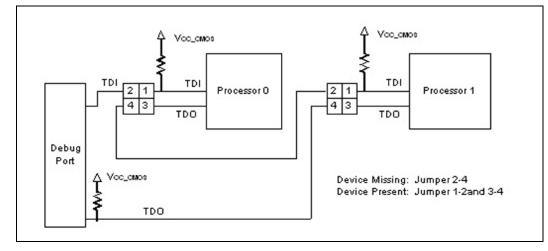

Figure 3-8 demonstrates the expected route of the JTAG data link for a processor only cluster. It is obligatory to pull up TDI/TDO for each signal, however. Note that when the number of processors is changed, a bypass must be used for the empty sites.

Figure 3-9 and Figure 3-10 illustrate possible bypass configurations with a three pin jumper and a fourpin jumper.

Figure 3-8. JTAG Signals TDI/TDO for Processor Only

Figure 3-9. TDO 3-Pin Jumper Bypass

Figure 3-10. 4-Pin Jumper Bypass

This page intentionally left blank

# int<sub>el</sub> *Clocking*

#### **General Clocking Considerations** 4.1

The host bus clock signals are critical signals in a platform design. The signal integrity and timing of these signals should be carefully evaluated and simulated. The following sections provide host clocking recommendations for the two supported Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache clocking methodologies: single-ended clocking and differential clocking.

In general, the following layout recommendations should be followed for the host bus clocks:

- It is recommended that system bus clocks be routed on the signal layer next to the ground layer (referenced to ground).

- It is strongly recommended that system bus clocks do not traverse multiple signal layers.

- ٠ System clock routing over power plane splits should be minimized.

- If necessary, grounded guard band traces can be routed next to clock traces to reduce crosstalk to other signals.

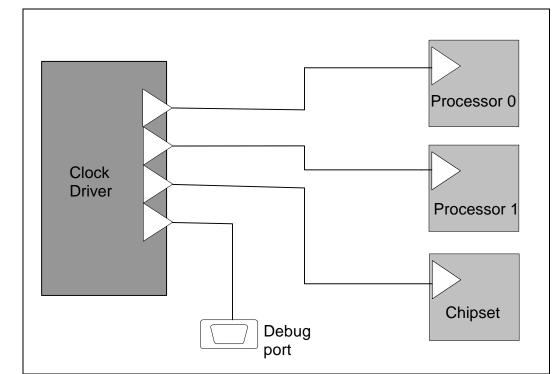

Figure 4-1 shows the host bus clocking connections that must be made in a dual-processor system. Detailed information regarding the routing, layout, and termination of the processor and chipset connections can be found in Section 4.2 and Section 4.3. The debug port routing has special requirements and are covered in Section 4.4.

Figure 4-1. Host Bus Clock Connections

The clocking requirements and timing information for the Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache can be found in the *Intel<sup>®</sup> Pentium<sup>®</sup>* III Processor with 512KB L2 Cache Datasheet. For additional information about the timing and clocking requirements of the chipset component, please contact your chipset vendor for the appropriate documentation.

### 4.2 Single Ended Host Bus Clocking Routing

Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache dual-processor platforms have support for using single-ended host bus clock drivers. When using this clocking method, the BCLK signal (pin W37) is used as the single-ended clock input to the processor. The BCLK#/CLKREF signal (pin Y33) is used as a reference voltage and must be connected to the appropriate filter circuit described in Section 4.2.1.

Figure 4-2 shows the topology that should be used for the processor clock traces. Please note that L0, L1, and L2 refer to trace lengths between the illustrated components. Table 4-1 contains the recommended lengths and component values for this topology.

Clock Driver Processor L1 Rs Zo = 60 ohm Rs Zo = 60 ohm U37 U

#### Figure 4-2. Single Ended Clocking Topology - CPU

Table 4-1. Component Values for SE Clocking Topology - CPU

| Reference | Value                                                    | Notes                                                                                                               |

|-----------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| LO        | 0.25 to 0.5 inches                                       | All L0s should be matched                                                                                           |

| L1        | Chipset L1 + 1" +/- 0.125<br>Chipset L1 + 0.5" +/- 0.125 | Use this processor L1 length if the chipset L1 is 5"-7"<br>Use this processor L1 length if the chipset L1 is 7"-12" |

| L2        | 0.0 to 1.0 inches                                        | L2 should be as short as possible.                                                                                  |

| Rs        | 22 to 33 Ω                                               | 1% Tolerance                                                                                                        |

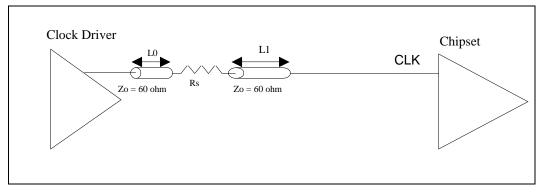

Figure 4-3 shows the topology that should be used for the chipset clock traces. Please note that L0 and L1 refer to trace lengths between the illustrated components. Table 4-2 contains the recommended lengths and component values for this topology.

Figure 4-3. Single Ended Clocking Topology - Chipset

| Reference | Value                 | Notes                      |

|-----------|-----------------------|----------------------------|

| LO        | 0.25 to 0.5 inches    | All L0s should be matched  |

| L1        | 5 inches to 12 inches | Effects processor lengths. |

| Rs        | 22 to 33 Ω            | 1% Tolerance               |

#### Table 4-2. Component Values for SE Clocking Topology - Chipset

The following guidelines should also be followed for single-ended clock implementations:

- BCLK must be routed through trace impedance of 60 ohm +/- 10%.

- Use 5 mil wide traces.

- Place all serial termination resistors within 0.50 inches to clock driver pins.

- Place all other signals at least 20 mils from the clock traces.

- All the termination resistors are rated at 1% accuracy.

- The two processor clock traces should be matched to within 0.250 inches.

#### 4.2.1 CLKREF Filter Implementation

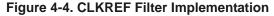

When using single-ended clocking mode, the BCLK#/CLKREF signal on the processor serves as a reference voltage to the clock input. To provide a steady reference voltage, a filter circuit must be implemented and attached to this pin. Figure 4-4 shows the recommended CLKREF filter implementation. The CLKREF filter should be placed as close as possible (less that 1.0 inch) to the processor's CLKREF pin.

| Reference | Value  | Notes        |

|-----------|--------|--------------|

| R1        | 150 Ω  | 1% Tolerance |

| R2        | 150 Ω  | 1% Tolerance |

| C1        | 4.7 μF |              |

### Table 4-3. CLKREF Component Values

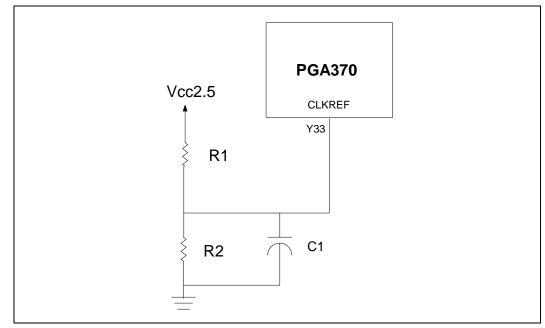

### 4.2.2 Single-Ended Clocking BSEL[1:0] Implementation

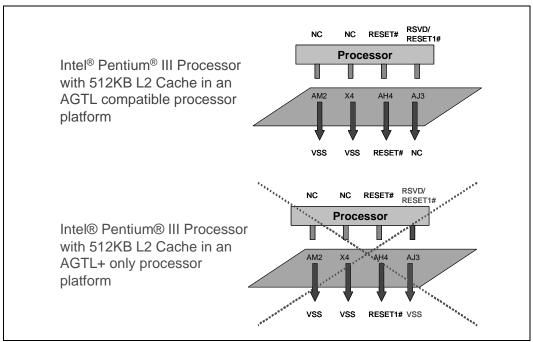

In an Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache platform that is using single-ended (SE) clocking or a clock source that does not support the VTT\_PWRGD protocol, the normal BSEL frequency selection process will not work. Since the clock generator is not compatible with dynamic BSEL assertions, all BSEL[1:0] signals should not be connected together. Instead, the BSEL pins on the clock generator should be pulled-up to 3.3 V through a 1 K $\Omega$ , 5% resistor. This strapping will force the clock generator into 133 MHz clocking mode and will only support 133 MHz capable processors.

# 4.3 Differential Host Bus Clocking Routing

Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache dual-processor platforms support differential host bus clock drivers. When operating in differential clocking mode, the BCLK and BCLK#/CLKREF form a differential pair of clock inputs. The differential pair of traces should be routed with special care and using standard differential signalling techniques. The following sections contain the recommended topology and routing for differential clocking for these platforms.

# intel

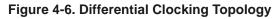

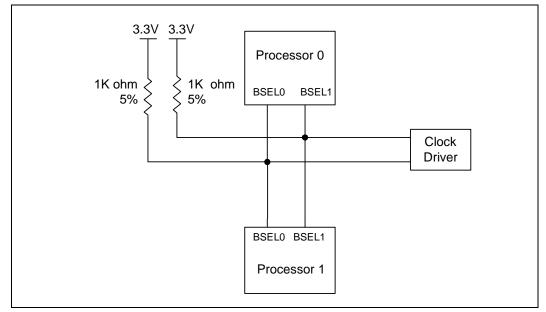

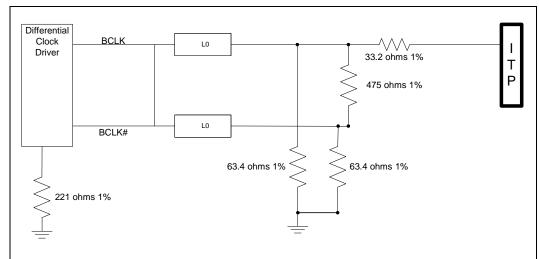

### 4.3.1 Differential Clocking Topology

Figure 4-6 shows the topology that should be used for the processor and chipset traces. Please note that L0 and L1 refer to trace lengths between the illustrated components. Table 4-4 contains the recommended lengths and component values for this topology.

### Table 4-4. Component Values for Differential Clocking

| Reference      | Value                                  | Notes                                                               |

|----------------|----------------------------------------|---------------------------------------------------------------------|

| L0 (Processor) | 5 to 9 inches                          | Match each processor<br>differential pair to within 0.250<br>inches |

| L0 (Chipset)   | Processor L0 + 1 inch +/- 0.125 inches | Match to the processor L0 and add 1 inch for package loading        |

| L1             | 0.0 to 0.4 inches                      | Should be as short as possible                                      |

| Rd             | 63.4Ω                                  | 1% Tolerance                                                        |

| Rs             | 33.2Ω                                  | 1% Tolerance                                                        |

| Rc             | 475Ω                                   | 1% Tolerance                                                        |

The following guidelines should also be followed for differential clock implementations:

- Match BCLK and BCLK# in length, width and impedance.

- BCLK and BCLK# should be coupled to achieve odd mode impedance of 50 ohm.

- Use 5 mil traces, routed differentially.

- Place all termination resistors within 0.40 inches of BCLK/BCLK# pins at the receiver.

- Other should be spaced at least 20 mils away from clock lines.

- All the termination resistors are rated as 1% accuracy.

- Minimize stubs to passive components.

- Clock to chipset is 1 inch longer than the clock to CPU (to compensate for CPU package load).

# intel®

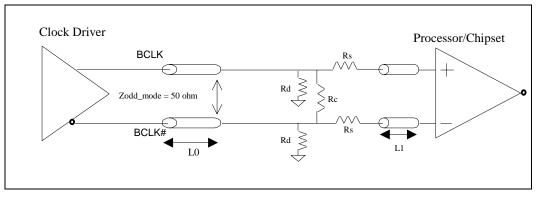

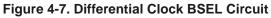

### 4.3.2 Differential Clocking BSEL[1:0] Implementation

The System Bus Frequency Select Signals (BSEL [1:0]) are used to select the system bus frequency for the host bus agents. The frequency selection is determined by the processor(s) and driven out to the host bus clock generator. All system bus agents must operate at the same 133MHz frequency. The BSEL pins for the processor are open drain signals and rely on a 3.3V pull-up resistor to set the signal to a logic high level. Figure 4-7 shows the recommended implementation for a differentially clocked system.

# 4.4 Debug Port Host Clock Connection

In order to recover full front side bus speed BPM[5:0]# and RESET# data with the ITP, the Debug Port should be placed as close as is physically reasonable to the system bus and no further than 1.5 ns flight time (as measured by trace length of the BPM[5:0]# and RESET# signals) from the nearest front side bus agent. System designers should record the flight time of the BPM[5:0]# and RESET# signals from the nearest front side bus agent to the Debug Port. This value will be important during the routing of several other Debug Port signals.

Assuming BCLK (and BCLK# in differential clocked systems) signals are routed from the system clock buffer to each of the synchronous clock agents with a matched length, the copy of this signals from the system clock buffer to the ITP Debug Port must have a flight time equal to the matched length of the other synchronous clock agents plus the flight time of the BPM[5:0]# signals from the nearest bus agent to the Debug Port noted above. This will ensure that the same BCLK to BPM[5:0]# phase relationship seen at the closest system bus agent will be present at the Debug Port pins. Clock trace lengths may be adjusted to center the recovery of BPM[5:0]# and RESET# at the Debug Port within the ITP receiver setup an hold window.

For a single-ended clock driver design, the topology illustrated in Figure 4-3 should be used. In this case, the "chipset" in the illustration is actually the debug port pin. The trace length L0 and the Rs value are the same as recommendations for the chipset in Table 4-2. However, the length of the trace segment L1 should be chosen so that it complies with the requirements described in the previous paragraph. This means that the L1 for the debug port is at least as long as the L1 for the processor clock traces.

The circuit recommendations for a differential clock driver design are shown in Figure 4-8. The length, L0, should be chosen to complies with the flight time requirements mentioned in this section. Please note that these requirements will make the length L0 longer than the processor clock trace's L0 lengths. The terminating resistors should be placed as close the ITP socket as possible.

Figure 4-8. Debug Port Differential Host Clock Implementation

### 4.5 Clock Driver Decoupling and Power Delivery

The decoupling and power delivery requirements of the system clock driver are dependent on the clock driver and chipset used in the system implementation. Because of this, no specific information can be provided in this document. However, since proper decoupling and noise-free power delivery are critical to the clock driver's operation, Intel encourages system implementors to carefully follow the chipset and clock driver vendor's recommendations in these areas. An incorrect implementation of these circuits can easily cripple a clock driver's ability to produce reliable clock signals and lead to system instability. Please refer to the appropriate clock driver and chipset vendor information for more details.

The intent of this section is to familiarize the reader with the processor power requirements for an Intel® Pentium<sup>®</sup> III Processor with 512KB L2 Cache dual processor platform, and to show simulation model and power implementation techniques. Only specific power distribution and control issues pertaining to Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache platforms are discussed in this section. It is assumed that the reader is familiar with power distribution issues of the Intel<sup>®</sup> Pentium<sup>®</sup> III processors.

#### Terminology 5.1

"Power-Good" or "PWRGOOD" (an active high signal) indicates that all of the supplies and clocks within the system are stable. PWRGOOD should go active a predetermined time after system voltages are stable and should go inactive as soon as any of these voltages fail their specifications.

"V<sub>CC</sub>" or "V<sub>CCCORE</sub>" refers to Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache core and cache supply voltages.

" $V_{\tau\tau}$ " refers to the AGTL termination voltage.

"AGTL" refers to Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache's Assisted Gunning Transceiver Logic supply voltage. "AGTL" is the bus between the processor and its chipset. The terms "AGTL" and "System Bus" are synonymous.

"VRM 8.5" refers to the DC-DC design guidelines for Intel<sup>®</sup> Pentium<sup>®</sup> III Processors with 512KB L2 Cache. These voltage regulator design supplies the required voltage and current to a single processor.

#### **Typical Power Delivery** 5.2

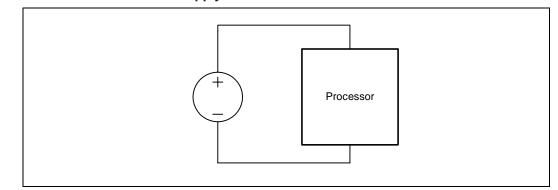

Power distribution is generally thought of as supplying power to the components that require it. Most digital designers typically assume that an ideal supply will be provided. The printed circuit board (PCB) designers attempt to create this ideal supply with two power planes in the PCB or by using large width traces to distribute power. High frequency noise created when logic gates switch is typically controlled with high frequency ceramic capacitors, which are recharged from lower frequency bulk capacitors. Various rule of thumb methods exist for determining the amount of each type of capacitance that is

required. For Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache dual processor designs, the system designer needs to design beyond the rule of thumb and architect a power distribution system that meets the processor specifications. Figure 5-1 shows the ideal power model.

Figure 5-1. Ideal Processor Power Supply Scheme

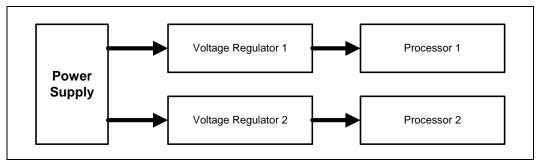

Figure 5-2 shows the recommended system baseboard solution involving local voltage regulators. Each voltage regulator solution can be either a voltage regulator module (VRM) or an embedded voltage regulator (VRD) depending upon the specific requirements of the board designs. It is recommended that board designers follow the guidelines in VRM 8.5 DC-DC converter design guidelines document.

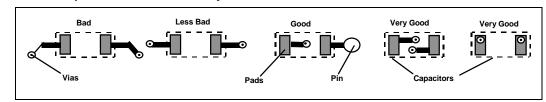

Each regulator circuit should be placed as close as possible to the corresponding processor and aligned to the side of the socket with the higher density of power and ground pins.

In previous generation Pentium® III dual processor based systems, there existed the possibility of sourcing the combined voltage and current requirements for both processors from one large voltage regulator. However, due to the load-line characteristics specified by the Intel<sup>®</sup> Pentium<sup>®</sup> III Processor with 512KB L2 Cache, Intel recommends that separate power planes be utilized. This configuration of voltage regulators is shown in Figure 5-2.

Figure 5-2. Power Distribution for a DP System Motherboard

# int<sub>el</sub>®

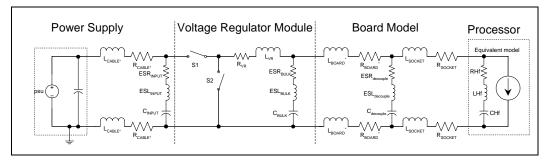

To completely model the motherboard system, one must include the inductance and resistance which exists in the cables, connectors, PCB planes, pins and body of components (such as resistors and capacitors), processor socket and voltage regulator. A more detailed model showing these effects is shown in Figure 5-3 below.

Figure 5-3. Detailed Power Distribution Model for System with VRM

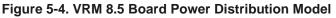

Both VRD and VRM solutions should be designed in conjunction with the recommended load model referenced in Figure 5-4.