## **ITP700 Debug Port**

**Design Guide**

February 2004

Document Number: 249679-014

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® processors may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel, Pentium, Intel Xeon, Itanium, Intel NetBurst, and Intel Centrino and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2001–2004, Intel Corporation

# int<sub>el</sub>,

## **Contents**

| 1 | Unipro     | cessor ITP Debug Port Implementation Guidelines                                                                                                                                | 11 |

|---|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1        | General Description                                                                                                                                                            |    |

|   | 1.0        | 1.1.1 ITP Features                                                                                                                                                             |    |

|   | 1.2<br>1.3 | Recommended Signal Terminations                                                                                                                                                |    |

|   | 1.5        | 1.3.1 System Signal Layout Guidelines                                                                                                                                          |    |

|   |            | 1.3.2 JTAG Signal Layout Guidelines                                                                                                                                            |    |

|   |            | 1.3.3 Execution Signal Layout Guidelines                                                                                                                                       | 16 |

|   | 1.4        | ITP700 Flex Alternative Debug Port                                                                                                                                             |    |

|   |            | <ul><li>1.4.1 Signal Descriptions</li><li>1.4.2 Termination and Routing Guidelines</li></ul>                                                                                   |    |

|   |            | 1.4.2         Termination and Routing Guidelines           1.4.3         ITP700 Flex Deltas to Standard ITP AC/DC Characteristics                                              |    |

| 2 | Multipr    | rocessor ITP Debug Port Implementation Guidelines                                                                                                                              | 23 |

|   | 2.1        | General Description                                                                                                                                                            | 23 |

|   |            | 2.1.1 ITP Features                                                                                                                                                             |    |

|   | 2.2        | Recommended Signal Terminations                                                                                                                                                |    |

|   | 2.3        | ITP Signal Layout Guidelines                                                                                                                                                   |    |

|   |            | <ul><li>2.3.1 System Signal Layout Guidelines</li><li>2.3.2 JTAG Signal Layout Guidelines</li></ul>                                                                            |    |

|   |            | 2.3.3 Execution Signal Layout Guidelines                                                                                                                                       |    |

| 3 | ITP700     | 0 DPA Specifications                                                                                                                                                           | 33 |

|   | 3.1        | ITP700 DPA Specifications                                                                                                                                                      | 33 |

|   | 3.2        | ITP700 DPA DC Electrical Characteristics                                                                                                                                       |    |

|   | 3.3        | ITP700 DPA AC Electrical Characteristics                                                                                                                                       |    |

|   | 3.4        | Pin Absolute Maximums                                                                                                                                                          |    |

|   | 3.5        | Mechanical Requirements                                                                                                                                                        | 41 |

| 4 | ITP700     | 0 LVDPA Specifications                                                                                                                                                         |    |

|   | 4.1        | ITP700 LVDPA Signal Descriptions                                                                                                                                               |    |

|   | 4.2        | ITP700 LVDPA DC Electrical Characteristics                                                                                                                                     |    |

|   | 4.3        | ITP700 LVDPA AC Electrical Characteristics                                                                                                                                     | 50 |

| 5 | ITP700     | 0 Flex Mechanical Requirements                                                                                                                                                 | 53 |

| 6 |            | Xeon <sup>™</sup> Processor with 512- KB L2 Cache at 2.20, 2.0, and 1.80 GHz DP / Inte<br><sup>™</sup> Processor MP Server System Implementation Guidelines                    |    |

|   | 6.1        | Termination and Routing Guidelines                                                                                                                                             | 57 |

| 7 |            | Pentium <sup>®</sup> 4 Processor / Mobile Intel <sup>®</sup> Pentium <sup>®</sup> 4 Processor-M / Intel <sup>®</sup> Centrinc<br>• Technology System Implementation Guidelines |    |

|   |            |                                                                                                                                                                                |    |

|   | 7.1        | Termination and Routing Guidelines                                                                                                                                             | 59 |

|    | <ul> <li>7.1.1 ITP Clock Routing for Intel<sup>®</sup> Pentium<sup>®</sup> 4 Processor</li> <li>7.1.1.1 Option A) Using the CK408 Clock Generator</li> <li>7.1.1.2 Option B) Using the ITPCLKOUT[1:0] Pins: (For B0 Silicon or Greater)</li> </ul> | 61 |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 8  | Intel <sup>®</sup> Itanium <sup>®</sup> 2 Processor System Implementation Guidelines                                                                                                                                                               | 65 |  |

|    | <ul> <li>8.1 ITP DC and AC Electrical Specifications for Intel<sup>®</sup> Itanium<sup>®</sup> 2 Processor<br/>Systems</li> <li>8.1.1 DC Electrical Specifications</li> </ul>                                                                      | 65 |  |

|    | <ul> <li>8.1.2 AC Electrical Specifications</li> <li>8.2 ITP Signal Layout Guidelines</li></ul>                                                                                                                                                    | 70 |  |

|    | 8.2.2 JTAG Signal Layout Guidelines<br>8.2.3 BPM Connectivity for I/O Domain Debug Ports                                                                                                                                                           | 71 |  |

|    | 8.3 Intel <sup>®</sup> Itanium <sup>®</sup> 2 Processor Routing Guidelines                                                                                                                                                                         |    |  |

| 9  | Intel <sup>®</sup> E8870 Chipset System Implementation Guidelines                                                                                                                                                                                  | 75 |  |

|    | 9.1 The I/O Domain Debug Port Guidelines                                                                                                                                                                                                           |    |  |

|    | 9.2 The Miscellaneous Debug Port Guidelines                                                                                                                                                                                                        | 76 |  |

| 10 | Appendix A – Alternate Bypass Methods                                                                                                                                                                                                              | 77 |  |

| 11 | Appendix B – Buffering TCK                                                                                                                                                                                                                         | 81 |  |

| 12 | Appendix C – Recovering a Single-Ended BCLK                                                                                                                                                                                                        | 83 |  |

| 13 | Appendix D – Arbitration of the Scan Chain With a Local TAP Master                                                                                                                                                                                 | 85 |  |

| 14 | Appendix E – Designer's Checklist for Schematic and Layout Reviews                                                                                                                                                                                 | 87 |  |

| 15 | Appendix F – ITP700 DPA Spice Models                                                                                                                                                                                                               |    |  |

# int<sub>el</sub>,

### Figures

| Figure 1. PWR Routing and Usage                                                                                                       | . 13 |

|---------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2. Recommended Layout Topology                                                                                                 | . 17 |

| Figure 3. ITP700 Flex Required Layout of Reset                                                                                        |      |

| Figure 4. ITP700 Flex Required Layout of BPM[5:0]#                                                                                    |      |

| Figure 5. PWR Routing and Usage                                                                                                       |      |

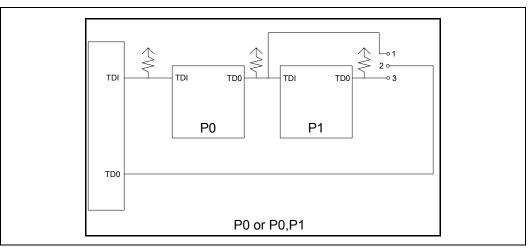

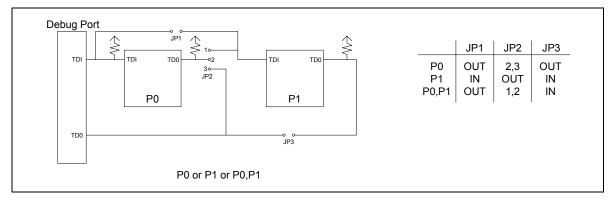

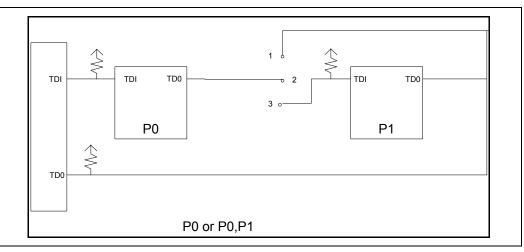

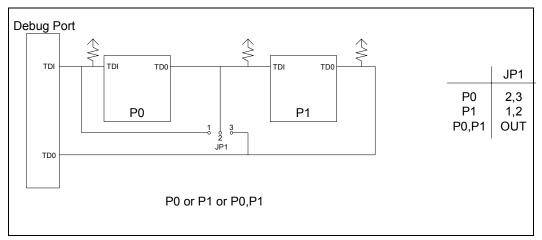

| Figure 6. TDI/TDO Scan Chain                                                                                                          |      |

| Figure 7. Recommended Bypass Jumper Configuration                                                                                     | . 29 |

| Figure 8. Recommended Layout Topology                                                                                                 | . 31 |

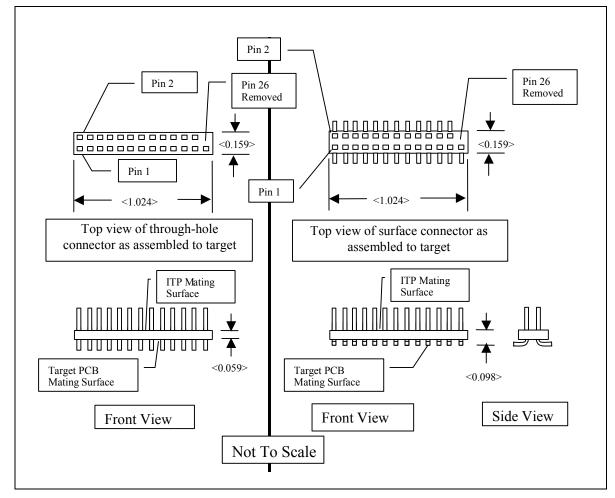

| Figure 9. ITP700 DPA Debug Port Pinout (Top View)                                                                                     | . 33 |

| Figure 10. Debug Port Connectors                                                                                                      |      |

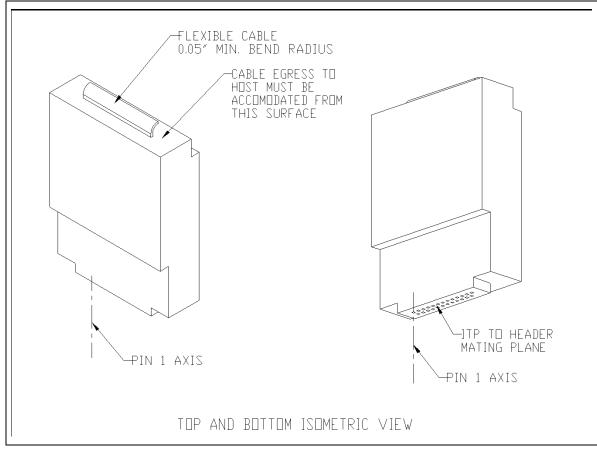

| Figure 11. Isometric View of Debug Port Adapter Keepout Volume                                                                        | . 42 |

| Figure 12. Front, Side, and Top View of ITP Debug Port Adapter Keepout Volume                                                         | . 43 |

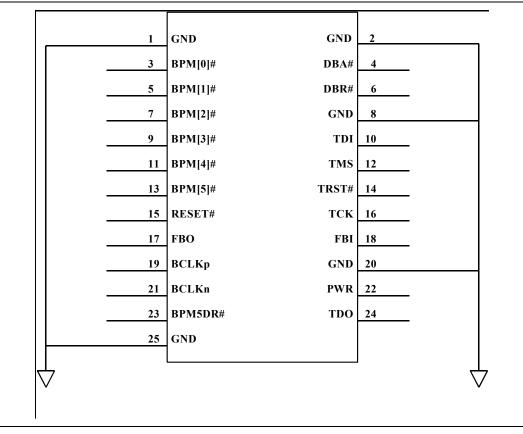

| Figure 13. ITP LVPDA Debug Port Pinout (Top View)                                                                                     | .45  |

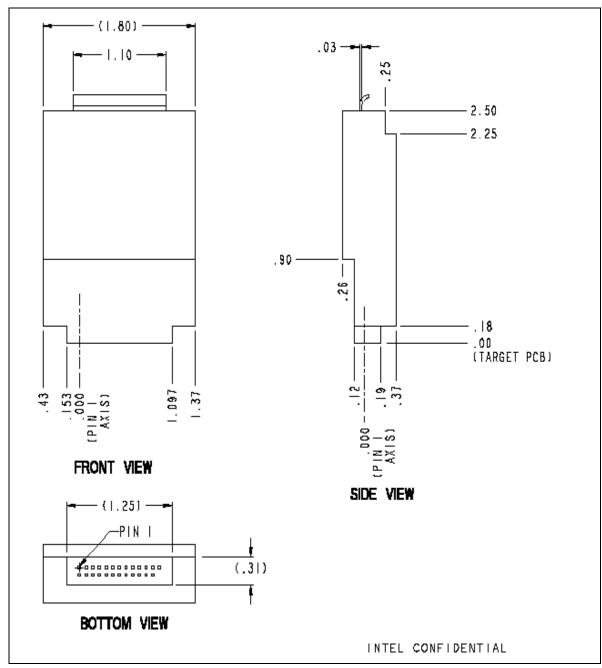

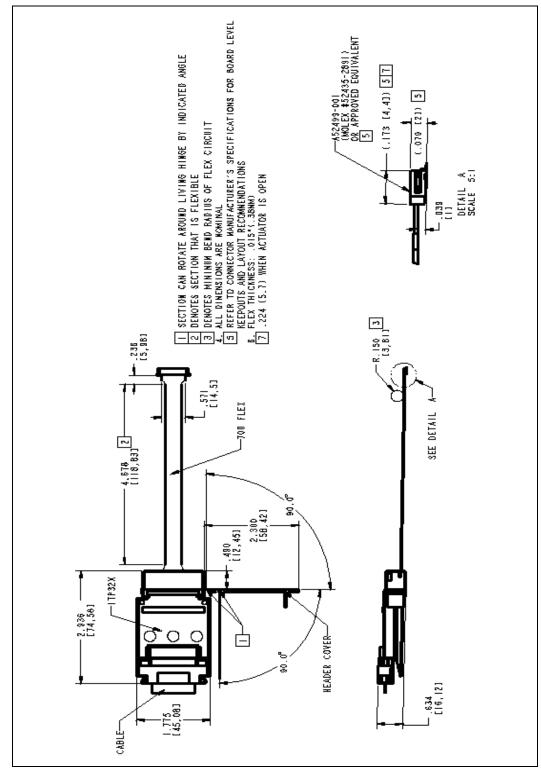

| Figure 14. ITP700 Flex Mechanical Drawing                                                                                             |      |

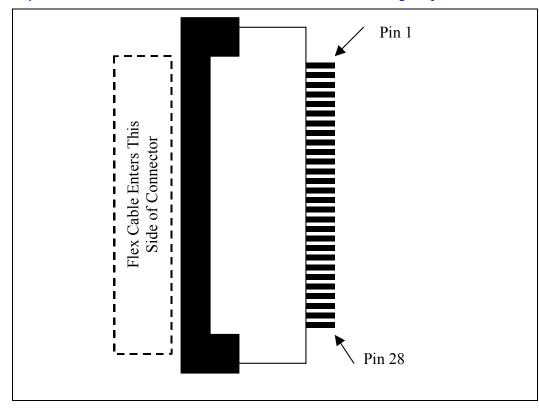

| Figure 15. Top View of Surface Mount ITP700 Flex Connector on the Target System                                                       |      |

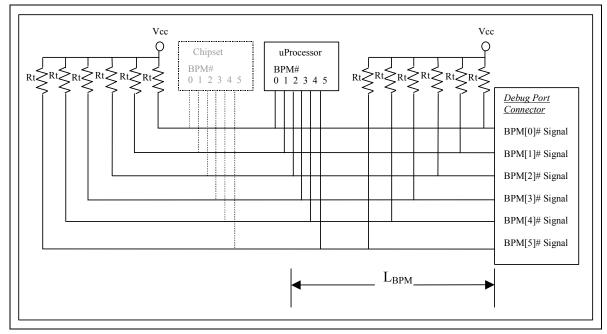

| Figure 16. BPM[5:0]# Connectivity for Intel <sup>®</sup> Xeon™ Processor with 512-KB L2 Cache a                                       |      |

| 2.20, 2.0, and 1.80 GHz DP / Intel <sup>®</sup> Xeon <sup>™</sup> Processor MP Servers                                                | . 57 |

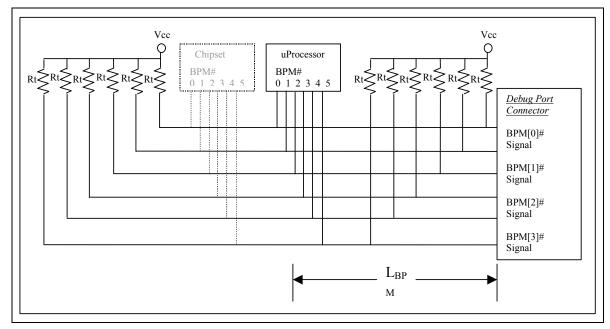

| Figure 17 – BPM[5:0]# Connectivity for Intel <sup>®</sup> Pentium <sup>®</sup> 4 Processor, Intel <sup>®</sup> Pentium <sup>®</sup> 4 |      |

| Processor-M, and Systems Based on Intel <sup>®</sup> Centrino <sup>™</sup> Mobile Technology                                          |      |

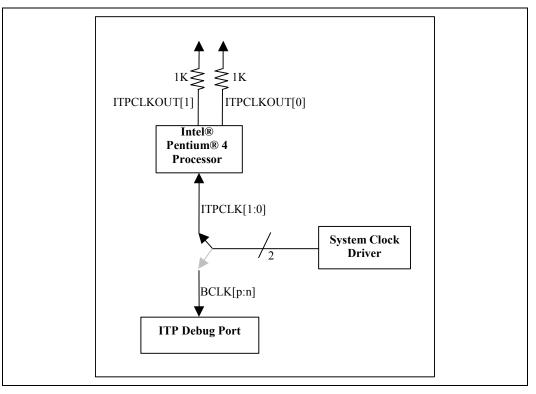

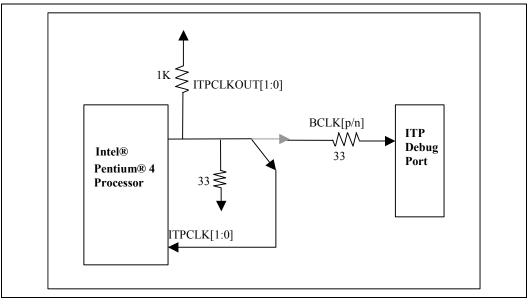

| Figure 18 – ITP Clock Routing options using System Clock Driver                                                                       |      |

| Figure 19 – ITP Clock Routing Options Using ITPCLKOUT[1:0] Pins                                                                       |      |

| Figure 20. Intel <sup>®</sup> Itanium <sup>®</sup> 2 IO Domain BPM Connectivity                                                       |      |

| Figure 21. Complete Bypass of One Out of Two Agents                                                                                   | . 77 |

| Figure 22. Complete Bypass of Two Agents with Three Headers                                                                           | . 77 |

| Figure 23. Three-pin Bypass Option                                                                                                    |      |

| Figure 24. Illegal Bypass Configuration                                                                                               | . 78 |

### **Tables**

| Table 1. Recommended Debug Port Signal Terminations                 | . 12 |

|---------------------------------------------------------------------|------|

| Table 2. System Signal Layout Guidelines                            |      |

| Table 3. JTAG Signal Layout Guidelines                              |      |

| Table 4. Execution Signal Layout Guidelines                         |      |

| Table 5. ITP700 Flex Edge Connector Pinout                          | . 18 |

| Table 6. Recommended Debug Port Signal Terminations                 | . 19 |

| Table 7. Reset Definitions                                          |      |

| Table 8. BPM[5:0]# Definitions                                      | . 21 |

| Table 9. ITP700 Flex Deltas from Standard ITP AC/DC Specifications  | . 22 |

| Table 10. Recommended Debug Port Signal Terminations                | . 24 |

| Table 11. System Signal Layout Guidelines                           | . 26 |

| Table 12. JTAG Signal Layout Guidelines                             | . 27 |

| Table 13. Execution Signal Layout Guidelines                        |      |

| Table 14. ITP700 DPA System Signal Descriptions                     | . 34 |

| Table 15. JTAG Signal Descriptions                                  | . 35 |

| Table 16. Execution Signal Descriptions                             | . 35 |

| Table 17. ITP700 DPA System Signal DC Characteristics               |      |

| Table 18. ITP700 DPA JTAG Signal DC Electrical Characteristics      | . 37 |

| Table 19. ITP700 DPA Execution Signal DC Electrical Characteristics | . 38 |

## int<sub>el</sub>

| Table 20. ITP700 DPA System Signal AC Electrical Characteristics                                               | . 38 |

|----------------------------------------------------------------------------------------------------------------|------|

| Table 21. ITP700 DPA JTAG Signal AC Electrical Characteristics                                                 |      |

| Table 22. ITP700 DPA Execution Signal AC Electrical Characteristics                                            |      |

| Table 23. P700 DPA Pin Absolute Maximums                                                                       |      |

| Table 24. ITP700 LVDPA System Signal Descriptions                                                              | .46  |

| Table 25. JTAG Signal Descriptions                                                                             |      |

| Table 26. Execution Signal Descriptions                                                                        |      |

| Table 27. ITP LVDPA System Signal DC Characteristics                                                           |      |

| Table 28. ITP700 LVDPA JTAG Signal DC Electrical Characteristics                                               | .49  |

| Table 29. ITP700 LVDPA Execution Signal DC Electrical Characteristics                                          |      |

| Table 30. ITP700 LVDPA System Signal AC Electrical Characteristics                                             |      |

| Table 31. ITP700 LVDPA JTAG Signal AC Electrical Characteristics                                               | . 51 |

| Table 32. ITP700 LVDPA Execution Signal AC Electrical Characteristics                                          | . 52 |

| Table 33. BPM[5:0]# Figure Definitions                                                                         |      |

| Table 34. BPM[5:0]# Figure Definitions                                                                         | . 60 |

| Table 35. ITP System Signal DC Characteristics for the Intel® Itanium® 2 Processor                             | . 66 |

| Table 36 - ITP JTAG Signal DC Electrical Characteristics for the Intel <sup>®</sup> Itanium <sup>®</sup> 2     |      |

| Processor                                                                                                      | . 67 |

| Table 37. ITP Execution Signal DC Electrical Characteristics for the Intel <sup>®</sup> Itanium <sup>®</sup> 2 |      |

| Processor                                                                                                      | . 68 |

| Table 38 - ITP System Signal AC Electrical Characteristics for the Intel <sup>®</sup> Itanium <sup>®</sup> 2   |      |

| Processor                                                                                                      | . 69 |

| Table 39 - ITP JTAG Signal AC Electrical Characteristics for the Intel <sup>®</sup> Itanium <sup>®</sup> 2     |      |

| Processor                                                                                                      | . 69 |

| Table 40. ITP Execution Signal AC Electrical Characteristics for the Intel <sup>®</sup> Itanium <sup>®</sup> 2 |      |

| Processor                                                                                                      |      |

| Table 41. Part 1: BPM[5:0]#BCLK(p/n) DBR# and RESET# Connectivity                                              | . 87 |

| Table 42. Part 2: TDI/TDO Connectivity                                                                         | . 88 |

| Table 43. TDI/TDO Connectivity Through Bypass Circuitry                                                        | . 88 |

| Table 44. Part 3: TCK / TMS Implementation                                                                     | . 88 |

| Table 45. Buffered TCK / TMS Implementation Issues                                                             | . 89 |

| Table 46. Part 4: Pull-Up / Pull Downs                                                                         | . 89 |

|                                                                                                                |      |

## **Revision History**

| Revision | Description                                                                                                                                                                                                                             | <b>Revision Date</b> |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Rev 1.0  | Initial Release with Intel <sup>®</sup> Xeon <sup>™</sup> Processor                                                                                                                                                                     | May 2001             |

| Rev 1.03 | Correction of +/- TCLK                                                                                                                                                                                                                  | May 2001             |

| Rev 1.10 | Addition of Chapter 5: Intel <sup>®</sup> Pentium <sup>®</sup> 4 Processor in the 478 Pin Package System Implementation Guidelines                                                                                                      | August 2001          |

|          | Addition of termination information for BPM[5:0]# and Reset# signals                                                                                                                                                                    |                      |

| Rev 1.15 | Append to Chapter 5: Intel <sup>®</sup> Pentium <sup>®</sup> 4 Processor in the 478 Pin<br>Package / Intel <sup>®</sup> Pentium <sup>®</sup> 4 Processor with 512KB L2 Cache on 0.13<br>micron process System Implementation Guidelines | January 2002         |

|          | Addition of ITP700 Flex debug port information                                                                                                                                                                                          |                      |

|          | Addition of Appendix E: Designer's Checklist for Schematic and Layout Reviews                                                                                                                                                           |                      |

| Rev 1.20 | I.20 Addition of Chapter 6: Intel <sup>®</sup> Xeon <sup>™</sup> Processor with 512-KB L2 Cache at 2.20, 2.0, and 1.80 GHz –DP Server System Implementation Guidelines                                                                  |                      |

|          | Updated ITP700 Keep-Out Volume Diagram                                                                                                                                                                                                  |                      |

| Rev 1.21 | Additional explanation of ITP700 Keep-Out Volume changes                                                                                                                                                                                | February 2002        |

| Rev 1.22 | Addition to Chapter 5 to include Mobile Intel <sup>®</sup> Pentium <sup>®</sup> 4 Processor-M System Implementation Guidelines                                                                                                          | June 2002            |

| Rev 1.30 | Chapter 7 added for Intel® Itanium® 2 Processor                                                                                                                                                                                         | July 2002            |

| Rev 1.40 | Chapter 8 added for Intel® E8870 Chipset                                                                                                                                                                                                | August 2002          |

| Rev 1.50 | Addition of Intel <sup>®</sup> Xeon <sup>™</sup> Processor MP Server System Implementation Guidelines                                                                                                                                   | November 2002        |

|          | Merge of Chapter 6 with Chapter 4                                                                                                                                                                                                       |                      |

| Rev 1.60 | Addition to Chapter 7 to include Intel <sup>®</sup> Centrino <sup>™</sup> mobile technology support                                                                                                                                     | March 2003           |

| Rev 1.65 | Append to Chapter 7 to include Intel® Pentium® 4 processor on 90 nm process System Implementation Guidelines                                                                                                                            | January 2004         |

### **Definitions**

| Term                | Definition                                                                                                                                                                                                                                                                 |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPA                 | Debug Port Adapter. Section of ITP hardware that plugs into the target system Debug Port.                                                                                                                                                                                  |

| ITP                 | The acronym "ITP" as used within this document refers to an In-Target Probe run-time control tool as produced by Intel as well as third party vendors. This specification is not meant to imply that any vendor's debug tool is preferred over any other.                  |

| ITP700 Flex         | Flex cable adapter to the ITP that connects to a small form factor connector on the target platform, drastically reducing the footprint and vertical clearance from the standard ITP700 style debug port. This debug port style currently supports UP configurations only. |

| JTAG                | Joint Test Access Group                                                                                                                                                                                                                                                    |

| Local TAP<br>Master | A device other than the ITP that is designed to control accesses into an IEEE STD 1149 style scan chain and all TAP agents contained within that scan chain. Usually this device is used for manufacturing test purposes.                                                  |

| LVDPA               | Low-Voltage Debug Port Adapter. Section of ITP hardware that plugs into the target system Debug Port that supports operating voltages as low as 0.6V.                                                                                                                      |

| TAP                 | IEEE STD 1149 defined test access port                                                                                                                                                                                                                                     |

| TAP Master          | A device that is designed to control accesses into an IEEE STD 1149 style scan chain and all TAP agents contained within that scan chain. The ITP is an example of a TAP master.                                                                                           |

| VTERM               | Termination voltage of the BPM[5:0]# and RESET# signals.                                                                                                                                                                                                                   |

| VTAP                | Pull-up voltage for the ITP scan chain signals                                                                                                                                                                                                                             |

### How to Use This Document

This document has two primary roles in the design process. First and foremost, this document is a location for recording all of the best-known methods relating to the design of an ITP700 based scan chain in a target. Second, this document serves as the Intel Corporation communication of Design Guide and In Target Probe (ITP) signal specifications for a given processor. The document is structured to serve both purposes.

Chapters 1 and 2 describe the debug port implementation guidelines for a generic uniprocessor (UP) and generic multiprocessor (MP) system, respectively.

Chapter 3, 4, and 5 contain the Electrical and Mechanical Specifications for the ITP700 DPA, ITP700 LVDPA, and ITP700 Flex respectively. These chapters include the specifications of the different types of ITP hardware IO under all drive levels as well as specifications under non-standard current loads and pull-up voltages. This information can be helpful if designers would like to know more about the characteristics of the ITP under non-standard operating conditions, or would like to interpolate the effects of changing recommended implementations to meet other design requirements. This Keepout-Volume (KOV) information in the Mechanical Requirements section is also useful when designing a debug port onto a platform.

Chapters 6 and beyond describe implementation information specific to particular Intel Corporation processor families. This information includes expected input and output voltage characteristics of the ITP (when terminated in the method recommended by this Design Guide) as well as processor-specific implementation details that are not consistent with the 'generic' implementation guidelines in Chapter 1 through Chapter 5. These chapters make reference to the 'generic' UP and MP routing guidelines found in Chapters 1 and 2.

The Appendices go into detail on certain advanced design topics that are not relevant to the other sections of this document. Appendices also include Spice Models for the ITP and a Designer's Checklist for a schematic and layout review.

System designers should first familiarize themselves with the general implementation, routing, and termination rules as defined in the UP or MP implementation guidelines chapters of this document as applicable to their design. They should then review the specific chapter for the processor that the system is being designed for. Note that some of the generic implementations may not be applicable based on the content of the processor specific chapter. Any non-standard design topics are described in the appendices of this document.

This page is intentionally left blank.

## 1 Uniprocessor ITP Debug Port Implementation Guidelines

The signals involved in the ITP debug system are high-speed signals and must be routed with highspeed design considerations in mind. The implementation offers some flexibility in areas such as scan chain routing, addition of non-ITP TAP master to the local scan chain, and clock rate of the scan chain. However, the implementation is not flexible in system bus BPM[5:0]#, RESET#, or BCLK(p/n) connections.

Simulation models of the ITP700 DPA interface hardware is available. Intel highly recommends that customers include this model in platform simulations. These models can be found in Appendix E of this document.

### 1.1 General Description

The debug port (DP) is the command and control interface for the In-Target Probe (ITP) debug tool. The ITP is a specialized JTAG Test Access Port (TAP) master that interfaces into processors and chipset TAP agents through a carefully routed private scan chain on the target system.

The primary operations of the ITP and associated debug port are to provide system, execution, and TAP interfaces to the target system. The system interface informs the debug tool if power, clock, and access state are available in the target system. The execution interface is used to coordinate debug activities with the current execution state of the agents attached to the debug port. The TAP interface allows for query and editing of registers and state within the agents attached to the scan chain.

The debug port and JTAG signal chain must be designed into a system board to utilize the ITP for debug purposes. There are several mechanical, electrical and functional constraints on the debug port and associated scan chain that must be followed. The mechanical constraints require a debug port connector to be installed in the system with adequate physical clearance for the ITP hardware while the system is running. The electrical constraints require that the debug port operate using the TAP signals at high speed, and that the ITP be connected to the processor system bus break point and reset signals for recovery at full speed through a dedicated BCLK connection. The functional constraint requires the debug port to be able to share the scan chain with any local TAP systems via a handshake and multiplexing scheme.

### **1.1.1 ITP Features**

- Operation at up to 16 MHz.

- Ability to drive up to one EXECUTION signal (BPM5DR#).

- Ability to monitor up to six EXECUTION signals (BPM[5-0]#).

- Accepts a differential system BCLK input.

- Synchronous TAP operations.

- Hot-plug support for the debug port adapter (DPA) into a target system.

- Supports arbitration with a local TAP Master (e.g. manufacturing test chain) through a simple handshake.

### **1.2 Recommended Signal Terminations**

#### **Table 1. Recommended Debug Port Signal Terminations**

| Signal    | Termination Value                                              | Termination<br>Voltage                 | Termination<br>Location         | Notes |

|-----------|----------------------------------------------------------------|----------------------------------------|---------------------------------|-------|

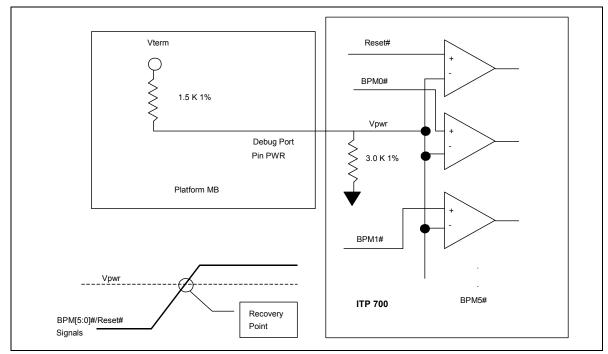

| PWR       | 1.5 kΩ 1%                                                      | VTERM of BPM[5:0]#<br>and RESET#       | Within 1 ns of debug port       | 1     |

| BCLK(p/n) |                                                                |                                        |                                 | 2     |

| DBA#      | 150 – 240 Ω 5%                                                 | VCC of target system recovery circuit. | Within 1 ns of debug<br>port    | 3     |

| DBR#      | 150 – 240 Ωs 5%                                                | VCC of target system recovery circuit  | Within 1 ns of debug<br>port    |       |

| FBI       | 220 Ω 5%                                                       | GND                                    | Within 200 ps of the receiver   | 4     |

| FBO       | Connect to TCK pin at the closest<br>BPM[5:0]# bus load device | NA                                     | NA                              |       |

| ТСК       | 27 Ω 1%                                                        | GND                                    | Within 200 ps of the debug port |       |

| TMS       | 39 Ω 1 %                                                       | VTAP                                   | Within 200 ps of the debug port |       |

| TDI       | 150 Ω 5%                                                       | VTAP                                   | Within 300 ps of the receiver   | 5     |

| TDO       | 75 Ω 5%                                                        | VTAP                                   | Within 300 ps of the debug port | 5     |

| TRST#     | 500 – 680 Ω 5%                                                 | GND                                    |                                 |       |

| BPM[5:0]# | Characteristic impedance of the transmission line 5%           | VTERM                                  |                                 | 2     |

| RESET#    | Characteristic impedance of the transmission line 5%           | VTERM                                  |                                 | 2     |

| BPM5DR#   | Connect to BPM[5]# at the debug<br>port                        | NA                                     | NA                              |       |

NOTES:

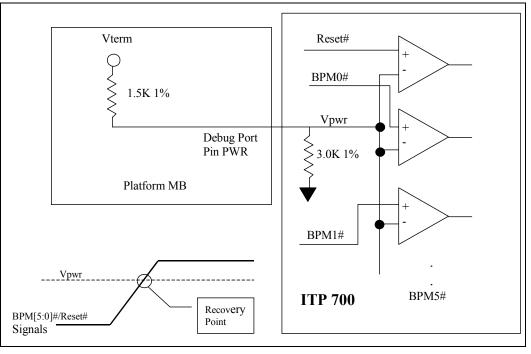

- The target system resistor connected between VTERM and the PWR pin is part of a voltage division circuit (see below). The voltage derived from the voltage divider is used as a reference for recovery of the BPM[5:0]# and RESET# signals on the ITP. The recovery point of the BPM[5:0]# and RESET# signals can be modified by scaling the target system resistor. The standard 1.5 K 1% target system resistor will result in a recovery point of 2/3rds of VTERM.

- 2. Resistance, voltage, and termination location are defined in the Platform Design Guide documentation.

- Only required if DBA# is used with any target system circuitry. This signal may be left unconnected if unused.

- 4. Only required if FBI is used to source a buffer for JTAG TCK. This signal may be left unconnected if unused.

- 5. A termination resistor must be located at the receiver of each scan chain agent

NOTE: By varying the platform 1.5-K resistor, the recovery point could be increased or decreased.

### 1.3 ITP Signal Layout Guidelines

This section contains the layout guidelines for the debug port signals. Please refer to the specification chapter for the debug port electrical and mechanical specifications. Routing to the debug port of Signals BPM[5:0]# and RESET# must be shorter than 1.0 ns of electrical length from the nearest system bus agent. Note that the <1.0 ns requirement applies only to the BPM[5:0]# and RESET# trace segments between the debug port and the nearest system bus agent. All other system bus trace segments must be routed according to the guidelines located in the Platform Design Guides.

There are three signal groups within the debug port. Each group has a different set of layout requirements:

- System The system signal group indicates the access state of the entire system

- JTAG The JTAG signal group consists of the five standard JTAG pins. The JTAG signals are to be designed to run up to 16 MHz.

- Execution The execution signal group contains the reset and run control signals used to indicate operational conditions.

The following three subsections clarify the routing guidelines for each of these signal classes. VTERM is the termination voltage of the system bus BPM[5:0]# and RESET# signals as defined by the processor data sheet. VTAP refers to the pull-up voltage of the JTAG signals on the system board. This pull-up voltage is chosen by the system designers to be consistent with the JTAG IO buffer specs for the processor and the ITP. Information on input voltage specifications, drive strength, and recommended termination values for the processor can be obtained from processor

datasheets. VTAP should be used for the pull-up resistors on all JTAG signals in the scan chain that operates directly from the ITP. If a bus translator is used to translate an ITP scan chain to a higher voltage, VTAP on the opposite side of the translator from the ITP shall change as well.

*Note:* All termination locations indicated are referenced to the target system.

### 1.3.1 System Signal Layout Guidelines

#### **Table 2. System Signal Layout Guidelines**

| Debug Port Signal | Layout Guideline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PWR               | If PWR is used to arbitrate with a local TAP master for control of the scan chain: Pull-up resistor to VTERM and an open drain control gate must be located less than 1 ns from the debug port.                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                   | If PWR is not used to arbitrate with a local TAP master for control of the Scan chain: Pull-up resistor to VTERM must be located less than 1 ns from the debug port.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| BCLK(p/n) 1       | BCLK for the debug port should originate as a unique output of the system clock tree. The BCLK routed from the clock distribution component to the debug port must have a propagation delay equal to the length of the BCLK traces from the clock distribution component to the other front side bus agents plus the electrical length of the BPM[5:0]# and RESET# signals as measured from the processor to the debug port. This will ensure that these critical signals have the same phase relationship at the debug port as is seen at the processor. |  |  |

|                   | BCLK is a differential high speed clock supplied by the target system. It is a critical system signal requiring careful timing and signal integrity considerations.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

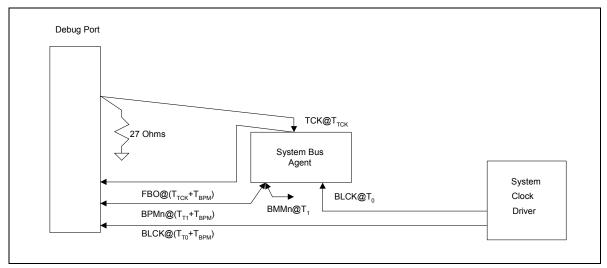

| FBO               | FBO is used to monitor the phase relationship of TCK to BCLK and to recover TDO. It is important that the phase of FBO to BCLK at the debug port is the same as the phase of TCK to BCLK at the processor. To meet this requirement, the electrical length fixed by BPM[5:0]# and RESET# (between the processor and the debug port) must also be the electrical length of FBO(TCK) from the processor back to the debug port. See the Execution Signal Layout Guidelines in this chapter for additional information.                                      |  |  |

| FBI               | FBI is a fast edge copy of TCK that can optionally be used as the source of scan chain TCK when TCK buffers are implemented on a system board. FBI should be loaded with no greater than 40 pF and have a DC load of no less than 200 $\Omega$ to GND. If used, this is a critical clock for the scan chain and must be analyzed for signal quality and timing with respect to the specifications of the intended receiver of the FBI signal.                                                                                                             |  |  |

| DBR#              | This is a non-critical route.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| DBA#              | This is a non-critical route.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

NOTE: : Refer to BCLK system requirements for proper termination requirements and routing rules

DBA# and DBR# are output signals from the ITP. The ITP provides an open drain FET closure to GND as the drive of DBA# and DBR#. The target system should provide the pull-up for both of these signals. The pull-up can be to any voltage up to five volts that is consistent with the input specifications of the component used to receive these signals on the target system. DBR# is the ITP debug port reset signal that should always be routed to the system reset controller. DBA# is the ITP debug port scan active signal used to indicate that the ITP is currently driving the scan chain. DBA# is an optional signal of the debug port.

### 1.3.2 JTAG Signal Layout Guidelines

#### **Table 3. JTAG Signal Layout Guidelines**

| Debug Port Signal | Layout Guideline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| тск               | This is a critical JTAG clock signal, sourced by the debug port, which requires thorough timing and signal integrity analysis/simulation. The termination resistor to GND on TCK must be located within 200 ps of the debug port in order to minimize IR losses that would degrade signal voltage levels at the loads. The length of TCK should not exceed 2 ns in electrical length. Note that TCK returns a feedback copy of TCK to FBO at the debug port. The length of the trace between the processor TCK pin and the debug port must be equal to the electrical length of BPM[5:0] and RESET# from the processor to the debug port. Load capacitance at the processor must be no more than 35 pF. It is strongly recommended that this signal be simulated for signal integrity purposes. Non-monotonicity on the rising or falling edge of TCK will render the ITP inoperative. See the Execution Signal Layout Guidelines section of this chapter for additional information. |  |  |

| TMS               | Critical JTAG mode select signal, sourced by the debug port, which requires moderate timing and signal integrity analysis / simulation. The termination resistor to VTAP on TMS should be located within 200 ps of the debug port in order to minimize resistive losses that would degrade signal voltage levels at the loads. TMS is driven on the falling edge of TCK at the ITP and recovered on the following rising edge of TCK at the processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| TDI, TDO          | JTAG scan data signals. These signals require minor timing and signal integrity analysis / simulation. The terminations should be located within 300 ps to each load. TDI is driven on the falling edge of TCK at the ITP and recovered on the following rising edge of TCK at the processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| TRST#             | Non-critical JTAG reset signal routed to all scan chain devices. TRST#<br>requires a pull-down resistor to ensure the signal is held in the asserted (low)<br>state if the debug port is not driving the signals. Layout of this signal needs to<br>be such that noise will not be coupled to the signal and cause a false reset of<br>the scan chain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

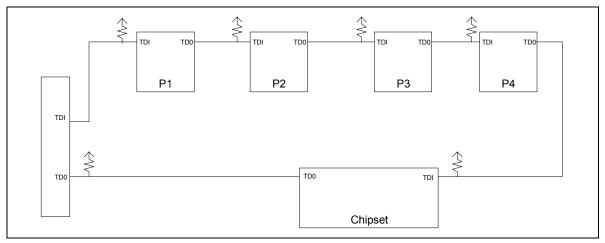

For a uniprocessor scan-chain that does not include a other scan chain components: The TDI pin of the ITP is connected to the TDI pin of the processor with the pull-up located within 200 ps of the processor. The TDO pin of the processor is routed back to the TDO pin of the debug port with the pull-up located within 200 ps of the debug port.

### **1.3.3 Execution Signal Layout Guidelines**

#### **Table 4. Execution Signal Layout Guidelines**

| Debug Port Signal | Layout Guideline                                                                                                                                                                                                                                                                                                                                                                |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BPM[5:0]#         | These signals are extremely routing critical. The debug port recovers these signals relative to BCLK at the debug port pins. Therefore, the signals must be routed with closely matched electrical lengths (within ±50 ps) and no greater than 1.0 ns from the processor to the debug port.                                                                                     |  |

| BPM5DR#           | The debug port BPM5DR# output pin should be connected on the board to the BPM5# pin of the debug port. This allows the ITP or run-control tool to drive BPM5# at reset. It also allows ITP to assert BPM5# if ITP needs to assert a trigger signal that can be seen directly by the target system. Note that ITP asserts / de-asserts this signal asynchronous to the bus BCLK. |  |

The debug port should be placed as close as is physically reasonable to the processor and no further than 1.0 ns flight time (as measured by trace length of the BPM[5:0]# signals) from the processor. System designers should record the flight time of the BPM[5:0]# signals from the processor to the debug port. This value will be important during the routing of several other debug port signals. Ideally BPM[5]# will be routed from the processor to the debug port BPM[5]# pin matched with the other BPM# signals. From pin 13 the trace will route directly to the debug port BPM5DR# pin and continue to the termination of the transmission line.

Assuming BCLK(p/n) signals are routed from the system clock buffer to each of the synchronous clock agents with a matched length, the copy of BCLK(p/n) from the system clock buffer to the ITP debug port must have a flight time equal to the matched length of the other synchronous clock agents plus the flight time of the BPM[5:0]# signals from the processor to the debug port noted above. This will ensure that the same BCLK to BPM[5:0]# phase relationship seen at the processor will be present at the debug port pins. BCLK trace lengths may be adjusted to center the recovery of BPM[5:0]# and RESET# at the debug port within the ITP receiver setup and hold window.

Multiple layer transitions of the BCLK, BPM, and TCK signals will compromise signal integrity. An effort should be made to minimize the number of layer transitions for these signals. Try to keep the BCLK, BPM, and TCK signals referenced to GND whenever possible. If layer transitions are required, stitching vias should be included near ever every layer transition of the BCLK, BPM, and TCK signals, even when not referencing the same voltage. This is recommended to reduce the lengths of return current loops. Adding an AC bypass capacitor near every layer transition or plane split between the two referenced planes will also help to minimize AC return current loops. An effort should be made to not share ITP AC bypass capacitors with other high-speed signals.

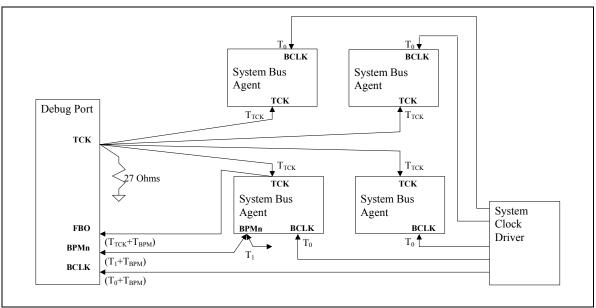

TCK and TMS must be routed with pull-up / pull-downs located at the driver. FBO is routed such that it is connected to the TCK at the processor, and routed back to the debug port with an electrical length equal to the flight time of the BPM[5:0]# and RESET# signals from the processor to the debug port. This is done to guarantee that the BCLK to TCK phase relationship at the processor will be seen at the debug port FBO and BCLK(p/n) pins. The diagram below illustrates these routing relationships.

Figure 2. Recommended Layout Topology

#### NOTES:

- 1. All of the above routes must be simulated to ensure signal integrity. Failure to do so may result in non functional ITP.

- 2. All combination timings in the above drawing are ±50 ps in routing length maximum.

The figure above defines propagation delays of various ITP signals from the driver to the receiver. The following are definitions of individual trace segments that are included in the figure.

- $T_{TCK}$  Propagation delay of the TCK trace from the debug port to the system bus agent TCK pin

- T<sub>BPM</sub> Propagation delay of the BPM traces from the debug port to the nearest system bus agent.

- T<sub>0</sub> Propagation delay of BCLK from the system clock driver to the processors and chipset components

- $T_1$  Propagation delay of the BPM traces from the driving system bus agent to the system bus agent closest to the debug port.

### 1.4 ITP700 Flex Alternative Debug Port

There is a smaller version of the debug port available as an alternative that can be designed into uniprocessor platforms. The ITP700 Flex is a single piece of flexible circuitry with a right-angled standard male debug port connector on one end and the other end is plugged into a small footprint surface mount connector that is soldered to the platform.

The following are the requirements that platforms must meet in order to be able to use the ITP700 Flex debug port.

- The target system cannot require the use of an external buffer for TCK

- BPM[5:0]# pins are not terminated correctly when the ITP700 Flex is not installed. The platform must either not use BPM[5:0]# signals when ITP700 Flex is not plugged in or it must be able to terminate BPM# [5:0]when ITP700 Flex is removed.

The advantages of this ITP700 Flex are a significantly reduced footprint and keepout volume. Please refer to the ITP700Flex specifications chapter for the mechanical specifications.

### 1.4.1 Signal Descriptions

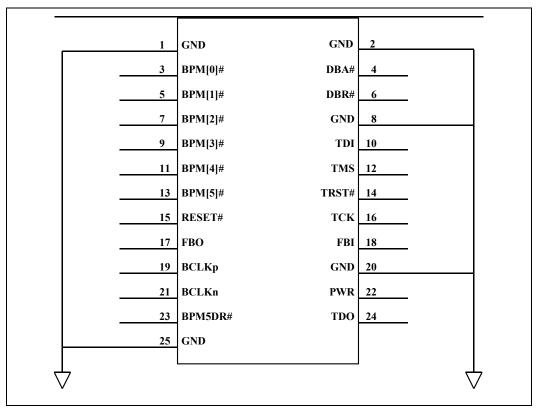

The pinout of the debug port connector at the end of the ITP700 Flex is identical to that of the standard debug port connector. See Figure 4 for details.

The pinout of the target system surface mount connector for ITP700 Flex is below.

#### Table 5. ITP700 Flex Edge Connector Pinout

| Pad # | Signal Name | Pad # | Signal Name |

|-------|-------------|-------|-------------|

| 1     | TDI         | 2     | TMS         |

| 3     | TRST#       | 4     | NC1         |

| 5     | тск         | 6     | NC2         |

| 7     | TDO         | 8     | BCLKn       |

| 9     | BCLKp       | 10    | GND         |

| 11    | FBO         | 12    | RESET#      |

| 13    | BPM5#       | 14    | GND         |

| 15    | BPM4#       | 16    | GND         |

| 17    | BPM3#       | 18    | GND         |

| 19    | BPM2#       | 20    | GND         |

| 21    | BPM1#       | 22    | GND         |

| 23    | BPM0#       | 24    | DBA#        |

| 25    | DBR#        | 26    | VTAP        |

| 27    | VTT         | 28    | VTT         |

### **1.4.2 Termination and Routing Guidelines**

#### Table 6. Recommended Debug Port Signal Terminations

| Signal               | Termination Value                                                 | Termination<br>Voltage                       | Termination<br>Location         | Notes |

|----------------------|-------------------------------------------------------------------|----------------------------------------------|---------------------------------|-------|

| BCLK(p/n)            |                                                                   |                                              |                                 | 1     |

| DBA#                 | 150 – 240 Ω 5%                                                    | VCC of target<br>system recovery<br>circuit. | Within 1 ns of debug port       | 2     |

| DBR#                 | 150 – 240 Ω 5%                                                    | VCC of target<br>system recovery<br>circuit  | Within 1 ns of debug port       |       |

| FBO                  | Connect to TCK pin at the<br>closest BPM[5:0]# bus load<br>device | NA                                           | NA                              |       |

| ТСК                  | 27 Ω 1%                                                           | GND                                          | Within 200 ps of the debug port |       |

| TMS                  | 39 Ω 1 %                                                          | VTAP                                         | Within 200 ps of the debug port |       |

| TDI                  | 150 Ω 5%                                                          | VTAP                                         | Within 300 ps of the receiver   | 3     |

| TDO                  | 75 Ω 5%                                                           | VTAP                                         | Within 300 ps of the debug port | 3     |

| TRST#                | 500 – 680 Ω 5%                                                    | GND                                          |                                 |       |

| BPM[5:0]#            | Characteristic impedance of<br>transmission line                  | VTERM                                        |                                 | 6     |

| RESET#               |                                                                   |                                              |                                 | 1, 5  |

| Vtt                  | N/A                                                               |                                              |                                 | 4     |

| All Other<br>Signals | N/A                                                               | N/A                                          | N/A                             |       |

NOTES:

- 1. Resistance, voltage, and termination location are defined in the Platform Design Guide documentation. Appendix D is not valid for ITP700 Flex.

- Only required if DBA# is used with any target system circuitry. This signal may be left unconnected if unused

- 3. A termination resistor must be located at the receiver of each scan chain agent.

- Mount debug port directly over the Vtt plane. Connect plane with vias and short, wide traces to Vtt (pins 27 and 28). If a plane is not available, add a 0.1 μF ceramic cap between Vtt and GND within 0.1 inches of the Vtt pins of the debug port.

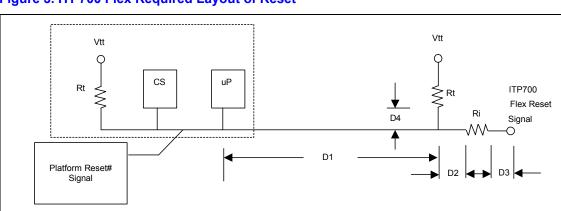

- 5. See Figure 3. ITP700 Flex Required Layout of Reset

- 6. See Figure 4. ITP700 Flex Required Layout of BPM[5:0]#

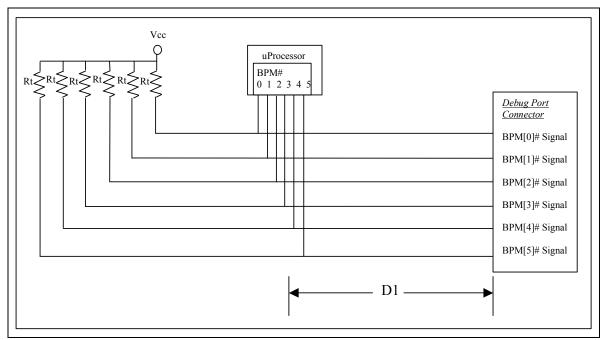

The most radical difference between the standard ITP700 and ITP700 Flex implementation guidelines is the termination requirements for the BPM[5:0]# signals. For ITP700 Flex the terminations on the debug port end of the transmission line are built into the ITP700 Flex device. Note that this means that there is no termination on BPM[5:0]# if the ITP700 Flex is not installed. If the platform designers require these signals to be terminated when ITP700 Flex is not installed it

is possible to terminate these signals using resistances equal to the characteristic impedance of the motherboard using short (100 ps or less) stubs after the trace meets the ITP700 Flex surface mount connector on the motherboard.

BPM[5:0]# lengths must still be matched on the motherboard to within 50 ps of one another and with RESET# length D1 (see Figure 4 and Figure 5). Note that BPM5DR# is completely removed form the ITP700 Flex design. Its functionality is integrated on the ITP700 Flex hardware. Systems using the ITP700 Flex must only contain one load on the BPM[5:0]# signals and thus there can be no BPM[5:0]# connections on the chipset.

*Note:* Note that BPM0# and BPM2# as well as BPM1# and BPM3# are no longer tied together at the processor or the debug port. Instead they are routed directly through (eg BPM[5:0]# on the closest agent routed directly to its corresponding pin BPM[5:0]# on the debug port or ITP700 Flex).

Since the BPM[5:0] Signals are terminated on the ITP700 Flex extension, the system bus termination voltage (Vtt) must be connected to the debug port. Preferably the ITP700 Flex will be located over the Vtt plane and pins 27 and 28 will be connected using short, wide traces to vias connected to the Vtt plane. The maximum expected current on these two pins together is 1.5 mA. If a plane is not available directly beneath the debug port connector, add a 0.1  $\mu$ F ceramic cap between Vtt and Ground within 0.1 inches of the Vtt pins of the debug port.

RESET# signal is a system bus signal and used in many places. The routing of the RESET# signal will be defined by the Platform Design Guide. The following figure illustrates the layout of the RESET# signal at the debug port. The information within the dotted box is a simplified representation of the Platform Design Guide layout. This document will only define the parameters D1, D2, D3, D4 and Ri at the debug port end of the RESET# line. Note that as the debug port will be at one end of the transmission line, it will have a termination resistance of the same value as that defined by the Platform Design Guide. Lengths D2, D3, and D4 should be as short as possible so as not to disturb the signal integrity of this system bus signal.

#### Figure 3. ITP700 Flex Required Layout of Reset

#### Table 7. Reset Definitions

| Parameter  | Min | Nominal  | Max   | Notes |

|------------|-----|----------|-------|-------|

| D1         |     |          | 1 ns  | 1     |

| D2, D3, D4 |     |          | 20 ps |       |

| Ri         |     | 150 Ω 5% |       |       |

#### Table 8. BPM[5:0]# Definitions

| Parameter | Min | Nominal | Мах  | Notes |

|-----------|-----|---------|------|-------|

| D1        |     |         | 1 ns | 1,2   |

| Rt        |     |         |      | 3     |

NOTES:

- 1. This signal must be length matched to RESET# to within 50 ps.

- 2. D1 is defined as the total length from the processor driver to the corresponding BPM at the connector.

- 3. Characteristic Impedance of Transmission Line

Vtap should be connected to the same supply as provides the voltage of the JTAG pull-up resistors on the target system. This connection is lightly loaded (<50 mA). Check your platform, as this voltage may be the same as Vtt.

### 1.4.3 ITP700 Flex Deltas to Standard ITP AC/DC Characteristics

The following data represents the changes to the AC/DC specifications from the ITP700 DPA or the ITP700 LVDPA to be used with the ITP700 Flex. Note that this table only represents the changes to the base tables. Please reference the AC/DC Specifications for the ITP700 DPA or the ITP700 LVDPA in the Specifications chapters for debug port style of choice.

| Signal            | Specification                             | Standard ITP      | ITP700 Flex       |

|-------------------|-------------------------------------------|-------------------|-------------------|

| BCLK(p/n)         | V <sub>PTP</sub>                          | 300 mV            | 320 mV            |

| DBA#, DBR#        | Resistance from pin to ground when active | 6 Ω               | 10 Ω              |

| ТСК               | V <sub>OH MIN</sub> <sup>2</sup>          | 1.25 V            | 1.20 V            |

| TMS               | V <sub>OL MAX</sub> <sup>3</sup>          | 0.30 V            | 0.32 V            |

| BPM[5:0]#, RESET# | V <sub>IH MIN</sub>                       | PWR+(0.15*VTERM)  | PWR+(0.16*VTERM)  |

| BPM[5:0]#, RESET# | V <sub>IL MAX</sub>                       | PWR -(0.15*VTERM) | PWR -(0.16*VTERM) |

| BPM[5:0]#, RESET# | Min Setup                                 | 400 ps            | 430 ps            |

| BPM[5:0]#, RESET# | Min Hold                                  | 200 ps            | 230 ps            |

#### Table 9. ITP700 Flex Deltas from Standard ITP AC/DC Specifications

NOTES:

1. At maximum current specified. 2. As measured into a 39  $\Omega$  1% resistor terminated to 1.10 V.

2

## Multiprocessor ITP Debug Port Implementation Guidelines

The ITP scan chain of multiprocessor systems with multiple chipset components requires that the debug port and associated scan chain be designed into the system board. An interposer debug port solution will not provide visibility to a multiple load scan chain because an interposer has no physical way to break the scan chain without losing access to the remainder of the processors and chipset. If the traces, termination, and connector footprint (without the header) for the debug port are designed into a system board, it is possible to enable use of a multiple load scan chain by simply populating the debug port header.

The signals involved in the ITP debug system are high-speed signals and must be routed with high speed design considerations in mind. The implementation offers some flexibility in areas such as scan chain routing, addition of non-ITP TAP master to the local scan chain, and clock rate of the scan chain. However, the implementation is not flexible in system bus BPM[5:0]#, RESET#, or BCLK(p/n) connections.

Simulation models of the ITP interface hardware are available. Intel highly recommends that customers include this model in platform simulations. These models can be found in Appendix E of this document.

### 2.1 General Description

The debug port (DP) is the command and control interface for the In-Target Probe (ITP) debug tool. The ITP is a specialized Test Access Port (TAP) master that interfaces into processors and chipset TAP agents through a carefully routed private scan chain on the target system.

The primary operations of the ITP and associated debug port are to provide system, execution, and TAP interfaces to the target system. The system interface informs the debug tool if power, clock, and access state are available in the target system. The execution interface is used to coordinate debug activities with the current execution state of the agents attached to the debug port. The TAP interface allows for query and editing of registers and state within the agents attached to the scan chain.

The debug port and JTAG signal chain must be designed into a system board to utilize the ITP for debug purposes. There are several mechanical, electrical and functional constraints on the debug port and associated scan chain that must be followed. The mechanical constraints require a debug port connector to be installed in the system with adequate physical clearance for the ITP hardware while the system is running. The electrical constraints require that the debug port operate using the TAP signals at high speed, and that the ITP be connected to the processor system bus debug signals for recovery at full speed through a dedicated BCLK connection. The functional constraint requires the debug port to be able to share the scan chain with any local TAP systems via a handshake and multiplexing scheme.

### 2.1.1 ITP Features

- Operation at up to 16 MHz.

- Ability to drive up to one EXECUTION signal (BPM5#).

- Ability to monitor up to six EXECUTION signals (BPM[5-0]#).

- Accepts a differential system BCLK.

- Synchronous TAP operations.

- Hot-plug support for the debug port adapter (DPA) into a target system.

- Supports arbitration with a local TAP Master (e.g., manufacturing test chain) through a simple handshake.

### 2.2 **Recommended Signal Terminations**

#### **Table 10. Recommended Debug Port Signal Terminations**

| Signal    | Termination Value                                                 | Termination<br>Voltage                   | Termination<br>Location                                                 | Notes |

|-----------|-------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------|-------|

| PWR       | 1.5 K 1%                                                          | VTERM of BPM[5:0]#<br>and RESET#         | Within 1 ns of debug port                                               | 1     |

| BCLK(p/n) |                                                                   |                                          |                                                                         |       |

| DBA#      | 150 – 240 Ω 5%                                                    | VCC of target system<br>recovery circuit | Within 1 ns of debug port                                               | 2     |

| DBR#      | 150 – 240 Ω 5%                                                    | VCC of target system<br>recovery circuit | Within 1 ns of debug port                                               |       |

| FBI       | 220 Ω 5%                                                          | GND                                      | Within 200 ps of the receiver                                           | 3     |

| FBO       | Connect to TCK pin at the<br>closest BPM[5:0]# bus load<br>device | NA                                       | NA                                                                      |       |

| тск       | 27 Ω 1%                                                           | GND                                      | At branch of star<br>topology and within<br>200 ps of the debug<br>port |       |

| TMS       | 39 Ω 1 %                                                          | VTAP                                     | At branch of star<br>topology and within<br>200 ps of the debug<br>port |       |

| TDI       | 150 Ω 5%                                                          | VTAP                                     | Within 300 ps of the receiver                                           | 4     |

| TDO       | 75 Ω 5%                                                           | VTAP                                     | Within 300 ps of the debug port                                         | 4     |

| TRST#     | 500 – 680 Ω 5%                                                    | GND                                      |                                                                         |       |

| BPM[5:0]# | Characteristic impedance of the transmission line                 | VTERM                                    |                                                                         |       |