## Intel® Pentium® II Processor – Low-Power Module Design Guide

**Application Note**

February 2000

Order Number: 273212-003

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> Pentium<sup>®</sup> II Processor – Low-Power Module may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2000

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Introduction |                                                        |    |  |

|-----|--------------|--------------------------------------------------------|----|--|

|     | 1.1          | Key Terms                                              | 9  |  |

|     | 1.2          | Overview                                               |    |  |

|     | 1.3          | Related Documents                                      | 11 |  |

| 2.0 | Desi         | ign Features                                           | 12 |  |

|     | 2.1          | Pentium <sup>®</sup> II Processor – Low Power Module   |    |  |

|     | 2.2          | Intel® 440BX AGPset                                    |    |  |

|     |              | 2.2.1 System Bus Interface                             |    |  |

|     |              | 2.2.2 DRAM Interface                                   |    |  |

|     |              | 2.2.3 Accelerated Graphics Port Interface              |    |  |

|     |              | 2.2.4 PCI Interface                                    |    |  |

|     | 2.3          | PCI ISA IDE Xcelerator (PIIX4E)                        |    |  |

| 2.0 |              | ·                                                      |    |  |

| 3.0 |              | nory Guidelines                                        |    |  |

|     | 3.1          | DRAM Interface Overview                                |    |  |

|     |              | 3.1.1 SDRAM Signal Description                         |    |  |

|     |              | 3.1.2 SDRAM Signal Connectivity                        |    |  |

|     |              | 3.1.4 Single Set DRAM Interface                        |    |  |

|     |              | 3.1.4.1 EDO DRAM                                       |    |  |

|     |              | 3.1.4.2 SDRAM                                          |    |  |

|     | 3.2          | DRAM Layout Guidelines                                 |    |  |

|     |              | 3.2.1 SODIMM Connection - EDO DRAMs                    |    |  |

|     |              | 3.2.2 SODIMM Connection - SDRAM                        |    |  |

|     | 0.0          | 3.2.3 Memory Trace Lengths for Module Design           |    |  |

|     | 3.3          | SODIMM DRAM Organization                               |    |  |

|     |              | ·                                                      |    |  |

| 4.0 | Cloc         | king Guidelines                                        |    |  |

|     | 4.1          | Clocking System Overview                               | 27 |  |

|     | 4.2          | Clock Synthesizer Pinout and Specifications            |    |  |

|     | 4.3          | Timing Guidelines                                      |    |  |

|     | 4.4          | Clock Layout Guidelines                                |    |  |

|     | 4.5<br>4.6   | Optional Clock LayoutClock Vendors                     |    |  |

|     |              |                                                        |    |  |

| 5.0 | 8244         | I3BX AGP Interface for Low-Power Module Design         | 33 |  |

|     | 5.1          | Layout and Routing Guidelines                          |    |  |

|     |              | 5.1.1 On-board AGP Compliant Device Layout Guidelines  |    |  |

|     |              | 5.1.1.1 Data and Strobe Signal Routing Recommendations |    |  |

|     | 5.2          | 5.1.1.2 Control Signal Routing Recommendations         |    |  |

|     | 5.2<br>5.3   | AGP IDSEL Routing                                      |    |  |

|     | 0.0          | 7.C. 12.C.L. 1.Codii 19                                |    |  |

### Pentium<sup>®</sup> II Processor – Low-Power Module Design Guide

| 6.0 | Desi | gn Gui  | deline Checklists                                              | 35   |

|-----|------|---------|----------------------------------------------------------------|------|

|     | 6.1  | Resist  | or Values                                                      | 35   |

|     | 6.2  | Low-P   | ower Module Design Checklist [ ]Pass, [ ]Fail                  | 36   |

|     |      | 6.2.1   | Low-Power Module Errata                                        |      |

|     |      | 6.2.2   | Power and Ground Pins                                          | 36   |

|     |      | 6.2.3   | Decoupling Requirements                                        | 37   |

|     |      |         | 6.2.3.1 V_DC and V_5 Decoupling                                | 38   |

|     |      | 6.2.4   | Clock and Test Signals                                         | 39   |

|     |      | 6.2.5   | SDRAM and EDO Signals                                          | 39   |

|     |      | 6.2.6   | Module Strapping Options                                       | 40   |

|     |      | 6.2.7   | PCI Bus Signals                                                | 40   |

|     |      |         | 6.2.7.1 Design Considerations                                  | 40   |

|     |      | 6.2.8   | Processor/PIIX4E ISA Bridge Sideband Signals                   |      |

|     |      | 6.2.9   | Power Management Signals                                       |      |

|     |      | 6.2.10  | 5                                                              |      |

|     | 6.3  | 82371   | EB (PIIX4E) Design Checklist [ ]Pass, [ ]Fail                  |      |

|     |      | 6.3.1   | 82371EB (PIIX4E) Errata                                        |      |

|     |      | 6.3.2   | Power and Ground Pins                                          |      |

|     |      | 6.3.3   | Clock and Test Signals                                         |      |

|     |      | 6.3.4   | PCI Bus Signals                                                |      |

|     |      | 6.3.5   | ISA/EIO Signals                                                |      |

|     |      | 6.3.6   | Power Management Signals                                       |      |

|     |      | 6.3.7   | USB Interface                                                  |      |

|     |      | 6.3.8   | IDE Interface                                                  |      |

|     |      | 6.3.9   | BIOS to Flash Memory Interface                                 |      |

|     |      | 6.3.10  |                                                                |      |

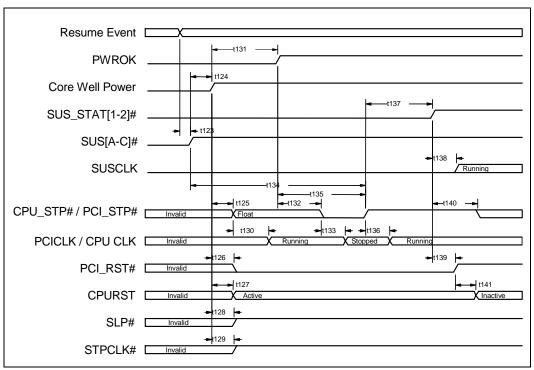

| 7.0 | Pow  | er Sequ | uencing                                                        | 50   |

|     | 7.1  | PIIX4E  | Power Sequencing                                               | 50   |

|     |      | 7.1.1   | Power Sequencing Requirements                                  |      |

|     |      | 7.1.2   | Suspend/Resume and Power Plane Control                         |      |

|     |      |         | 7.1.2.1 Power On Suspend (POS) System Model                    |      |

|     |      |         | 7.1.2.2 Suspend to RAM (STR)                                   | 51   |

|     |      |         | 7.1.2.3 Suspend to Disk (STD) and Soft Off (SOff)              |      |

|     |      | 710     | 7.1.2.4 Mechanical Off (MOff)                                  |      |

|     |      | 7.1.3   | System Resume                                                  |      |

|     |      |         | 7.1.3.1 System Resume Events                                   | 53   |

|     |      | 7.1.4   | System Suspend and Resume Control Signaling                    |      |

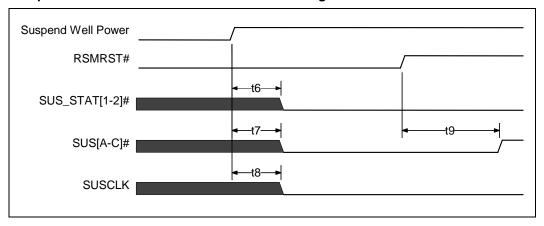

|     |      | 7.1     | 7.1.4.1 Power Well and Reset Signal Timings                    |      |

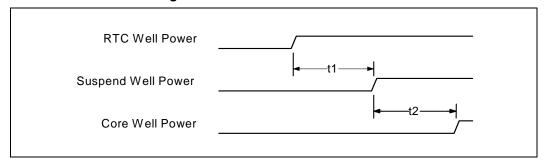

|     |      |         | 7.1.4.2 PIIX4E Power Well Timings                              |      |

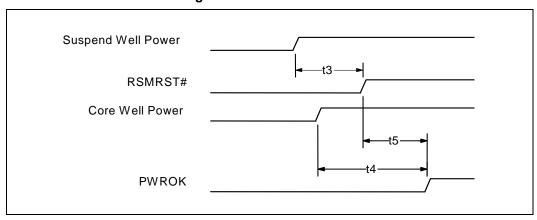

|     |      |         | 7.1.4.3 RSMRST# and PWROK Timing                               |      |

|     |      |         | 7.1.4.4 Suspend Well Power and RSMRST# Activated Signals       |      |

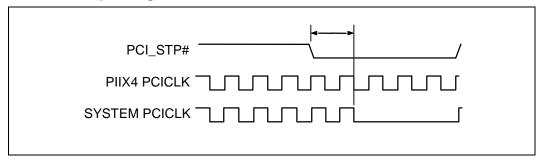

|     |      |         | 7.1.4.5 PCI Clock Control Timings                              | 57   |

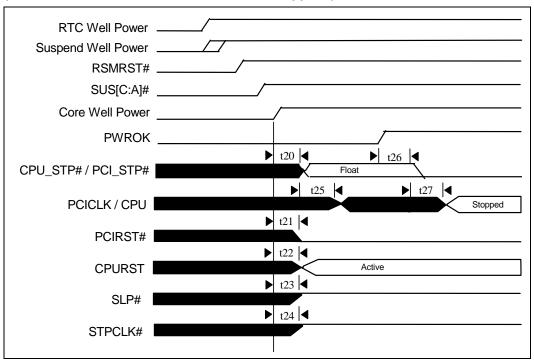

|     |      |         | 7.1.4.6 Core Well Power and PWROK Activated Signals (RSMRST#   |      |

|     |      |         | Inactive Before Core Well Power Applied)                       | . 58 |

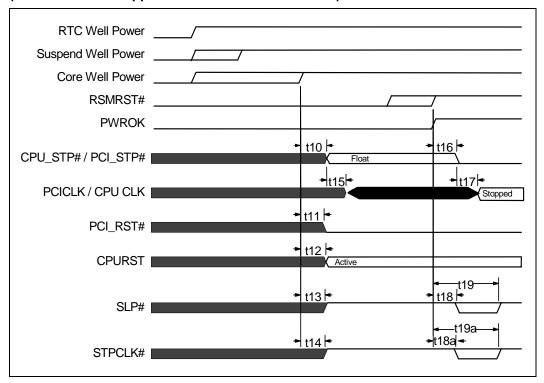

|     |      |         | 7.1.4.7 Core Well Power and PWROK Activated Signals (Core Well | EC   |

|     |      | 715     | Power Applied Before RSMRST# Inactive)                         |      |

|     |      | 7.1.5   | Power Management State Transition Timings                      |      |

|     |      |         | 7.1.5.1 Mechanical On to On                                    |      |

|     |      |         | 7.1.0.2 0.1.0.1 00                                             | . 02 |

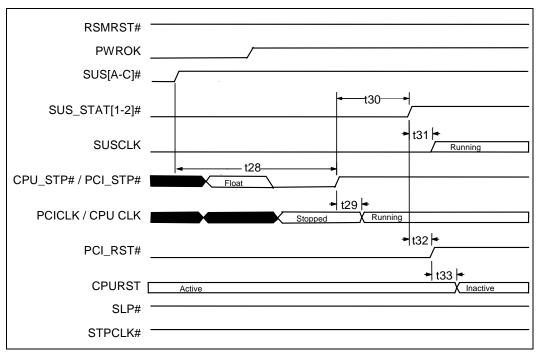

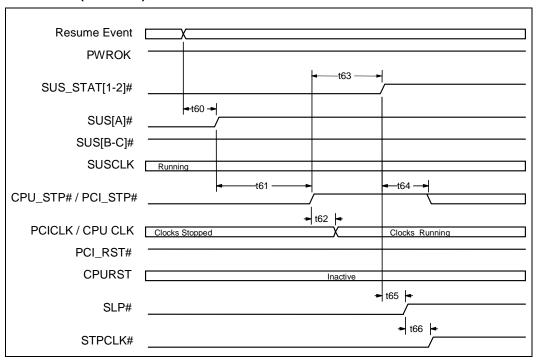

|            | 7.1.5.3 POS to On (with Processor and PCI Reset)            |    |

|------------|-------------------------------------------------------------|----|

|            | 7.1.5.4 POS to On (with Processor Reset)                    |    |

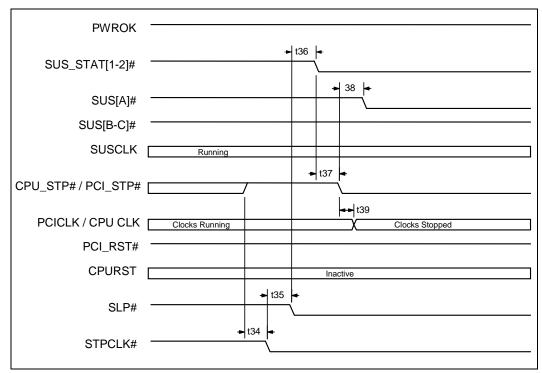

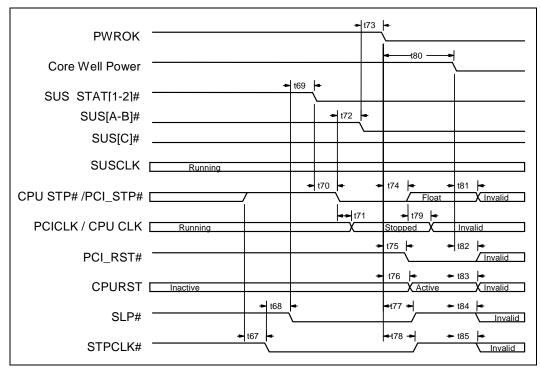

|            | 7.1.5.6 On to STR                                           |    |

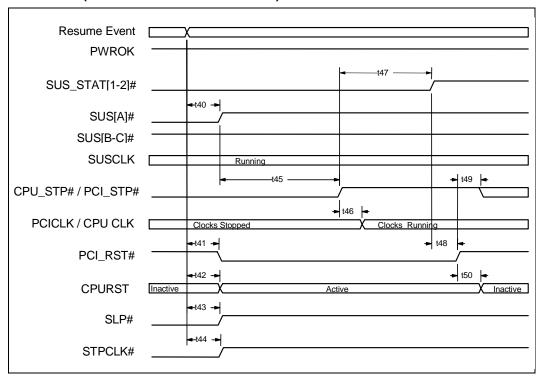

|            | 7.1.5.7 STR to On                                           |    |

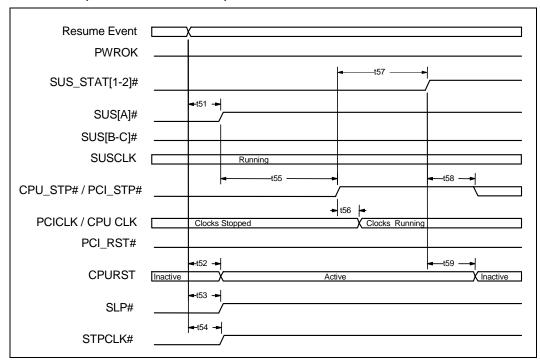

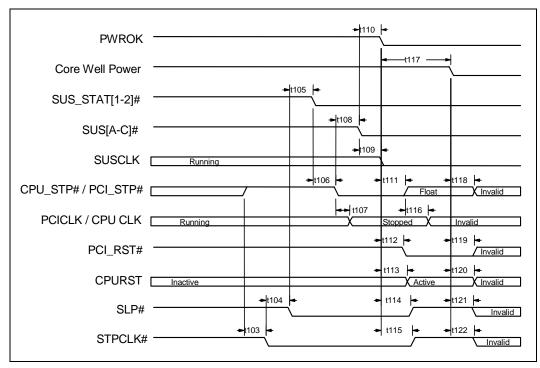

|            | 7.1.5.8 On to STD/SOff                                      |    |

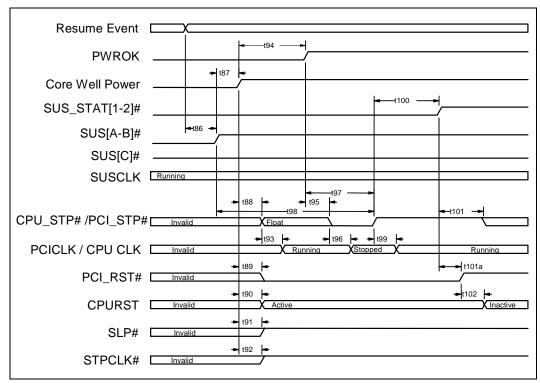

|            | 7.1.5.9 STD/SOff to On                                      |    |

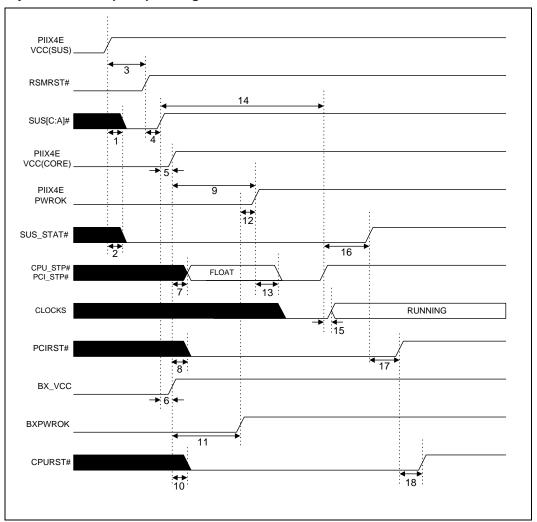

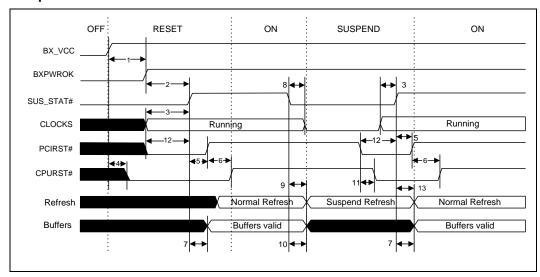

| 7.2        | 82443BX Host Bridge/Controller Power Sequencing             |    |

|            | 7.2.1 Power Sequencing Requirements                         |    |

|            | 7.2.2 440BX AGPset Power Management                         |    |

|            | 7.2.2.1 System Power Modes                                  |    |

|            | 7.2.2.2 System Power-up Sequencing                          | 76 |

|            | 7.2.2.3 Suspend Resume Protocols                            |    |

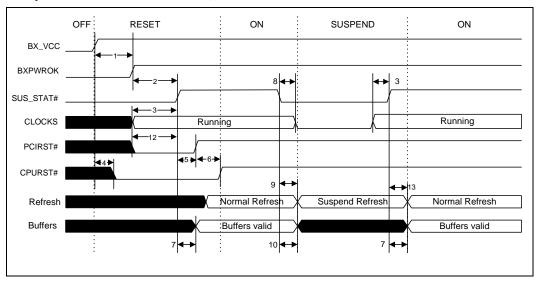

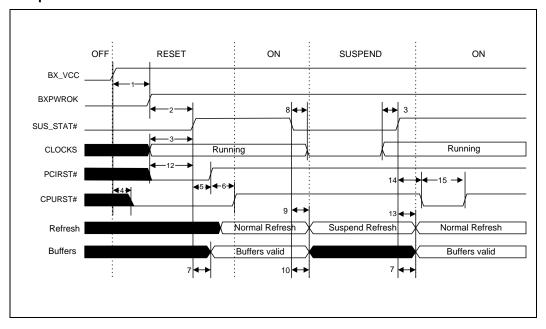

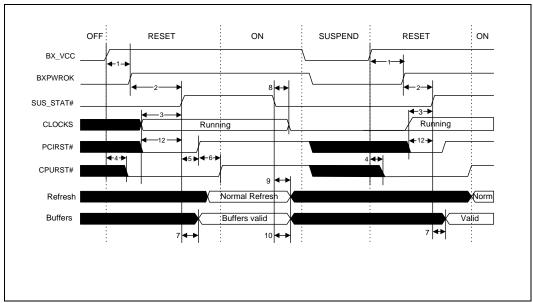

|            | 7.2.2.4 82443BX Suspend/Resume Sequences and Timing         | 81 |

|            | 7.2.2.5 Suspend/Resume with PCIRST# Active                  | 82 |

|            | 7.2.2.6 Suspend/Resume with inactive PCIRST#, CPURST#       |    |

|            | 7.2.2.7 Suspend/Resume with CPURST Active, PCIRST# Inactive |    |

| <b>-</b> 0 | 7.2.2.8 Suspend/Resume from STD                             |    |

| 7.3        | Low-Power Module Power Sequencing                           |    |

|            | 7.3.1 Voltage Regulator Control                             |    |

|            | 7.3.2 Voltage Signal Definition and Sequencing              | 86 |

| 1          | Low-Power Module/440BX AGPset System Block Diagram          | 10 |

|            |                                                             |    |

| 2          | EDO DRAM - One On-board Bank, Two SODIMMs                   |    |

|            | EDO DRAM - Two SODIMMs EDO DRAM - Three SODIMMs             |    |

| 4<br>5     | SDRAM - One On-board Bank, Two SODIMMs                      |    |

| 5<br>6     | SDRAM - Two SODIMMs                                         |    |

| 7          | SDRAM - Two SODIMMs                                         |    |

| 8          | Clock Connections to the Low-Power Module                   |    |

| 9          | Pinout for CK100-M Compatible Clock Synthesizer             |    |

| 10         | Pinout for CKF00-W Compatible Clock Synthesizer             |    |

| 11         | Timing Specifications Layout                                |    |

| 12         | Low-Power Module Clocking Layout                            |    |

| 13         | General Clock Layout                                        |    |

| 14         | On-board AGP Compliant Device Layout Guidelines             |    |

| 15         | Signal Layout Recommendations                               |    |

| 16         | Pull-up Resistor Example                                    |    |

| 17         | V_DC to V_5 Decoupling                                      |    |

| 18         | Clock Design Block Diagram                                  |    |

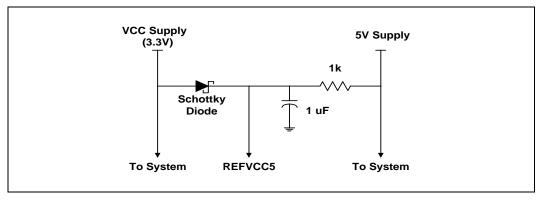

| 19         | VREF Supply Schematic                                       |    |

| 20         | PIIX4E Power Well Timings                                   |    |

| 21         | RSMRST# and PWROK Timings                                   |    |

| 22         | Suspend Well Power and RSMRST# Activated Signals            |    |

| 23         | PCI Clock Stop Timing                                       |    |

| 24         | PCI Clock Start Timing                                      |    |

| 25         | Core Well Power and PWROK Activated Signals                 |    |

## Pentium<sup>®</sup> II Processor – Low-Power Module Design Guide

**Tables**

26

|          | (RSMRST# Inactive before Core Well Power Applied)            | 58 |

|----------|--------------------------------------------------------------|----|

| 26       | Core Well Power and PWROK Activated Signals                  |    |

|          | (Core Well Power Applied before RSMRST# Inactive)            | 59 |

| 27       | Mechanical Off to On                                         |    |

| 28       | On to POS                                                    |    |

| 29       | POS to On (with Processor and PCI Reset)                     | 63 |

| 30       | POS to On (with Processor Reset)                             |    |

| 31       | POS to On (No Reset)                                         |    |

| 32       | On to STR                                                    | 66 |

| 33       | STR to On                                                    |    |

| 34       | On to STD/SOff                                               |    |

| 35       | STD/SOff to On                                               |    |

| 36       | REFVCC5 Supply Circuit Schematic                             |    |

| 37       | System Power-up Sequencing                                   |    |

| 38       | Suspend/Resume with PCIRST# Active                           |    |

| 39       | Suspend/Resume with CPURST, PCIRST# Inactive                 |    |

| 40       | Suspend/Resume with Inactive PCIRST and Active CPURST#       |    |

| 41       | Suspend/Resume from STD                                      |    |

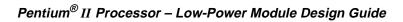

| 42       | Power On Sequence                                            | 87 |

| 1        | Related Intel Documents                                      | 11 |

| 2        | Related Specifications                                       |    |

| 3        | SDRAM Signal Descriptions                                    |    |

| 3<br>4   | SDRAM Signals and Corresponding SO-DIMM Pins                 |    |

| 5        | Module SDRAM Signals and Corresponding Onboard SDRAM Signals |    |

| 6        | Trace Lengths for the DRAM Interface                         |    |

| 7        | SODIMM DRAM Organization                                     |    |

| 8        | System Examples for Supporting 64-Mbit SDRAM                 |    |

| 9        | Timing Specifications for Maximum and Minimum Clock Skews    |    |

| 10       | Low-Power Module Clocking Trace Layout Specifications        |    |

| 11       | Clock Vendors                                                |    |

| 12       | Data and Associated Strobe                                   |    |

| 13       | Motherboard Recommendations                                  |    |

| 14       | Control Signal Line Length Recommendations                   |    |

| 15       | Power Supply Design Specifications                           |    |

| 16       | Capacitance Requirement per Power Plane                      |    |

| 17       | Clock and Test Signal Resistor Values                        |    |

| 18       | SDRAM and EDO Signal Resistor Values                         |    |

| 19       | Low-Power Module Strapping Options                           |    |

| 20       | PCI Bus Signals Resistor Values                              |    |

| 21       | Sideband Signal Resistor Values                              | 41 |

| 22       | Power Management Signals Resistor Values                     |    |

| 23       | A O D O's state Desi's (see Malesta                          |    |

|          | AGP Signals Resistor Values                                  |    |

| 24<br>25 | PIIX4E Power Signal Pin Assignments                          | 44 |

6 Application Note

PCI Bus Signal Resistor Values......45

| 27 | ISA/EIO Signal Resistor Values                    | 46 |

|----|---------------------------------------------------|----|

| 28 | Power Management Signal Resistor Values           | 47 |

| 29 | IDE Interface Signal Resistor Values              | 48 |

| 30 | ITP/JTAG Interface                                | 49 |

| 31 | Power State Decode                                | 52 |

| 32 | Resume Events Supported In Different Power States | 52 |

| 33 | Resume Event Programming Model                    | 53 |

| 34 | Power Plane Control                               | 54 |

| 35 | Power Plane Control Using SUS[C:A]# Signals       | 54 |

| 36 | PIIX4E Power Well Timings                         | 55 |

| 37 | RSMRST# and PWROK Timing                          | 55 |

| 38 | Suspend Well Power and RSMRST# Timing             | 56 |

| 39 | Core Well Power and PWROK Timing                  | 58 |

| 40 | Core Well Power and PWROK Timing                  | 60 |

| 41 | Mechanical Off to On Timing                       | 61 |

| 42 | On to POS Timing                                  | 62 |

| 43 | POS to On Timing                                  | 63 |

| 44 | POS to On (with Processor Reset) Timing           | 64 |

| 45 | POS to On (No Reset) Timing                       | 65 |

| 46 | On to STR Timing                                  | 67 |

| 47 | STR to On Timing                                  | 68 |

| 48 | On to STD/SOff Timing                             | 70 |

| 49 | STD/SOff to On Timing                             | 72 |

| 50 | System-wide Low-power Modes                       | 75 |

| 51 | System Power-up Sequencing Timing                 | 77 |

| 52 | Suspend Resume Events And Activities              | 78 |

| 53 | 443BX Signal States During POS and STR Modes      |    |

| 54 | Suspend/Resume Timing                             | 81 |

| 55 | Voltage Signal Definitions and Sequences          | 86 |

### Revision History

| Revision | Date         | Notes                                                                                                                                                                                               |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 003      | January 2000 | Updated V_DC spec. Expanded description of decoupling requirements and added section on ITP/JTAG. Updated document to cover Pentium <sup>®</sup> II Processor with On Die Cache – Low-Power Module. |

| 002      | May 1999     | Changed module name to Pentium® II Processor – Low-Power Module                                                                                                                                     |

| 001      | October 1998 | First release of this document.                                                                                                                                                                     |

### 1.0 Introduction

This document provides design guidelines for developing systems based on the Intel<sup>®</sup> Pentium<sup>®</sup> II Processor – Low-Power Module. The module is available in two versions:

- 266 MHz Pentium II Processor Low-Power Module with 512 Kbytes of on-board L2 cache

- 333 MHz Pentium II Processor with On-Die Cache with 256 Kbytes of on-die L2 cache

System board and memory subsystem design guidelines are included. Special design recommendations and concerns are presented. Likely design errors have been listed here in a checklist format. These are recommendations only. It is recommended that you perform your own simulations to meet design-specific requirements.

### 1.1 Key Terms

The Low-Power Module is identical to the Intel<sup>®</sup> Pentium<sup>®</sup> II Processor Mobile Module Connector 2 (MMC-2). A complete description of the module is located in the *Intel<sup>®</sup> Pentium<sup>®</sup> II Processor – Low-Power Module* datasheet or the *Intel<sup>®</sup> Pentium<sup>®</sup> II Processor with On-Die Cache – Low-Power Module* datasheet.

**Intel 440BX AGPset** refers to both the 82443 BX Host Bridge/Controller and the 82371EB PCI ISA IDE Xcelerator.

82443BX refers to the Intel 82443BX Host Bridge/Controller.

PIIX4E refers to the Intel 82371EB PCI ISA IDE Xcelerator.

**Design Features** are items that allow the designer to fully use the capabilities of the Pentium II processor and the Intel 440BX AGPset.

**Design Checklists** are items which provide recommendations for designing a Low-Power Module-based platform.

**Design Considerations** are items that should be considered but may not be applicable to your design.

#### 1.2 Overview

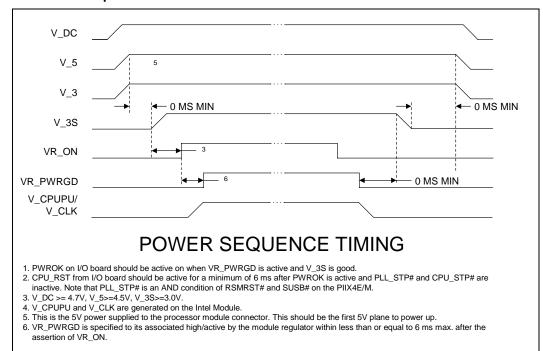

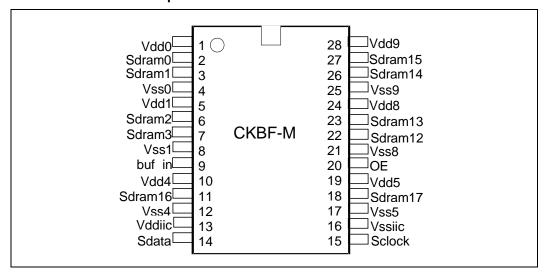

Low-Power Module features are summarized below. Figure 1 is a block diagram of a typical Low-Power Module system design.

- Full support for mobile Pentium II processors with system bus frequencies of 66 MHz

- L2 Cache Memory

- 512 Kbytes on board cache memory (266 MHz version)

- 256 Kbytes on-die cache memory (333 MHz version)

- Intel 440BX AGPset

- 82443BX Host Bridge/Controller (443BX)

- 82371EB PCI ISA IDE Accelerator (PIIX4E)

- 66 MHz memory interface: A wide range of DRAM support including:

- 64-bit memory data interface plus 8 ECC bits and hardware scrubbing

- 60 ns EDO DRAM and 66 MHz SDRAM support

- 16-Mbit and 64-Mbit DRAM technologies

- 5 PCI masters

- PCI Specification Rev 2.1 Compliant

- Accelerated Graphics Port (AGP) Slot:

- AGP Interface Specification Revision 1.0 compliant

- AGP 66/133 MHz, 3.3-V device support

- Integrated IDE controller with Ultra DMA/33 support

- PIO Mode 4 transfers

- PCI IDE bus master support

- Integrated Universal Serial Bus (USB) controller with two USB ports

- Integrated System Power Management support

Figure 1. Low-Power Module/440BX AGPset System Block Diagram

### 1.3 Related Documents

#### Table 1. Related Intel Documents

| Document                                                                                         | Order Number     |

|--------------------------------------------------------------------------------------------------|------------------|

| Intel® Pentium® II Processor – Low-Power Module datasheet                                        | 273256           |

| Intel® Pentium® II Processor with On-Die Cache – Low-Power Module datasheet                      | 273257           |

| Mobile Pentium <sup>®</sup> II Processor Specification Update                                    | 243887           |

| Intel® 440BX AGPset: 82443BX Host Bridge/Controller datasheet                                    | 290633           |

| Intel® 440BX AGPset: 82443BX Host Bridge/Controller Specification Update                         | 290639           |

| Intel® 82371AB PCI-to-ISA/IDE Xcelerator (PIIX4) datasheet                                       | 290562           |

| Intel® 82371EB PCI-to-ISA/IDE Xcelerator (PIIX4E) Specification Update                           | 290635           |

| PIIX4 Universal Serial Bus Design Guide                                                          | NDA <sup>†</sup> |

| Pentium <sup>®</sup> II Processor - Low Power Module Thermal Design Guide                        | 273216           |

| CK97 Clock Synthesizer Design Guidelines application note                                        | 243867           |

| Intel <sup>®</sup> Architecture Software Developer's Manual, Volume 1; Basic Architecture        | 243190           |

| Intel <sup>®</sup> Architecture Software Developer's Manual, Volume 2; Instruction Set Reference | 243191           |

| Intel® Architecture Software Developer's Manual, Volume 3; System Programming Guide              | 243192           |

| Intel <sup>®</sup> Architecture MMX™ Technology Developer's Guide                                | 243006           |

| AP-485 Intel Processor Identification and the CPUID Instruction application note                 | 241618           |

| AP-585 Pentium® II Processor GTL + Guidelines application note                                   | 243330           |

| AP-586 Pentium® II Processor Thermal Design Guidelines application note                          | 243331           |

| AP-587 Slot 1 Processor Power Distribution Guidelines application note                           | 243332           |

| AP-589 Slot 1 Processor EMI Overview application note                                            | 243334           |

<sup>†</sup> NDA documents are only available through an Intel Field Sales Representative.

### Table 2. Related Specifications

| Document                                                                                    | URL/Contact                                  |

|---------------------------------------------------------------------------------------------|----------------------------------------------|

| PCI Local Bus Specification, Revision 2.1                                                   | http://www.pcisig.com/specs.html             |

| Universal Serial Bus Specification, Revision 1.0                                            | http://www.usb.org/usb/developers/index.html |

| AGP Interface Specification, Revision 1.0                                                   | http://www.agpforum.org/index.htm            |

| AGP Platform Design Guide, Revision 1.1A                                                    | http://www.agpforum.org/index.htm            |

| Information Technology – AT Attachment with Packet Interface Extension (ATA/ATAPI-4)        | ftp://fission.dt.wdc.com/pub/standards/      |

| System Management Bus Specification                                                         | http://www.sbs-forum.org/                    |

| 66-MHz Unbuffered SDRAM 64-bit (Non-ECC/Parity) 144-pin SO-DIMM Specification, Revision 1.0 | Contact an Intel Field Sales Representative  |

### 2.0 Design Features

### 2.1 Pentium<sup>®</sup> II Processor – Low Power Module

The Intel<sup>®</sup> Pentium<sup>®</sup> II processor – Low Power Module is offered for applied computing platforms. It is available at 266 and 333 MHz with a processor side bus speed of 66 MHz. The 266 MHz Pentium II Processor – Low Power Module has an on-board 512 Kbyte L2 cache using a Tag RAM and two BSRAM devices. The 333 MHz Pentium II Processor with On-Die Cache – Low Power Module has 256 Kbytes of on-die L2 cache.

The processor consists of a Pentium II processor core with an integrated second-level cache controller and a 64-bit high-performance host bus. The Pentium II processor – Low Power has a private second-level cache bus that allows a high-performance 64-bit wide cache subsystem to be gluelessly implemented. The Pentium II processor – Low Power can cache up to 512 Mbytes of memory. The private second-level cache bus complements the host bus by providing critical data faster, improving performance, and reducing total system power consumption. The Pentium II processor – Low Power's 64-bit wide Low-power GTL+ host bus is compatible with the 440BX AGPset and provides a glueless, point-to-point interface for an I/O bridge and memory controller.

### 2.2 Intel<sup>®</sup> 440BX AGPset

The Intel® 440BX AGPset is based on the Pentium II processor architecture. It interfaces with the Pentium II processor's system bus at 66 MHz. Along with its Host-to-PCI bridge interface, the 82443BX Host Bridge/Controller has been optimized with a 66 MHz SDRAM memory controller and data path unit. The 82443BX also features the Accelerated Graphics Port (AGP) interface. The 82443BX component includes the following functions and capabilities:

- 64-bit Low Power GTL+ based system data bus interface

- 32-bit system address bus support

- 64/72-bit main memory interface with optimized support for SDRAM

- 32-bit PCI bus interface with integrated PCI arbiter

- AGP interface with up to 133 MHz data transfer capability

- Extensive data buffering between all interfaces for high throughput and concurrent operations

Figure 1 shows a block diagram of a typical platform based on the 440BX AGPset. The 82443BX system bus interface supports a Pentium II processor at a bus frequency of 66 MHz. The physical interface design is based on the Low Power GTL+ specification and is compatible with the Intel 440BX AGPset. The 440BX provides an optimized 72-bit DRAM interface (64-bit Data plus ECC). This interface supports 3.3-V DRAM technologies.

The 82443BX is designed to support the PIIX4E I/O bridge. The PIIX4E is a highly-integrated multifunctional component that supports the following functions and capabilities:

- PCI Revision 2.1 compliant PCI-to-ISA bridge with support for 33 MHz PCI operations

- ACPI Power Management support

- Enhanced DMA controller, interrupt controller and timer functions

- Integrated IDE controller with Ultra DMA/33 support

### Pentium® II Processor - Low-Power Module Design Guide

- USB host interface with support for two USB ports

- System Management Bus (SMB) with support for DIMM Serial Presence Detect

### 2.2.1 System Bus Interface

The 82443BX supports a maximum of 4 Gbytes of memory address space from the processor perspective. The largest address size is 32 bits. The 82443BX provides bus control signals and address paths for transfers between the processor bus, PCI bus, Accelerated Graphics Port and main memory. The 82443BX supports a 4-deep-in-order queue, which provides support for pipelining of up to four outstanding transaction requests on the system bus. The Pentium II processor supports a second-level cache; all cache-control logic is provided on the processor.

For system bus-to-PCI transfers, the addresses are either translated or directly forwarded on the PCI bus, depending on the PCI address space being accessed. When the access is to a PCI configuration space, the processor I/O cycle is mapped to a PCI configuration space cycle. When the access is to a PCI I/O or memory space, the processor address is passed without modification to the PCI bus. Certain memory address ranges are dedicated for a graphics memory address space. When this space or a portion of it is mapped to main DRAM, the address is translated by the AGP address remapping mechanism and the request is forwarded to the DRAM subsystem. A portion of the graphics aperture can be mapped on the AGP, and the corresponding system bus cycles accessing that range are forwarded to the AGP without any translation. The AGP address map defines other system bus cycles that are forwarded to the AGP.

#### 2.2.2 DRAM Interface

The 82443BX integrates a main memory controller that supports a 64/72-bit DRAM interface which operates at 66 MHz. The integrated DRAM controller features include:

- 3.3-V interface

- Support for up to three double-sided SODIMMs

- 8 Mbytes to 48 Mbytes using 16-Mbit technology

- 192 Mbytes using 64-Mbit technology

- 384 Mbytes using 128-Mbit technology

- Support for ECC with hardware scrubbing

### 2.2.3 Accelerated Graphics Port Interface

The 82443BX supports an AGP interface. The AGP interface has a maximum theoretical transfer rate of  $\sim 532$  Mbytes/s.

#### 2.2.4 PCI Interface

The 82443BX PCI interface operates at 33 MHz, is Revision 2.1 compliant, and supports up to five external PCI bus masters in addition to the PIIX4E I/O bridge. The PCI interface is only 3.3 V. If the developer requires a 5-V interface, a level shifter implementation is recommended.

#### 2.2.5 System Clocking

The 82443BX operates the system bus interface at 66 MHz, the PCI bus at 33 MHz and the AGP at a transfer rate of 66/133 MHz. The 82443BX clocking scheme uses an external clock synthesizer that produces reference clocks for the system bus and PCI interfaces. The 82443BX generates the AGP and DRAM clock signals. Please refer to the *CK97 Clock Synthesizer/Driver Specification* (order number 243867).

### 2.3 PCI ISA IDE Xcelerator (PIIX4E)

The PCI ISA IDE Xcelerator (PIIX4E) is a multi-function PCI device that implements a PCI-to-ISA bridge function, a PCI IDE function, a Universal Serial Bus host/hub function, and an Enhanced Power Management function. Because it is a PCI-to-ISA bridge, the PIIX4E integrates many common I/O functions found in ISA-based PC systems; a seven channel DMA Controller, two 82C59 Interrupt Controllers, an 8254 Timer/Counter, and a Real Time Clock. In addition to DMA Compatible transfers, each DMA channel also supports Type F transfers.

The PIIX4E contains full support for PC/PCI and Distributed DMA protocols that implement PCI-based DMA. The Interrupt Controller has edge or level sensitive programmable inputs. Chip select decoding is provided for a BIOS, Real Time Clock, Keyboard Controller, second external microcontroller, and two Programmable Chip Selects. The PIIX4E provides full Plug-and-Play compatibility. The PIIX4E can be configured as a subtractive decode bridge or as a positive decode bridge.

The PIIX4E supports two IDE connectors. This provides an interface for IDE/EIDE hard disks and CD-ROMs. Up to four IDE devices can be supported in Bus Master mode. The PIIX4E contains support for Ultra DMA/33 compatible synchronous DMA devices.

The PIIX4E contains a Universal Serial Bus (USB) host controller that is Universal Host Controller Interface (UHCI) compatible. The host controller's root hub has two programmable USB ports.

The PIIX4E supports Enhanced Power Management, including full clock control, device management for up to 14 devices, and suspend and resume logic with Power On Suspend, Suspend to RAM, or Suspend to Disk. The PIIX4E fully supports operating-system-directed power management according to the Advanced Configuration and Power Interface (ACPI) specification. The PIIX4E integrates both a System Management bus (SMBus) host and slave interface for serial communication with other devices.

For more information on the PIIX4E, please refer to the *82371AB PCI-to-ISA/IDE Xcelerator* (*PIIX4*) datasheet (order number 290562) and the *82371EB PCI-to-ISA/IDE Xcelerator* (PIIX4E) Specification Update (order number 290635).

### 3.0 Memory Guidelines

This section lists guidelines to be followed when routing the signal traces for the board design. The order in which signals are routed first and last will vary from designer to designer. Some designers prefer routing the clock signals first, while others prefer routing the high-speed bus signals first. Either order can be used, as long as the guidelines listed here are followed. When the guidelines listed here are not followed, it is very important to simulate the design. Even when the guidelines are followed, it is recommended that you simulate these signals for proper signal integrity, flight time and cross talk.

#### 3.1 DRAM Interface Overview

The 82443BX integrates a main memory DRAM controller that supports a 64-bit DRAM array for embedded environments. The DRAM types supported are Synchronous (SDRAM) and Extended Data Out (EDO). The 82443BX does not support a mixture of SDRAM and EDO memory. The 82443BX DRAM interface runs at 66 MHz. The DRAM controller interface is fully configurable through a set of control registers. Complete descriptions of these registers are given in the *Intel*® 440BX AGPset: 82443BX Host Bridge/Controller datasheet.

The 443BX supports industry standard 64-bit wide 144-pin SODIMM modules with SDRAM or EDO DRAM devices. Both symmetric and asymmetric addressing is supported. For write operations of less than a Qword in size, the 443BX will either perform a byte-wide write cycle (non-ECC protected configuration) or a read-modify-write cycle by merging the write data on a byte basis with the previously read data. The 82443BX requires 60 ns EDO DRAMs or SDRAM with CAS latency of 2 (CL2), and supports 1-and 2-row SODIMMs. The 82443BX provides refresh functionality with programmable rates (normal DRAM rate is 1 refresh/15.6 µs). When using SDRAM the 82443BX can be configured via the paging policy register to keep multiple pages open within the memory array. Pages can be kept open in all rows of memory. When using two bank SDRAM devices in a particular row, up to two pages can be kept open within that row.

The DRAM interface of the 82443BX is configured by the DRAM control registers, DRAM timing register, SDRAM control register, bits in the NBXCFG register and the eight DRAM row boundary (DRB) registers. The DRAM configuration registers control the DRAM interface to select EDO or SDRAM, RAS timing, and CAS rates. The eight DRB registers define the size of each row in the memory array, enabling the 82443BX to assert the proper CSA[7:0]#, CSB[7:0]# pair for accesses to the array.

#### 3.1.1 SDRAM Signal Description

The following sections explain which signals are used in applied computing platforms, and how they should be connected. Note that MAB[13,10] are not inverted because these address bits are used to define various SDRAM commands. Also note that MECC[7:0] should be left unconnected, because the Pentium II Processor - Low Power does not support ECC.

Table 3 identifies the SDRAM signals and the corresponding description.

Table 3. SDRAM Signal Descriptions

| Name                                                                     | Туре        | Voltage | Description                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MECC[7:0] <sup>1</sup>                                                   | I/O<br>CMOS | V_3     | Memory ECC Data: These signals carry Memory ECC data during access to DRAM. These pins are implemented by design (NOT TESTED) on the module.                                                                                                                                                                                                                                        |

| CSA[5:0]#                                                                | O<br>CMOS   | V_3     | Chip Select (SDRAM): These pins activate SDRAM. SDRAM accepts any command when its CS# pin is active low.                                                                                                                                                                                                                                                                           |

| DQMA[7:0]                                                                | O<br>CMOS   | V_3     | Input/Output Data Mask (SDRAM): These pins act as synchronized output enables during a read cycle and as a byte mask during a write cycle.                                                                                                                                                                                                                                          |

| MAB[9:0]#<br>MAB[10] <sup>2</sup><br>MAB[12:11]#<br>MAB[13] <sup>1</sup> | O<br>CMOS   | V_3     | Memory Address (SDRAM): This is the row and column address for DRAM. The 443BX Host Bridge system controller has two identical sets of address lines (MAA and MAB#). The Pentium II Processor - Low Power Module supports only the MAB set of address lines. For additional addressing features, please refer to the Intel® 440BX AGPset: 82443BX Host Bridge/Controller Datasheet. |

| MWEA#                                                                    | O<br>CMOS   | V_3     | <b>Memory Write Enable (SDRAM):</b> MWEA# should be used as the write enable for the memory data bus.                                                                                                                                                                                                                                                                               |

| SRASA#                                                                   | O<br>CMOS   | V_3     | SDRAM Row Address Strobe (SDRAM): When active low, this signal latches Row Address on the positive edge of the clock. This signal also allows Row access and pre-charge.                                                                                                                                                                                                            |

| SCASA#                                                                   | O<br>CMOS   | V_3     | SDRAM Column Address Strobe (SDRAM): When active low, this signal latches Column Address on the positive edge of the clock. This signal also allows Column access.                                                                                                                                                                                                                  |

| CKE[5:0]                                                                 | O<br>CMOS   | V_3     | SDRAM Clock Enable (SDRAM): The SDRAM clock enable pin. When these signals are deasserted, SDRAM enters power-down mode. Each row is individually controlled by its own clock enable.                                                                                                                                                                                               |

| MD[63:0]                                                                 | I/O<br>CMOS | V_3     | <b>Memory Data:</b> These signals are connected to the DRAM data bus. They are not terminated on the module.                                                                                                                                                                                                                                                                        |

#### NOTES:

### 3.1.2 SDRAM Signal Connectivity

The DRAM expansion socket is a 144-pin SO-DIMM. Table 4 identifies the SDRAM signals and the corresponding SO-DIMM pins. Table 5 identifies the module SDRAM signals and the corresponding onboard SDRAM signals.

Table 4. SDRAM Signals and Corresponding SO-DIMM Pins

| Signal Name | SO-DIMM Pin |

|-------------|-------------|

| MAB[11]#    | 106         |

| MAB[12]#    | 70, 110     |

| MAB[13]#    | 72, 112     |

MECC[7:0] signals should be left unconnected, because the Pentium II Processor - Low Power does not support ECC.

MAB[13,10] signals are not inverted because these address bits are used to define various SDRAM commands.

#### Table 5. Module SDRAM Signals and Corresponding Onboard SDRAM Signals

| Signal Name | SDRAM Component Pin |

|-------------|---------------------|

| MAB[11]#    | A13/BA0             |

| MAB[12]#    | A12/BA1             |

| MAB[13]#    | A11                 |

#### 3.1.3 Pin Groups

The 82443BX has multiple copies of many of the signals interfacing to memory. However, the Low-Power Module/440BX AGPset only supports a single copy of the memory signals. See "Single Set DRAM Interface" on page 18 for more information. The interface consists of the following pins:

#### Multiple copies:

MAA[13:0], MAB[12:11,9:0]# and MAB[13, 10] CSA[7:0]#, CSB[7:0]# SRASA#, SRASB# SCASA#, SCASB# WEA#, WEB# DQMA[7:0], DQMB[5:1]

#### Single copies:

CKE[5:0] (for three SODIMM configuration)

MD[63:0]

MECC[7:0]

GCKE (for four DIMM configuration)

FENA (FET switch control for four DIMM configuration)

The CSA[7:0]#, CSB[7:0]# pins function as RAS# pins in the case of EDO DRAMs. The DQM pins function as CAS# pins in the case of EDO DRAMs. Two CS# lines are provided per row. These are functionally equivalent. The extra copy is provided for loading reasons. The two SRAS#, SCAS# and WE# pins are also functionally equivalent and each copy drives two rows of DRAM. Most pins use programmable strength output buffers. When a row contains 16-Mbit SDRAMs, MAA11 and MAB11# function as Bank Select lines. When a row contains 64-Mbit SDRAMs, MAA[12:0], MAB[12:11] function as Bank Addresses (BA[1:0], or Bank Selects).

#### 3.1.4 Single Set DRAM Interface

The following two sections explain which signals are used in embedded platforms. Note that MAB[13,10] are not active low because these address bits are used to define various SDRAM commands.

#### 3.1.4.1 EDO DRAM

Single copies used:

MAB[12:11,9:0]# and MAB[13,10] MD[63:0] MECC[7:0] RASA[5:0]# CASA[7:0]# WEA#

#### 3.1.4.2 SDRAM

Single copies used:

MAB[12:11,9:0]# and MAB[13,10] MD[63:0] MECC[7:0] CSA[5:0]# DQMA[7:0] CKE[5:0] SRASA# SCASA# WEA#

### 3.2 DRAM Layout Guidelines

*Note:* The following DRAM layout guidelines are intended for use with the Low-Power Module platforms that will use *only* 66 MHz Host/SDRAM clock frequencies.

- The DRAM expansion socket for embedded applications is the 144-pin SODIMM.

- MAB[11]# should be connected to pin 106 of the SODIMM connector.

- MAB[12]# should be connected to pin 70 and pin 110 of the SODIMM connector.

- MAB[13] should be connected to pin 72 and pin 112 of the SODIMM connector.

- For onboard 64-Mbit SDRAM devices on the motherboard, MAB[11]# should be connected to A13/BA0 on the SDRAM device, and MAB[13] should be connected to A11 on the SDRAM device.

- The memory data bit traces may be byte-swapped to simplify board routing and minimize trace lengths. This should also be done for the data bits within the byte channel.

- Board impedance should be 55  $\Omega \pm 15\%$ .

- All resistors should be within 5% tolerance.

- Trace widths for memory signals should be 5 mil.

- Populate the furthest SODIMM first to avoid stub reflections.

- Any onboard memory should be put further away from the Low-Power Module than the SODIMM connectors.

- Place the on board DRAM connector, SODIMM connector, and Low-Power Module connector as near to each other as possible.

#### 3.2.1 SODIMM Connection - EDO DRAMs

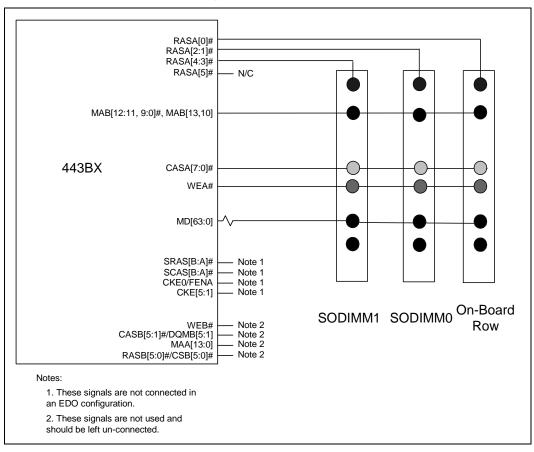

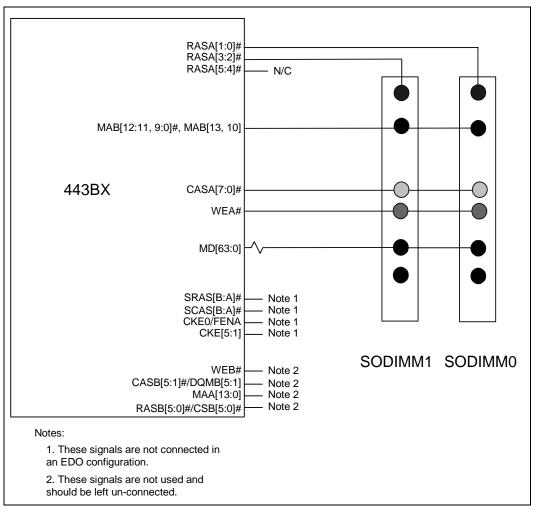

Figures 2 and 3 show how to route the Low-Power Module/440BX DRAM interface to EDO DRAM.

Figure 2. EDO DRAM - One On-board Bank, Two SODIMMs

Figure 3. EDO DRAM - Two SODIMMs

### 3.2.2 SODIMM Connection - SDRAM

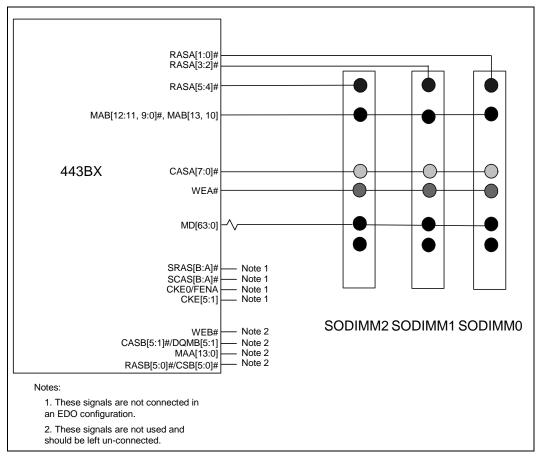

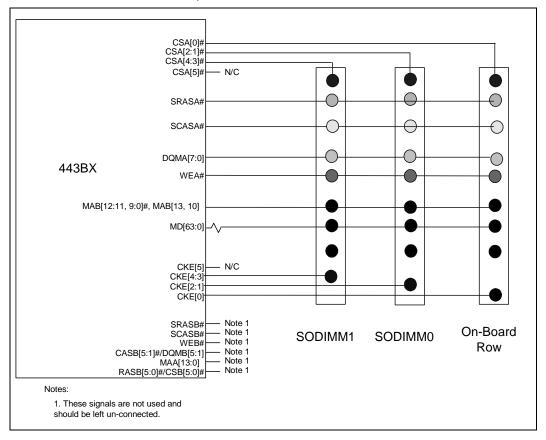

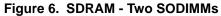

Figures 5 and 6 show how to route the Low-Power Module/440BX DRAM interface to SDRAM.

Figure 5. SDRAM - One On-board Bank, Two SODIMMs

Figure 7. SDRAM - Three SODIMMs

### 3.2.3 Memory Trace Lengths for Module Design

**Note:** The following DRAM layout guidelines are intended for use with the Low-Power Module platforms that use *only* 66 MHz Host/SDRAM clock frequencies.

Table 6 provides the minimum and maximum trace lengths to the SODIMM connector for each signal group (excluding clock) for each design. For the trace lengths of clocks, see "Clocking Guidelines" on page 27.

For memory configurations with on-board memory devices, signal traces should be routed as if there were a "phantom" connector on the board. The designer should follow the routing guidelines from the 66MHz Unbuffered SDRAM 64-bit (Non-ECC/Parity) 144-pin SO-DIMM Specification, Revision 1.0, for the memory signals from the "phantom" connector to the on-board memory devices (refer to Table 2 on page 11). In other words, route the memory channel from the 82443BX to the position that SODIMM0 would occupy in your design following the given constraints, and route from that point onward according to the 66MHz Unbuffered SDRAM 64-bit (Non-ECC/Parity) 144-pin SO-DIMM Specification.

| Signal                              | Min.<br>Length | Max. Length |          | Resistor<br>(on System Electronics Board) |

|-------------------------------------|----------------|-------------|----------|-------------------------------------------|

| MAB[13:0]x, WEA#,<br>SRASA#, SCASA# | 0 inch         | 8.0 inch    | 203.2 mm | NONE                                      |

| CKE[5:0]                            | 0 inch         | 9.0 inch    | 228.6 mm | NONE                                      |

| CSA/RASA[5:0]#                      | 0 inch         | 9.0 inch    | 228.6 mm | NONE                                      |

| CASA[7:0]#/DQMA[7:0]#               | 0 inch         | 9.0 inch    | 228.6 mm | NONE                                      |

| MD[63:0], MECC[7:0]                 | 0 inch         | 8.0 inch    | 203.2 mm | 18 Ω ± 5%                                 |

### 3.3 SODIMM DRAM Organization

The 144-pin SODIMM (1" height) has a maximum capacity of eight devices and provides the following configuration possibilities (see Table 7) for SDRAM or EDO.

Table 7. SODIMM DRAM Organization

| Technology | SODIMM<br>Organization | Component<br>Organization | Devices<br>per Row | Mbyte per<br>SODIMM |

|------------|------------------------|---------------------------|--------------------|---------------------|

| 16 Mbit    | 1 M x 64 / S           | 1 M x 16                  | 4                  | 8 Mbyte             |

|            | 2 M x 64 / D           | 1 M x 16                  | 4                  | 16 Mbyte            |

|            | 2 M x 64 / S           | 2 M x 8                   | 8                  | 16 Mbyte            |

| 64 Mbit    | 2 M x 64 / S           | 2 M x 32                  | 2                  | 16 Mbyte            |

|            | 4 M x 64 / D           | 2 M x 32                  | 2                  | 32 Mbyte            |

|            | 4 M x 64 / S           | 4 M x 16                  | 4                  | 32 Mbyte            |

|            | 8 M x 64 / D           | 4 M x 16                  | 4                  | 64 Mbyte            |

|            | 8 M x 64 / S           | 8 M x 8                   | 8                  | 64 Mbyte            |

| 128 Mbit   | 16 M x 64 /S           | 8 M x 16                  | 4                  | 128 Mbyte           |

NOTE: "S" denotes single-sided SODIMMs. "D" denotes double-sided SODIMMs.

### 3.3.1 64-Mbit SDRAM System Examples

Table 8 lists five system examples. Each example is based on using three SODIMM sockets or one on-board DRAM and two SODIMM sockets. The terms used in Table 8 are defined below:

144 SODIMM: Number of SODIMM sockets plus on-board DRAM

Row: RAS[5:0]# or CS[5:0]# connection. Technology: DRAM technology 16 Mbit, 64 Mbit

Density/Width: DRAM configuration 16 Mbit: 2 M x 8, or 1 M x 16

64 Mbit: 8 M x 8, 4 M x16, or 2 M x 32

128 Mbit: 8 M x 16, or 16 M x 8

# Devices/Row: Number of DRAM components per row.

Table 8. System Examples for Supporting 64-Mbit SDRAM

| 144<br>SODIMM   | Row | Technology           | Density x Width      | # Devices/Row | Mbytes per<br>SODIMM   |

|-----------------|-----|----------------------|----------------------|---------------|------------------------|

|                 | 1   | Exa                  | imple #1             |               |                        |

| #1 or on-board  | 0   | 16 Mbit              | 2 M x 8              | 8             | 16 Mbytes              |

| #2              | 1   | 16 Mbit              | 1 M x 16             | 4             | 8 Mbytes               |

| #2              | 2   | 16 Mbit              | 1 M x 16             | 4             | 8 Mbytes               |

| #3              | 3   | 16 Mbit              | 2 M x 8              | 8             | 16 Mbytes              |

| Total           | 4   |                      |                      | 24            | 48 Mbytes              |

|                 |     | Exa                  | imple #2             |               |                        |

| #1 or on-board  | 0   | 16 Mbit              | 2 M x 8              | 8             | 16 Mbytes              |

| #2              | 1   | 16 Mbit              | 2 M x 8              | 8             | 16 Mbytes              |

| #3              | 2   | 16 Mbit              | 2 M x 8              | 8             | 16 Mbytes              |

| Total           | 3   |                      |                      | 24            | 48 Mbytes              |

|                 |     | Exa                  | imple #3             |               |                        |

| #1 or on-board  | 0   | 16 Mbit              | 2 M x 8              | 8             | 16 Mbytes              |

| #2              | 1   | 64 Mbit              | 8 M x 8              | 8             | 64 Mbytes              |

| #3              | 2   | 64 Mbit              | 4 M x 16             | 4             | 32 Mbytes              |

| Total           | 3   |                      |                      | 20            | 112 Mbytes             |

|                 |     | Exa                  | imple #4             |               |                        |

| #1 or on-board  | 0   | 64 Mbit              | 8 M x 8              | 8             | 64 Mbytes              |

| #2              | 1   | 64 Mbit              | 8 M x 8              | 8             | 64 Mbytes              |

| #3              | 2   | 64 Mbit              | 8 M x 8              | 8             | 64 Mbytes              |

| Total           | 3   |                      |                      | 24            | 192 Mbytes             |

|                 | l   | Exa                  | imple #5             |               |                        |

| #1 or on-board  | 0   | 128 Mbit             | 8 M x 16             | 4             | 64 Mbytes              |

| #1 01 011-b0a10 | 1   | 128 Mbit             | 8 M x 16             | 4             | 64 Mbytes              |

| #2              | 2 3 | 128 Mbit             | 8 M x 16<br>8 M x 16 | 4<br>4        | 64 Mbytes              |

|                 | 4   | 128 Mbit<br>128 Mbit | 8 M x 16             | 4             | 64 Mbytes              |

| #3              | 5   | 128 Mbit             | 8 M x 16<br>8 M x 16 | 4             | 64 Mbytes<br>64 Mbytes |

| Total           | 6   |                      |                      | 24            | 384 Mbytes             |

### 4.0 Clocking Guidelines

This section lists guidelines to be followed when routing the signal traces for the board design. The order in which signals are routed will vary from designer to designer. Some designers prefer routing all of the clock signals first, while others prefer routing the high-speed bus signals first. Either order can be used, as long as the guidelines listed here are followed. When the guidelines listed here are not followed, it is very important to simulate the design. Even when the guidelines are followed, it is recommended that you simulate signals for proper signal integrity, flight time and cross talk.

### 4.1 Clocking System Overview

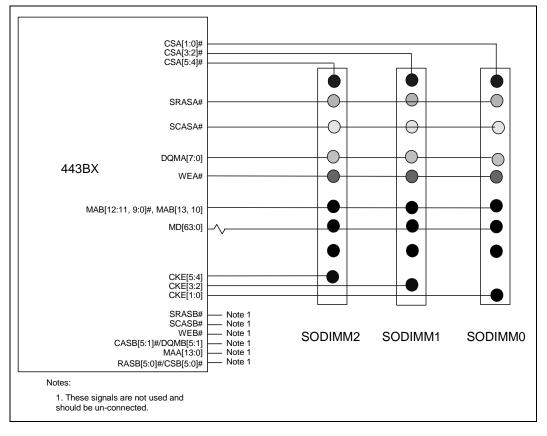

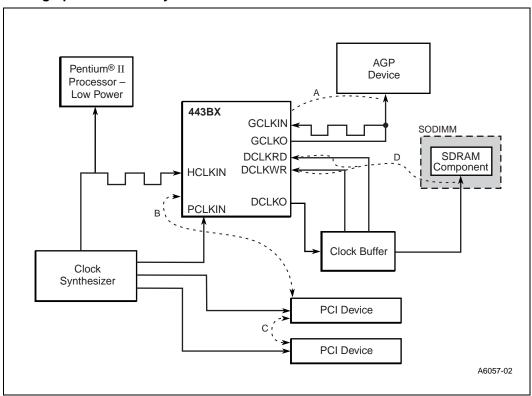

This section provides guidelines and application information for clock layout in a Low-Power Module/440BX AGPset system. These guidelines are based on the HCLK, PCICLK and SDRAMCLK requirements and should be implemented along with the application instructions supplied by your clock chip vendor. Figure 8 shows the clock synthesizer connection to the processor, 443BX, and SDRAM when using a Low-Power Module.

Figure 8. Clock Connections to the Low-Power Module

### 4.2 Clock Synthesizer Pinout and Specifications

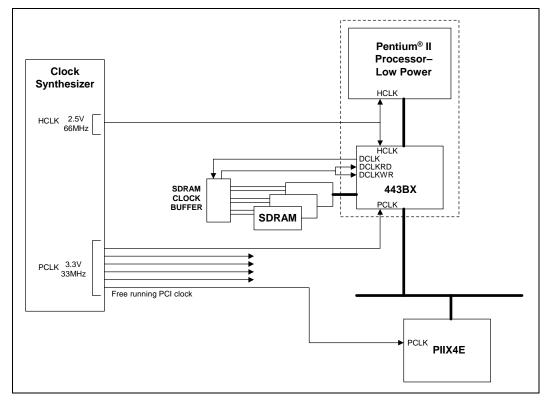

A clock synthesizer that meets the *CK97 Clock Synthesizer Design Guidelines* (order number 243867) will meet the requirement for a Low-Power Module/440BX AGPset-based system. Table 11 on page 32 lists clock vendors that provide clock synthesizers which meet the *CK97 Clock Synthesizer Design Guidelines*.

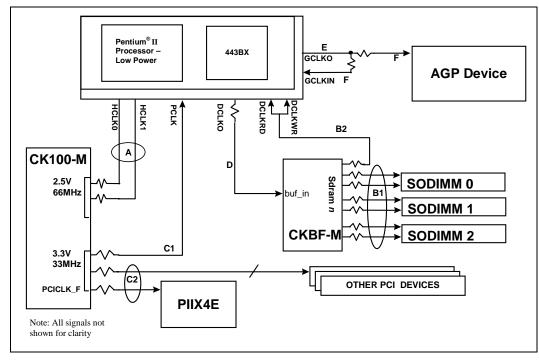

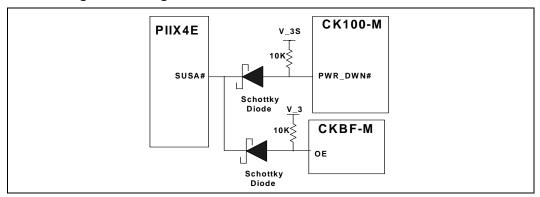

**Note:** The CK100-M compatible clock synthesizer operates in multi-voltage mode. The processor clocks operate at 66 MHz at 2.5 V, and the PCI clocks operate at 33 MHz at 3.3 V. The CKBF-M compatible clock buffer provides clocks for SDRAM operating at 66 MHz at 3.3 V.

Figure 9. Pinout for CK100-M Compatible Clock Synthesizer

Figure 10. Pinout for CKBF-M Compatible Clock Buffer

### 4.3 Timing Guidelines

Trace lengths should be matched within clock signal groups to minimize skew between copies of the clocks. This applies to the HCLK-to-HCLK and the PCICLK-to-PCICLK clock trace lengths.

Figure 11. Timing Specifications Layout

Figure 11 shows a simplified clocking layout for the timing specifications. The recommended trace lengths are given in the Note on page 30. See Table 9 for the clock skews.

Table 9. Timing Specifications for Maximum and Minimum Clock Skews

| Symbol | Description                                           | CK100-M<br>Pin-to-Pin | Boards                         | Total                          |

|--------|-------------------------------------------------------|-----------------------|--------------------------------|--------------------------------|

| Α      | A AGP device (GCLK) to 440BX AGPset (GCLKIN) skew N/A |                       | 100 ps (max)<br>- 100 ps (min) | 100 ps (max)<br>- 100 ps (min) |

| В      | 440BX AGPset (HCLK) to                                | 4.0 ns (max.) 1       | 1.0 ns (max.)                  | 5.0 ns (max.)                  |

|        | PCI (PCLK) skew                                       | 1.5 ns (min.)         | 0 ns (min.)                    | 1.5 ns (min.)                  |

| С      | PCI (PCLK) to                                         | 500 ps (max)          | 1.5 ns (max)                   | 2.0 ns (max)                   |

|        | PCI (PCLK) skew                                       | - 500 ps (min)        | -1.5 ns (min)                  | - 2.0 ns (min)                 |

| D      | DCLKWR to                                             | 250 ps (max)          | 380 ps (max) 2                 | 630 ps (max)                   |

|        | SDRAM (SCLK) skew                                     | -250 ps (min)         | - 380 ps (min) 2               | - 630 ps (min)                 |

#### NOTES

- The 82443BX PCICLK input should lag its HCLK input by a minimum of 1.5 ns to a maximum of 4.0 ns at the pins of the CK100-M device. An integrated buffer offers the best control over these output-to-output drive skews.

- 4. This skew allowance includes ±280 ps for I/O capacitance and SODIMM routing variation. Motherboards should allow for no more than ±100 ps contribution to the total skew.

**Note:** Clock period, jitter, offset and skew are measured on the rising edge of the clock signals at 1.25 V for the 2.5-V clocks and at 1.5 V for the 3.3-V clocks.

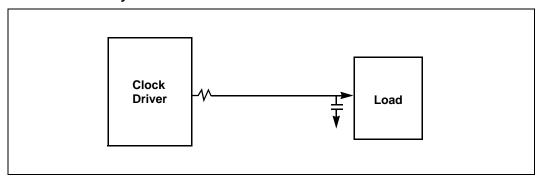

### 4.4 Clock Layout Guidelines

- Series matching resistors are required.

- Resistor Value: See Table 10.

- Placement: As near as possible to the driver pin (less than 1")

- A PCLK that is used for a PCI socket should be a point-to-point connection and should not be shared with another load.

- When designing with an expansion connector, remember to account for the PCICLK trace length in the docking station.

- Route all clocks on internal layers to provide better trace delay consistency and EMI containment.

- Board impedance should be 55  $\Omega \pm 15\%$ .

- Use discrete resistors on HCLK signals coming from CK100-M.

- Minimize the use of vias in clock signals.

- All clocks should have 1:2 width-to-spacing ratio.

- CKBF-M should be on the V\_3 rail and CK100-M should be on the V\_3S rail (see "Power and Ground Pins" on page 36 for a description of these rails).

Figure 12. Low-Power Module Clocking Layout

**Table 10. Low-Power Module Clocking Trace Layout Specifications**

| Variable                       | Trace<br>Width | Minimum Trace<br>Length                               | Maximum Trace<br>Length                             | Tolerance<br>(Note 1)     | Resistor<br>Value |

|--------------------------------|----------------|-------------------------------------------------------|-----------------------------------------------------|---------------------------|-------------------|

| A<br>(Notes 3)                 | 10 mil         | 0 inch<br>(0 mm)                                      | 4.0 inch<br>(101.6 mm)                              | ± 0.1 inch<br>(± 2.54 mm) | 18 Ω ± 5%         |

| B <sub>1</sub><br>(Notes 2, 3) | 5 mil          | 0 inch<br>(0 mm)                                      | 4.0 inch<br>(101.6 mm)                              | ± 0.1 inch<br>(± 2.54 mm) | 18 Ω ± 5%         |

| B <sub>2</sub>                 | 5 mil          | B <sub>1</sub> +2.4 inch<br>(B <sub>1</sub> +60.9 mm) | B <sub>1</sub> +2.6 inch<br>(B <sub>1</sub> +66 mm) |                           | 18 Ω ± 5%         |

| C <sub>1</sub>                 | 5 mil          | А                                                     | A+4 inch<br>(A+101.6 mm)                            |                           | $33~\Omega\pm5\%$ |

| C <sub>2</sub>                 | 5 mil          | C <sub>1</sub>                                        | C <sub>1</sub>                                      | ± 4.5 inch<br>(± 114.3mm) | $33~\Omega\pm5\%$ |

| D                              | 5 mil          | 0 inch<br>(0 mm)                                      | 4.0 inch<br>(101.6 mm)                              |                           | 18 Ω ± 5%         |

| E                              | 10 mil         | 0 inch<br>(0 mm)                                      | 1 inch<br>(25.4 mm)                                 |                           | None              |

| F                              | 5 mil          | 0 inch<br>(0 mm)                                      | 8.5 inch<br>(215.9 mm)                              |                           | 18 Ω ± 5%         |

#### NOTES:

- 1. "Tolerance" refers to the allowed difference in length between multiple traces sharing the same variable name.

- 2. For platforms with on-board memory devices, clock traces should be routed as if there were a "phantom" connector on the board. The designer should follow the routing guidelines in the 66 MHz Unbuffered SDRAM 64-bit Non-ECC/Parity 144-pin SODIMM Specification for the clock signals from the "phantom" connector to the on-board memory devices. In other words, route the clock trace to the position that SODIMM0 would occupy following the constraints given above, and route from that point onward according to the 66 MHz Unbuffered SDRAM 64-bit Non-ECC/Parity 144-pin SODIMM Specification.

- 3. These layout guidelines are intended only for platforms in which the Host/SDRAM clocks run at 66 MHz.

### 4.5 Optional Clock Layout

Figure 13. General Clock Layout

This optional layout implementation is suggested to accommodate clock tuning, HCLK & PCICLK from CK100-M and SCLK from CKBF-M. This will allow the designer to tune the individual clock signals to minimize EMI and allow for variations in impedance, skew and loading.

The variables to be considered include:

- · Variation in actual device load

- Line and load impedance variation

- Driver output impedance

- · Vendor variation

The stub to the capacitor must be minimized. The maximum stub length on a clock trace is < 0.5 inch. The capacitor should be placed as close as possible to the load. Refer to the specific clock vendors for layout and termination guidelines.

#### 4.6 Clock Vendors

This vendor list is provided as a service to our customers for reference only. The inclusion of this list should not be considered a recommendation or product endorsement by Intel Corporation.

Table 11. Clock Vendors

| Vendor Name                       | Address                                                                                      |  |

|-----------------------------------|----------------------------------------------------------------------------------------------|--|

| International Microcircuits, Inc. | 525 Los Coches Street<br>Milpitas, CA 95035<br>(408) 263-6300<br>http://www.imicorp.com      |  |

| Integrated Circuit Systems, Inc.  | 1271 Parkmoor Avenue<br>San Jose, CA 95126-3448<br>(408) 925-9493<br>http://www.icst.com     |  |

| Cypress Semiconductor             | 12020 113th Ave. Northeast<br>Kirkland, WA 98034<br>(425) 398-3400<br>http://www.cypress.com |  |

# 5.0 82443BX AGP Interface for Low-Power Module Design

This section lists guidelines to be followed when routing the signal traces for the board design. Even when the guidelines are followed, it is recommended that you simulate as many signals as possible for proper signal integrity and cross talk. See Section 6.2.10, "AGP Signals" on page 42 for AGP pull-up requirements. See Section 4.0, "Clocking Guidelines" on page 27 for AGP clocking information.

### 5.1 Layout and Routing Guidelines

For the definition of AGP interface functionality (protocols, rules and signaling mechanisms, and the platform level aspects of AGP functionality), refer to the latest *AGP Interface Specification* and *AGP Platform Design Guide*. This document focuses only on specific 440BX platform recommendations for the AGP interface.

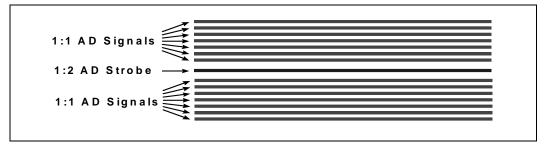

Throughout this section the term "data" refers to G\_AD[31:0], G\_C/BE[3:0]# and SBA[7:0]. The term "strobe" refers to AD\_STB[B:A] and SB\_STB. When the term "data" is used, it is referring to one of three groups of data as seen in Table 12. When the term "strobe" is used it is referring to one of the three strobes as it relates to the data in its associated group.

Table 12. Data and Associated Strobe

| Data                         | Associated Strobe |  |

|------------------------------|-------------------|--|

| G_AD[15:0] and G_C/BE[1:0]#  | AD_STBA           |  |

| G_AD[31:16] and G_C/BE[3:2]# | AD_STBB           |  |

| SBA[7:0]                     | SB_STB            |  |

#### 5.1.1 On-board AGP Compliant Device Layout Guidelines

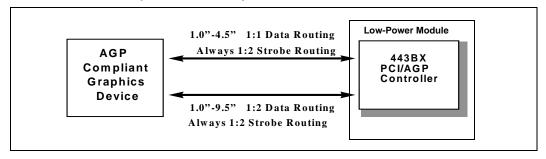

Longer trace lengths require a greater amount of spacing between traces in order to reduce crosstalk. When using 1:2 spacing, maximum trace length of data lines is 9.5 inches. The line length mismatch is 0.5 inches. The strobe is the longest trace of the group. This restricts the maximum trace length of data lines to less than 4.5 inches for a 1:1 trace spacing. The strobe requires a 1:2 trace spacing. Trace length guidelines given in this section do not reflect signal integrity and EMI. It is recommended that you simulate the routes to ensure that signal quality requirements are met.

Figure 14. On-board AGP Compliant Device Layout Guidelines

Figure 15. Signal Layout Recommendations

#### 5.1.1.1 Data and Strobe Signal Routing Recommendations

**Table 13. Motherboard Recommendations**

| Width:Space           | Trace        | Line Length                   | Line Length Matching         |

|-----------------------|--------------|-------------------------------|------------------------------|

| 1:1(Data)/1:2(Strobe) | Data /Strobe | 1.0 in < line length < 4.5 in | 0.5 in, strobe longest trace |

| 1:2                   | Data/Strobe  | 1.0 in < line length < 9.5 in | 0.5 in, strobe longest trace |

The line length mismatch must be less than 0.5" and the strobe must be the longest signal of the group. For example, if the strobe is at 4.0 inches, the data line can be from 3.5 to 4.0 inches in length. It is best to reduce the line length mismatch wherever possible to ensure added margin. The strobe is always required to have 1:2 trace spacing. It is also best to separate the traces by as much as possible in order to reduce the amount of trace-to-trace coupling.

**Note:** Under certain layouts, crosstalk and ground bounce can be observed on the AD\_STB signals of the AGP interface. Although Intel has not observed system failures due to this issue, noise margin has been improved by enhancing the AGP buffers on the 82443BX. For new designs, additional margin can be obtained by following AGP layout guidelines.

### 5.1.1.2 Control Signal Routing Recommendations

Some of the control signals require pull-up resistors to be installed on the motherboard. Pull-up resistors should be discrete resistors, since resistor packs will need longer stub lengths and may violate timing requirements. The stub length to these pull-up resistors must be controlled. The maximum stub length on a strobe trace is < 0.1 inch. The maximum stub trace length on all other traces is < 0.5 inch. For pull-up recommendations, see "AGP Signals" on page 42.

**Table 14. Control Signal Line Length Recommendations**

| Width:Space | Board       | Trace           | Line Length                    | Pull-up Stub Length         |

|-------------|-------------|-----------------|--------------------------------|-----------------------------|

| 1:1         | Motherboard | Control Signals | 1.0 in < line length < 8.5 in  | < 0.5 in (Strobes < 0.1 in) |

| 1:2         | Motherboard | Control Signals | 1.0 in < line length < 10.0 in | < 0.5 in (Strobes < 0.1 in) |

### 5.2 ACPI Compliance Requirements

Based on the Advanced Configuration and Power Interface (ACPI) specification, the AGP graphics device must be ACPI compliant and must implement its self power management circuitry, such as self clock-gating and an idle bus detection mechanism to reduce power. However, in a Pentium II processor-based platform the AGP device clock is a derivative of the host clock.

When the host clock stops (C3 state - Deep Sleep), the AGP clock also stops. An AGP\_BUSY# protocol solves this instantaneous AGP stop clock problem. The AGP graphics device must signal the operating system or the south bridge that it is currently busy and the AGP clock should not be stopped.

The AGP device internally protects its core logic to ensure that an illegal clock will not corrupt the AGP device state. This protection gates the internal clock nets used for the device's logic from the time STP\_AGP# is asserted until it is deasserted. The STP\_AGP# signal is an indication that the AGP clock will not be valid for much longer and should be gated off for protection. STP\_AGP# should be connected to the PIIX4E's SUS\_STAT1# signal.

The AGP\_BUSY# signal indicates that the graphics controller requires the GCLK to be running. This signal should be connected to one of the PIIX4E's PCIREQ# pins. When the PCIREQ# pin must be shared, it can be logically ORed with one of the PIIX4E's PCIREQ# inputs. AGP\_BUSY# is an open-drain signal from the graphics device and requires a  $10~\mathrm{K}\Omega$  pull-up resistor.

AGP\_SUSPEND# is for AGP devices that support Suspend mode. The AGP\_SUSPEND# signal can be connected to the PIIX4E's SUSB# signal.

### 5.3 AGP IDSEL Routing

An AGP compliant master is composed of a PCI compliant target interface and an AGP compliant master interface. (Optionally the device can also include a PCI compliant master interface when required.) When used in a PCI mode of operation, the AGP device must provide an external IDSEL that is connected to AD16. When the AGP device is designed for exclusive operation on the AGP interface the device does not have an external IDSEL pin, therefore IDSEL does not need to be routed.

### 6.0 Design Guideline Checklists

Design checklists provided in this section are intended to be used for schematic reviews of the Pentium II Processor – Low-Power Module-based platform designs. The checklists do not represent the only way to design a system, but do provide recommendations. The system designer should examine the checklist items for correctness. Additional design considerations are also provided.

#### 6.1 Resistor Values

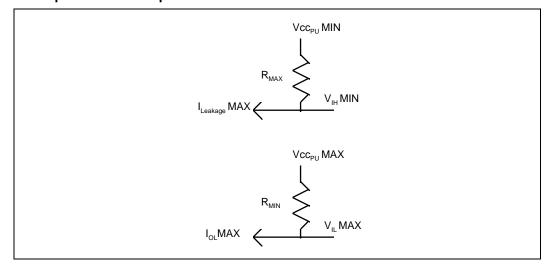

Pull-up and pull-down register values are system dependent. The appropriate value for your system can be determined from an AC/DC analysis of the pull-up voltage used, the current drive capability of the output driver, input leakage currents of all devices on the signal net, the pull-up voltage tolerance, the pull-up/pull-down resistor tolerance, the input high/low voltage specifications, the input timing specifications (RC rise time), etc. Analysis should be done to determine the minimum

and maximum values that may be used on an individual signal. Engineering judgment should be used to determine the optimal value. This determination can include cost concerns, commonality considerations, manufacturing issues, specifications and other considerations.

A simplistic DC calculation for a pull-up value is:

$$R_{MAX} = (Vcc_{PU} MIN - V_{IH} MIN) / I_{Leakage} MAX$$

$R_{MIN} = (Vcc_{PU} MAX - V_{IL} MAX) / I_{OL} MAX$

#### Figure 16. Pull-up Resistor Example

### 6.2 Low-Power Module Design Checklist [ ]Pass, [ ]Fail

For PIIX4E recommendations on the I/O system electronics board, please see "82371EB (PIIX4E) Design Checklist [ ]Pass, [ ]Fail" on page 43.

#### 6.2.1 Low-Power Module Errata

Please see the *Mobile Pentium*® *II Processor Specification Update* (order number 243887) for workarounds for any errata that may be present on the stepping used.

#### 6.2.2 Power and Ground Pins

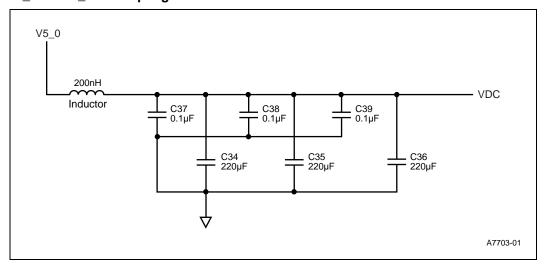

- V\_DC is the DC voltage driven from the power supply and is required to be between 5-V and 21-V DC. The module cannot be inserted or removed while V DC is powered on.

- V\_3S is a SUSB#-controlled 3.3-V voltage supply which is an output of the voltage regulator

on the system electronics. This rail should be off during Suspend-to-RAM (STR), Suspend-toDisk (STD), and Soft-Off (SOff) modes.

- V\_5 is a SUSC# controlled 5-V voltage supply which is an output of the voltage regulator on

the system electronics. This rail should be off during Suspend-to-Disk (STD), and Soft-Off

(SOff) modes.

- V\_3 is a SUSC# controlled 3-V voltage supply which is an output of the voltage regulator on the system electronics. This rail should be off during Suspend-to-Disk (STD), and Soft-Off (SOff) modes.

- V\_CPUPU is driven by the Low-Power Module to power processor interface signals such as the PIIX4E open-drain pull-ups for the processor/PIIX4E sideband signals.

- V\_CLK is driven by the Low-Power Module to power the HCLK drivers from the CK100-M clock source.

- VCCAGP is the VDDQ AGP voltage, and should be connected to V\_3.

- V<sub>TT</sub> is an output of the DC-DC regulator on the Low-Power Module, and is driven to the core voltage (VCC\_CORE) of the processor. V<sub>TT</sub> is used for ITP implementations.

- All unused active low 3.3-V tolerant inputs should be connected to V\_3S with a 10-KΩ resistor unless otherwise stated.

- All unused active high inputs should be connected to ground (V<sub>SS</sub>) through a 10-KΩ resistor unless otherwise stated.