# INTEL 380FB PCISET: 82380FB MOBILE Docking Controller (MPCI2)

- PCI Docking

- Efficient Repeater Architecture.

Mirrors Most Transactions Across the Bridge

- Subtractive Decoding Guarantees that All Accesses Targeted for a Down Stream ISA Bridge (such as the MISA) Arrive at Destination

- Supports the PCI Bus Enumeration Mechanism for PCI Docking

- High Performance Bridge Supports Fast Back-to-Back agents, and Memory Prefetching

- Supports a 5V Desktop PCI Interface for up to Four Bus Master PCI Add-in Card Slots on the Secondary PCI Bus

- The MISA PCI-to-ISA Bridge Allows a Docking Station to have an Additional Three ISA Slots

- PC/PCI DMA Protocol and PCI Docking Interface Creates a Very Low Pin Count Docking Connector

- Full Docking Support

- Notebooks can be Docked with No Pre-conditioning: On, Off, or Suspended (powered-on, to DRAM, or to disk)

- Undocking Mechanism Guarantees

Uninterrupted Notebook Operation

- The Same Docking Station can be used with 5V and 3.3V Notebooks

- Supports Automatic Isolation of All Active Docking Connector Signals

- Support for Both Desktop (A/C powered) and Mobile (Battery Powered) Docking Stations

- Non-Volatile Memory Interface to Store Docking Identification, and Notebook Configuration Information

- Full Power Management Support for Mobile Docking Stations

- Suspend (Powered-on, to DRAM, and to Disk)

- Resume

- PCI Clockrun Protocol

- Powered-on Suspend/Resume

Mode for A/C Powered Desktop

Docking Stations

- Low Power Mode Support for Undocked Mobile Docking Stations

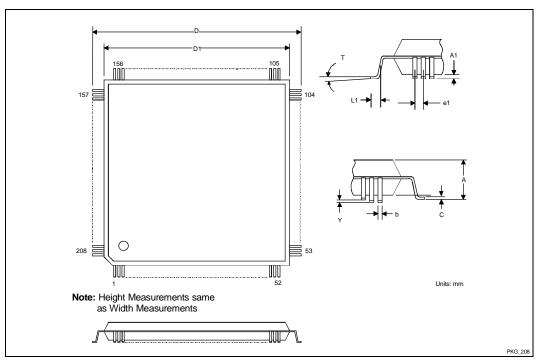

- 208-lead SQFP Package for the 82380FB MPCI2

The Intel 380FB PCIset (380FB) consists of the 82380FB Intel Docking Controller (MPCI2) and the 82380AB Mobile PCI-to-ISA Bridge (MISA). The 380FB supports four PCI slots and three ISA slots. The MPCI2 and MISA can also be used individually to provide either PCI slot expansion or ISA slot expansion.

The 380FB supports a full Hot Docking capable docking station with 5V PCI and ISA add-in expansion slots. MPCI2 provides the docking control for hot insertion, power management, and a support for a 5V PCI desktop style add-in bus. Internal arbitration supports four bus masters on the secondary PCI bus. The PC/PCI arbitration interface logic provides PC/PCI bridge support. The 380FB controls all docking, undocking and suspend/resume sequences for the docking station. The E²PROM interface logic provides an industry standard interface to a non-volatile memory device (E²PROM) for supporting dynamic autoconfiguration of a previously configured notebook/docking station combination. The Power management logic provides a control and status interface between the docking station and notebook that allows the docking station to control the state of the notebook. A non-volatile memory interface is used to store docking identification and notebook configuration information to speed dynamic configuration for a pre-configured notebook docking combination.

MPCI2 supports the PCI bus enumeration mechanism for PCI Docking. This is needed to support the Windows\* 95 dynamic configuration of system resources when the system docks or undocks. Otherwise, the operating system must reset the system after reconfiguration.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by the sale of Intel products. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intellectual products including liability or warranties relating to filmes for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, lift is saving, or life sustaining applications. Intel retains the right to make changes to specifications and product descriptions at any time, without notice. The Intel 380FB PCIset may contain design defects or errors known as errata. Current characterized errata are available on request. Third-party brands and names are the property of their respective owners.

The undocking mechanism of the 380FB guarantees a safe notebook removal. Event notification allows docking resources to be dynamically removed and applications gracefully shut down, if needed. A hardware mechanism is provided to indicate when the notebook is prepared to undock. This can be used to eject or unlock the notebook from the docking station.

The MPCI2's subtractive decoding guarantees that all accesses targeted for a downstream ISA bridge (such as the MISA) arrive at their destination. Software does not need to determine the devices on the ISA bridge and then program positive decode ranges (as is needed on traditional positive decode bridges).

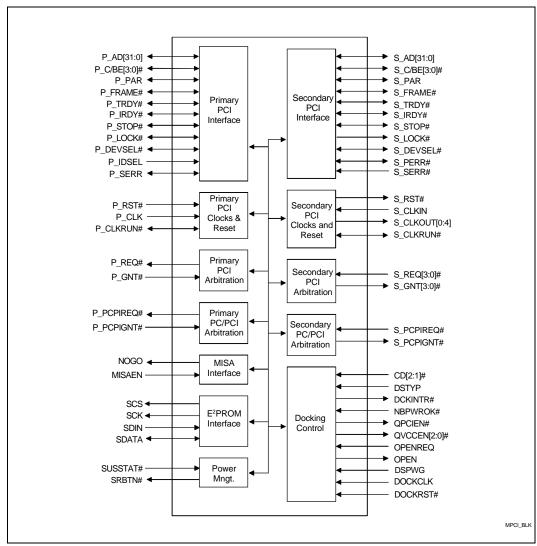

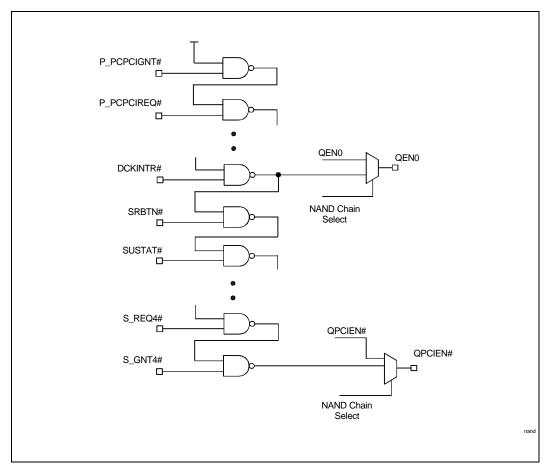

**MPCI2 Simplified Block Diagram**

# **CONTENTS**

|                                                              | PAGE |

|--------------------------------------------------------------|------|

| 1.0. ARCHITECTURE OVERVIEW                                   | 5    |

| 2.0. SIGNAL DESCRIPTION                                      | 6    |

| 2.1. Primary PCI Bus Signals (Docking Connector Side)        | 6    |

| 2.2. Secondary PCI Bus Signals (Docking Station Side)        | 7    |

| 2.3. MPCI2 to MISA Interface                                 | 9    |

| 2.4. Docking Station Management                              | 9    |

| 2.5. Power, Ground and Test                                  | 10   |

| 3.0. REGISTER DESCRIPTION                                    | 11   |

| 3.1. VID—Vendor Identification Register                      | 13   |

| 3.2. DID—Device Identification Register                      | 13   |

| 3.3. P_PCICMD—Primary Bus PCI Command Register               | 13   |

| 3.4. P_PCISTS—Primary PCI Status Register                    | 14   |

| 3.5. RID—Revision Identification Register                    | 14   |

| 3.6. CCODE—Class Code Register                               | 15   |

| 3.7. CACHE_LS—Cache Line Size Register                       | 15   |

| 3.8. P_MLT—Primary Bus Master Latency Timer                  | 15   |

| 3.9. HEADT—Header Type Register                              | 16   |

| 3.10. P_BUSNUM—Primary PCI Bus Number Register               | 17   |

| 3.11. S_BUSNUM—Secondary PCI Bus Number Register             | 17   |

| 3.12. SUB_BUSNUM—Subordinate PCI Bus Number Register         | 17   |

| 3.13. S_PCISTS—Secondary PCI Status Register                 | 18   |

| 3.14. PMEMBASE—Prefetchable Memory Base Register             | 18   |

| 3.15. PMEMLMT—Prefetchable Memory Limit Register             | 19   |

| 3.16. BRDG_C—Bridge Control Register                         | 19   |

| 3.17. CONCNTL—Connector Control Register                     | 19   |

| 3.18. CONEVNT—Connector Event Register                       | 20   |

| 3.19. SIF_BURSTEN—Serial Interface and Burst Enable Register |      |

| 3.20. MISC_STS—MPCI2 Miscellaneous Status Register           | 22   |

| 3.21. SPCYC_MSG—Special Cycle Message Encode Register        | 22   |

| 4.0. FUNCTIONAL DESCRIPTION                                  | 23   |

| 4.1. PCI Docking Operations                                  | 23   |

| 4.1.1. Configuration Cycles                                  | 23   |

| 4.1.2. Special Cycles                                        | 23   |

| 4.1.3. Interrupt Acknowledge Cycles                          | 23   |

| 4.1.4. Subtractive Decode                                    | 23   |

| 4.1.5. Memory and I/O Cycles                                 | 24   |

| 4.1.5.1. Moment and I/O Transaction Control                  | 24   |

# 82380FB (MPCI2)

| 4.1.5.2. Write Posting                           | 25 |

|--------------------------------------------------|----|

| 4.1.5.3. Memory Read Bursting and Prefetching    | 26 |

| 4.1.6. Parity Support                            | 26 |

| 4.1.7. Error Support                             | 26 |

| 4.1.8. Arbitration                               | 27 |

| 4.1.8.1. Secondary PCI Bus Master Arbitration    | 27 |

| 4.1.8.2. PC/PCI REQ#/GNT#                        | 28 |

| 4.1.8.3. Distributed DMA                         | 28 |

| 4.1.9. Clock Run Protocol                        | 29 |

| 4.1.10. Bus Lock                                 | 29 |

| 4.1.10.1. Bus Lock for Standard PCI Masters      | 29 |

| 4.1.10.2. Bus Lock for PC/PCI Masters            | 29 |

| 4.1.11. Reset Behavior                           | 29 |

| 4.2. Docking Control Logic                       | 29 |

| 4.2.1. Docking Control Interface Signals         | 30 |

| 4.2.2. Docking Operation                         | 31 |

| 4.2.2.1. Initialization                          | 31 |

| 4.2.2.2. Connecting the PCI Bus                  | 31 |

| 4.2.3. Undocking Operation                       | 31 |

| 4.2.3.1. Undocking events                        | 31 |

| 4.2.3.2. PCI bus Disconnect and Notebook Release | 32 |

| 4.3. Power Management Description                | 33 |

| 4.3.1. Suspend Modes                             | 33 |

| 4.3.1.1. Power-on Suspend                        | 33 |

| 4.3.1.2. Power-off Suspend                       |    |

| 4.3.1.3. Hardware control signals                | 33 |

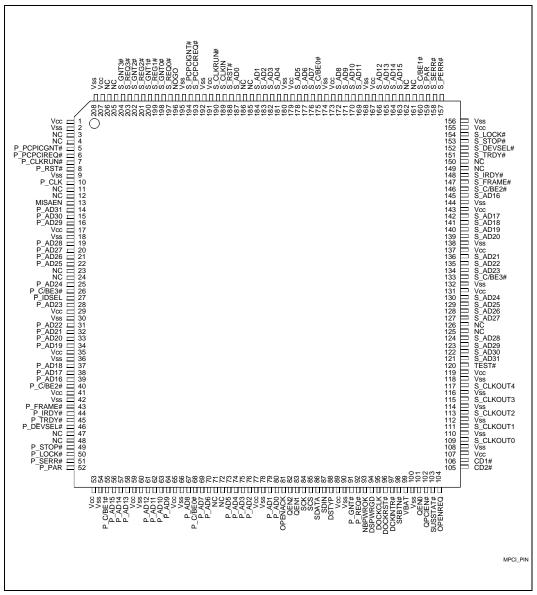

| 5.0. PINOUT AND PACKAGE INFORMATION              | 34 |

| 5.1. MPCI2 Pinout Information                    | 34 |

| 5.2. MPCI2 Package Information                   | 38 |

| 6.0. TESTABILITY                                 | 39 |

## 1.0. ARCHITECTURE OVERVIEW

The Intel 380FB PCIset consists of the 82380FB MPCI2 and the 82380AB MISA. This PCIset provides the logic necessary to build a full Hot Docking capable docking station with 5V PCI and ISA add-in expansion slots. MPCI2 provides the docking control for hot insertion, power management and a support for a 5V PCI desktop style add-in bus. MISA provides a PCI-to-ISA bridge for a 5V ISA desktop style add-in bus. This document describes the MPCI2 component.

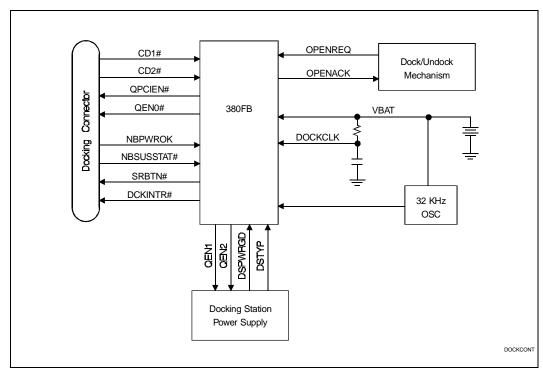

MPCI2's Primary and Secondary PCI bus units control the PCI Docking Functions. The PCI Arbitration logic provides a secondary PCI arbitre that handles four PCI request grant pairs for docking station slots. The PC/PCI arbitration interface logic provides PC/PCI bridge support. The MISA interface logic provides a proprietary interface between the MPCI2 and the MISA (when present). The Docking Control logic controls all docking, undocking and suspend/resume sequences for the docking station. The E²PROM interface logic provides an industry standard interface to a non-volatile memory device (E²PROM) for supporting dynamic autoconfiguration of a previously configured notebook/docking station combination. The Power management logic provides a control and status interface between the docking station and notebook that allows the docking station to know and control the state of the notebook.

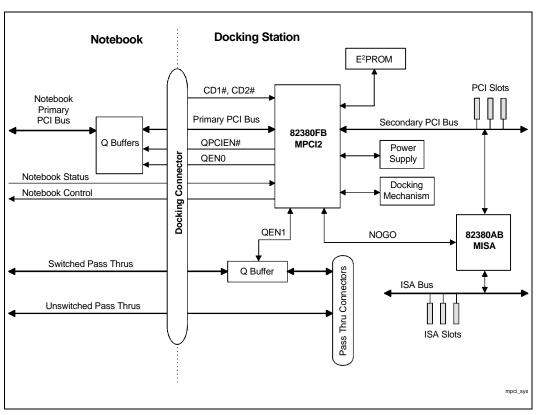

The typical 380FB-based docking system is illustrated in Figure 1. This diagram illustrates all of the major components, busses, important logic blocks and interconnects.

Figure 1. MPCI2 System Block Diagram

5

#### 2.0. SIGNAL DESCRIPTION

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of "active-low" and "active-high" signals. The term **assert**, or **assertion** indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term **negate**, or **negation** indicates that a signal is inactive.

The I/O buffer types are shown below:

Buffer TypeDescriptionIinput-only signalOtotem pole output

I/O bi-direction, tri-state input/output pin

s/t/s sustained tri-state od open drain

# 2.1. Primary PCI Bus Signals (Docking Connector Side)

| Name         | Туре  | Description                                                                                                                                                                                                                                                                        |

|--------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P_CLK        | I     | <b>Primary PCI Bus System Clock.</b> P_CLK provides timing for all transactions on the primary PCI bus. All other PCI signals are sampled on the rising edge of PCICLK, and all timing parameters are defined with respect to this edge. PCI supports 0–33 MHz.                    |

| P_RST#       | I     | <b>Primary PCI Bus Reset.</b> When P_RST# is active all primary PCI bus signals are tri-stated.                                                                                                                                                                                    |

| P_AD[31:0]   | I/O   | Primary PCI Bus Address and Data. The standard PCI address and data lines. Address is driven with FRAME# assertion, data is driven or received in following clocks. These signals are connected to the primary PCI bus Address and Data lines from the notebook docking connector. |

| P_C/BE[3:0]# | I/O   | <b>Primary PCI Bus Command and Byte Enables.</b> During the address phase of a transaction, P_C/BE[3:0]# define the bus command. During the data phase P_C/BE[3:0]# are used as Byte Enables.                                                                                      |

| P_PAR        | I/O   | <b>Primary PCI Bus Parity Signal.</b> Parity is even parity across P_AD[31:0] and P_C/BE[3:0]#.                                                                                                                                                                                    |

| P_FRAME#     | s/t/s | <b>Primary PCI Bus Cycle Frame Signal.</b> This signal is driven by the current primary PCI bus master to indicate the beginning and duration of an access.                                                                                                                        |

| P_IRDY#      | s/t/s | <b>Primary PCI Bus Initiator Ready.</b> This signal indicates the initiating agent's ability to complete the current data phase of the primary bus transaction.                                                                                                                    |

| P_TRDY#      | s/t/s | <b>Primary PCI Bus Target Ready.</b> This signal indicates the target agent's ability to complete the current data phase of the primary bus transaction.                                                                                                                           |

| Name        | Туре    | Description                                                                                                                                                                                                              |

|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P_STOP#     | s/t/s   | <b>Primary PCI Bus Stop.</b> This signal indicates the current target is requesting the master to stop the current primary bus transaction.                                                                              |

| P_LOCK#     | s/t/s   | <b>Primary PCI Bus Lock.</b> This signal indicates an atomic operation that may require multiple primary PCI bus transactions to complete.                                                                               |

| P_IDSEL     | I       | <b>Primary PCI Bus Initialization Device Select.</b> This signal is used as a chip select during configuration read and write transactions. This signal should be externally tied to one of upper 21 address signals.    |

| P_DEVSEL#   | s/t/s   | <b>Primary PCI Bus Device Select.</b> MPCI2 drives P_DEVSEL# to indicate that it is the target of the current primary bus transaction. MPCI2 always subtractively drives this signal.                                    |

| P_REQ#      | I/O     | <b>Primary PCI Bus Request.</b> MPCI2 drives this signal to request the primary PCI bus on behalf of a secondary PCI bus master.                                                                                         |

| P_GNT#      | I       | <b>Primary PCI Bus Grant.</b> P_GNT# indicates that the primary PCI bus has been granted to the MPCI, who requested the primary bus on behalf of a secondary PCI bus master or to flush its write post buffers upstream. |

| P_PCPCIREQ# | I/O     | Primary PCI Bus PC/PCI Request. This pin meets the PC/PCI DMA specification.                                                                                                                                             |

| P_PCPCIGNT# | I/O     | Primary PCI Bus PC/PCI Grant. This pin meets the PC/PCI DMA specification.                                                                                                                                               |

| P_SERR#     | od      | <b>Primary PCI Bus System Error.</b> MPCI2 pulses system error for one CLK upon detecting reported parity errors on the secondary PCI bus, or any other system error where the result will be catastrophic.              |

| P_CLKRUN#   | I/O, od | <b>Primary PCI Bus Clock Run.</b> The CLKRUN# central resource negates this signal to generate a primary PCI stop clock request. MPCI2 asserts this signal to request the primary PCI clock to be restarted.             |

# 2.2. Secondary PCI Bus Signals (Docking Station Side)

| Name          | Туре | Description                                                                                                                                                                                                                                        |

|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_CLKOUT[4:0] | 0    | Secondary PCI Bus System Clocks (0–33 MHz). These are five identical PCI clock images for the docking station PCI peripherals. These secondary PCI clocks are stopped when the primary PCI clock is stopped.                                       |

| S_CLKIN       | I    | Secondary PCI Bus System Clock Feedback. This clock input should be connected to one of the output clocks (SCLKOUT[4:0]). This signal is used by MPCI2 to minimize clock skew.                                                                     |

| S_RST#        | 0    | Secondary PCI Bus Reset. At power-up S_RST# is asserted and remains asserted until the docking station state machine negates it. S_RST# is asynchronously asserted and is synchronously negated.                                                   |

| S_AD[31:0]    | I/O  | Secondary PCI Bus Address and Data. The standard PCI address and data lines. Address is driven with FRAME# assertion, data is driven or received in following clocks. These signals are connected to the secondary PCI bus Address and Data lines. |

| Name         | Туре                | Description                                                                                                                                                                                                                                                                            |

|--------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_C/BE[3:0]# | I/O                 | Secondary PCI Bus Command and Byte Enables. During the address phase of a transaction, S_C/BE[3:0]# define the bus command. During the data phase S_C/BE[3:0]# are used as Byte Enables.                                                                                               |

| S_PAR        | I/O                 | Secondary PCI Bus Parity. Parity is even parity across S_AD[31:0] and S_C/BE[3:0]#.                                                                                                                                                                                                    |

| S_FRAME#     | s/t/s               | Secondary PCI Bus Cycle Frame. This signal is driven by the current secondary PCI bus master to indicate the beginning and duration of an access.                                                                                                                                      |

| S_IRDY#      | s/t/s               | Secondary PCI Bus Initiator Ready. This signal indicates the initiating agent's ability to complete the current data phase of the secondary bus transaction.                                                                                                                           |

| S_TRDY#      | s/t/s               | Secondary PCI Bus Target Ready. This signal indicates the target agent's ability to complete the current data phase of the secondary bus transaction.                                                                                                                                  |

| S_STOP#      | s/t/s               | Secondary PCI Bus Stop. This signal indicates the current target is requesting the master to stop the current secondary bus transaction.                                                                                                                                               |

| S_LOCK#      | s/t/s               | Secondary PCI Bus Lock. This signal indicates an atomic operation that may require multiple secondary PCI bus transactions to complete.                                                                                                                                                |

| S_DEVSEL#    | s/t/s               | Secondary PCI Bus Device Select. MPCI2 drives S_DEVSEL# to indicate that it is the target of the current secondary PCI bus transaction. MPCI2 always subtractively drives this signal, except during configuration cycles, when MPCI2 drives S_DEVSEL# during the medium decode phase. |

| S_REQ[3:0]#  | 1                   | Secondary PCI Bus Request [3:0]. Secondary PCI bus masters drive these signals to MPCI2 to indicate a need to use the bus.                                                                                                                                                             |

| S_GNT[3:0]#  | 0                   | Secondary PCI Bus Grant [3:0]. MPCI2 drives one of these grants active to indicate to the requesting master that the master may initiate a bus cycle on the secondary PCI bus.                                                                                                         |

| S_PCPCIREQ#  | I/O                 | Secondary PC/PCI Bus Request. This pin meets the PC/PCI DMA specification.                                                                                                                                                                                                             |

| S_PCPCIGNT#  | I/O                 | Secondary PC/PCI Bus Grant. This pin meets the PC/PCI DMA specification.                                                                                                                                                                                                               |

| S_PERR#      | I                   | Secondary PCI Bus Parity Error. This pin is driven by a secondary PCI bus agent to indicate a parity error has occurred on the secondary PCI bus.                                                                                                                                      |

| S_SERR#      | 1                   | Secondary PCI Bus System Error. This pin is driven by a secondary PCI bus agent to indicate a system error has occurred on the secondary PCI bus.                                                                                                                                      |

| S_CLKRUN#    | I/O,<br>s/t/s<br>pu | <b>Secondary PCI CLKRUN.</b> MPCI2 and the other secondary PCI bus agents use this pin to communicate their positions on whether the secondary clocks may currently be stopped or not.                                                                                                 |

# 2.3. MPCI2 To MISA Interface

| Name   | Туре | Description                                                                                                                                                                                               |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOGO   | 0    | <b>NO GO.</b> Signal to MISA indicating the source and destination of a PCI bus transaction. See section 3.5.                                                                                             |

| MISAEN | 1    | MISA Enable. MISAEN asserted indicates that a MISA is present in the docking station. This pin must be grounded if the docking station does not use MISA or tied to Vcc if MISA is present in the system. |

# 2.4. Docking Station Management

| Name     | Туре | Description                                                                                                                                                                                                                                                                                                                               |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCKINTR# | od   | DOCK Event Interrupt. This output is asserted during any docking event.                                                                                                                                                                                                                                                                   |

| NBPWROK  | I    | <b>Notebook Power Ok.</b> A high indicates the notebook power supply is valid. A low indicates the notebook power supply is not valid.                                                                                                                                                                                                    |

| DSPWRGD  | I    | <b>Docking Station Power Good.</b> A high indicates the docking station power supply is valid. A low indicates the docking station power supply is not valid.                                                                                                                                                                             |

| SUSSTAT# | I    | Notebook Suspend State. Low indicates the notebook is in a suspended state. High indicates the notebook is operating.                                                                                                                                                                                                                     |

| SRBTN#   | od   | Notebook Suspend/Resume Button.                                                                                                                                                                                                                                                                                                           |

| DOCKCLK  | I    | <b>Docking Clock.</b> 32.768 KHz Oscillator Input. This clock is used to clock the docking state machine.                                                                                                                                                                                                                                 |

| CD[2:1]# | I    | Docking Station Connector Detects 1 and 2. These two pins detect when the notebook's docking connector is fully seated with the docking station's docking connector.                                                                                                                                                                      |

| OPENREQ  | I    | <b>Docking Station Door Open Request.</b> This signal requests removal of the notebook from the docking station. This signal should be connected to a push-button that can generate an active high pulse with a minimum 128 µs pulse.                                                                                                     |

| OPENACK  | 0    | <b>Docking Station Door Open Pulse.</b> MPCI2 uses this signal to initiate an undocking sequence. MPCI2 pulses this signal high for 256 µs after it has prepared the docking station and notebook to undock. External logic uses this signal to unlock the notebook from the docking station, and then eject it from the docking station. |

| DSTYP    | I    | <b>Docking Station Type.</b> A high indicates a type 1 docking station (docking station power is independent of the notebook power). A low indicates a type 2 docking station (docking station power follows notebook power).                                                                                                             |

| DOCKRST# | I    | <b>Dock Reset.</b> Resets all the logic powered by VBAT. This signal should be asserted when the backup battery (VBAT) is changed.                                                                                                                                                                                                        |

| QPCIEN#  | 0    | PCI Q-Buffers Enable. Enables/Disables the PCI Q-buffers.                                                                                                                                                                                                                                                                                 |

| QEN0     | 0    | PCI and Quiet Dock Q-Buffers Enable. This signal is used to turn on the PCI and Quiet Dock Q-buffers.                                                                                                                                                                                                                                     |

| Name     | Туре | Description                                                                                                                                                                                                                                                       |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QEN[2:1] | 0    | PCI and Quiet Dock Q-Buffers Enable. QEN[2:1] are general purpose outputs controlled by CONCNTL register.                                                                                                                                                         |

| SCK      | 0    | <b>Serial E<sup>2</sup>PROM clock.</b> This pin is driven to reflect the state of SIF_BURSTEN register bit 0.                                                                                                                                                     |

| SCS      | 0    | Serial E <sup>2</sup> PROM Chip Select. This pin is driven to reflect the state of SIF_BURSTEN register bit 1.                                                                                                                                                    |

| SDIN     | I    | Serial E <sup>2</sup> PROM Input Data. The state of bit 4 of the SIF_BURSTEN register follows this input pin.                                                                                                                                                     |

| SDATA    | I/O  | <b>Serial E<sup>2</sup>PROM Data.</b> Data direction determined by SIF_BURSTEN register bit 10. As an output, the pin is driven to reflect the state of SIF_BURSTEN register bit 5. As an input, the state of bit 5 of the SIF_BURSTEN register follows this pin. |

# 2.5. Power, Ground, and Test

| Name  | Туре | Description                                                                                                                                                                                                                  |

|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VBAT  |      | <b>Backup Battery Power.</b> This power input is used to supply power to the docking state machine. Power should be supplied to this pin by the normal docking power source when on, or by a backup battery (VBAT) when off. |

| Vcc   |      | Power. Powered by the 5V docking station power source.                                                                                                                                                                       |

| Vss   |      | <b>Grounds.</b> These signals should be connected to the system ground.                                                                                                                                                      |

| NC    |      | No Connects. These pins should be left floating.                                                                                                                                                                             |

| TEST# |      | <b>Test Input.</b> This signal should be pulled HIGH through a pull-up resistor (10 k $\Omega$ ).                                                                                                                            |

#### 3.0. REGISTER DESCRIPTION

The MPCI2 contains only PCI Configuration registers. These registers are accessible only by primary PCI masters. The registers can be accessed as Byte, Word (16-bit), or DWord (32-bit) quantities. All multi-byte numeric fields use "little-endian" ordering (i.e., lower addresses contain the least significant parts of the field). The following nomenclature is used for access attributes.

**RO** Read Only. If a register is read only, writes to this register have no effect.

**R/W** Read/Write. A register with this attribute can be read and written.

R/WC Read/Write Clear. A register bit with this attribute can be read and written. However, a write of

1 clears (sets to 0) the corresponding bit and a write of 0 has no effect.

Some of the MPCI2 registers described in this section contain reserved bits. Software must deal correctly with fields that are reserved. On reads, software must use appropriate masks to extract the defined bits and not rely on reserved bits being any particular value. On writes, software must ensure that the values of reserved bit positions are preserved. That is, the values of reserved bit positions must first be read, merged with the new values for other bit positions and then written back.

In addition to reserved bits within a register, MPCI2 contains address locations in the PCI configuration space that are marked "Reserved" (Table 2). MPCI2 responds to accesses to these address locations by completing the Host cycle. Software should not write to reserved MPCI2 configuration locations in the device-specific region (above address offset 3Fh).

During a hard reset (RST# asserted), MPCI2 sets its internal configuration registers to predetermined **default** states. The default state represents the minimum functionality feature set required to successfully bring up the system. Hence, it does not represent the optimal system configuration. MPCI2 configuration registers assume their default conditions when:

A low level occurs on any of the following pins: DOCKRST#, P\_RST#, DSPWRGD, NBPWROK, SUSSTAT#

OR

A high level on any of the following pins: CD1#, CD2#

**Table 1. MPCI2 Configuration Space**

| Address<br>Offset | Register<br>Symbol | Register Name                              | Access |

|-------------------|--------------------|--------------------------------------------|--------|

|                   | •                  | PCI Specific Registers                     | ·      |

| 01–00h            | VID                | Vendor Identification                      | RO     |

| 02-03h            | DID                | Device Identification                      | RO     |

| 04–05h            | P_PCICMD           | Primary bus PCI Command Register           | R/W    |

| 06-07h            | P_PCISTS           | Primary bus PCI Status Register            | R/W    |

| 08h               | RID                | Revision Identification                    | RO     |

| 09-0Bh            | CCODE              | Class Code                                 | RO     |

| 0Ch               | CACHE_LS           | Cache Line Size                            | RO     |

| 0Dh               | P_MLT              | Primary Bus Master Latency Timer           | R/W    |

| 0Eh               | HEADT              | Header Type                                | RO     |

| 0F-17h            | _                  | Reserved                                   | _      |

| 18h               | P_BUSNUM           | Primary PCI Bus Number                     | R/W    |

| 19h               | S_BUSNUM           | Secondary PCI Bus Number                   | R/W    |

| 1Ah               | SUB_BUSNUM         | Subordinate PCI Bus Number                 | R/W    |

| 1B-1Dh            | _                  | Reserved                                   | _      |

| 1E-1Fh            | S_PCISTS           | Secondary PCI bus Status Register          | R/W    |

| 20-23h            | _                  | Reserved                                   | _      |

| 24-25h            | PMEMBASE           | Prefetchable Memory Base Register          | R/W    |

| 26-27h            | PMEMLMT            | Prefetchable Memory Limit Register         | R/W    |

| 28-3Dh            | _                  | Reserved                                   | _      |

| 3E-3Fh            | BRDG_C             | Bridge Control Register                    | R/W    |

|                   |                    | MPCI2 Specific Registers                   |        |

| 40h               | CONCNTL            | Connector Control Register                 | R/W    |

| 41h               | CONEVNT            | Connector Event Register                   | R/W    |

| 42-43h            | _                  | Reserved                                   | _      |

| 44–45h            | SIF_BURSTEN        | Serial Bus Interface/Burst Enable Register | R/W    |

| 46h               | MISC_STS           | MPCI2 Miscellaneous Status Register        | R/W    |

| 47–4Bh            | _                  | Reserved                                   |        |

| 4C-4Dh            | SPCYC_MSG          | Special Message Encode Register            | R/W    |

| 4Eh–FFh           |                    | Reserved                                   | _      |

## 3.1. VID—Vendor Identification Register

Address Offset: 00-01h

Default Value: 8086h

Attribute: Read Only

The VID Register contains the Intel vendor identification number (8086h). This 16-bit register combined with the Device Identification Register (DEVID) uniquely identifies MPCI2 device. Writes to this register have no effect.

| Bit  | Description                                                                     |

|------|---------------------------------------------------------------------------------|

| 15:0 | Vendor Identification Number. This is a 16-bit value assigned to Intel (8086h). |

# 3.2. DID—Device Identification Register

Address Offset: 02–03h Default Value: 124Bh Attribute: Read Only

This register contains the device identification number. This register along with the Vendor ID (VID), uniquely identifies the MPCI2. Writes to this register have no effect.

| Bit  | Description                                                             |

|------|-------------------------------------------------------------------------|

| 15:0 | Device Identification Number. This is a 16-bit value assigned to MPCI2. |

# 3.3. P\_PCICMD—Primary Bus PCI Command Register

Address Offset: 04–05h

Default Value: 0080h

Attribute: Read/Write

The P\_PCICMD register controls cycle transfers, other than configuration cycles, between the primary PCI bus and secondary PCI bus. Configuration cycles are always transferred by MPCI2, regardless of the state of this register.

| Bit  | Description                                                                                                                                                          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:9 | Reserved.                                                                                                                                                            |

| 8    | P_SERR# Enable. 1=Enable P_SERR# pin. 0=Disable.                                                                                                                     |

| 7    | Reserved. Returns a 1 on a Read operation.                                                                                                                           |

| 6:3  | Reserved.                                                                                                                                                            |

| 2    | <b>Secondary-to-primary Bus Enable.</b> When this bit is set (and bits[1:0]=11), secondary-to-primary PCI transfers are enabled.                                     |

| 1:0  | <b>Primary-to-secondary Bus Enable.</b> 11=Enables cycle transfer from the primary PCI bus to the secondary PCI bus. 00=Disable. 01 and 10 values are not supported. |

# 3.4. P\_PCISTS—Primary PCI Status Register

Address Offset: 06–07h Default Value: 0400h

Attribute: Read/Read Write Clear

The P\_PCISTS register provides primary PCI bus event information. Reads to this register behave normally. Status bits in this register are set by events on the MPCI2 primary PCI bus. Software sets these bits to 0 by writing a 1 to them.

| Bit  | Description                                                                                                                                                                                                                     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | Reserved.                                                                                                                                                                                                                       |

| 14   | Signaled System Error—R/WC. This bit is set when MPCI2 asserts P_SERR# on the primary PCI bus.                                                                                                                                  |

| 13   | <b>Received Master Abort—R/WC.</b> This bit is set when a MPCI2 initiated cycle on the primary PCI bus terminates with a master abort.                                                                                          |

| 12   | Received Target Abort—R/WC. This bit is set whenever a MPCl2 initiated cycle on the primary PCl bus terminates with a target abort.                                                                                             |

| 11   | <b>Signaled Target Abort—R/WC.</b> This bit is set whenever the MPCI2 as a target on the primary interface terminates a transaction with a target abort.                                                                        |

| 10:9 | <b>DEVSEL# Timing—RO.</b> This 2-bit field is read only and always returns a 10b. Since MPCI2 performs positive decode on configuration cycles and subtractive decode on all others, these bits will not be used by the system. |

| 8:0  | Reserved.                                                                                                                                                                                                                       |

# 3.5. RID—Revision Identification Register

Address Offset: 08h

Default: See latest stepping information

Access: Read Only

This read only register contains the revision number of each MPCI2 component.

| Bit | Description                                                                                                              |

|-----|--------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Revision Identification Number. Indicates the revision identification number for the MPCI2. (00h indicates A-0 stepping) |

## 3.6. CCODE—Class Code Register

Address Offset: 09–0Bh

Default Value: 060480h

Attribute: Read Only

This register indicates MPCI2's class code as defined in the PCI Specification.

| Bit  | Description                                                                         |

|------|-------------------------------------------------------------------------------------|

| 23:0 | Base Class Code. Value=06h indicating a Bus Bridge.                                 |

| 15:0 | Sub-Class Code. Value=04h indicating a PCI Docking.                                 |

| 7:0  | Programming Interface. Value=80h. Bit 7 High indicates a subtractive decode bridge. |

# 3.7. CACHE\_LS—Cache Line Size Register

Address Offset: 0Ch

Default Value: 08h

Attribute: Read Only

The Cache Line Size register is an 8-bit read-only register that specifies the system cache line size in units of 32-bit words. MPCl2 only allows a cache line size of 32 bytes. This register is used when accessing a non-prefetchable area using the memory read line (MRL) or memory read multiple (MRM) commands. In these cases, MPCl2 terminates the access on any 32-byte aligned address. A non-prefetchable memory area is defined as any burstable read access (MRM, MRL, MR) that is:

- Upstream with the UP\_BPF\_EN bit reset low

- · Downstream and does not fall within the prefetchable memory window

| Bit | Description                                                                         |

|-----|-------------------------------------------------------------------------------------|

| 7:0 | Cache Line Size. 08h indicates that the MPCI2 cache line size is fixed at 32 bytes. |

#### 3.8. P\_MLT—Primary Bus Master Latency Timer

Address Offset: 0Dh

Default Value: 00h

Attribute: Read/Write

This register specifies, in units of PCI bus clocks, the value of MPCI2's master latency timer when MPCI2 flushes its write post buffers on the primary bus after an upstream write has been completed by a secondary bus master. The counter is used in the following two ways:

1. During the initial write burst from a secondary PCI bus master, once the secondary PCI bus master terminates its cycle and the secondary PCI bus becomes idle, the master latency timer begins to count down. If the counter expires before the write post buffer flushing ends and MPCI2's P\_GNT# signal is sampled negated at that time, MPCI2 terminates its flushing onto the primary PCI bus after one more data phases, and re-asserts P\_REQ# to continue flushing at a later time. At this time, another primary bus master may get on the bus and generate transactions. While primary-to-primary PCI bus transactions

progress unimpeded, any primary-to-secondary PCI bus transaction, other than a write, are retried by MPCI2. Any write that must cross MPCI2 are disconnected at the first data phase.

If the timer does not expire before the flushing finishes, or if it does expire but P\_GNT# is still asserted, MPCl2 will continue flushing the post buffers until all data is written out.

2. If an initial write burst from a secondary PCI bus master is disconnected by a primary PCI bus target, MPCI2 will request the bus via P\_REQ# to flush the remaining data in its write post buffers. When P\_GNT# is given and MPCI2 starts flushing, it enables the master latency timer to count down at the start of the cycle (P\_FRAME# assertion). If the timer expires before the write post buffer flushing ends and MPCI2's P\_GNT# signal is sampled negated at that time, MPCI2 terminates its flushing on the primary PCI bus after one more data phases, and re-asserts P\_REQ# to continue flushing at a later time. At this time, another primary bus master may get on the bus and generate transactions. While primary-to-primary transactions progress unimpeded, any primary-to-secondary transaction, other than a write, will be retried by MPCI2. Any write that must cross MPCI2 will be disconnected at the first data phase.

If the timer does not expire before the flushing finishes, or if it does expire but P\_GNT# is still asserted, MPCl2 continues flushing the write post buffers until all data is written out.

When the MPCI2 is not flushing posted data, it relies on the initiating master's latency timer. In these cases, MPCI2 is simply generating cycles on behalf of a requesting bus master, and the cycles are subject to that master's latency timer. Thus, this register has no impact on other types of read or write cycles such as read bursting or prefetching.

When the MPCI2 is flushing posted data on a PCPCIGT# (Cascade Channel) the Master Latency Timer is disabled.

| Bit |            | Description                                                         |

|-----|------------|---------------------------------------------------------------------|

| 7:6 | Reserved.  |                                                                     |

| 5:4 | Timer Valu | e. This field determines the master latency timer value as follows: |

|     | Bits[5:4]  | Latency Time                                                        |

|     | 00         | timer disabled (no time-out)                                        |

|     | 01         | 16 clocks                                                           |

|     | 10         | 32 clocks                                                           |

|     | 11         | 0 clocks (immediate time-out)                                       |

| 3:0 | Reserved.  |                                                                     |

# 3.9. HEADT—Header Type Register

Address Offset: 0Eh

Default Value: 01h

Attribute: Read Only

This register indicates the configuration space format.

| Bit | Description                                                                                                                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Multifunction Device. 0 indicates a single function device.                                                                                                                                         |

| 6:0 | <b>Layout Code.</b> The value of 000 0001b indicates that the configuration register space is that of a PCI Docking. The layout is defined in <i>PCI to PCI Bridge Architecture Specification</i> . |

# 3.10. P\_BUSNUM—Primary PCI Bus Number Register

Address Offset: 18h

Default Value: 00h

Attribute: Read/Write

This register contains MPCI2's primary PCI bus number.

| Bit | Description                                         |

|-----|-----------------------------------------------------|

| 7:0 | Primary Bus Number. MPCI2's primary PCI bus number. |

# 3.11. S\_BUSNUM—Secondary PCI Bus Number Register

Address Offset: 19h

Default Value: 00h

Attribute: Read/Write

This register contains MPCI2's secondary PCI bus number.

| Bit | Description                                             |

|-----|---------------------------------------------------------|

| 7:0 | Secondary Bus Number. MPCI2's secondary PCI bus number. |

# 3.12. SUB\_BUSNUM—Subordinate PCI Bus Number Register

Address Offset: 1Ah

Default Value: 00h

Attribute: Read/Write

This register contains the number of the highest numbered PCI bus that is behind the MPCI2 (see PCI Docking Operations section for additional information).

| Bit | Description                                                                  |

|-----|------------------------------------------------------------------------------|

| 7:0 | Subordinate Bus Number. Number of the last PCI bus that is behind the MPCI2. |

# 3.13. S\_PCISTS—Secondary PCI Status Register

Address Offset: 1E–1Fh Default Value: 0400h

Attribute: Read Only, Read/Write Clear

The S\_PCISTS register provides secondary PCI bus event information. Reads to this register behave normally. Status bits in this register are set by events on the MPCI2 secondary PCI bus. Software sets the R/WC bits in this register to 0 by writing a 1 to them.

| Bit  | Description                                                                                                                                                                                                                     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | Reserved.                                                                                                                                                                                                                       |

| 14   | Received System Error—R/WC. This bit is set when the MPCI2 detects S_SERR# on the secondary PCI bus.                                                                                                                            |

| 13   | Received Master Abort—R/WC. This bit is set when a MPCI2 initiated cycle on the secondary PCI bus terminates with a master abort.                                                                                               |

| 12   | Received Target Abort—R/WC. This bit is set when a MPCI2 initiated cycle on the secondary PCI bus terminates with a target abort.                                                                                               |

| 11   | <b>Signaled Target Abort—R/WC.</b> This bit is set when the MPCI2, as a target on the secondary PCI bus, terminates a transaction with a target abort.                                                                          |

| 10:9 | <b>DEVSEL# Timing—RO.</b> This 2-bit field is read only and always returns a 10b. Since MPCI2 performs positive decode on configuration cycles and subtractive decode on all others, these bits will not be used by the system. |

| 8    | Data Parity Detected. Hardwired to 0. MPCI2 does not check parity.                                                                                                                                                              |

| 7:0  | Reserved.                                                                                                                                                                                                                       |

# 3.14. PMEMBASE—Prefetchable Memory Base Register

Address Offset: 24–25h Default Value: 0010h

Attribute: Read/Write, Read Only

This register specifies the upper 12 bits of the base address for the prefetchable memory address range. AD[19:0] is assumed to be all 0's. For a description of MPCI2's Read prefetch operations see the PCI Docking Operations section.

| Bit  | Description                                                                                                                                   |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15:4 | AD[31:20]—R/W. Bits [15:4] correspond to AD[31:20], respectively. This field locates the prefetchable memory base address on 1 MB boundaries. |  |

| 3:0  | <b>64-bit addressing—RO.</b> Hardwired to 0s. The MPCI2 supports only 32-bit addressing.                                                      |  |

# 3.15. PMEMLMT— Prefetchable Memory Limit Register

Address Offset: 26–27h Default Value: 0000h

Attribute: Read/Write, Read Only

This register specifies the upper memory address for the prefetchable memory address range. AD[19:0] is assumed to be all 1's. For a description of MPCI2's Read prefetch operations, see the PCI Docking Operations section.

| Bit  | Description                                                                                                                                     |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15:4 | AD[31:20] —R/W. Bits [15:4] correspond to AD[31:20], respectively. This field locates the prefetchable memory upper address on 1 MB boundaries. |  |

| 3:0  | <b>64-bit addressing—RO.</b> Hardwired to 0s. The MPCI2 supports only 32-bit addressing.                                                        |  |

# 3.16. BRDG\_C—Bridge Control Register

Register Location: 3F–3Eh

Default Value: 0000h

Attribute: Read/Write

This register controls the forwarding of S\_SERR# assertions to P\_SERR# on the primary PCI bus.

| Bit  | Description                                                                                                                                            |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15:2 | Reserved.                                                                                                                                              |  |

| 1    | <b>S_SERR#-to-P_SERR# Enable.</b> 1=Enable forwarding of S_SERR# to P_SERR# (P_SERR# Enable bit in the P_PCICMD register must be set to 1). 0=Disable. |  |

| 0    | Reserved.                                                                                                                                              |  |

## 3.17. CONCNTL—Connector Control Register

Register Location: 40h

Default Value: 00h

Attribute: Read/Write

This register contains the two power enable signals for two docking station isolation buffers: one for the parallel port and floppy disk drive, and the other for the external keyboard and mouse ports.

| Bit | Description                                                      |  |

|-----|------------------------------------------------------------------|--|

| 7:4 | Reserved.                                                        |  |

| 3   | QEN2 Output Signal. 1=QEN2 output is high. 0=QEN2 output is low. |  |

| 2   | QEN1 Output Signal. 1=QEN1 output is high. 0=QEN1 output is low. |  |

| 1:0 | Reserved.                                                        |  |

# 3.18. CONEVNT—Connector Event Register

Register Location: 41h

Default Value: Read: 11xx 1111b

Attribute: Read/Write, Read Only

This register provides a combination of status bits reflecting how several configuration pins are set, and an interrupt status register for the DCKINTR# interrupt. For a detailed description of the docking process, see the Docking Control Logic section.

#### NOTE

Reads from this register return the inverted values of the register bits.

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | Reserved. Read as 1.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 6   | <b>Power-on Suspend (PWRONSUS)</b> — <b>R/W.</b> This bit controls the MPCI2 powered-on suspend state and should be set to 0 during normal operation (see Power Management section).                                                                                                                                                                                                                                                             |  |

| 5   | MISAEN Pin Status—RO. This bit reflects the inverted state of the MISAEN pin.                                                                                                                                                                                                                                                                                                                                                                    |  |

| 4   | DSTYP Pin Status—RO. This bit reflects the inverted state of the DSTYP pin.                                                                                                                                                                                                                                                                                                                                                                      |  |

| 3   | UDKPERMIT—R/W. 1=DCKINTR# pin is asserted. MPCI2's docking state machine starts an undock sequence when this bit is cleared (set to 0). Software must wait a minimum of 32 μs (one dock clock period) between setting and clearing this bit or the event may not be recognized. When this bit is set to 0, MPCI2's docking state machine pulses the OPENACK signal for a duration of 256 μs to signal external hardware to "eject" the notebook. |  |

| 2   | Reserved. Read as 1.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 1   | <b>DOCKED—R/W.</b> MPCI2 sets this bit when its internal docking state machine completes its docking sequence. The MPCI2 then asserts its DCKINTR# pin. DCKINTR# can be negated by clearing the OPENREQ, DOCKED, and UDKPERMIT bits in this register.                                                                                                                                                                                            |  |

| 0   | <b>OPENREQ Pin.</b> MPCI2 sets this bit to 1 when the OPENREQ input pin is pulsed (asserted high). Software can assert the DCKINTR# pin by writing a 1 to this bit. DCKINTR# can be negated by clearing the OPENREQ, DOCKED, and UDKPERMIT bits in this register.                                                                                                                                                                                |  |

# 3.19. SIF\_BURSTEN—Serial Interface and Burst Enable Register

Address Offset: 44–45h

Default Value: 0000 0000 100x 0000b

Attribute: Read/Write

This register controls MPCI2 memory read bursting, prefetching, and memory write posting (see the PCI Docking Operations section for more details). SIF\_BURSTEN also controls the  $E^2$ PROM interface of the MPCI2.

| Bit   | Description                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 15:13 | Reserved.                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 12    | <b>Discard Write Posted Data Enable (EXP2SERR_EN).</b> 1=P_SERR# is asserted when MPCI2 discards posted write data and P_PCICMD [bit 8]=1.                                                                                                                                                                  |  |  |  |  |

| 11    | Reserved.                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 10    | SDATA Signal Direction (SDATA_DIR). 0=Output, 1=Input.                                                                                                                                                                                                                                                      |  |  |  |  |

| 9     | <b>Write Posting Enable (WR_POST_EN).</b> 1=Enable. 0=All write bursts are disconnected by MPCl2 at the first data phase.                                                                                                                                                                                   |  |  |  |  |

| 8     | <b>Read Bursting Enable (RD_BURST_EN).</b> 1=Enables non-prefetchable memory burst cycles (in both directions) to be translated into non-prefetchable memory read burst cycles. 0=Any non-prefetchable memory read burst access that crosses the MPCI2 bridge will be disconnected at the first data phase. |  |  |  |  |

| 7     | <b>Upstream Blind Prefetch Enable (US_BPF_EN).</b> 1=Enable. 0=Disable. Enables blind prefetching by MPCI2 for any upstream memory read burst cycle.                                                                                                                                                        |  |  |  |  |

| 6     | Reserved.                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 5     | <b>SDATA Signal State (SDATA_SS).</b> When SDATA_DIR (bit 10)=0, this bit programs the state of the SDATA pin (1=SDATA asserted. 0=SDATA negated). When SDATA_DIR=1, this bit reflects the state of the SDATA pin (1=SDATA asserted. 0=SDATA negated).                                                      |  |  |  |  |

| 4     | SDIN Signal State (SDIN_SS). 1=SDIN asserted (high). 0=SDIN negated (low).                                                                                                                                                                                                                                  |  |  |  |  |

| 3     | <b>S_PERR#-to-P_SERR# Map Disable.</b> 0=Pulse P_SERR# when S_PERR# is asserted (if P_SERR enable bit is set). 1=Do not pulse P_SERR# when S_PERR# is asserted.                                                                                                                                             |  |  |  |  |

| 2     | Cascade Determination Delay/Frame Determination Delay (CDD/FDD). 1=10 P_CLKs. 0=20 P_CLKs. This bit is used during PC/PCI transactions to determine the location of the bus master and to set the FRAME# delay during PC/PCI DMA retries.                                                                   |  |  |  |  |

| 1     | Serial E <sup>2</sup> PROM Chip Select (SCS). 1=SCS Output Pin asserted (high). 0=Negated.                                                                                                                                                                                                                  |  |  |  |  |

| 0     | Serial E <sup>2</sup> PROM Clock (SCK). 1=SCK Output Pin asserted (high). 0=Negated.                                                                                                                                                                                                                        |  |  |  |  |

# 3.20. MISC\_STS—MPCI2 Miscellaneous Status Register

Address Offset: 46h Default Value: 00h

Attribute: Read/Write Clear

This register contains MPCI2 miscellaneous status bits that are not recorded in the PCI standard status registers.

| Bit | Description                                                                                                                        |

|-----|------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | Reserved.                                                                                                                          |

| 0   | STEXP_ERR. 1=P_SERR# was asserted by MPCI2 after invalidation of posted write data. Software resets this bit by writing a 1 to it. |

# 3.21. SPCYC\_MSG—Special Cycle Message Encode Register

Register Location: 4C-4Dh Default Value: FFFEh Attribute: Read/Write

This register contains the message to be broadcast in the Encoded Message portion of a Special Cycle forwarded by MPCI2.

| Bi  | it  | Description                                                                                                                                                                                 |

|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15: | 5:0 | <b>Message Encode.</b> Encoded message portion of Special Cycle forwarded by MPCI2. See the <i>PCI Local Bus Specification</i> and <i>PCI to PCI Bridge Specification</i> for more details. |

## 4.0. FUNCTIONAL DESCRIPTION

# 4.1. PCI Docking Operations

MPCI2 operates as specified in *PCI Local Bus Specification*, revision 2.1 and *PCI to PCI Bridge Architecture Specification*, revision 1.0, with the options and exceptions described in this section.

MPCI2 uses a subtractive decoding mechanism rather than memory and I/O base and limit registers to determine where to forward cycles. All cycles initiated on the primary bus are repeated on the secondary bus, except when MPCI2 is flushing its write buffers downstream or the secondary bus is busy finishing up a previous cycle. All cycles initiated on the secondary bus are repeated on the primary bus, except for interrupt acknowledge cycles. Memory write posting and interrupt acknowledge cycles are discussed later in this section. If an MISA device (PCI-to-ISA Bridge) is present in the system, memory or I/O cycles not claimed by a primary or secondary bus target are assumed to be subtractively claimed by the PCI to ISA bridge.

MPCI2 does not support Fast Back-to-Back cycles of any type (even to the same agent) with one exception: two Fast Back-to-Back cycles on the primary bus in which the first cycle is two clocks long.

#### 4.1.1. CONFIGURATION CYCLES

MPCI2 repeats or converts all PCI configuration cycles in both directions (either primary-to-secondary or secondary-to-primary transfers). All type 0 configuration cycles are converted across MPCI2 as Configuration type 1 cycles with AD[23:2] all high. This includes primary interface type 0 configuration cycles that are targeted at MPCI2. Configuration type 0 burst cycles to MPCI2 are disconnected after the first data phase by MPCI2.

Configuration type 1 cycles that are to be ignored per the PCI to PCI Bridge Architecture Specification, revision 1.0, are forwarded by MPCI2 to the non-initiating bus as Configuration type 1 cycles with AD[23:2] all high.

#### 4.1.2. SPECIAL CYCLES

Special cycles received by MPCI2 on the initiating bus are converted to special cycles on the non-initiating bus. This cycle is used to maintain synchronization between the Primary and Secondary busses. The message portion of the converted special cycle is programmable using the Special Cycle Message Encode Register (4Ch–4Dh).

#### 4.1.3. INTERRUPT ACKNOWLEDGE CYCLES

MPCI2 forwards Interrupt Acknowledge cycles, unchanged, in the downstream direction. Interrupt Acknowledge cycles on the secondary bus will be ignored by MPCI2.

#### 4.1.4. SUBTRACTIVE DECODE

MPCI2 and MISA implement a proprietary signal (NOGO signal) so that the target of a secondary bus master can be communicated to MISA. When S\_FRAME# is asserted by a device other than MISA, source and target bus information is communicated to MISA. MPCI2 uses the NOGO signal to inform MISA about the originating bus. NOGO is sampled by MISA on the first PCICLK after S\_FRAME# is asserted. NOGO is high if the master is on the Primary PCI bus. NOGO is low if the master is on the secondary PCI bus. If MISA is the originator of the cycle, MPCI2 ignores NOGO.

For secondary bus masters, MPCI2 acts as the subtractive decode agent and asserts S\_DEVSEL#, if the cycle is not claimed by another device. For primary bus masters, MISA acts as the system's subtractive decode agent.

#### 82380FB (MPCI2)

If the bus master is on the primary bus and MISA claims the cycle by asserting DEVSEL#, it is assumed that the target is on the ISA bus. If the bus master is on the secondary bus and MPCI2 claims the cycle, the target may reside on the primary PCI bus or ISA bus. MPCI2 monitors the P\_DEVSEL# signal to check for a primary bus target. If the cycle is not claimed on the primary bus before the subtractive decode phase, MPCI2 assumes that the target is on the ISA bus. MPCI2 indicates this to MISA on the NOGO signal three clocks after the secondary bus decode phase. A high indicates that the target is on the primary bus. A low indicates that the target is on the ISA bus.

#### 4.1.5. MEMORY AND I/O CYCLES

The Primary Bus Enable field (bits[1:0]) in the P\_PCICMD register control access to I/O and memory space. These accesses must be enabled (bits[1:0]=11) for MPCI2 to repeat cycles across the bridge.

#### 4.1.5.1. Memory and I/O Transaction Control