### FC-PGA Intel<sup>®</sup> Pentium<sup>®</sup> III Processor and Intel<sup>®</sup> 840 Chipset

**Design Guide**

August 2000

Order Number: 273332-002

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> Pentium<sup>®</sup> III processor and Intel 840 chipset may contain design defects or errors known as errata which may cause the products to deviate from published specifications. Current characterized errata are available on request.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled platforms may require licenses from various entities, including Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2000

\*Third-party brands and names are the property of their respective owners.

# intel<sub>®</sub> Contents

| 1 | Desi  | ign Guide Introduction                                   | 1-1 |

|---|-------|----------------------------------------------------------|-----|

|   | 1.1   | Text Conventions                                         |     |

|   | 1.2   | Technical Support                                        |     |

|   |       | 1.2.1 Electronic Support Systems                         |     |

|   |       | 1.2.1.1 Online Documents                                 |     |

|   |       | 1.2.1.2 Intel Product Forums                             | 1-3 |

|   |       | 1.2.2 Telephone Technical Support                        | 1-3 |

|   | 1.3   | Product Literature                                       |     |

|   | 1.4   | Related Information                                      | 1-4 |

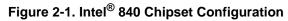

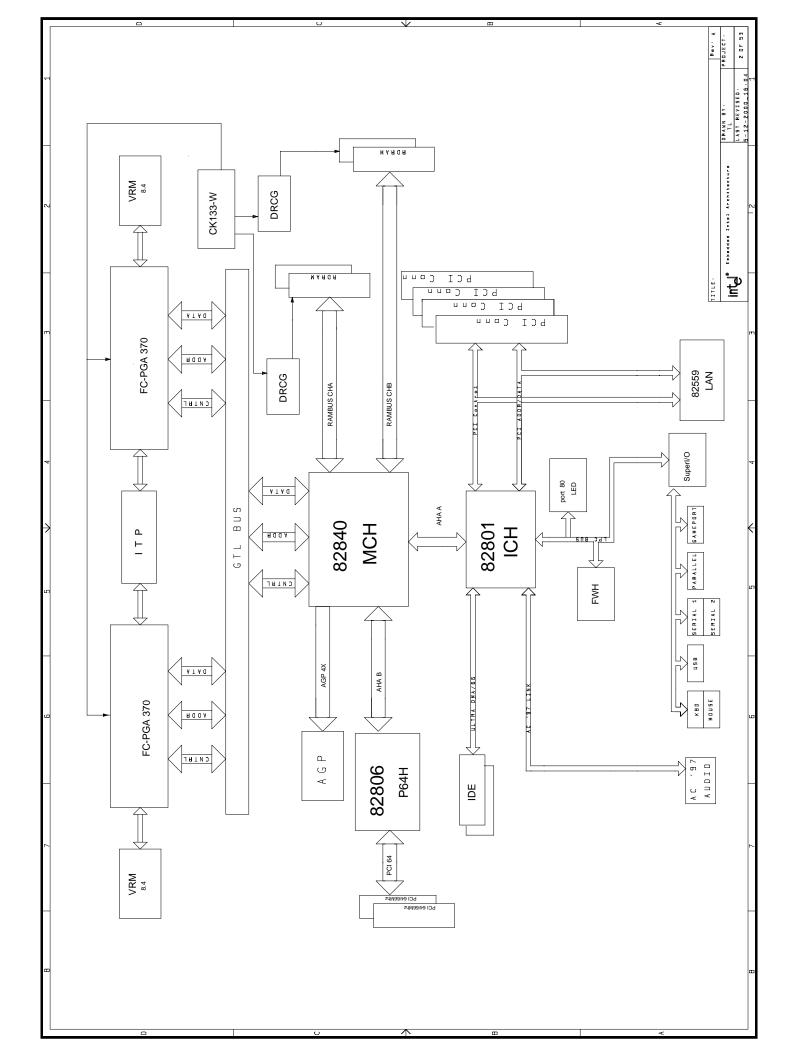

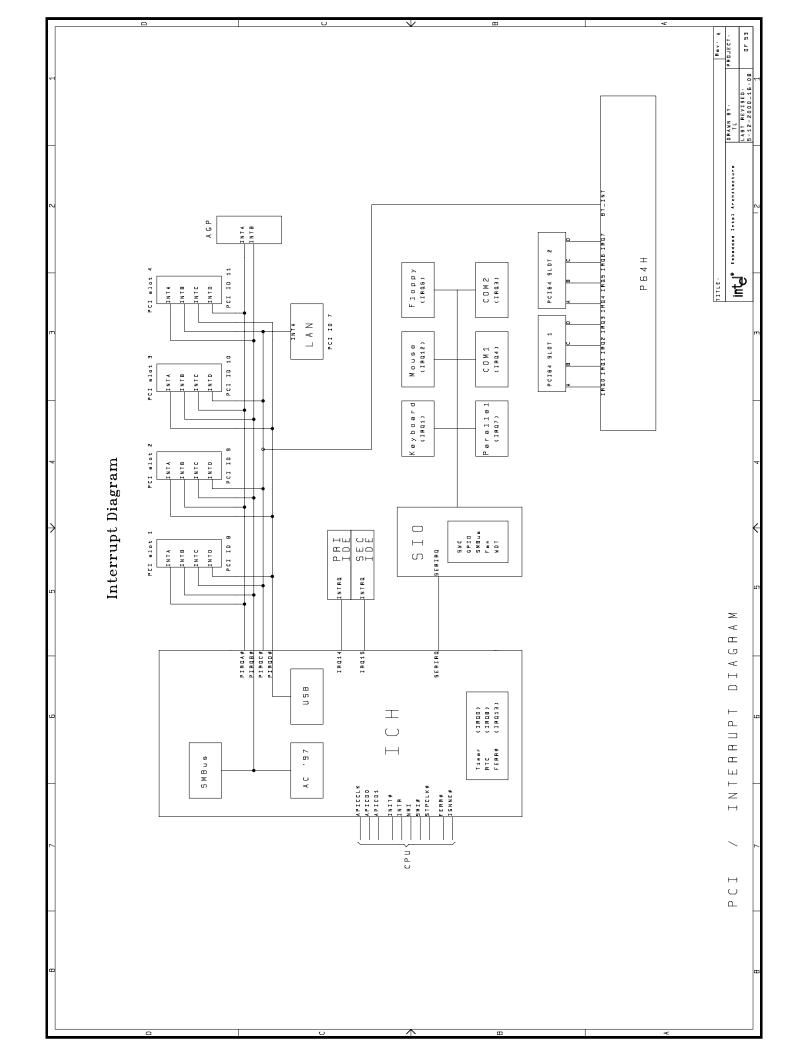

| 2 | Syst  | tem Overview                                             | 2-1 |

|   | 2.1   | Intel <sup>®</sup> 840 Chipset Components                | 2-2 |

|   |       | 2.1.1 Memory Controller Hub (MCH)                        | 2-2 |

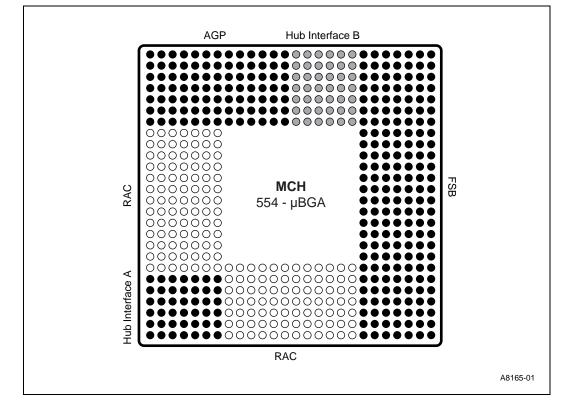

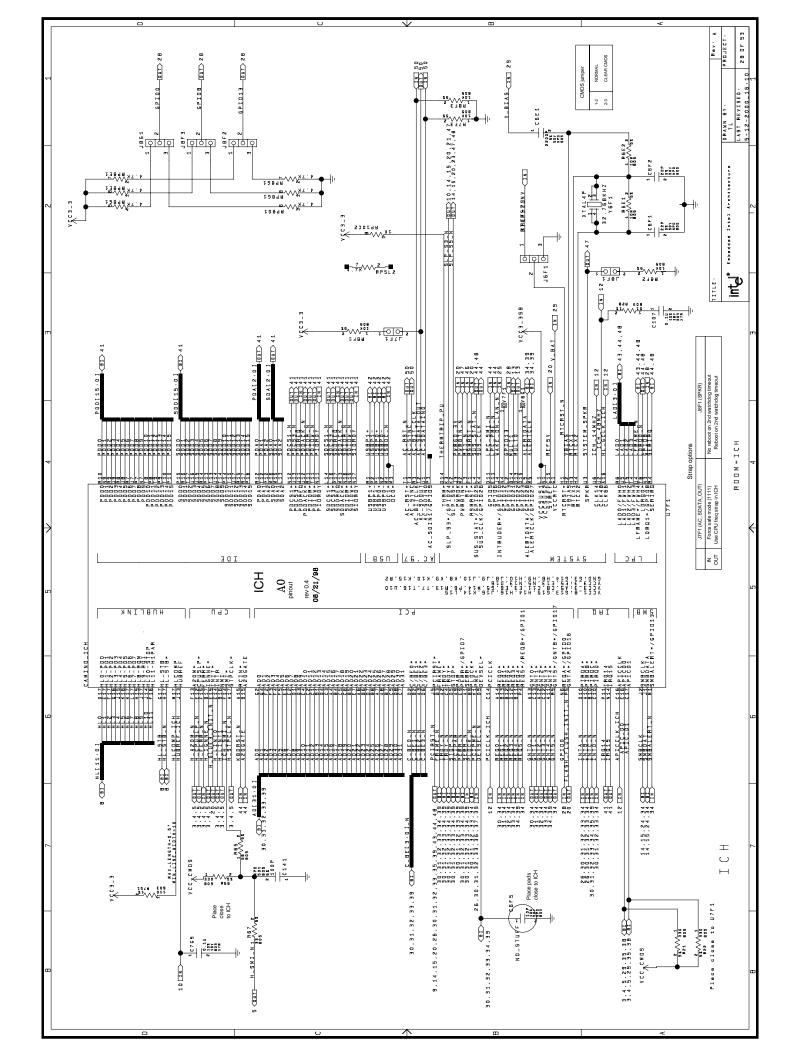

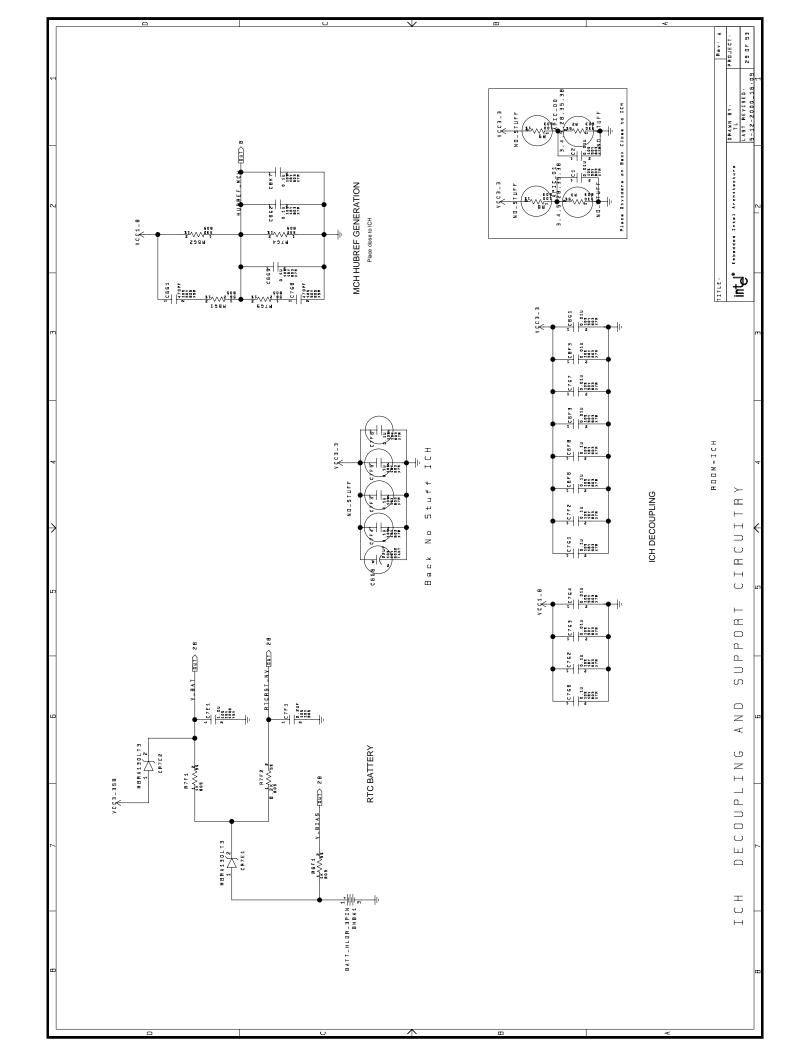

|   |       | 2.1.2 I/O Controller Hub (ICH)                           | 2-2 |

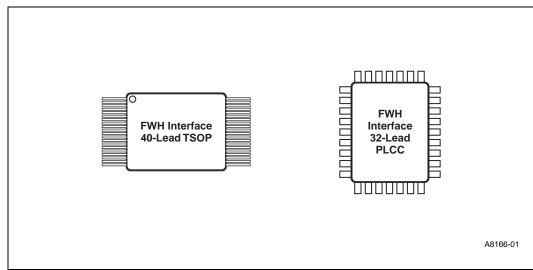

|   |       | 2.1.3 Firmware Hub (FWH)                                 |     |

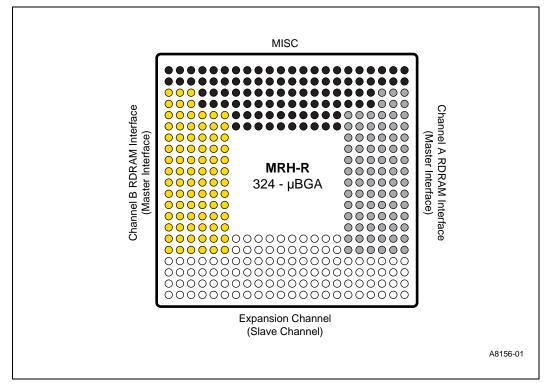

|   |       | 2.1.4 Memory Repeater Hub for RDRAM (MRH-R)              | 2-3 |

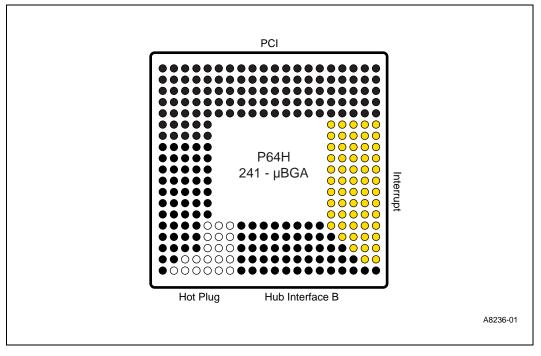

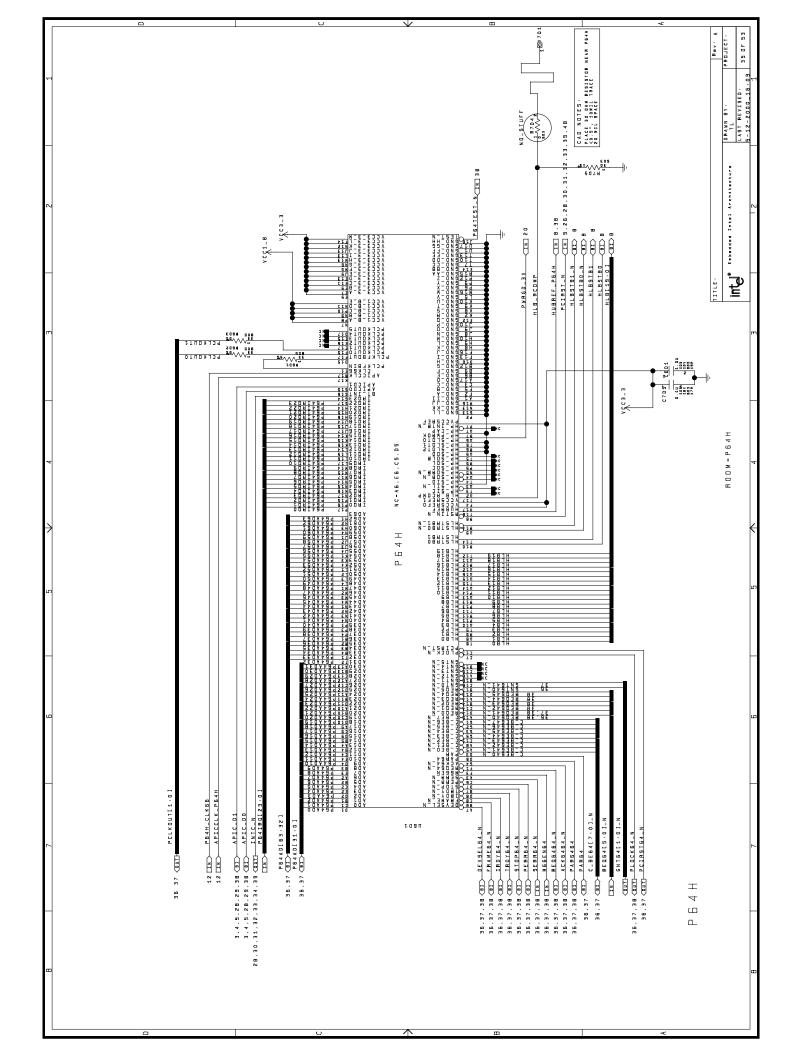

|   |       | 2.1.5 PCI 64-bit Hub (P64H)                              | 2-3 |

|   | 2.2   | Bandwidth Summary                                        | 2-3 |

|   | 2.3   | System Configuration                                     |     |

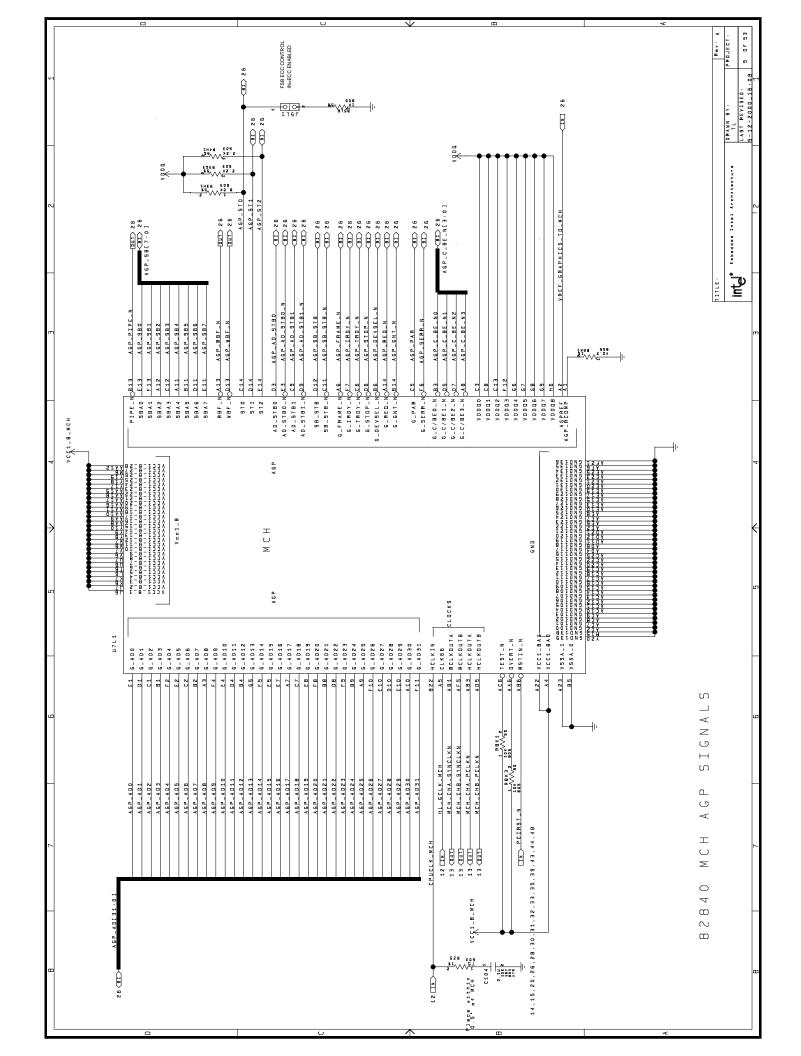

|   |       | 2.3.1 Platform Configuration                             | 2-4 |

| 3 | Platf | form Initiatives                                         | 3-1 |

|   | 3.1   | Memory Expansion Card and Connector                      | 3-1 |

|   | 3.2   | Direct RDRAM                                             |     |

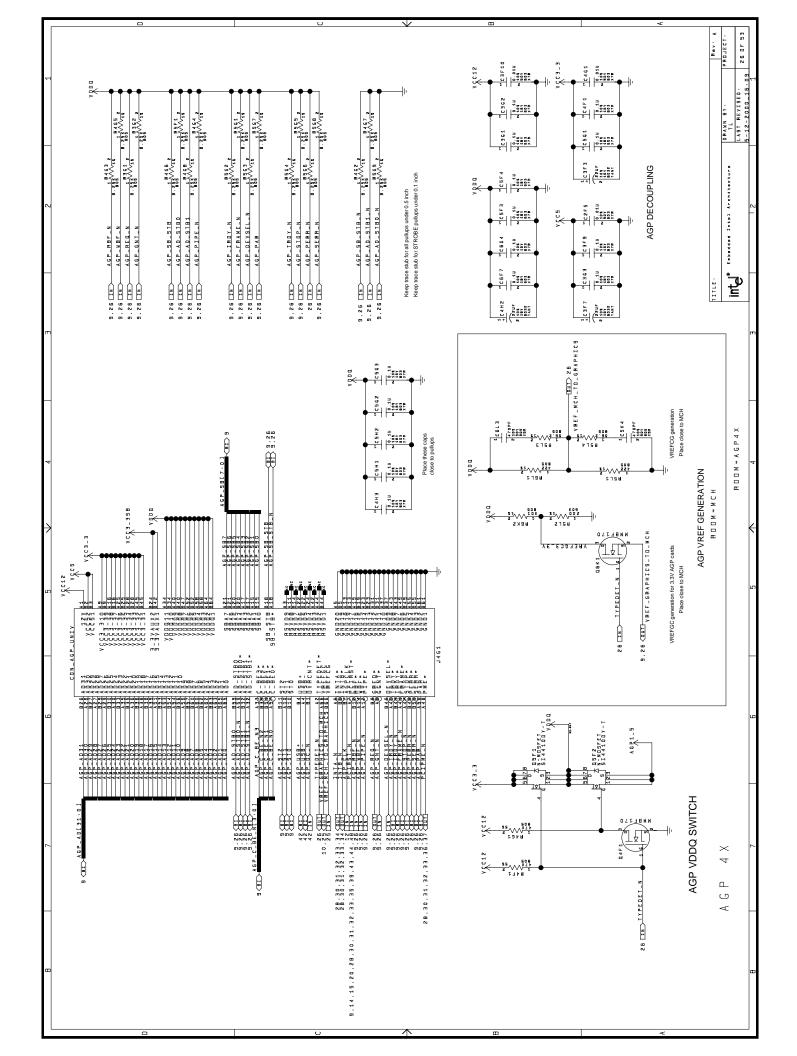

|   | 3.3   | Accelerated Graphics Port (AGP)                          | 3-1 |

|   |       | 3.3.1 AGP 2.0                                            | 3-1 |

|   |       | 3.3.2 AGP Pro                                            | 3-2 |

|   | 3.4   | Hub Interface                                            |     |

|   | 3.5   | Security: The Intel <sup>®</sup> Random Number Generator | 3-2 |

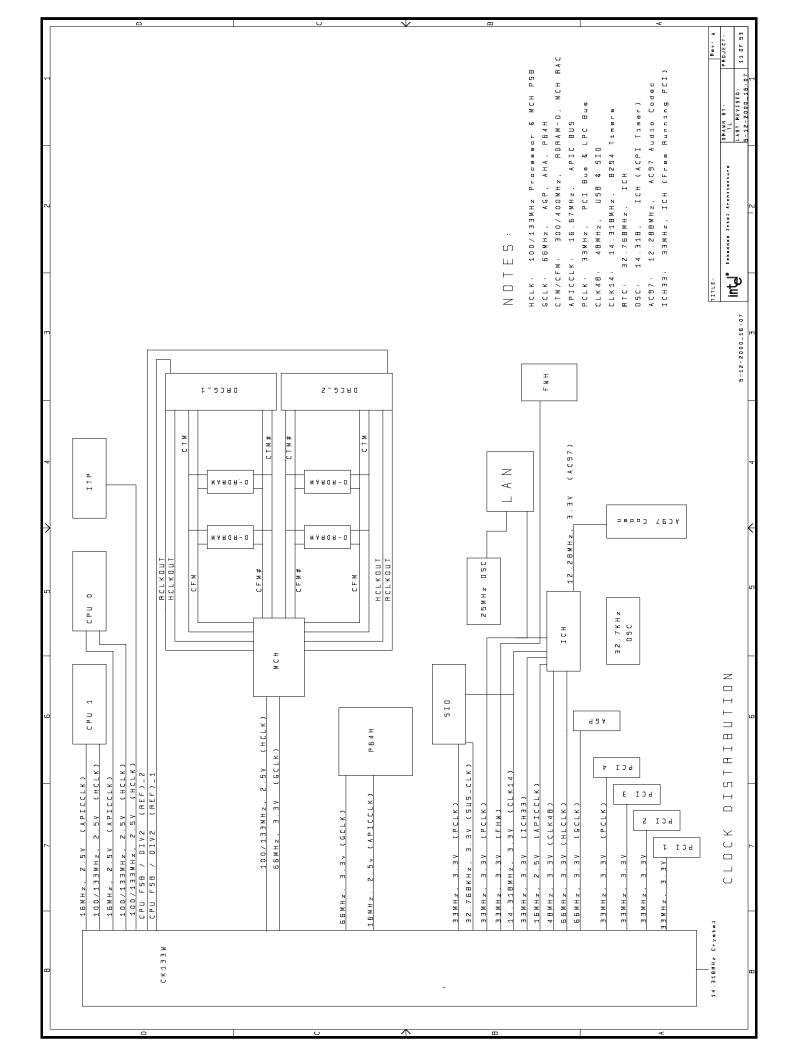

|   | 3.6   | Clocks                                                   | 3-4 |

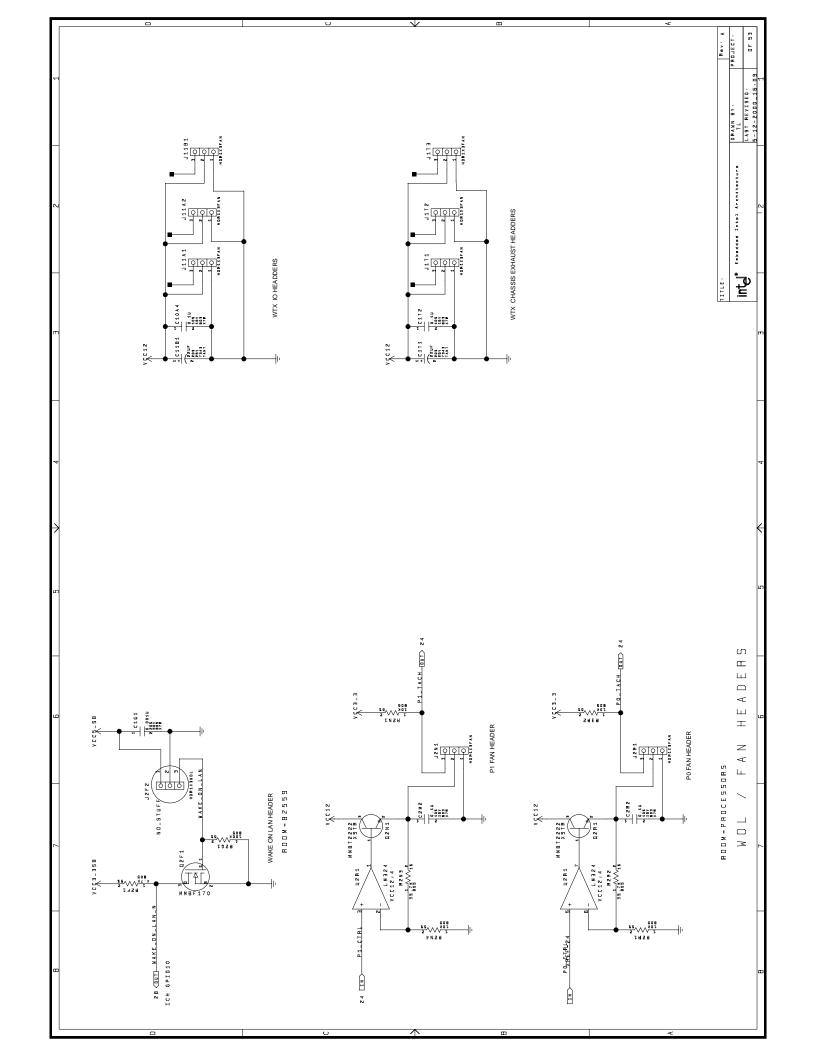

|   | 3.7   | WTX Form Factor                                          |     |

|   | 3.8   | Manageability                                            |     |

|   |       | 3.8.1 TCO Timer                                          |     |

|   |       | 3.8.2 CPU Present Indicator                              |     |

|   |       | 3.8.3 ECC Error Reporting                                |     |

|   |       | 3.8.4 Function Disable                                   |     |

|   |       | 3.8.5 Intruder Detect                                    |     |

|   |       | 3.8.6 SMBus                                              |     |

|   |       | 3.8.7 Alert-On-LAN                                       |     |

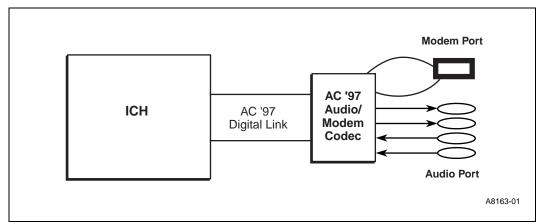

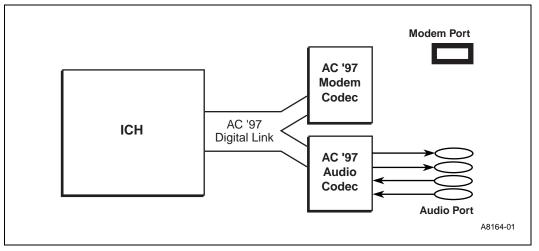

|   | 3.9   | AC '97                                                   |     |

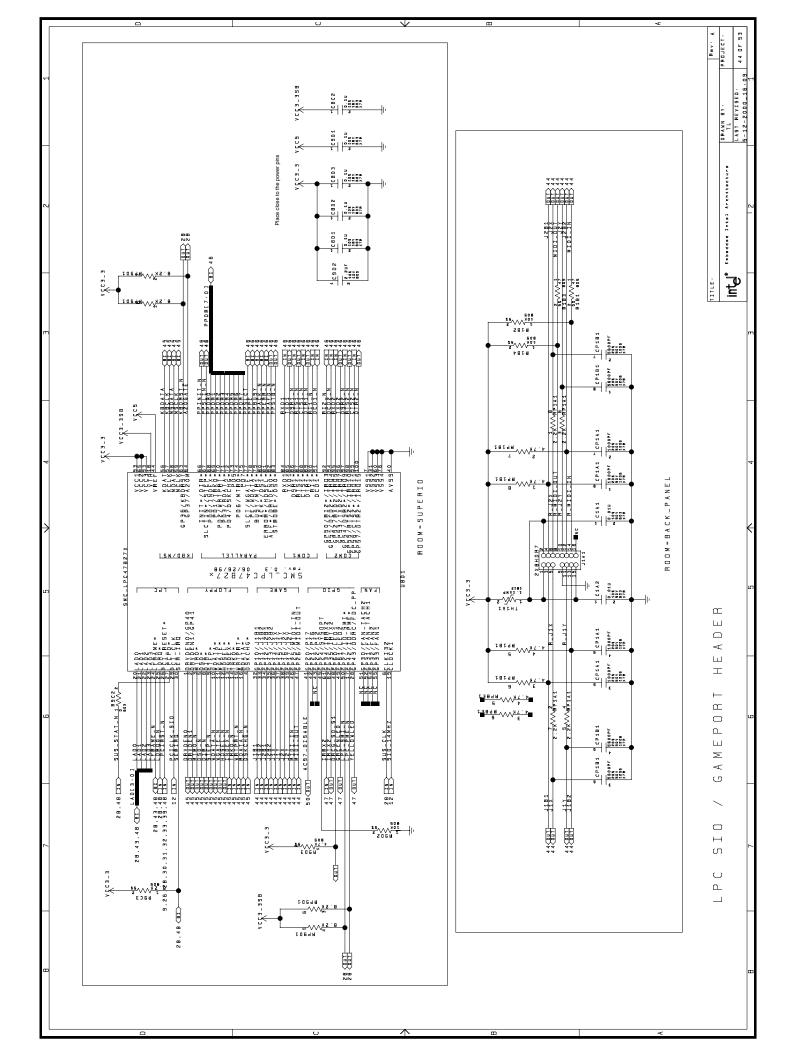

|   | 3.10  | Low Pin Count (LPC) Interface                            |     |

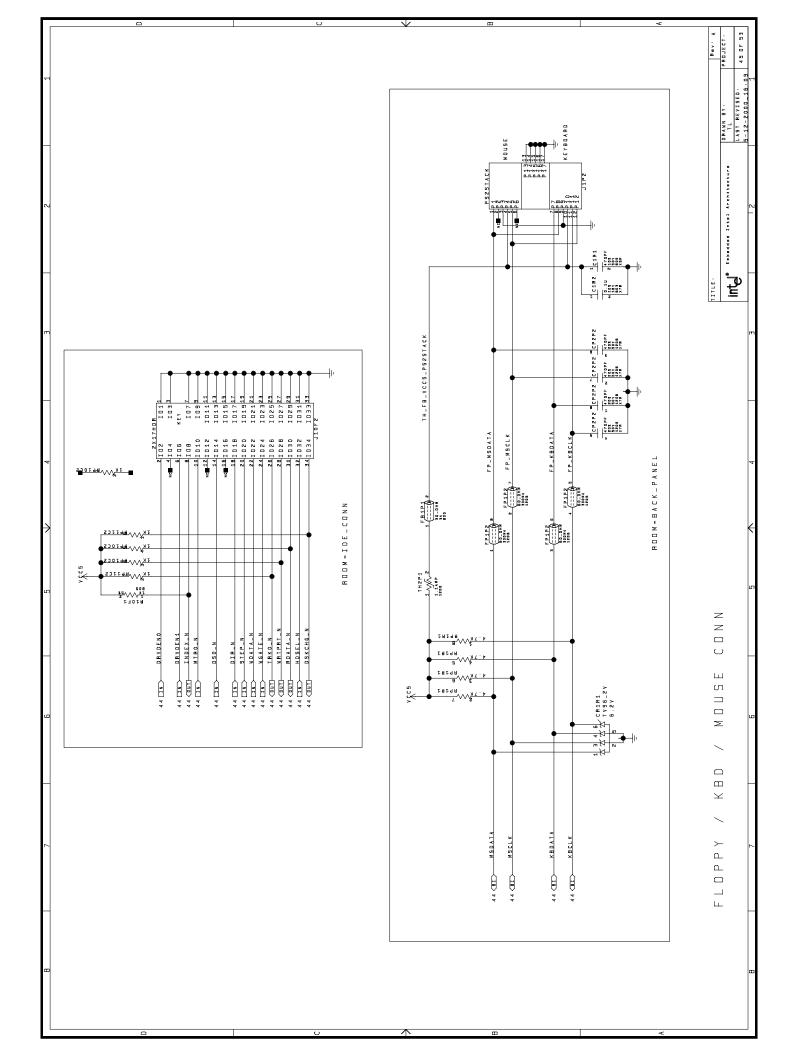

|   | 3.11  | Ultra DMA<br>Universal Serial Bus (USB)                  |     |

|   | 3.12  |                                                          |     |

| 4 | •     | tem Manufacturing                                        |     |

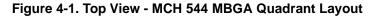

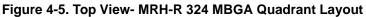

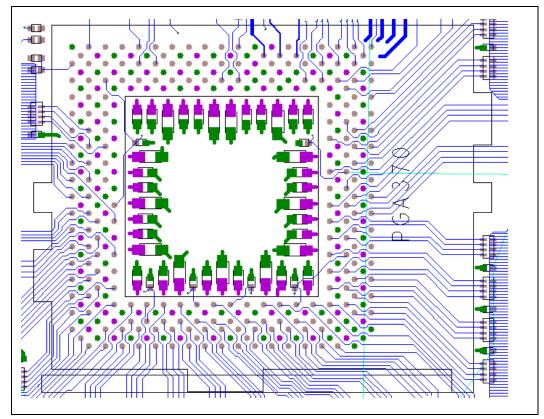

|   | 4.1   | Component Quadrant Layout                                | 4-1 |

| 5 |            | d Layout and Routing<br>elines                                                                                                                                                                                   | 5-1                             |

|---|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

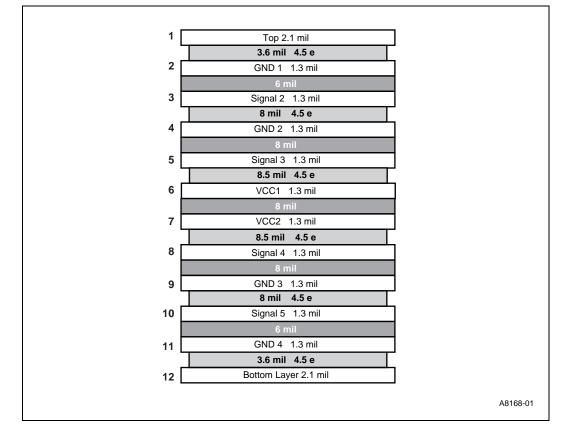

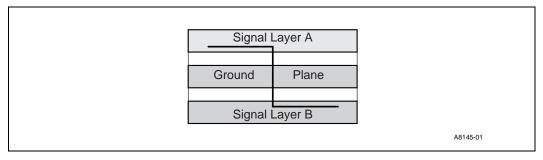

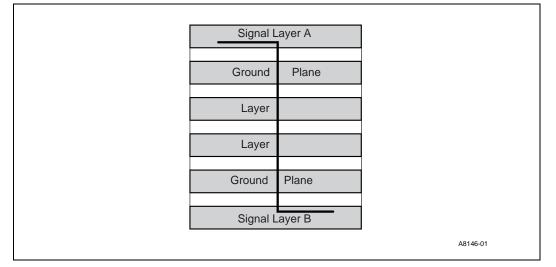

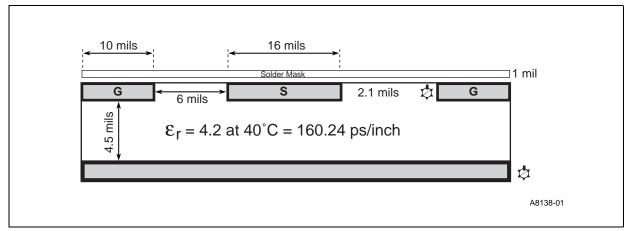

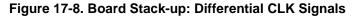

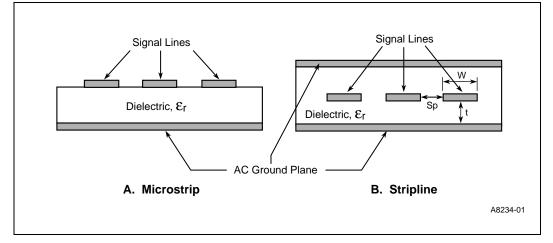

|   | 5.1<br>5.2 | General RecommendationsStack-up Requirement5.2.1Overview5.2.2PCB Material5.2.3Inner Layer Routing5.2.4Impedance Calculation Tools5.2.5Board Stack-Up                                                             | 5-1<br>5-1<br>5-2<br>5-2<br>5-3 |

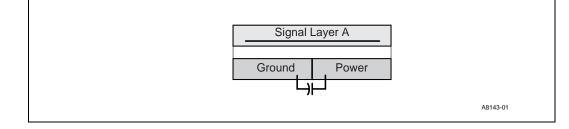

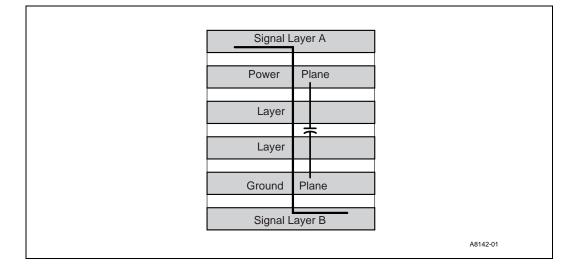

|   | 5.3        | Power Distribution         5.3.1       Reference Planes and PCB Stackup         5.3.1.1       High Frequency Decoupling                                                                                          | 5-5<br>5-6                      |

|   | 5.4        | Decoupling Guidelines for PGA370 Designs         5.4.1       V <sub>CC_CORE</sub> Decoupling Design         5.4.2       V <sub>TT</sub> Decoupling Design         5.4.3       V <sub>REF</sub> Decoupling Design | 5-9<br>5-9                      |

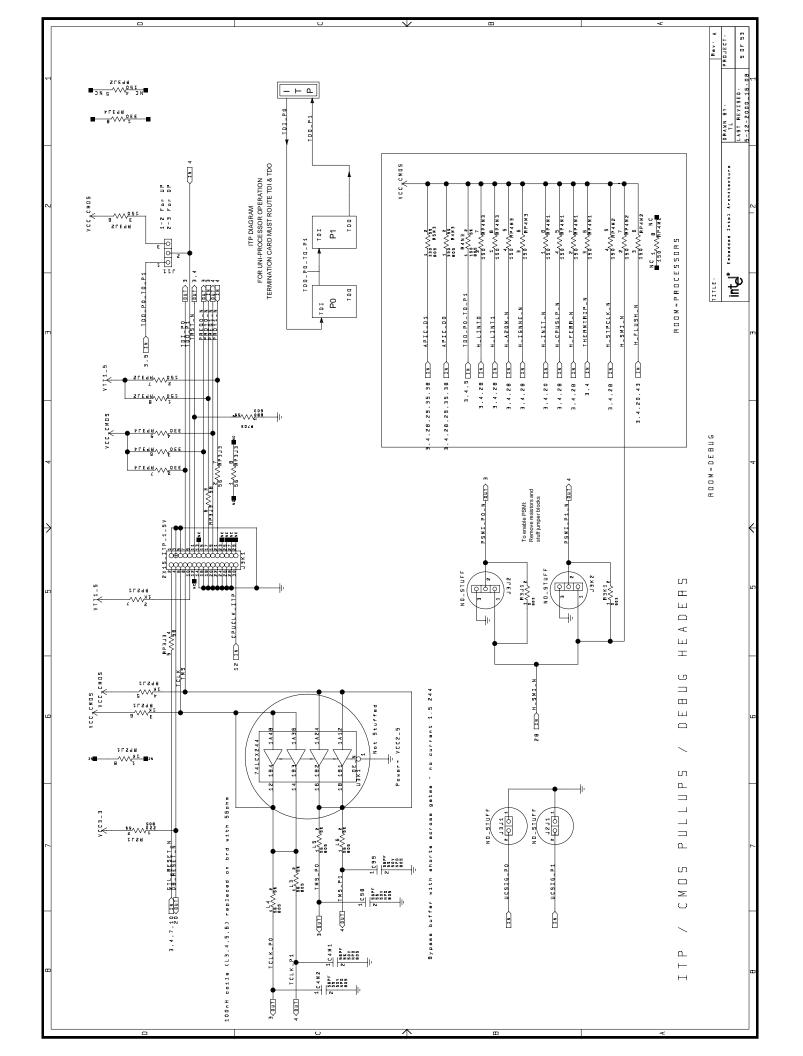

|   | 5.5        | Thermal/EMI Differences         5.5.1       Debug Port Changes                                                                                                                                                   | 5-10<br>5-10                    |

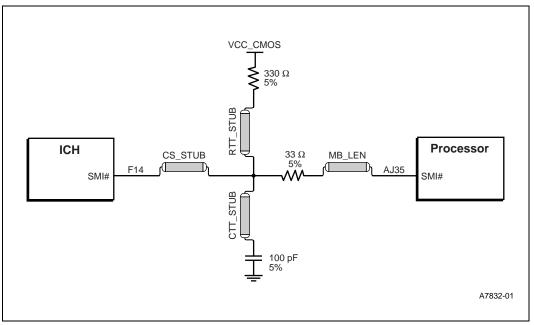

| • | 5.6        | SMI# Layout Guidelines                                                                                                                                                                                           |                                 |

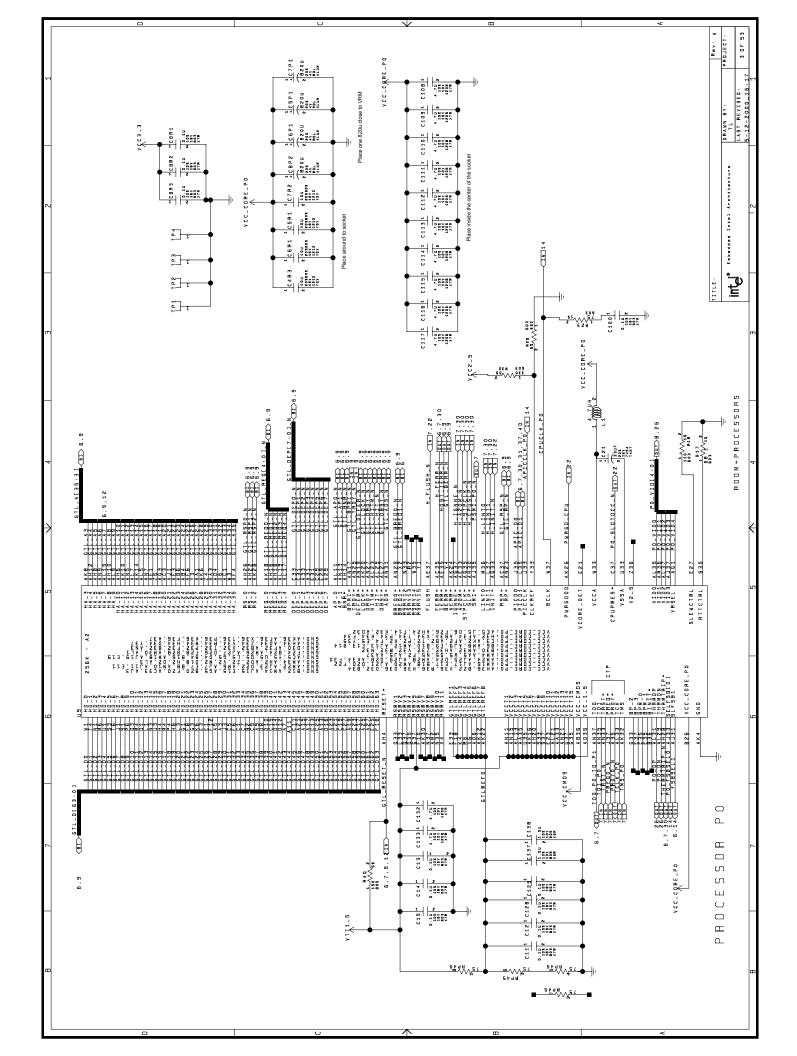

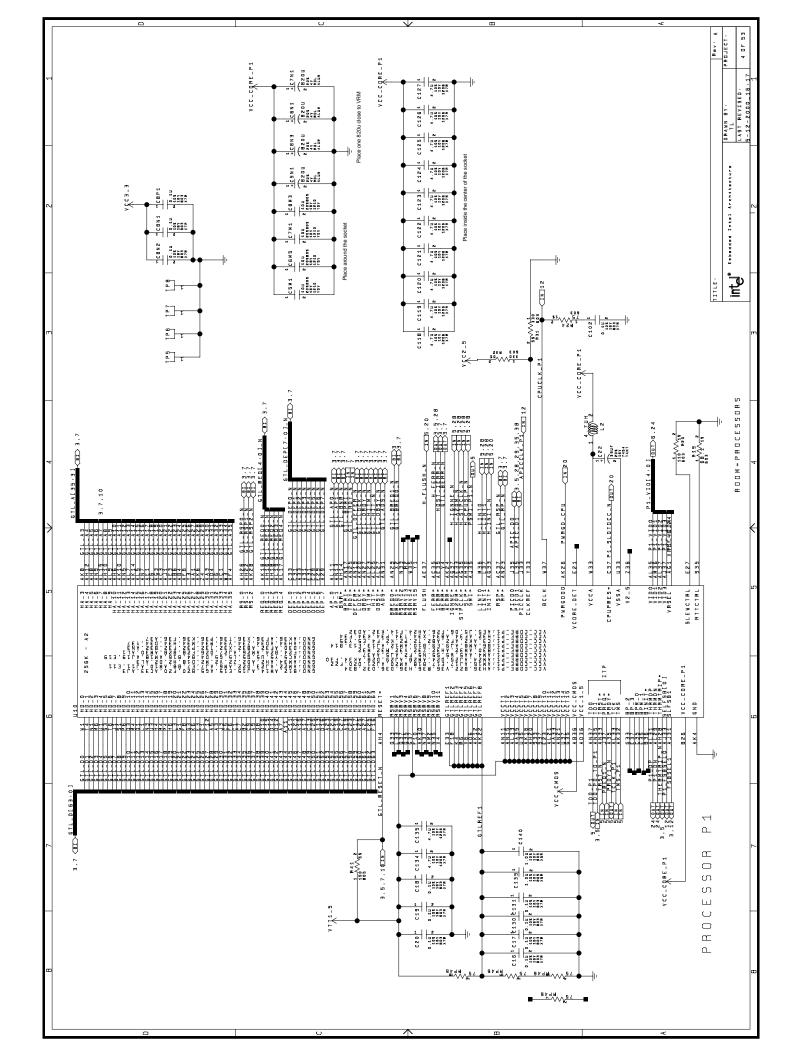

| 6 |            | (FC-PGA) Intel <sup>®</sup> Pentium <sup>®</sup> III Processors                                                                                                                                                  |                                 |

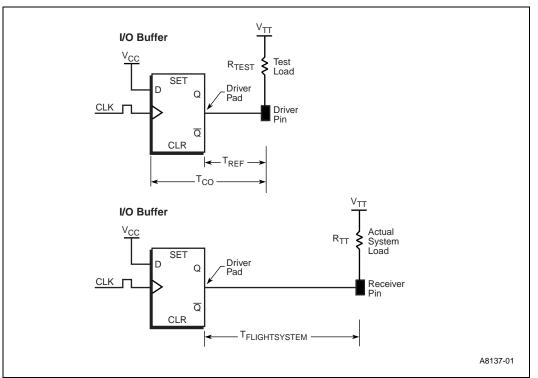

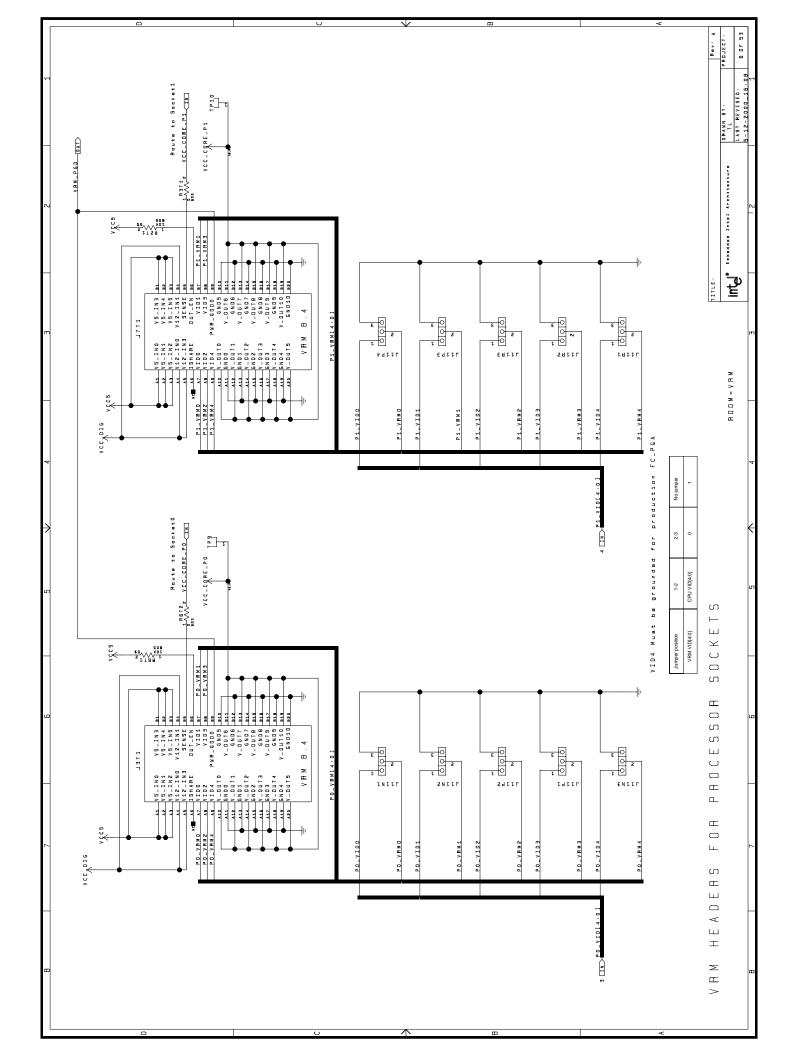

|   | 6.1<br>6.2 | Two-Way FC-PGA Pentium <sup>®</sup> III Processors and Intel <sup>®</sup> 840 Chipset Layout .<br>Definition of Terms                                                                                            | 6-2                             |

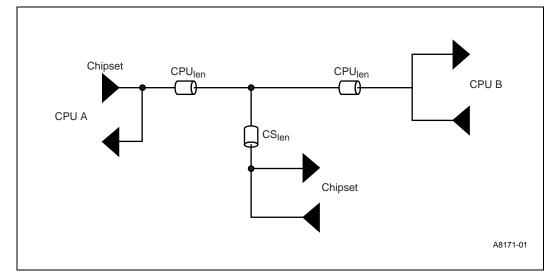

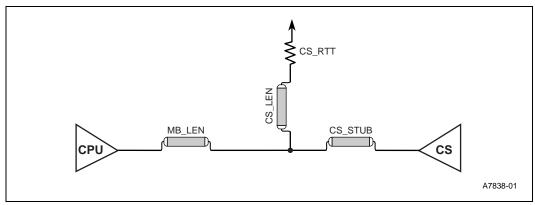

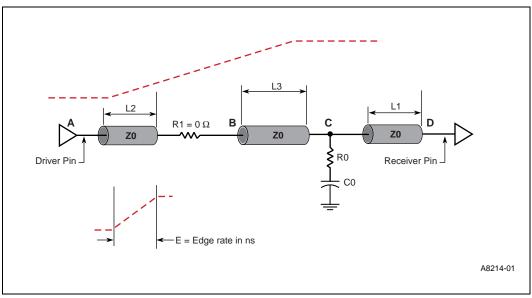

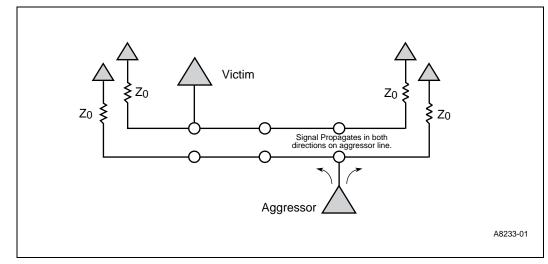

|   |            | <ul> <li>6.2.1 AGTL+ Design Guideline</li> <li>6.2.2 Initial Timing Analysis</li> <li>6.2.3 Dual Processor General Topology</li></ul>                                                                            | 6-5<br>6-8                      |

|   | 6.3        | 6.2.4 Cross-talk Routing Guidelines<br>Processor Overshoot/Undershoot Limits                                                                                                                                     |                                 |

|   | 6.4        | Wired-OR Signals                                                                                                                                                                                                 |                                 |

|   | 6.5        | Signal Return Path Considerations                                                                                                                                                                                | 6-9                             |

|   | 6.6        | Intel Pentium III Processor (FC-PGA) Pull-Up Values                                                                                                                                                              | 6-10                            |

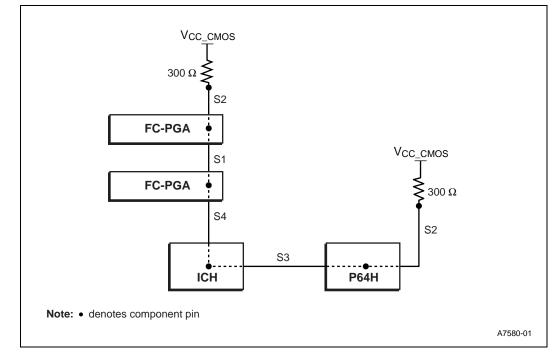

|   | 6.7        | <ul> <li>APIC / CMOS Bus</li> <li>6.7.1 Two-way FC-PGA and Intel 840 Chipset APIC Bus<br/>Layout Guidelines</li> </ul>                                                                                           |                                 |

|   | 6.8        | Processor THERMTRIP# Pin Connection                                                                                                                                                                              |                                 |

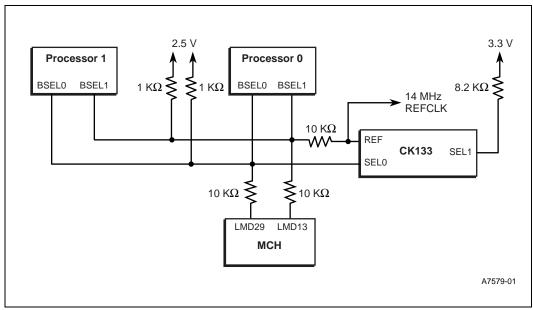

|   | 6.9        | BSEL[1:0] Implementation                                                                                                                                                                                         | -                               |

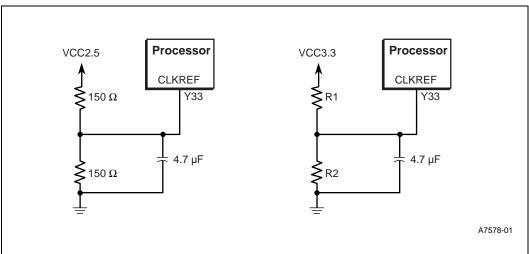

|   | 6.10       | CLKREF Circuit Implementation                                                                                                                                                                                    |                                 |

|   | 6.11       | On-die R <sub>TT</sub> Considerations                                                                                                                                                                            |                                 |

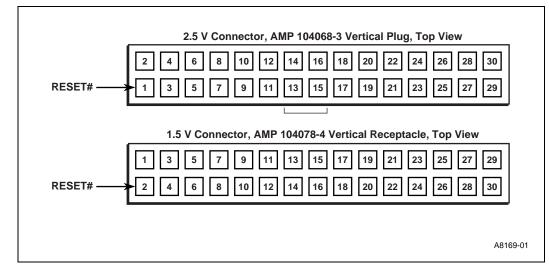

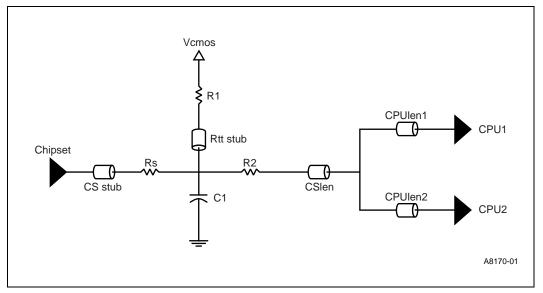

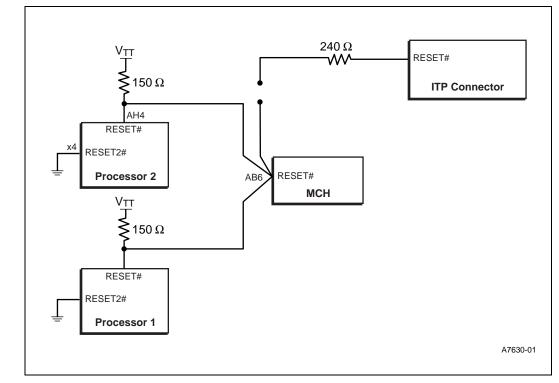

|   |            | <ul> <li>6.11.1 Connecting RESET# in Dual Processor PGA370 Designs</li> <li>6.11.2 AGTL+ Reset Layout Topology</li> </ul>                                                                                        | 6-14                            |

| 7 | Single     | e (FC-PGA) Intel <sup>®</sup> Pentium <sup>®</sup> III Processors                                                                                                                                                | 7-1                             |

|   | 7.1        | One-Way FC-PGA Pentium <sup>®</sup> III Processors and Intel <sup>®</sup> 840 Chipset Layout.                                                                                                                    | 7-1                             |

|   | 7.2        | Definition of Terms                                                                                                                                                                                              | 7-2                             |

|   | 7.3        | AGTL+ Design Methodology                                                                                                                                                                                         |                                 |

|   | 7.4        | Initial Timing Analysis<br>7.4.1 Flight Time Calculation                                                                                                                                                         |                                 |

|   | 7.5        | General Topology                                                                                                                                                                                                 |                                 |

|   | 7.6        | Changes in Signal Connectivity for Uniprocessor Systems                                                                                                                                                          |                                 |

|   | 7.7        | Connecting RESET# in Uniprocessor PGA370 Designs                                                                                                                                                                 |                                 |

|   | 7.8        | SMI# Layout Guidelines                                                                                                                                                                                           | 7-9                             |

#### Contents

# intel®

| . 1 | z |   | ) |  |

|-----|---|---|---|--|

|     | 7 | 1 | 2 |  |

| 1   |   |   | , |  |

9

10

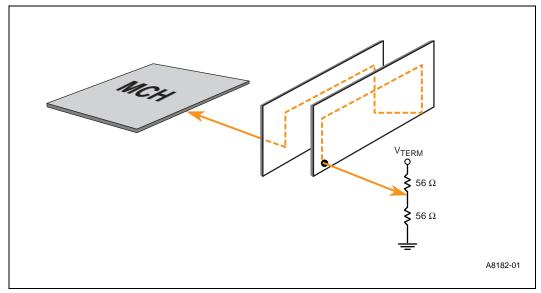

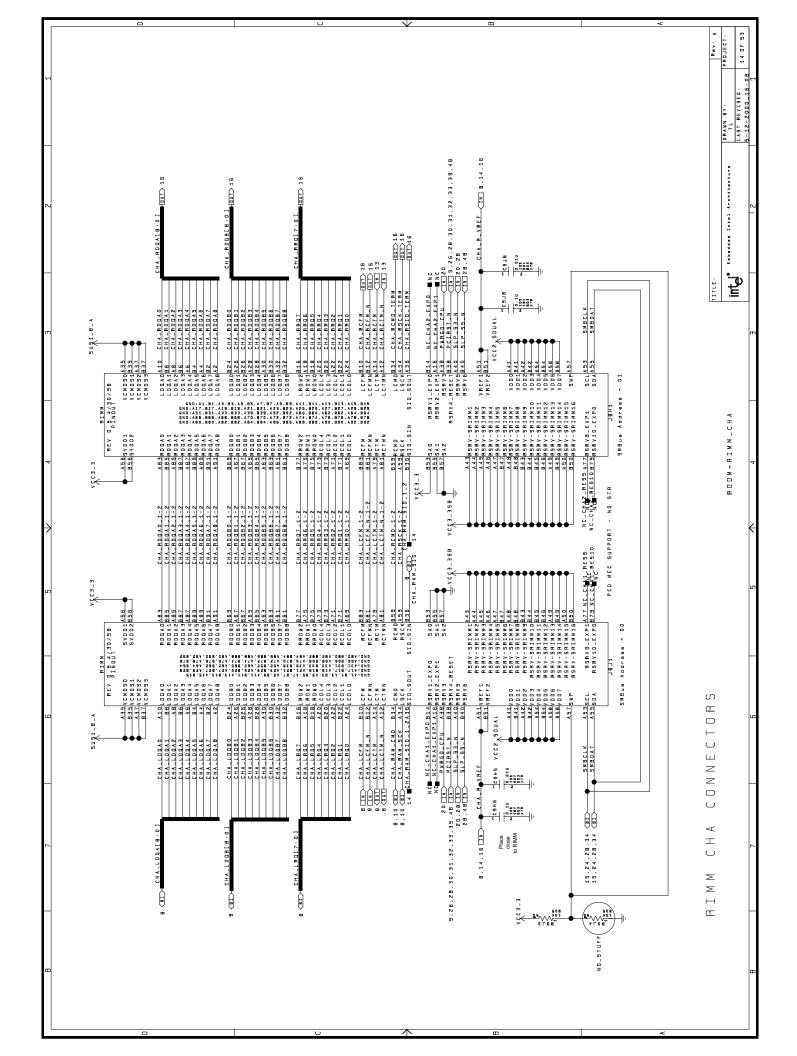

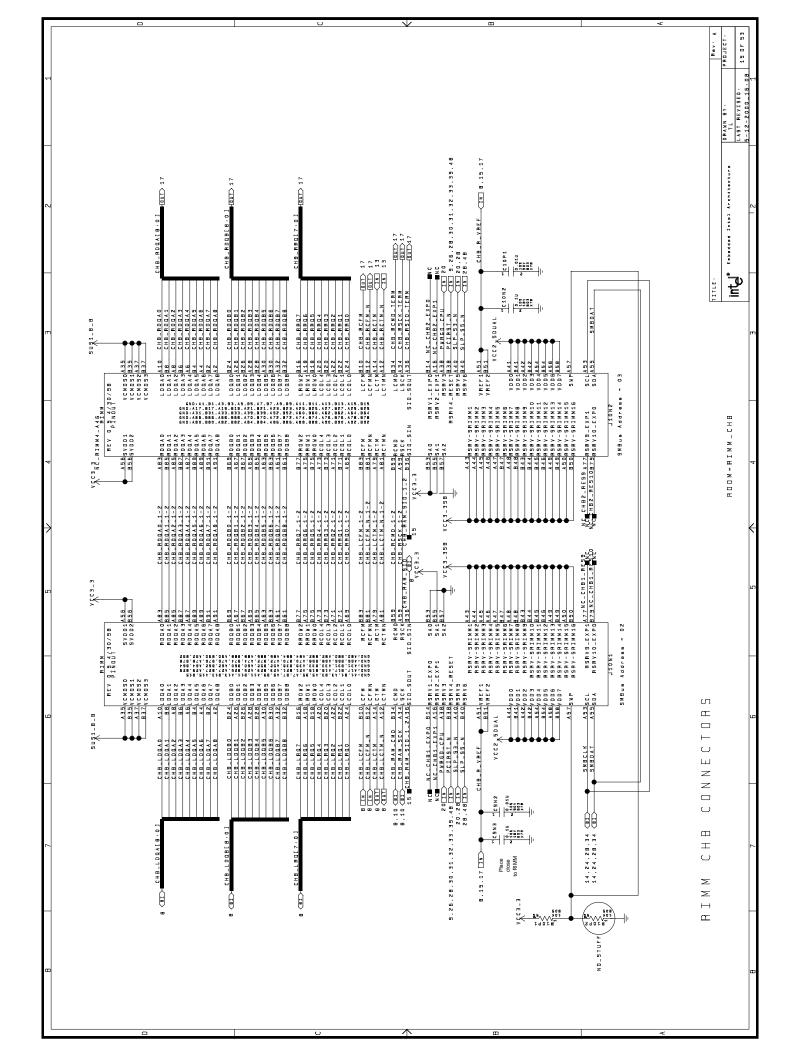

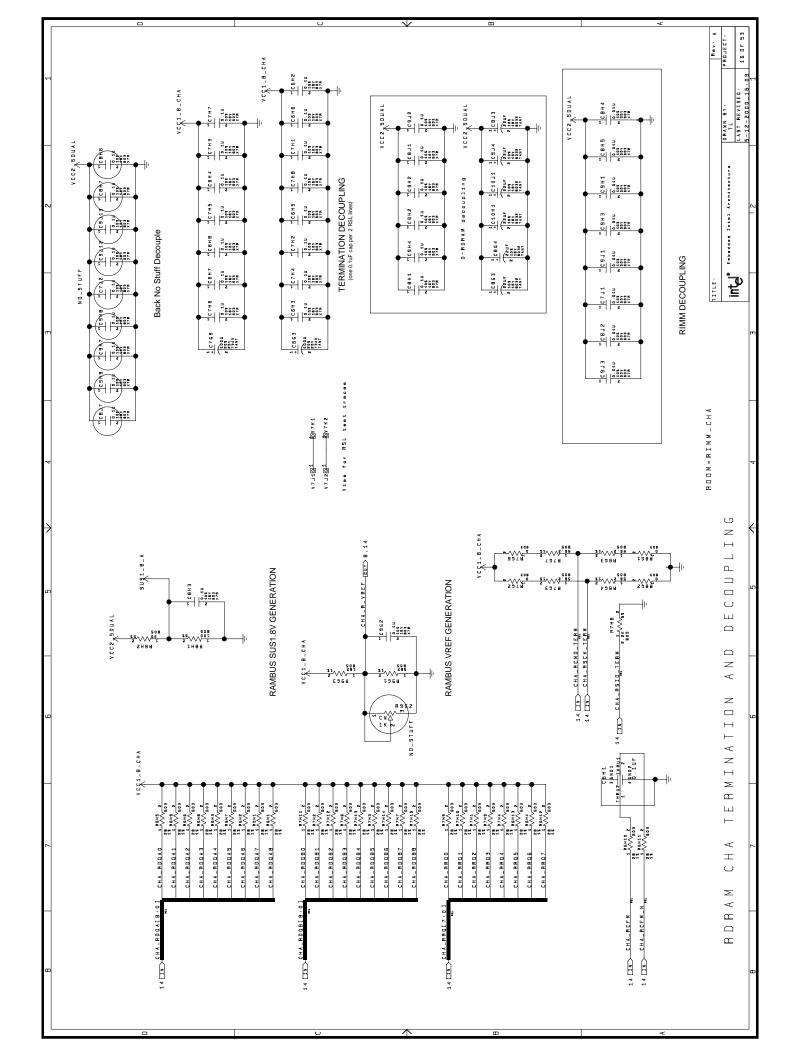

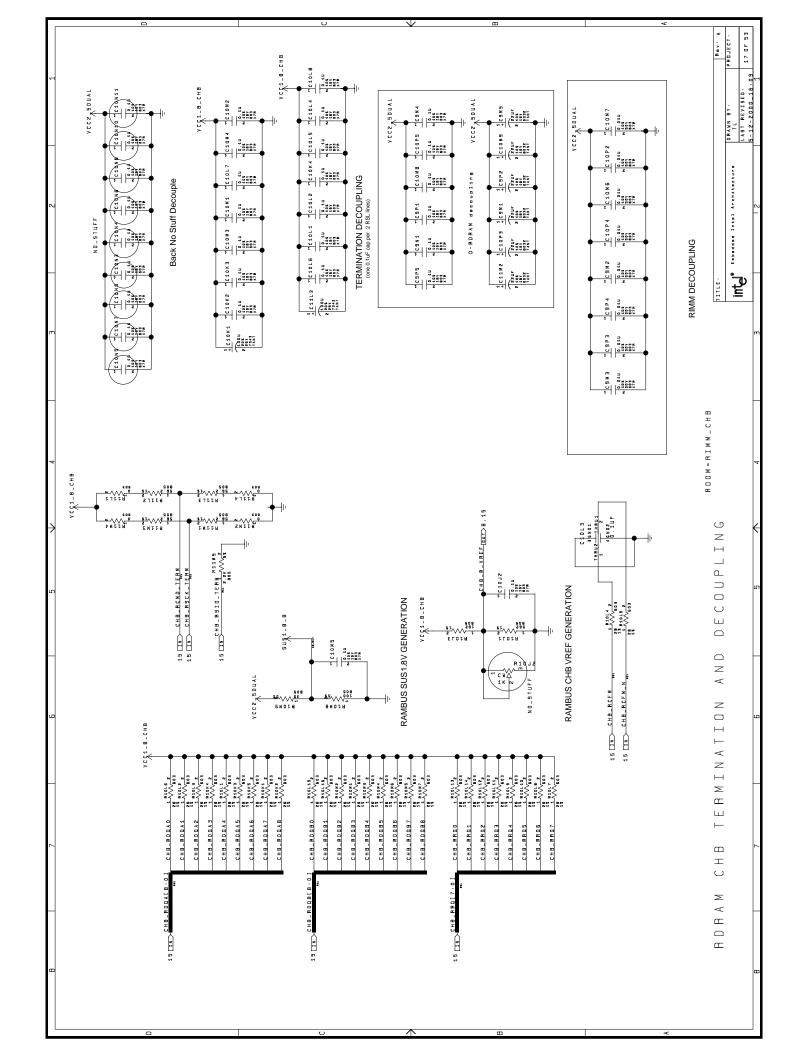

| Mem  | ory Interface.  |                                                         | 8-1  |

|------|-----------------|---------------------------------------------------------|------|

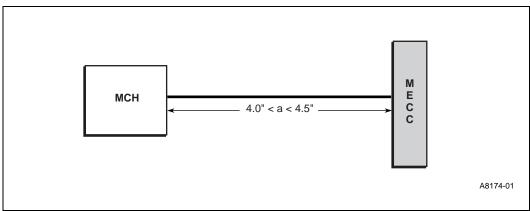

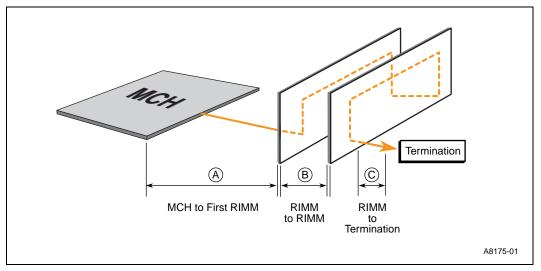

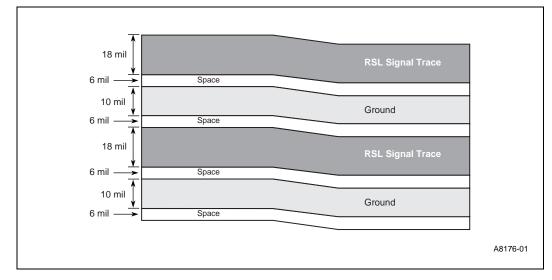

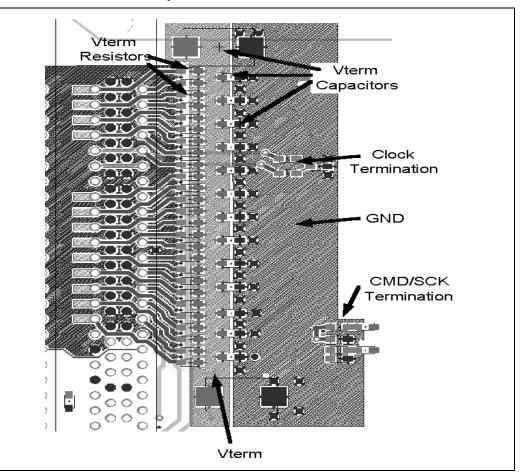

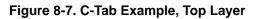

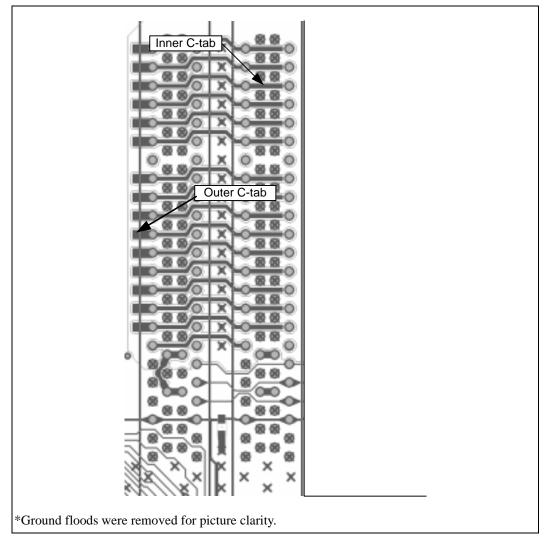

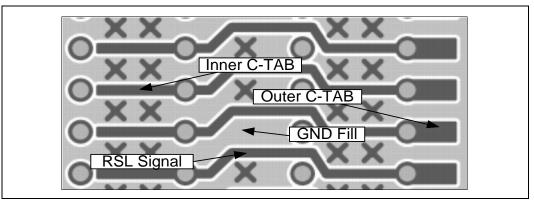

| 8.1  | Memory Desig    | n with MEC/MECC (Outer Layer Routing)                   | 8-2  |

| 8.2  |                 | Motherboard                                             |      |

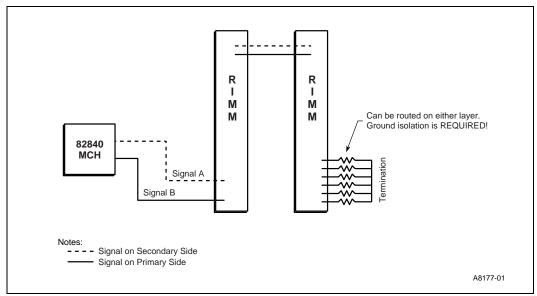

|      |                 | Signals                                                 |      |

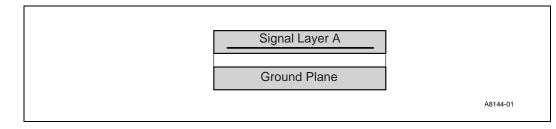

|      |                 | Signal Layer Alternation                                |      |

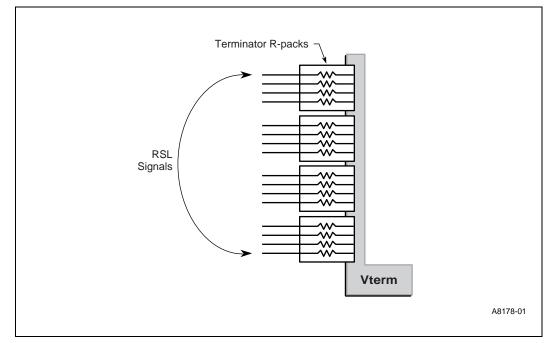

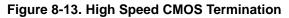

|      |                 | Signal Termination                                      |      |

|      |                 | RAM Connector Compensation                              |      |

|      |                 | ct RDRAM Ground Plane Reference                         |      |

|      |                 | th Matching Method                                      |      |

|      | 8.2.6.1         |                                                         |      |

|      | 8.2.6.2         |                                                         |      |

|      | 8.2.6.3         |                                                         |      |

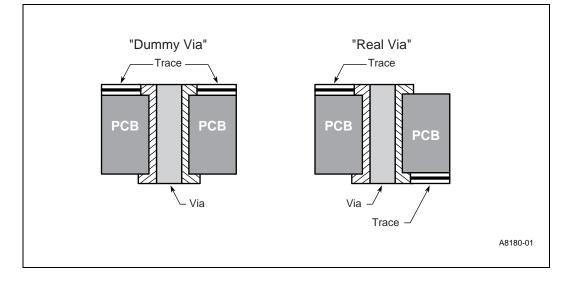

|      | 8.2.7 Via (     | Compensation                                            |      |

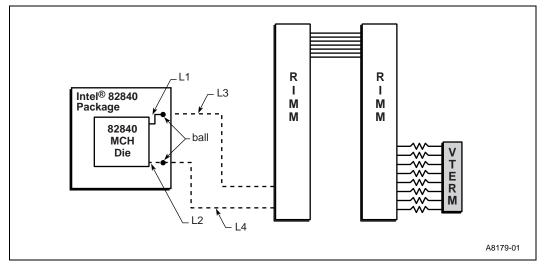

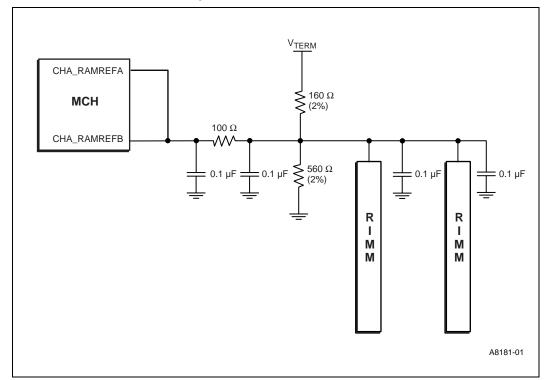

|      | 8.2.8 Dire      | ct RDRAM Reference                                      | 8-13 |

|      | 8.2.9 High      | Speed CMOS Routing                                      | 8-13 |

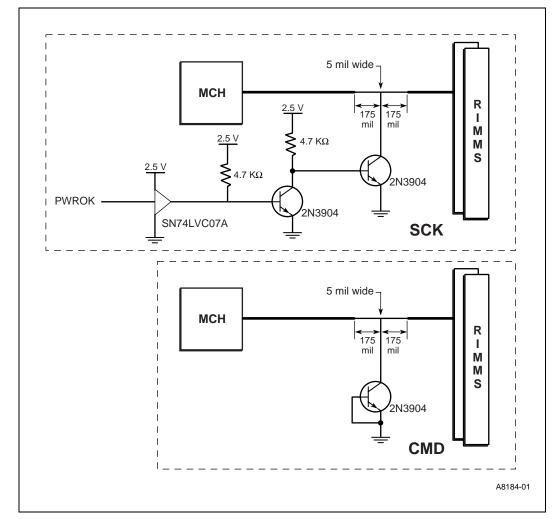

|      | -               | Routing                                                 |      |

|      |                 | pend-to-RAM Shunt Transistor                            |      |

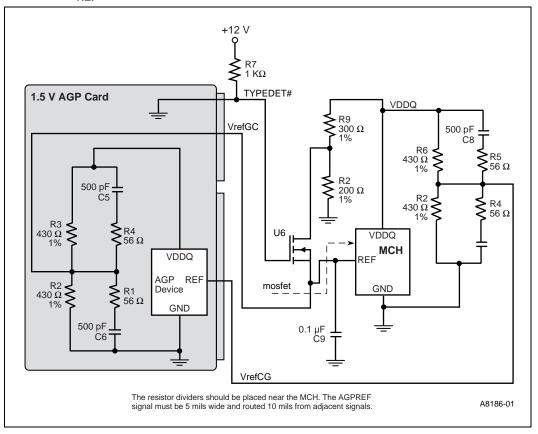

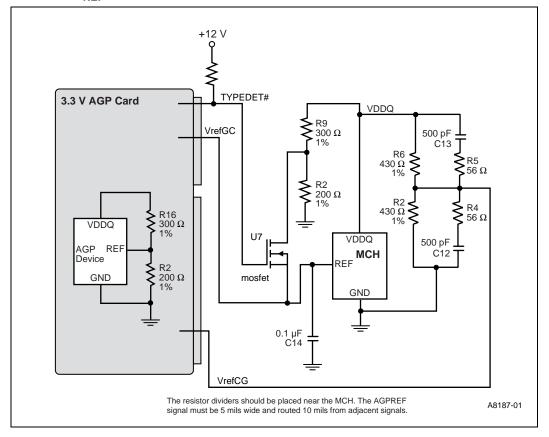

| AGP  | 2.0             |                                                         | 9-1  |

| 9.1  |                 | Routing Guidelines                                      |      |

|      |                 | pupling                                                 |      |

|      |                 | und Reference                                           |      |

| 9.2  |                 | nain Routing Guidelines                                 |      |

| 9.3  |                 | Domain Routing Guidelines                               |      |

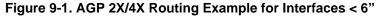

|      |                 | P Interfaces Signals < 6" Routing Guidelines            |      |

|      |                 | P Interface Signals > 6" and < 7.25" Routing Guidelines |      |

|      |                 | PRouting Summary                                        |      |

|      |                 | P Clock Skew                                            |      |

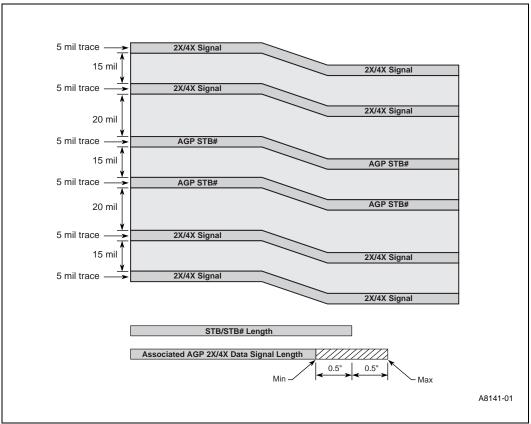

|      |                 | <sub>o</sub> and TYPEDET#                               |      |

|      |                 | Generation                                              |      |

|      |                 | pensation                                               |      |

|      |                 | ,<br>Pull-ups/Pull-down on AGP Signals                  |      |

|      |                 | Signal Voltage Tolerance List                           |      |

|      |                 | <sup>o</sup> Connector                                  |      |

|      |                 | sed AGP interface                                       |      |

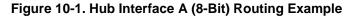

| Hub  | Interface       |                                                         | 10-1 |

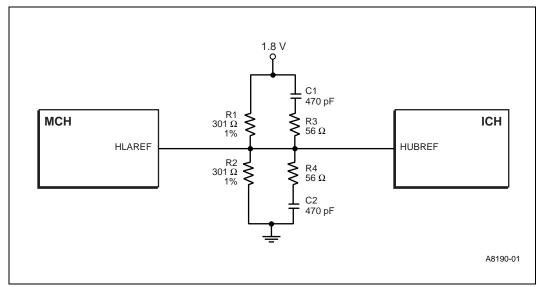

| 10.1 | Hub Interface / | A (8-bit) to ICH                                        | 10-2 |

|      |                 | Interface A Data Signals                                | 10-2 |

|      |                 | Interface A Strobe Signals                              |      |

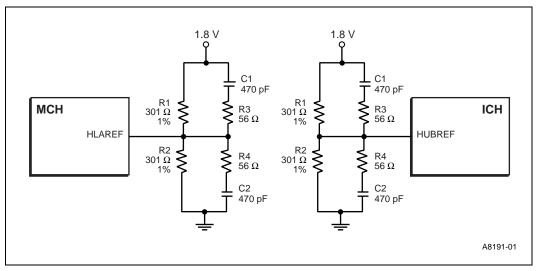

|      |                 | Interface A (HLAREF) Generation/Distribution            |      |

|      |                 | Interface A Compensation                                |      |

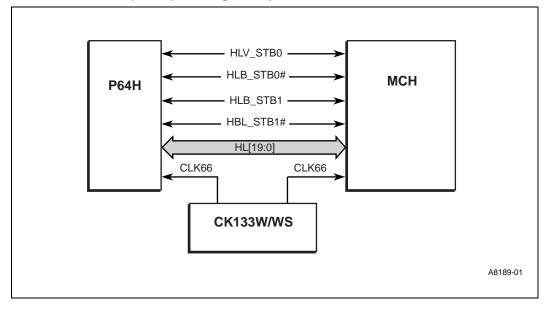

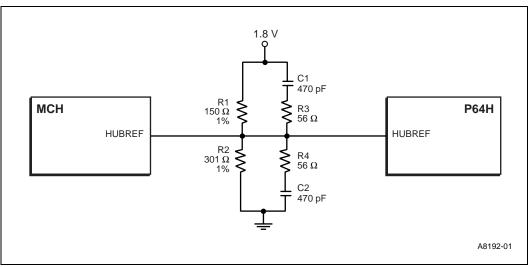

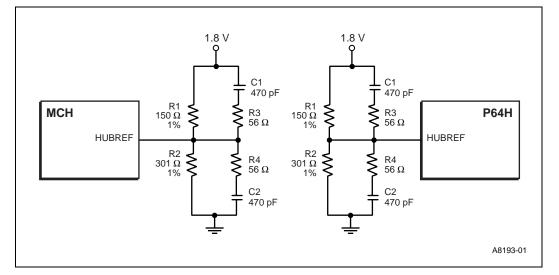

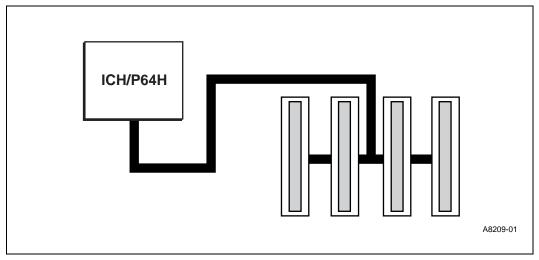

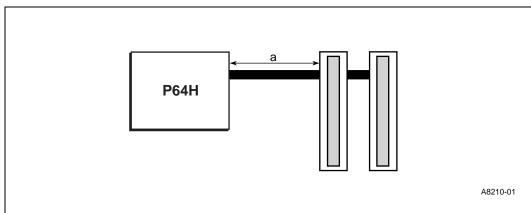

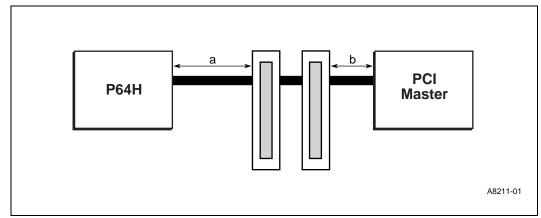

| 10.2 |                 | 3 (16-bit) to P64H                                      |      |

|      |                 | a Signals                                               |      |

|      |                 | be Signals                                              |      |

|      |                 | Interface B HUBREF Generation/Distribution              |      |

|      |                 | _RCOMP Signal                                           |      |

|      |                 | sed Hub Interface B                                     |      |

|      |                 |                                                         |      |

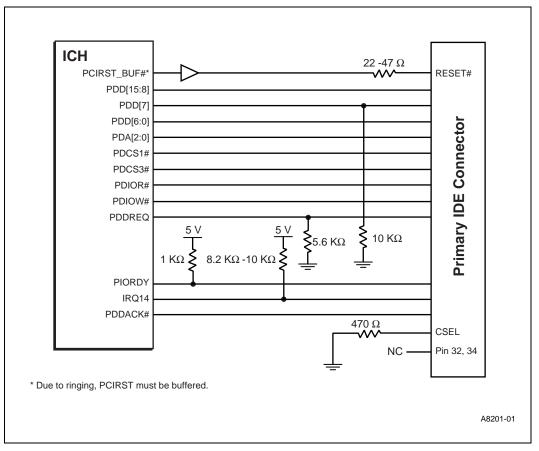

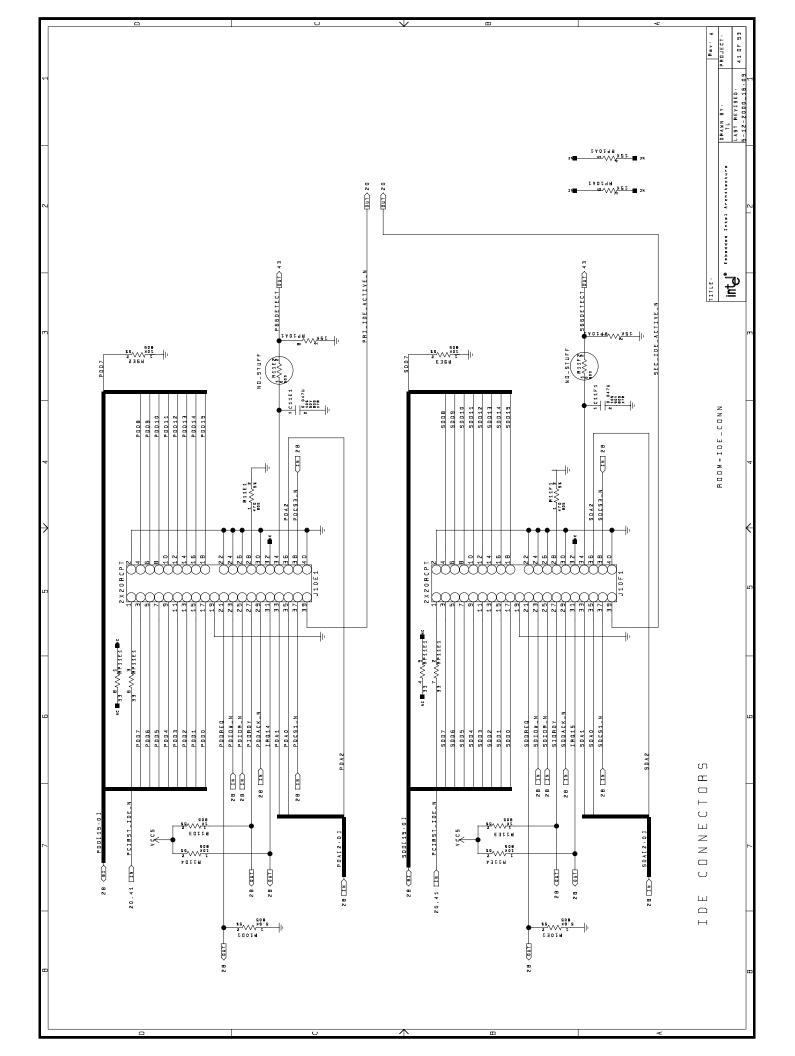

| 11 | Ultra        | 1 ATA/66                                                                                                                      | .11-1 |

|----|--------------|-------------------------------------------------------------------------------------------------------------------------------|-------|

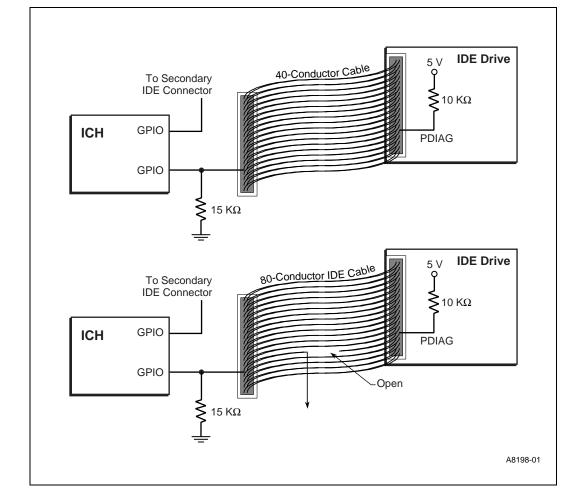

|    | 11.1<br>11.2 | Cable Requirement<br>Ultra ATA/66 Cable Detection                                                                             |       |

|    |              | 11.2.1 Host Side Detection-BIOS Detects Cable Type Using GPIOs                                                                |       |

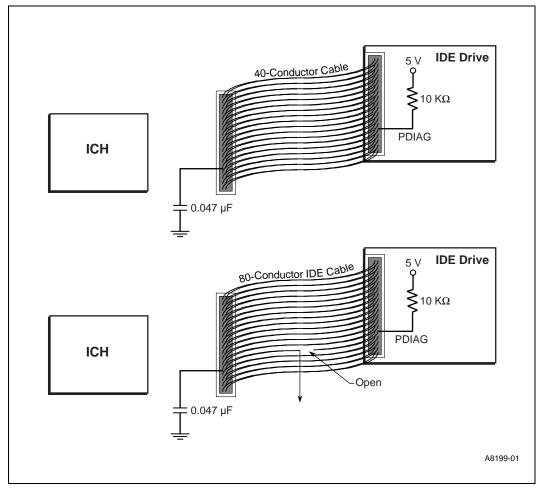

|    | 11.3         | 11.2.2 Device Side Detection-BIOS Queries IDE Drive for Cable Type<br>Layout for Host Side and Driver Side Cable<br>Detection |       |

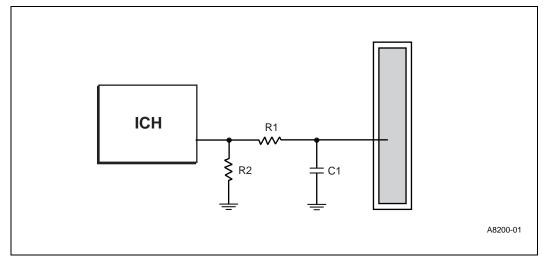

|    | 11.4         | Guidelines                                                                                                                    |       |

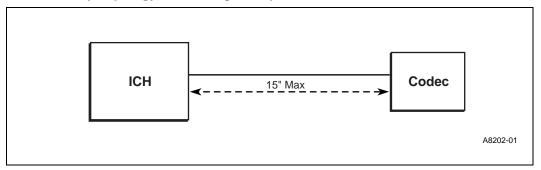

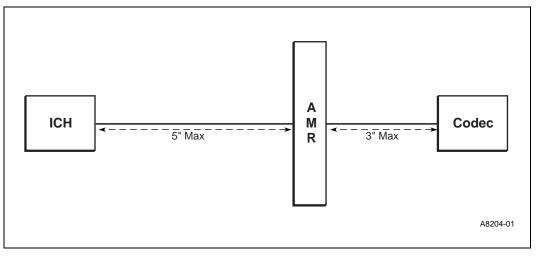

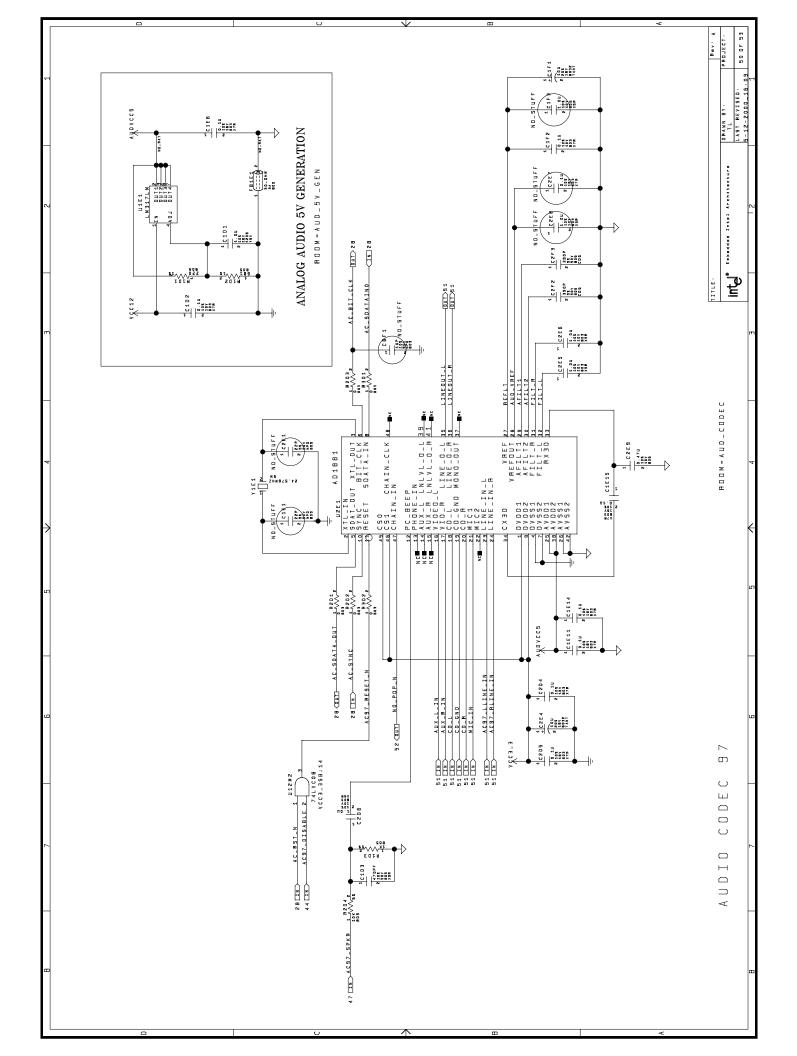

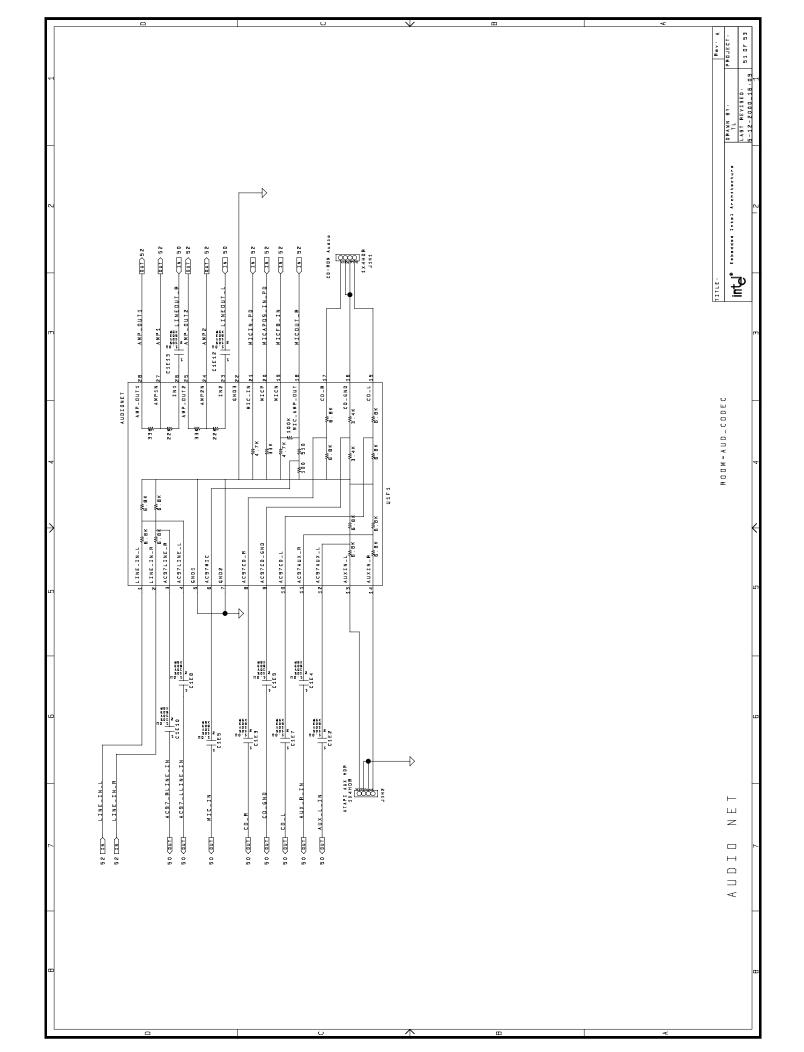

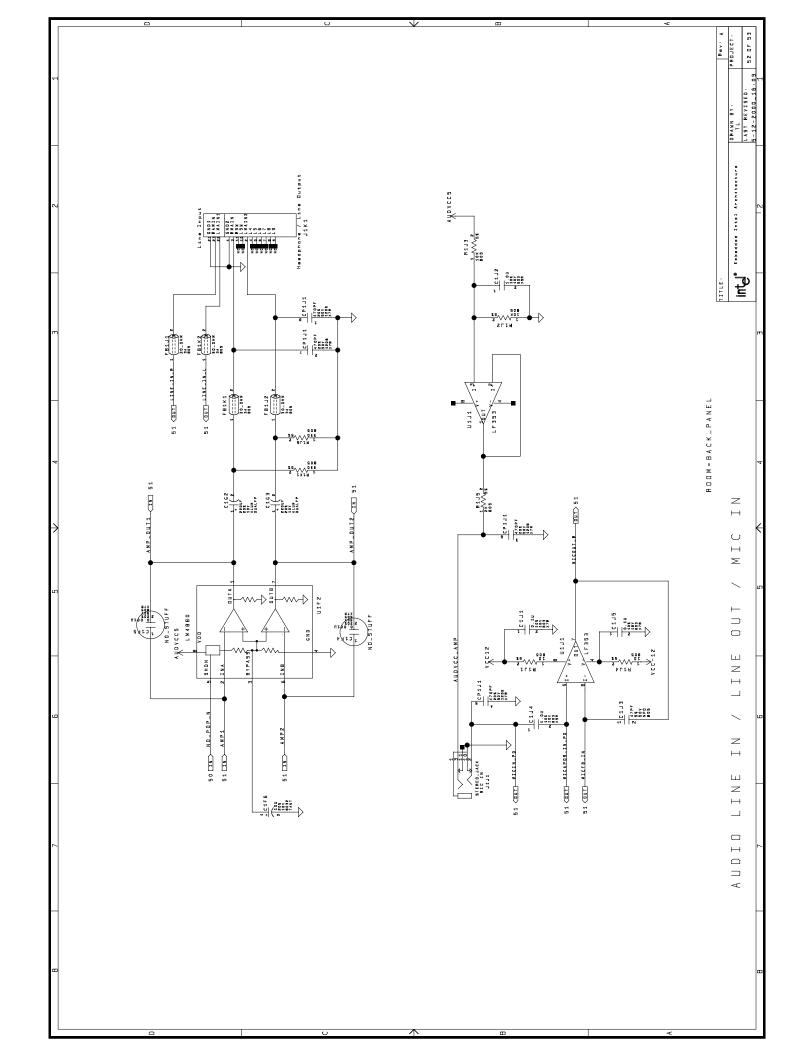

| 12 | AC 'S        | 97                                                                                                                            | .12-1 |

|    | 12.1         | AC '97 Codec-only                                                                                                             |       |

|    | 12.2         | Audio/Modem Riser Specification                                                                                               |       |

|    | 12.3         | AC '97 Signal Quality Requirements                                                                                            |       |

|    | 12.4         | AC '97 Motherboard Implementation                                                                                             |       |

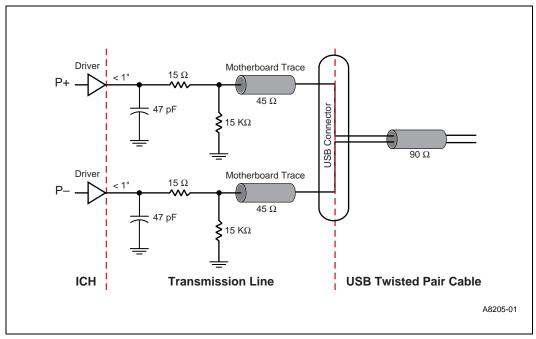

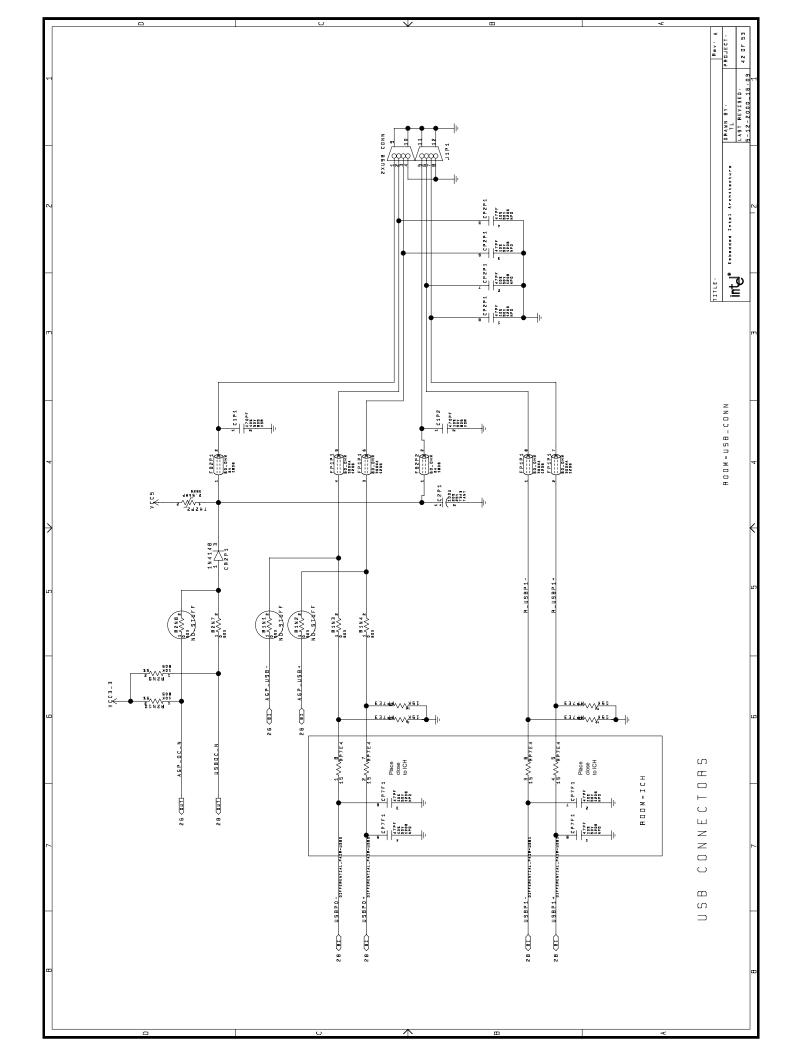

| 13 | Unive        | ersal Serial Bus (USB)                                                                                                        | .13-1 |

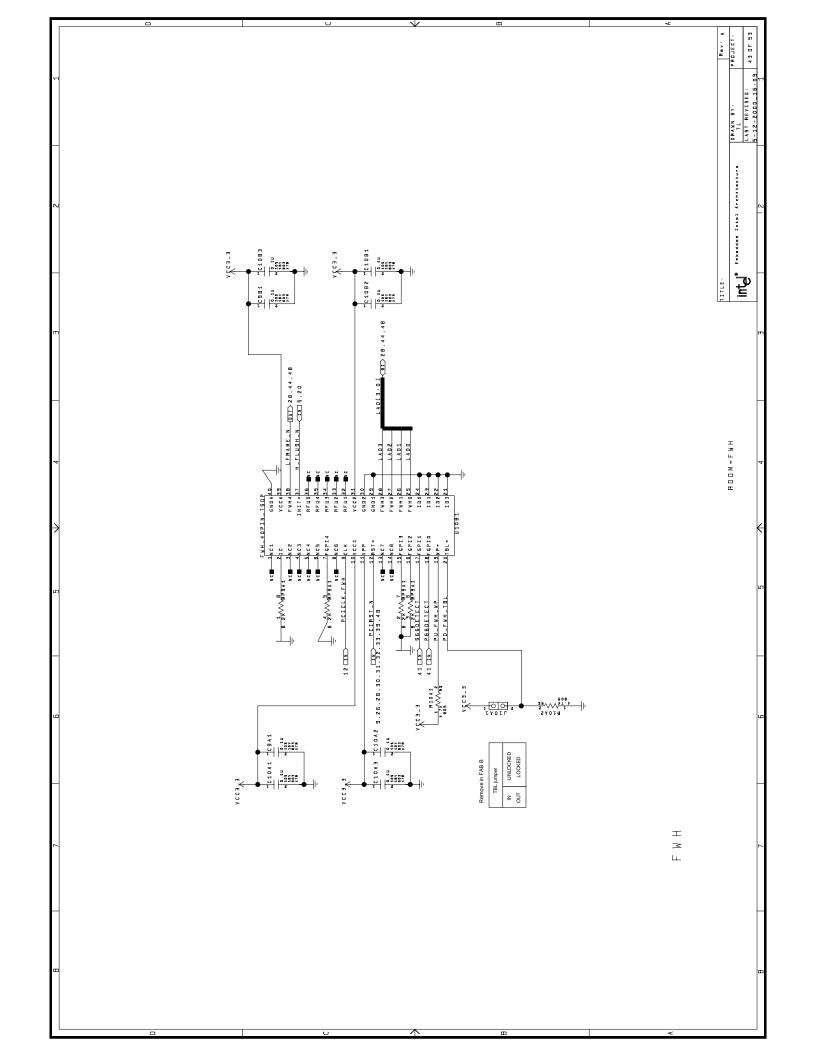

| 14 | Low          | Pin Count Interface (LPC)/FWH                                                                                                 | .14-1 |

|    | 14.1         | In Circuit FWH Programming                                                                                                    |       |

|    | 14.2         | FWH V <sub>PP</sub> Design Guidelines                                                                                         |       |

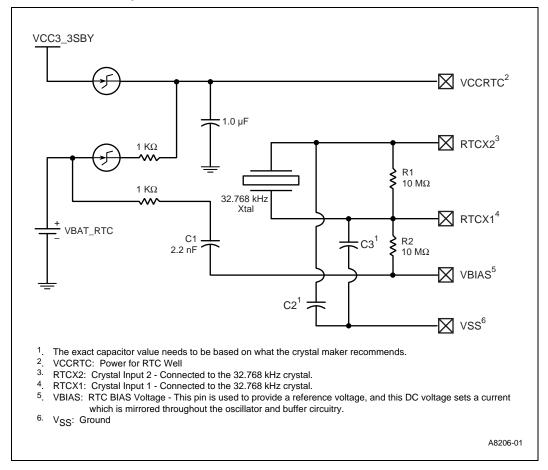

| 15 | RTC          |                                                                                                                               | .15-1 |

|    | 15.1         | RTC Crystal                                                                                                                   | .15-1 |

|    | 15.2         | External Capacitors                                                                                                           |       |

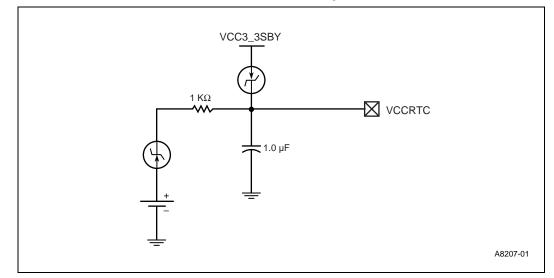

|    | 15.3         | RTC External Battery Connection                                                                                               |       |

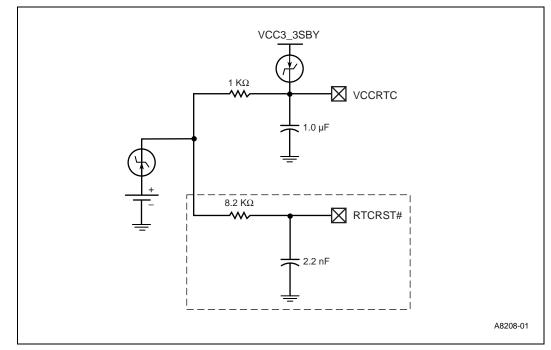

|    | 15.4         | RTC External RTCRST Circuit                                                                                                   |       |

|    | 15.5         | VBIAS Clarification                                                                                                           |       |

|    |              | 15.5.1 RTC Routing Guidelines                                                                                                 |       |

|    | 501          | 15.5.2 VBIAS DC Voltage and Noise Measurements                                                                                |       |

| 16 |              |                                                                                                                               |       |

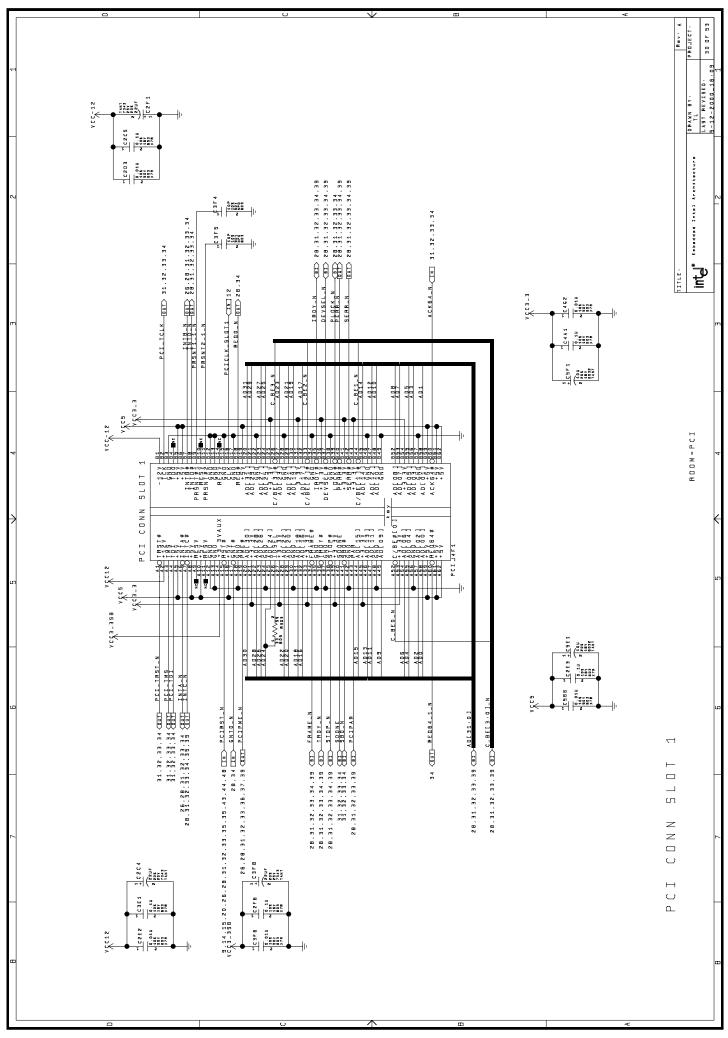

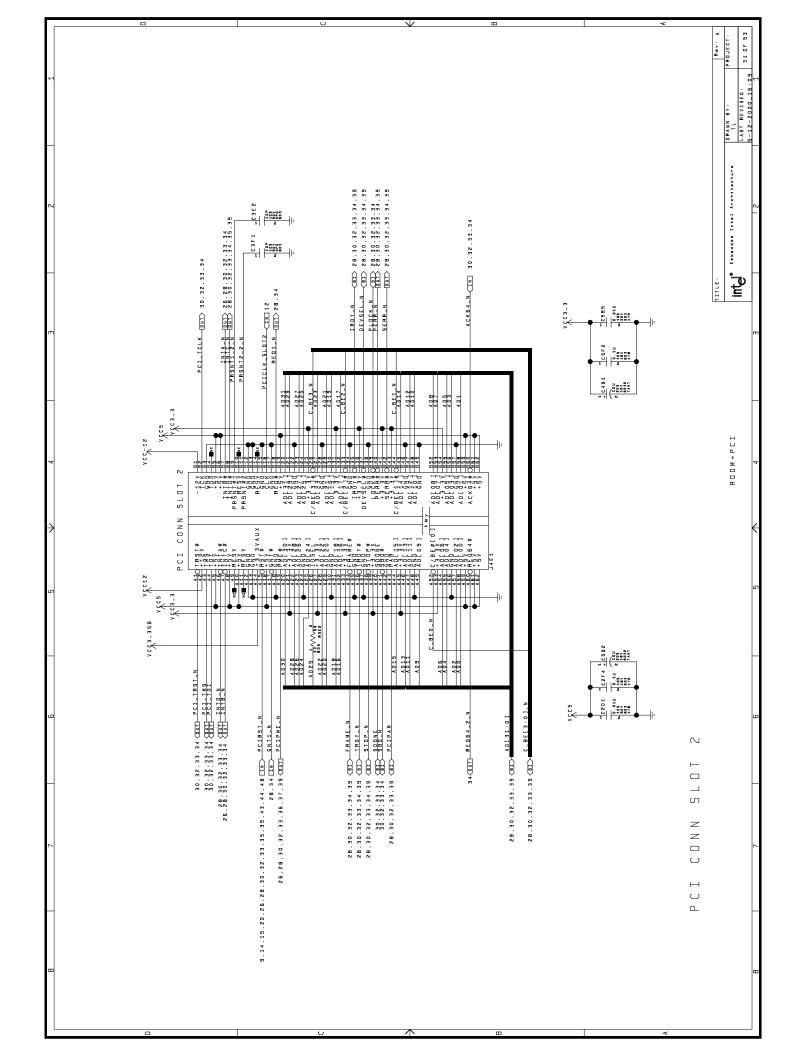

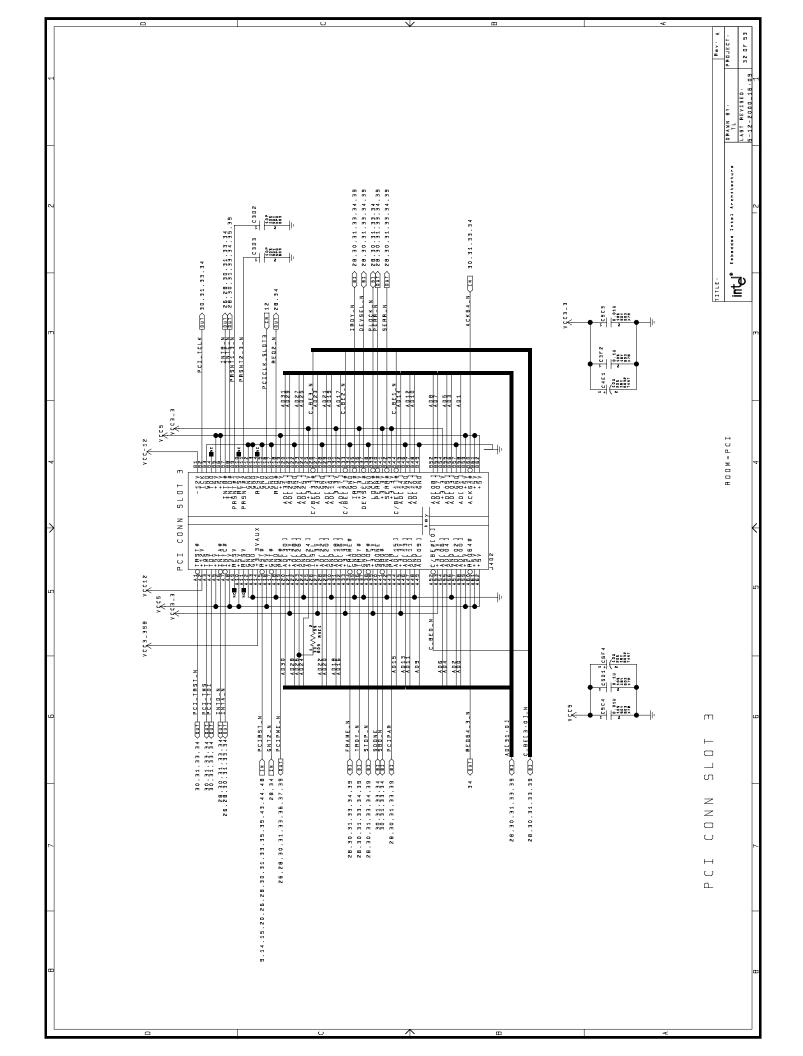

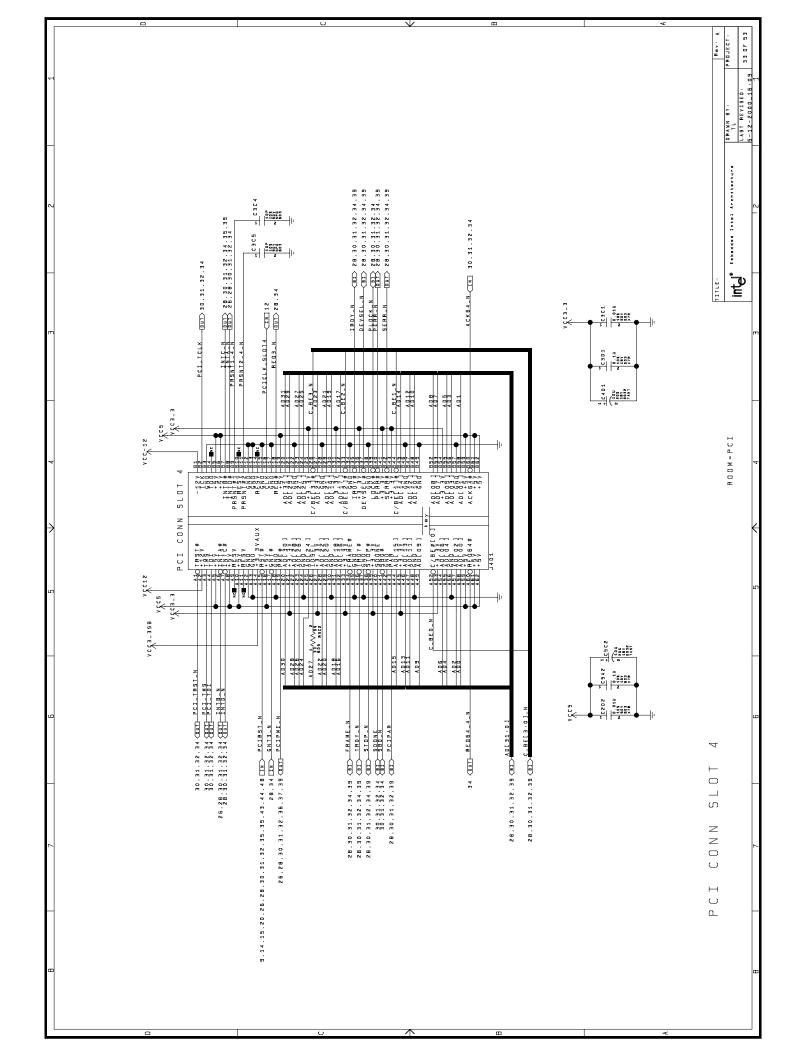

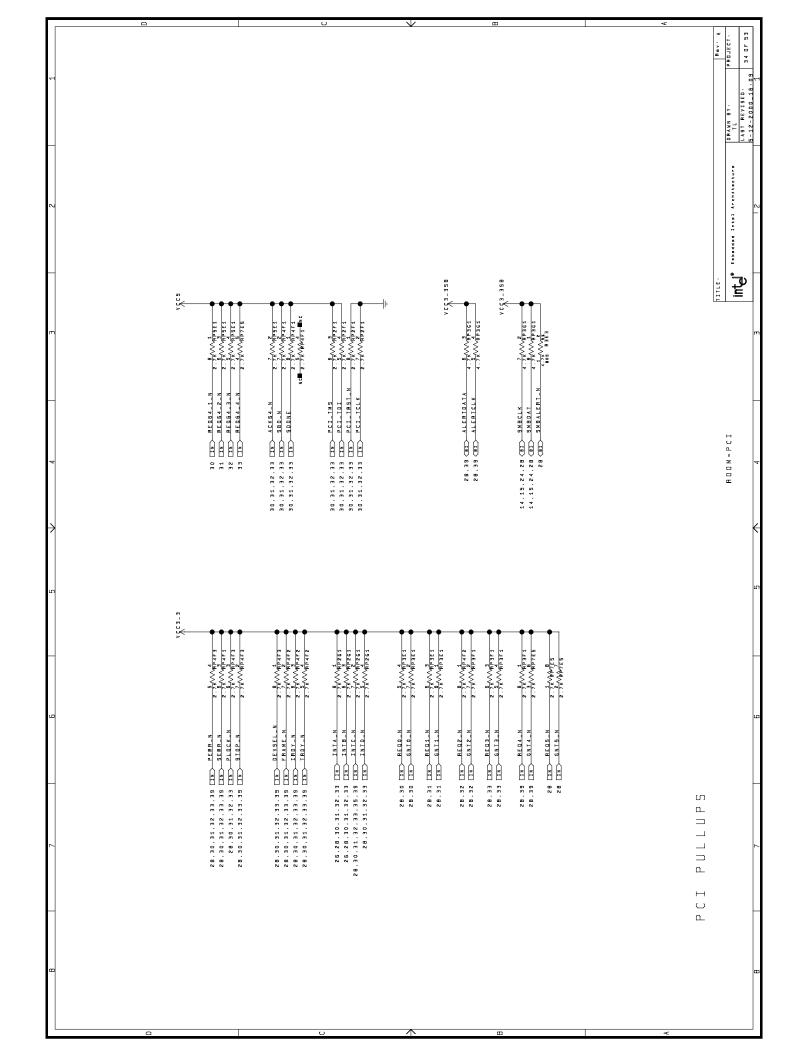

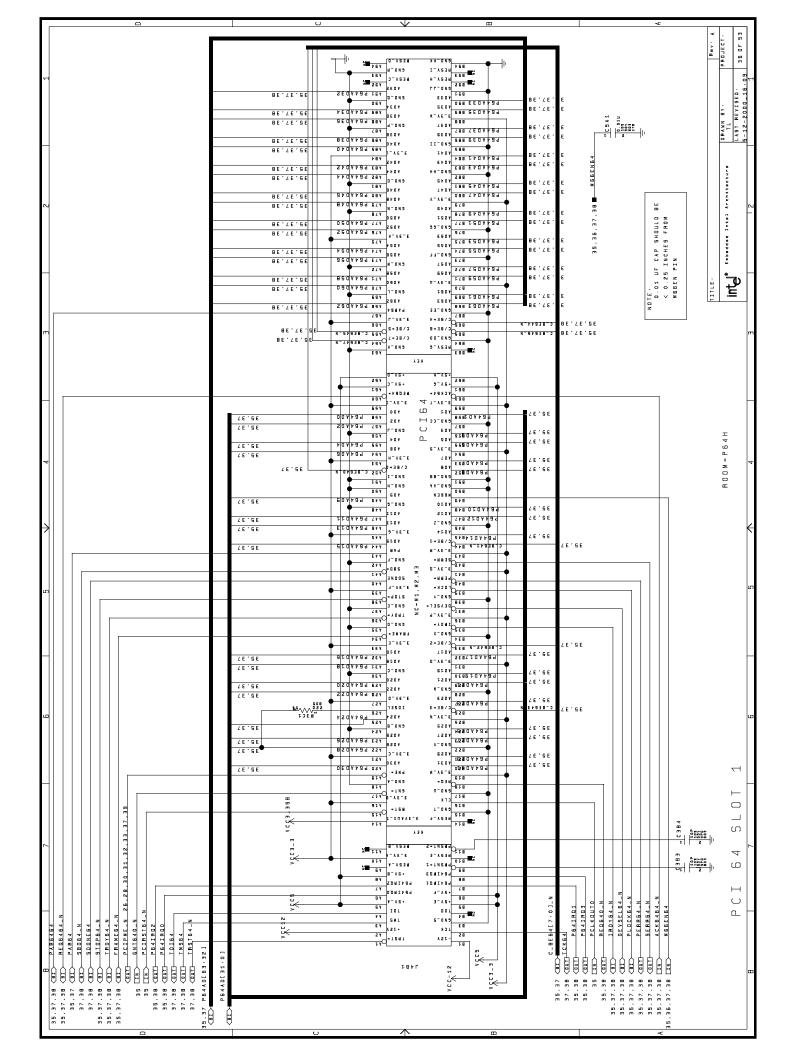

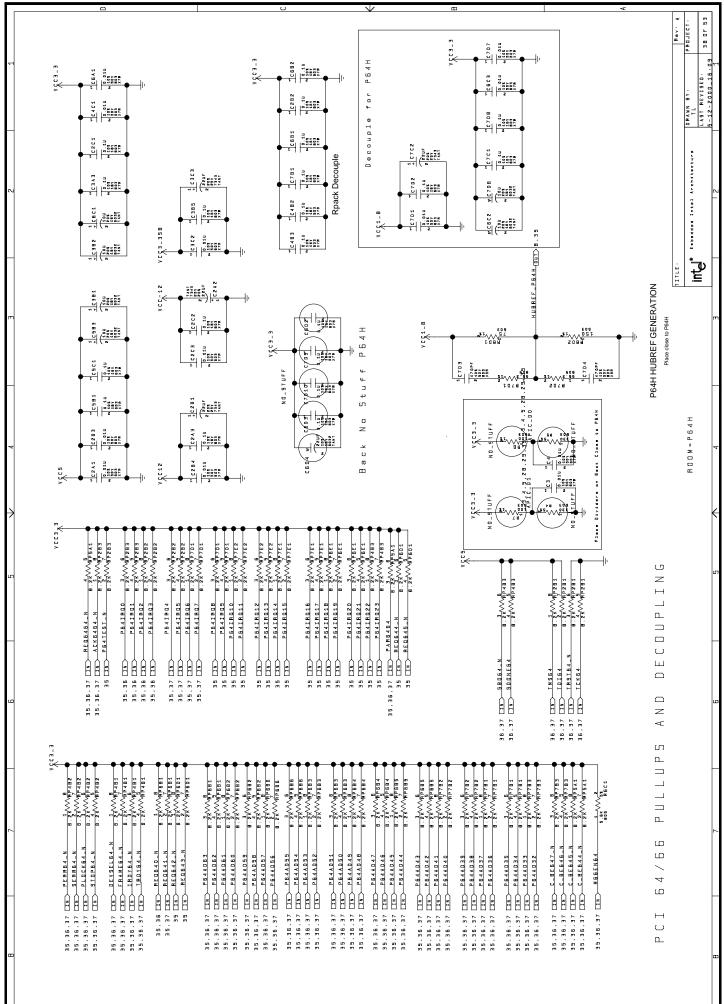

|    | 16.1         | PCI 33 MHz Guidelines                                                                                                         |       |

|    | 16.2         | PCI 66 MHz Guidelines                                                                                                         |       |

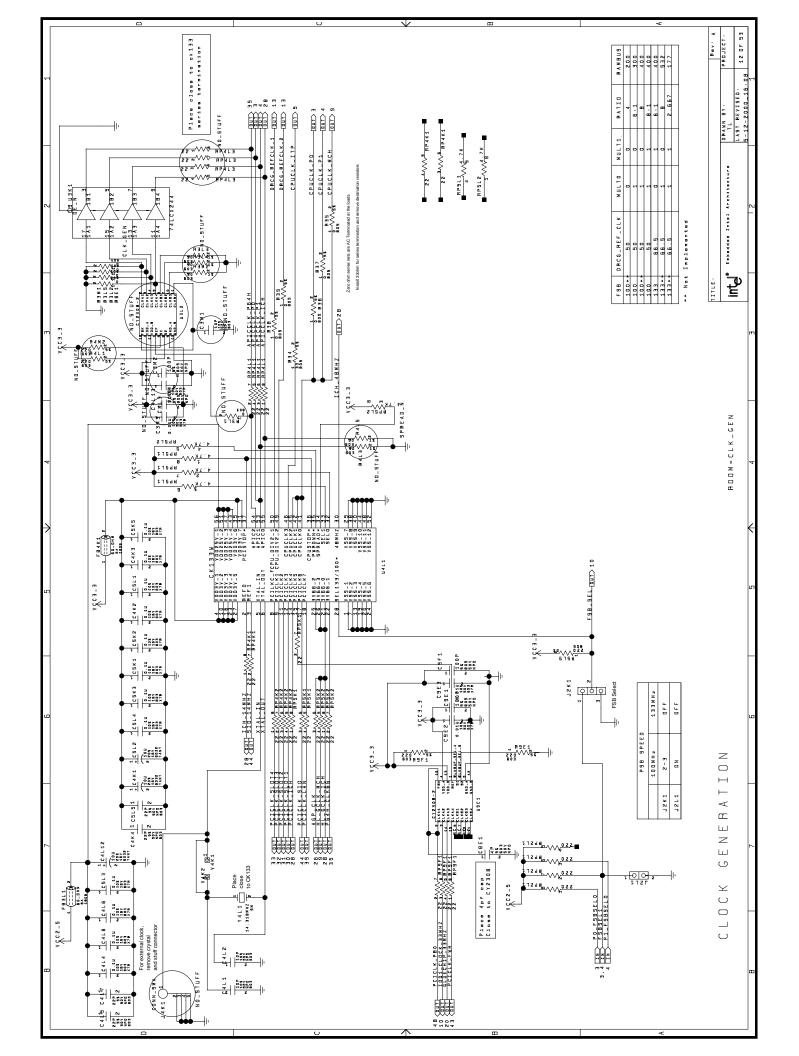

| 17 | Cloc         | king                                                                                                                          |       |

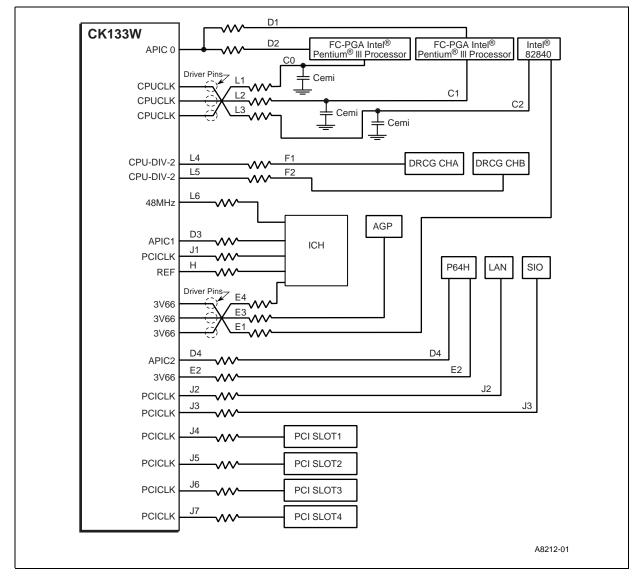

|    | 17.1         | CK133W                                                                                                                        | .17-1 |

|    |              | 17.1.1 FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processor                                                           | .17-2 |

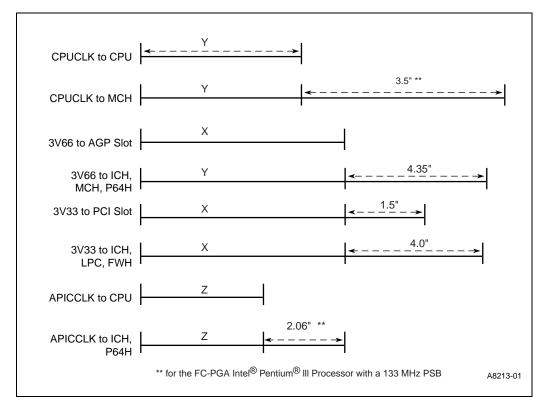

|    |              | 17.1.2 CK133W - FC-PGA Intel Pentium III Processor and<br>Intel 840 Chipset Clock Skew                                        | 17-3  |

|    |              | 17.1.3 BCLK Skew Between CPU and Chipset                                                                                      |       |

|    |              | 17.1.4 Processor Platform CPU Clocks Ganging Solution                                                                         |       |

|    | 17.2         | Series Termination Resistor for CK133W Clock Outputs                                                                          |       |

|    | 17.3         | Topology Under Investigation – Source Series                                                                                  |       |

|    |              | Termination with Receiver AC Termination                                                                                      |       |

|    | 17.4         | Unused CK133W Clock Outputs                                                                                                   |       |

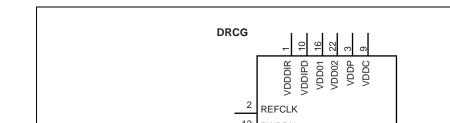

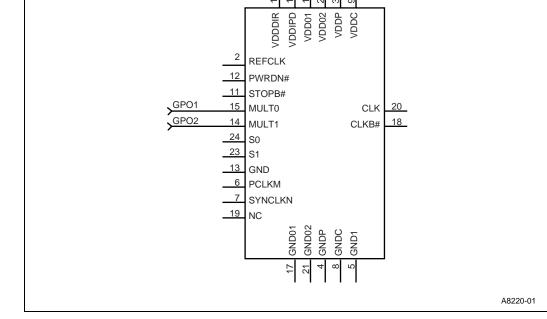

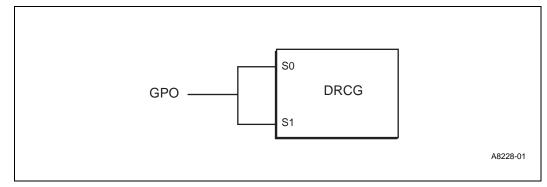

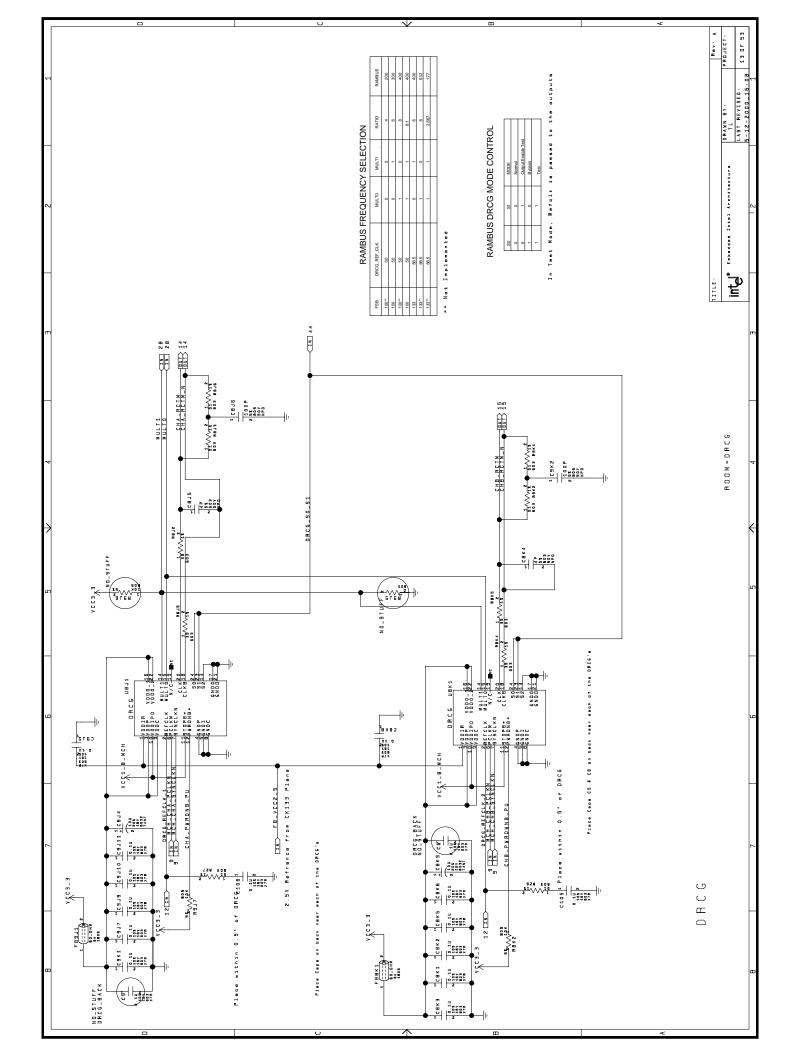

|    | 17.5         | DRCG                                                                                                                          |       |

|    | 17.6         | Component Placement and Layout Requirements                                                                                   |       |

|    |              | 17.6.1 14.318 MHz Crystal to CK133W                                                                                           | .17-7 |

|    |              | 17.6.2 CK133W to DRCG                                                                                                         | .17-7 |

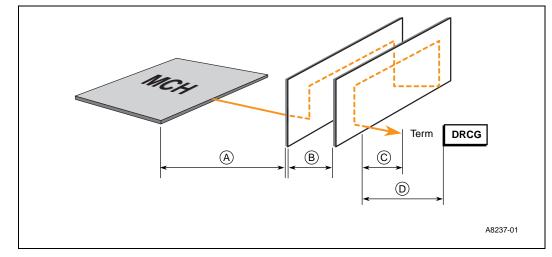

|    |              | 17.6.3 Intel <sup>®</sup> 82840-MCH to DRCG                                                                                   |       |

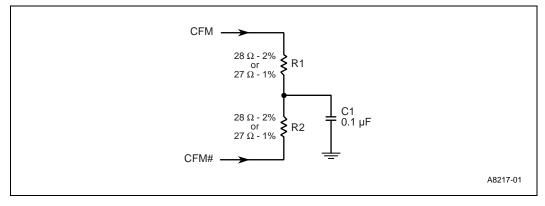

|    |              | 17.6.4 DRCG to RDRAM Channels                                                                                                 | .17-8 |

#### Contents

# intel

|    |              | 17.6.5 Trace Lengths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                     |

|----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

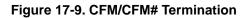

|    |              | 17.6.6 DRCG Impedance Matching Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                     |

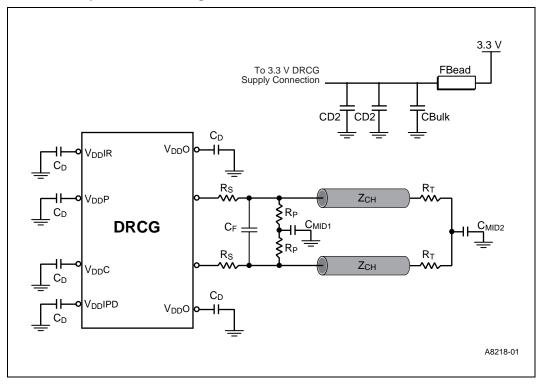

|    |              | 17.6.7 DRCG Layout Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                     |

|    |              | 17.6.8 Decoupling Recommendation for CK133W and DRCG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                     |

|    | 17.7         | DRCG Frequency Selection and DRCG+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                     |

|    |              | 17.7.1 DRCG Frequency Selection Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                     |

|    |              | 17.7.2 DRCG+ Frequency Selection Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                     |

|    | 17.8         | AGP Clock Routing Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                     |

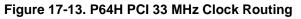

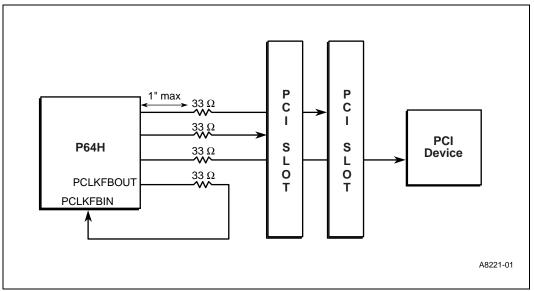

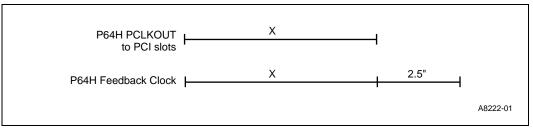

|    |              | 17.8.1 P64H PCI 33 MHz Clock Routing Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                     |

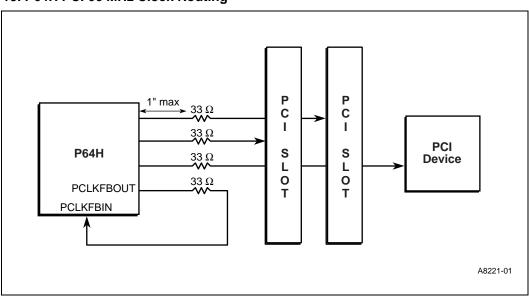

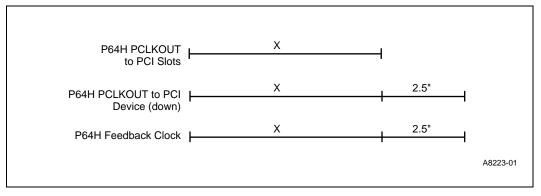

|    | 17.9         | P64H PCI 66 MHz Clock Routing Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17-17                                                                                                                                                                                                                                                                                                                                                               |

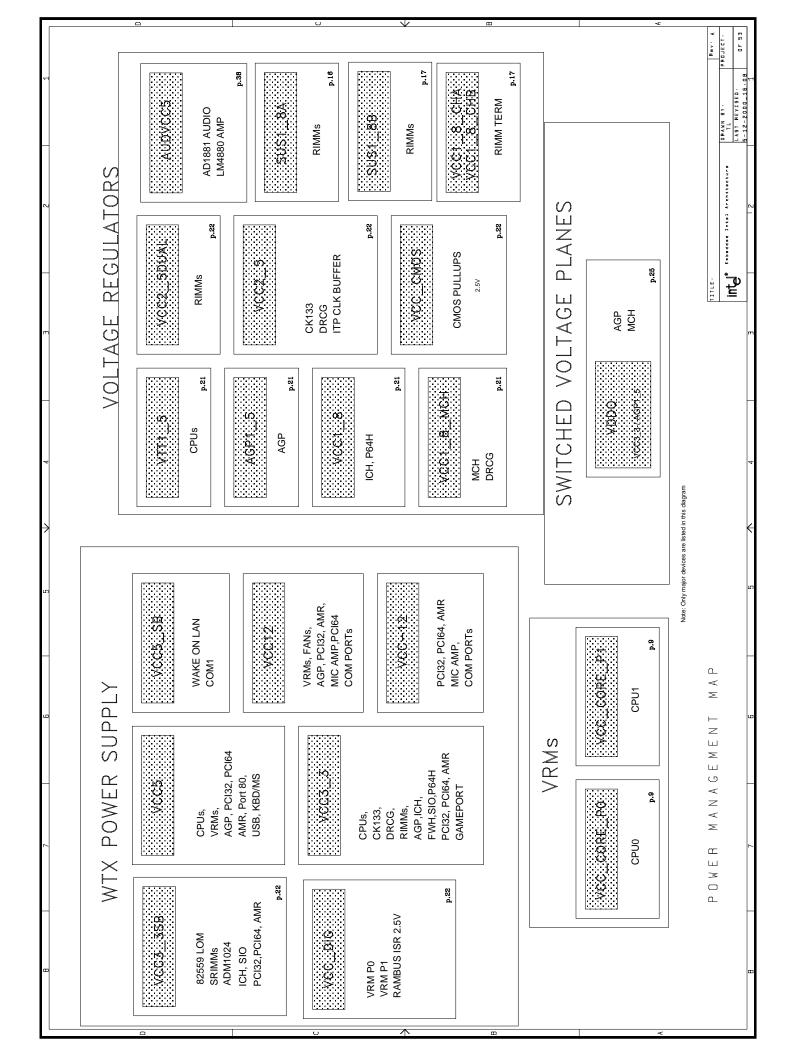

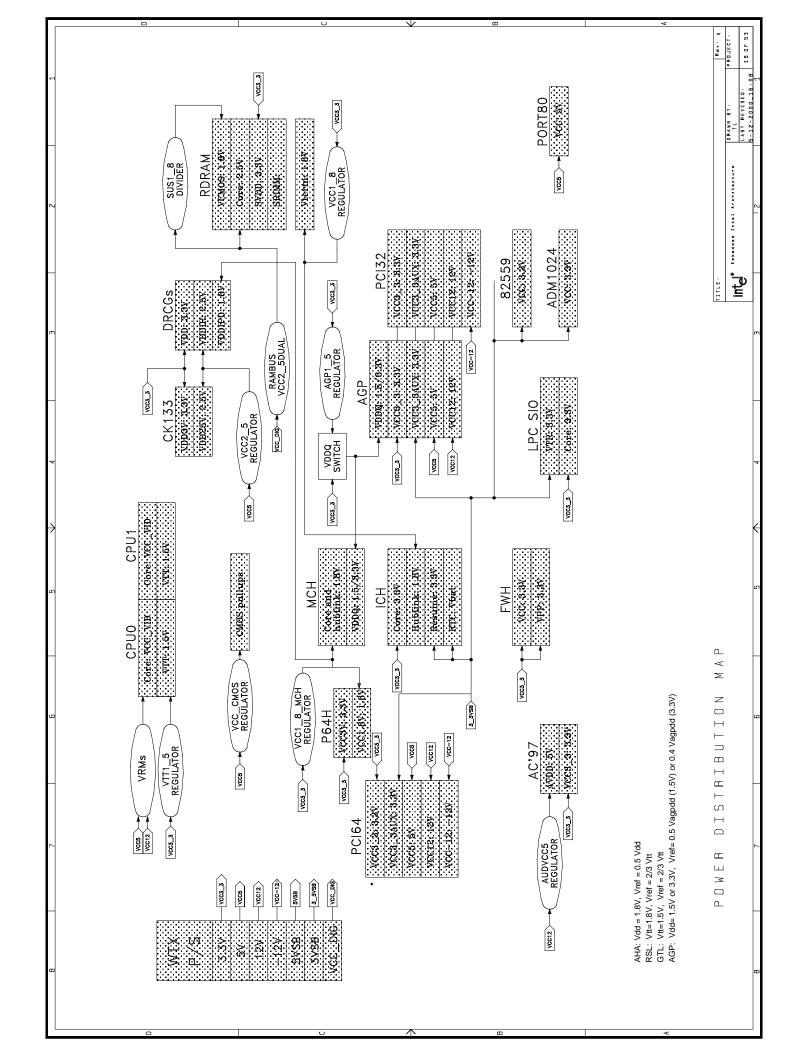

| 18 | Syste        | em Design Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18-1                                                                                                                                                                                                                                                                                                                                                                |

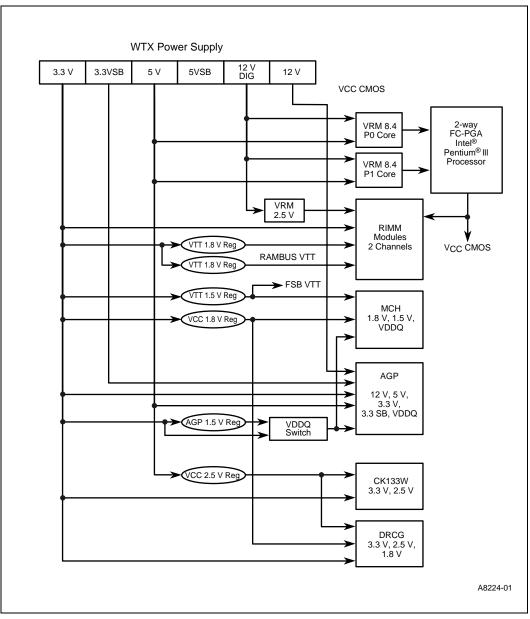

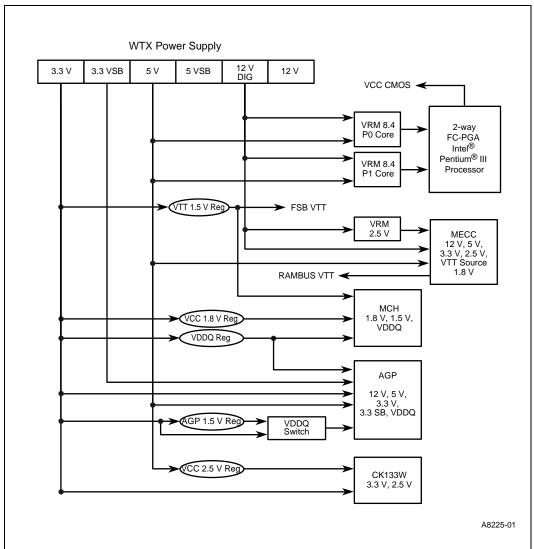

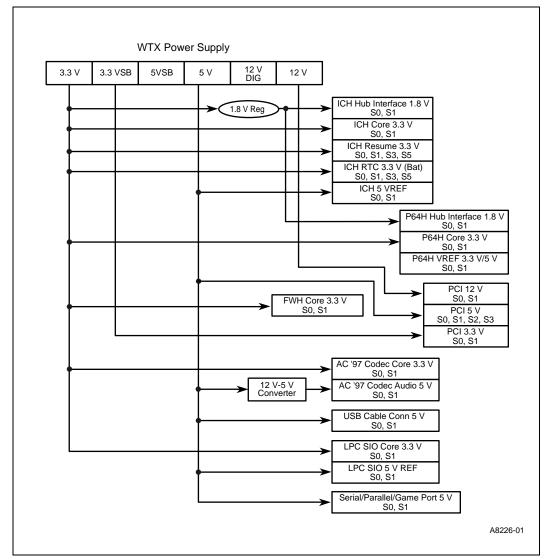

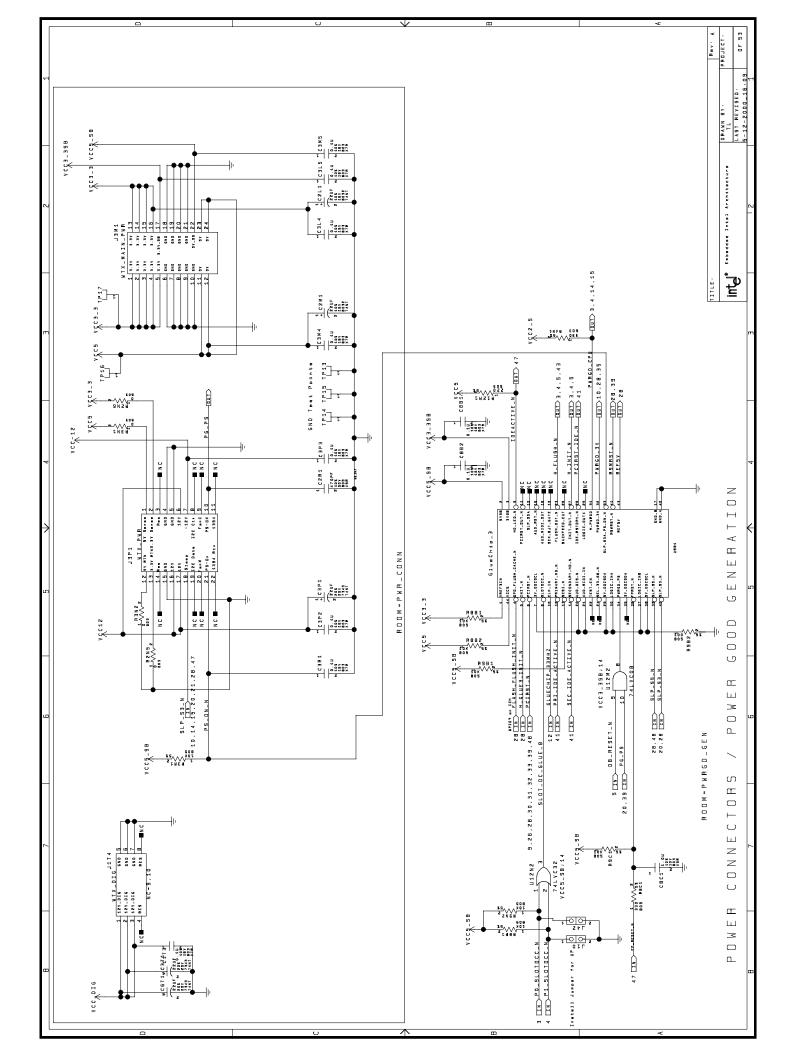

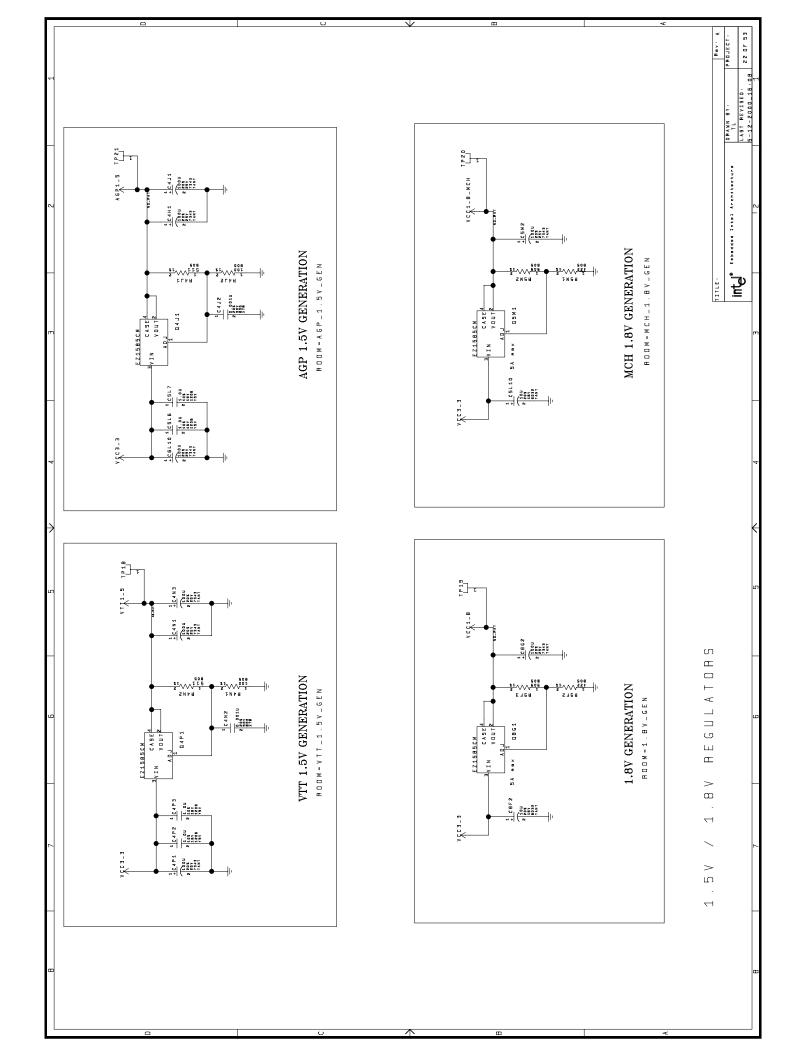

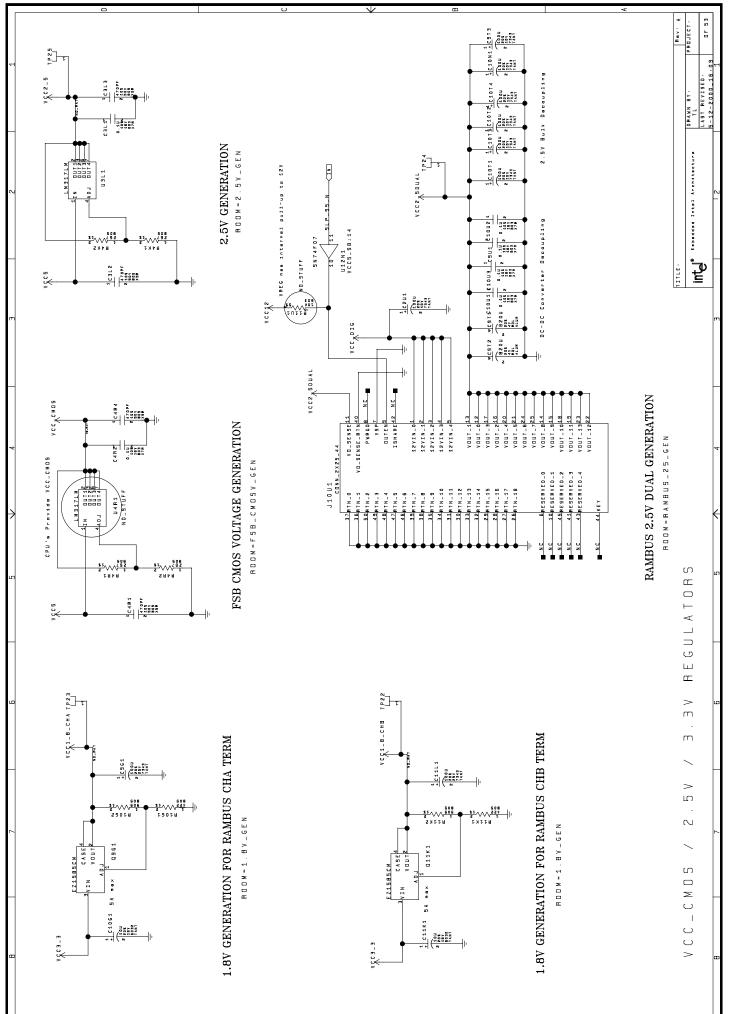

|    | 18.1         | Power Delivery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18-1                                                                                                                                                                                                                                                                                                                                                                |

|    |              | 18.1.1 Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                     |

|    |              | 18.1.2 Intel <sup>®</sup> 840 Chipset Board Power Delivery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18-2                                                                                                                                                                                                                                                                                                                                                                |

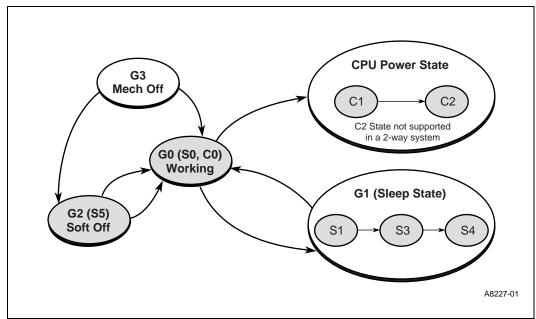

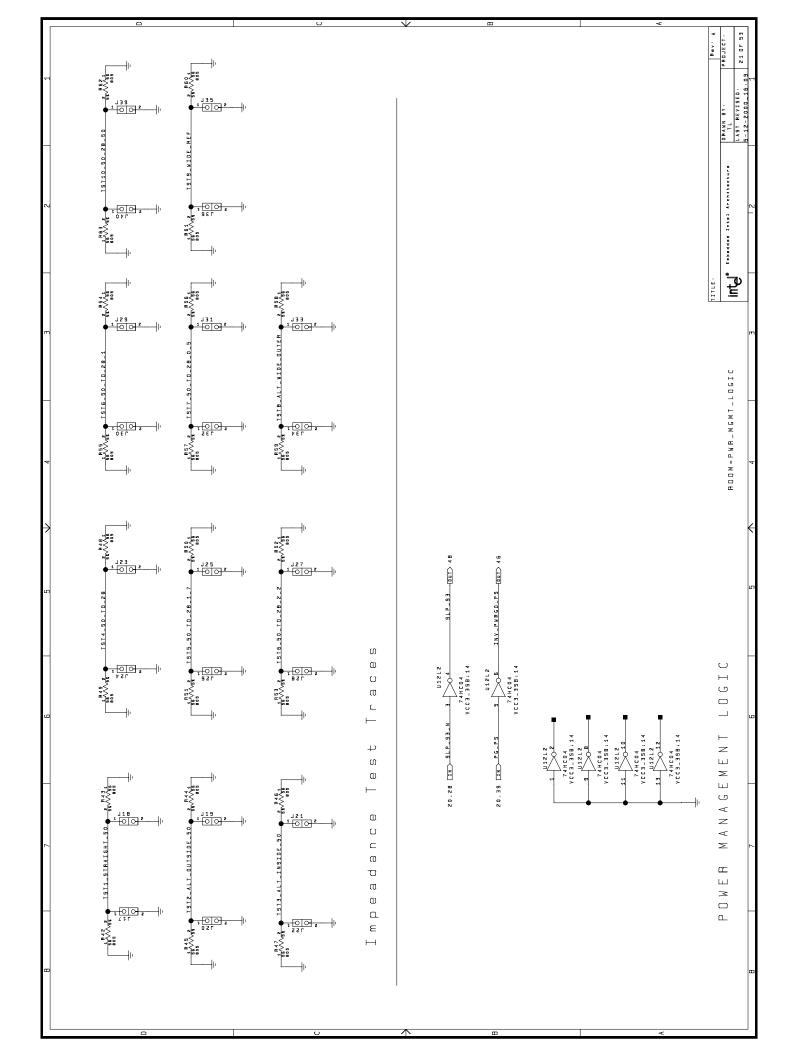

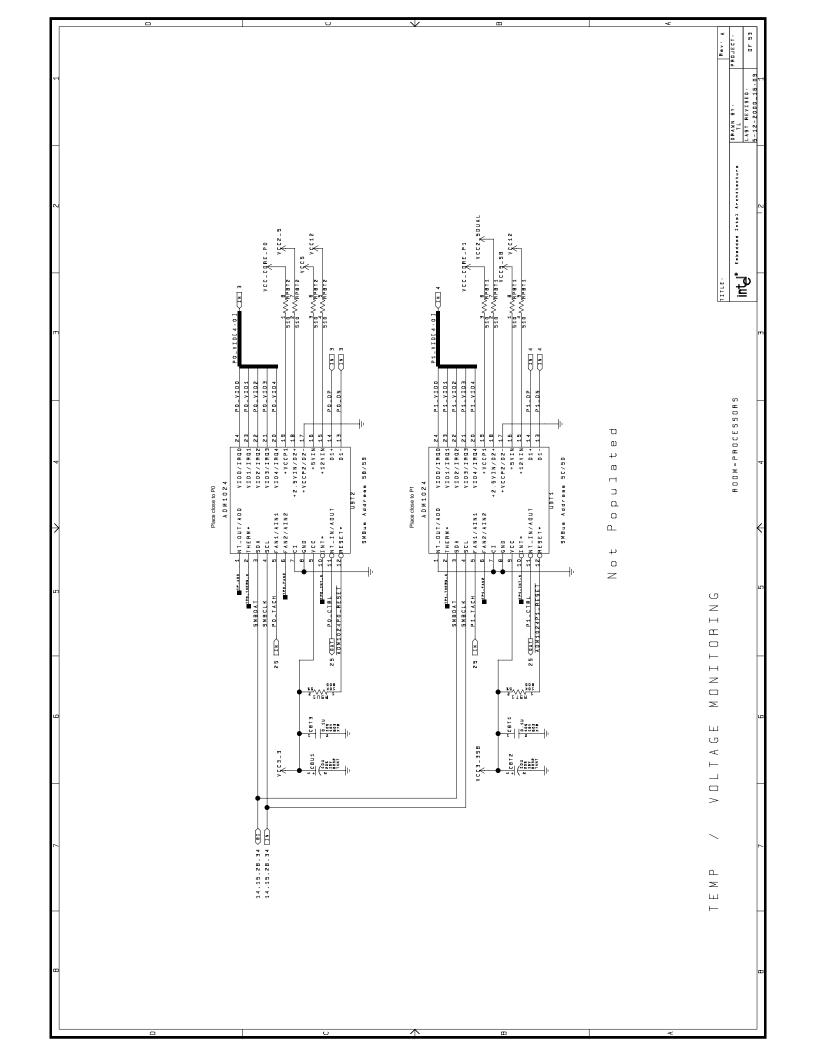

|    | 18.2         | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                     |

|    | 18.3         | ACPI Hardware Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                     |

|    | 18.4         | Thermal Design Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                     |

|    | 18.5         | 64/72-Mbit RDRAM Excessive Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                     |

|    |              | 18.5.1 Option 1: Reduce the Clock Frequency During Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                     |

|    |              | 18.5.2 Option 2: Increase the Current Capability of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                     |

|    |              | 2.5 V Voltage Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18-7                                                                                                                                                                                                                                                                                                                                                                |

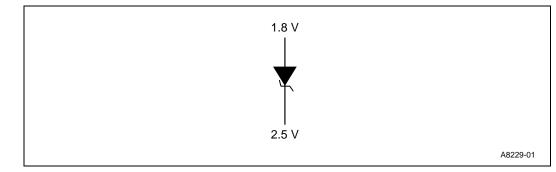

|    | 18.6         | V <sub>TERM</sub> /V <sub>DD</sub> Power Sequencing Requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18-8                                                                                                                                                                                                                                                                                                                                                                |

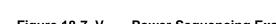

|    | 18.7         | V <sub>DDQ</sub> /V <sub>CC1.8</sub> Power Sequencing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                     |

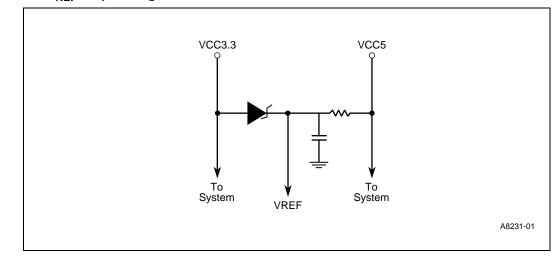

|    | 18.8         | ICH/P64H 5V <sub>REF</sub> and V <sub>CC3.3</sub> Sequencing Requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                     |

| 19 | Desid        | gn Considerations/Checklist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19-1                                                                                                                                                                                                                                                                                                                                                                |

| 10 | Desig        | g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                     |

| 15 | 19.1         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                     |

| 15 |              | General Design Considerations Design Consideration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19-1<br>19-1                                                                                                                                                                                                                                                                                                                                                        |

| 15 | 19.1         | General Design Considerations Design Consideration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19-1<br>19-1                                                                                                                                                                                                                                                                                                                                                        |

| 15 | 19.1         | General Design Considerations<br>Design Consideration<br>19.2.1 FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19-1<br>19-1<br>19-1                                                                                                                                                                                                                                                                                                                                                |

| 15 | 19.1<br>19.2 | General Design Considerations Design Consideration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19-1<br>19-1<br>19-1<br>19-2                                                                                                                                                                                                                                                                                                                                        |

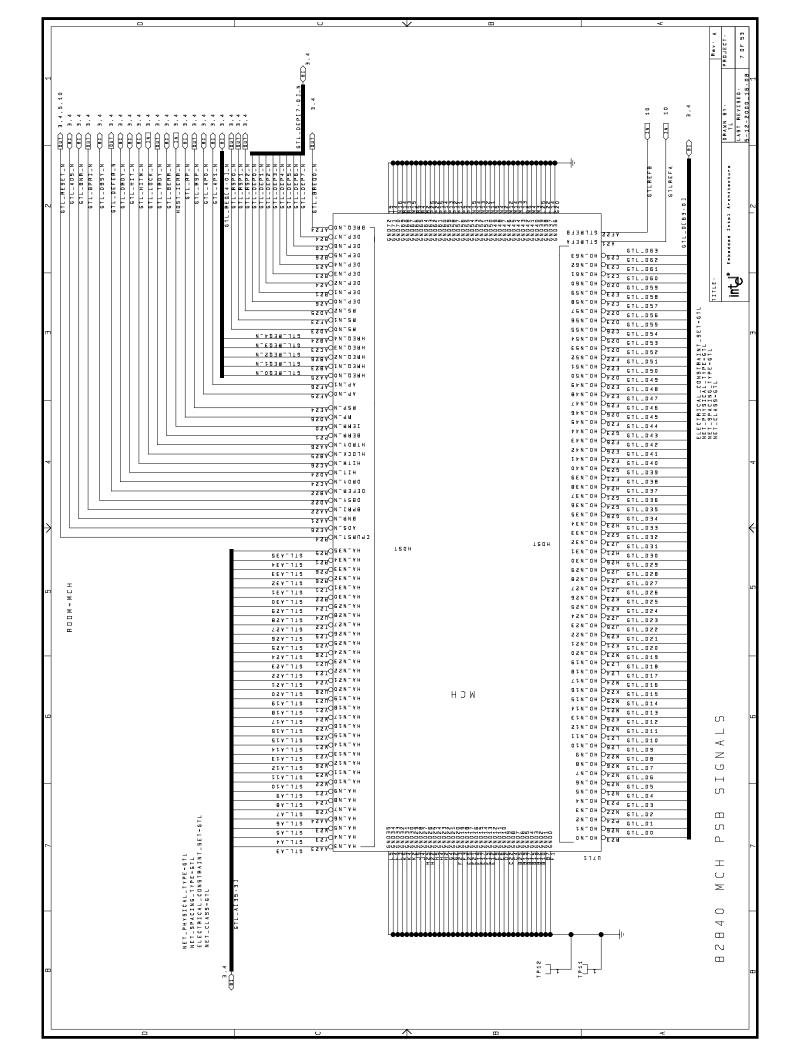

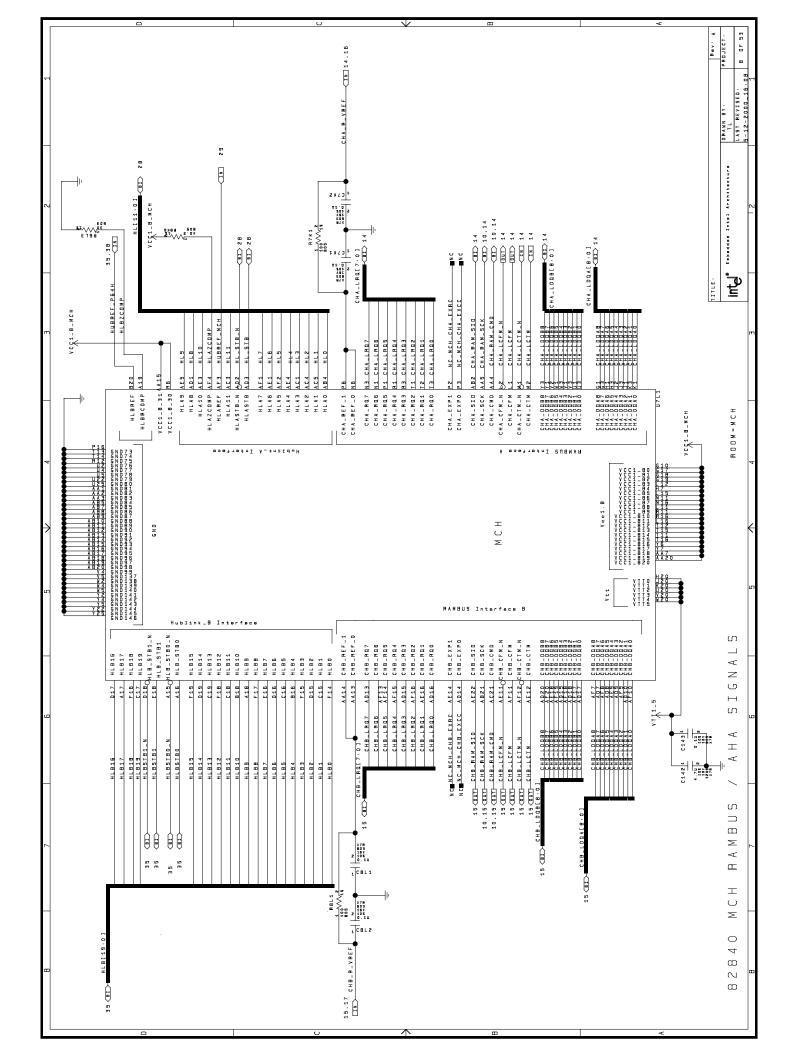

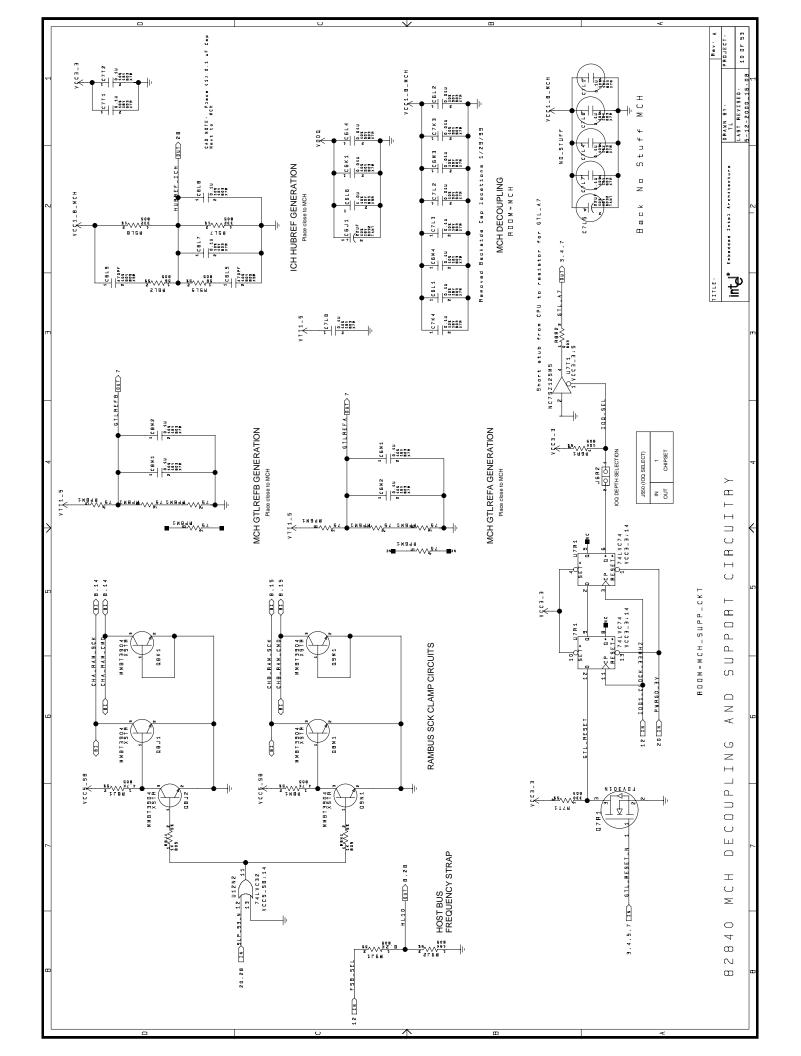

| 15 | 19.1<br>19.2 | General Design Considerations<br>Design Consideration<br>19.2.1 FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors<br>82840 Memory Controller Hub (MCH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19-1<br>19-1<br>19-1<br>19-2<br>19-2                                                                                                                                                                                                                                                                                                                                |

| 13 | 19.1<br>19.2 | General Design Considerations         Design Consideration         19.2.1       FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors         82840 Memory Controller Hub (MCH)         19.3.1       System Bus Interface         19.3.2       RDRAM Interface         19.3.2.1       Ground Isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19-1<br>19-1<br>19-2<br>19-2<br>19-2<br>19-2<br>19-2                                                                                                                                                                                                                                                                                                                |

| 10 | 19.1<br>19.2 | General Design Considerations         Design Consideration         19.2.1       FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors         82840 Memory Controller Hub (MCH)         19.3.1       System Bus Interface         19.3.2       RDRAM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19-1<br>19-1<br>19-2<br>19-2<br>19-2<br>19-2<br>19-2                                                                                                                                                                                                                                                                                                                |

| 15 | 19.1<br>19.2 | General Design Considerations         Design Consideration         19.2.1       FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors         82840 Memory Controller Hub (MCH)         19.3.1       System Bus Interface         19.3.2       RDRAM Interface         19.3.2.1       Ground Isolation         19.3.2.2       V <sub>TERM</sub> Layout Guidelines for Low Noise         19.3.2.3       CTM/CTM# Routing                                                                                                                                                                                                                                                                                                                                                                                                   | 19-1<br>19-1<br>19-2<br>19-2<br>19-2<br>19-2<br>19-3<br>19-3                                                                                                                                                                                                                                                                                                        |

|    | 19.1<br>19.2 | General Design Considerations         Design Consideration         19.2.1       FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors         82840 Memory Controller Hub (MCH)         19.3.1       System Bus Interface         19.3.2       RDRAM Interface         19.3.2.1       Ground Isolation         19.3.2.2       V <sub>TERM</sub> Layout Guidelines for Low Noise         19.3.2.3       CTM/CTM# Routing         19.3.2.4       DRCG Power Supply                                                                                                                                                                                                                                                                                                                                                          | 19-1<br>19-1<br>19-2<br>19-2<br>19-2<br>19-2<br>19-3<br>19-3<br>19-3<br>19-3                                                                                                                                                                                                                                                                                        |

| 15 | 19.1<br>19.2 | General Design Considerations         Design Consideration         19.2.1       FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors         82840 Memory Controller Hub (MCH)         19.3.1       System Bus Interface         19.3.2       RDRAM Interface         19.3.2.1       Ground Isolation         19.3.2.2       V <sub>TERM</sub> Layout Guidelines for Low Noise         19.3.2.3       CTM/CTM# Routing         19.3.2.4       DRCG Power Supply         19.3.2.5       DRCG Output Network Layout                                                                                                                                                                                                                                                                                                        | 19-1<br>19-1<br>19-2<br>19-2<br>19-2<br>19-2<br>19-3<br>19-3<br>19-3<br>19-3<br>19-4                                                                                                                                                                                                                                                                                |

|    | 19.1<br>19.2 | General Design Considerations         Design Consideration         19.2.1       FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors         82840 Memory Controller Hub (MCH)         19.3.1       System Bus Interface         19.3.2       RDRAM Interface         19.3.2.1       Ground Isolation         19.3.2.2       V <sub>TERM</sub> Layout Guidelines for Low Noise         19.3.2.3       CTM/CTM# Routing         19.3.2.4       DRCG Power Supply         19.3.2.5       DRCG Output Network Layout         19.3.2.6       RSL Transmission Line                                                                                                                                                                                                                                                           | 19-1<br>19-1<br>19-2<br>19-2<br>19-2<br>19-2<br>19-3<br>19-3<br>19-3<br>19-4<br>19-4                                                                                                                                                                                                                                                                                |

|    | 19.1<br>19.2 | General Design Considerations         Design Consideration         19.2.1       FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors         82840 Memory Controller Hub (MCH)         19.3.1       System Bus Interface         19.3.2       RDRAM Interface         19.3.2.1       Ground Isolation         19.3.2.2       V <sub>TERM</sub> Layout Guidelines for Low Noise         19.3.2.3       CTM/CTM# Routing         19.3.2.4       DRCG Power Supply         19.3.2.5       DRCG Output Network Layout         19.3.2.6       RSL Transmission Line         19.3.2.7       V <sub>REF</sub> Routing                                                                                                                                                                                                           | 19-1<br>19-1<br>19-2<br>19-2<br>19-2<br>19-2<br>19-3<br>19-3<br>19-3<br>19-3<br>19-4<br>19-4                                                                                                                                                                                                                                                                        |

|    | 19.1<br>19.2 | General Design Considerations         Design Consideration         19.2.1       FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors         82840 Memory Controller Hub (MCH)         19.3.1       System Bus Interface         19.3.2       RDRAM Interface         19.3.2.1       Ground Isolation         19.3.2.2       V <sub>TERM</sub> Layout Guidelines for Low Noise         19.3.2.3       CTM/CTM# Routing         19.3.2.4       DRCG Power Supply         19.3.2.5       DRCG Output Network Layout         19.3.2.6       RSL Transmission Line         19.3.2.7       V <sub>REF</sub> Routing         19.3.2.8       RSL Routing                                                                                                                                                                        | 19-1<br>19-1<br>19-2<br>19-2<br>19-2<br>19-2<br>19-3<br>19-3<br>19-3<br>19-3<br>19-4<br>19-4<br>19-4<br>19-5                                                                                                                                                                                                                                                        |

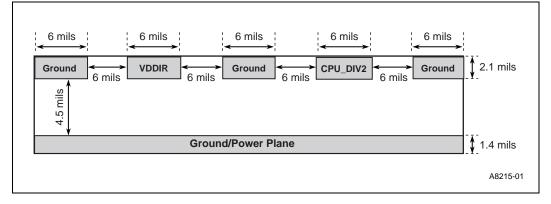

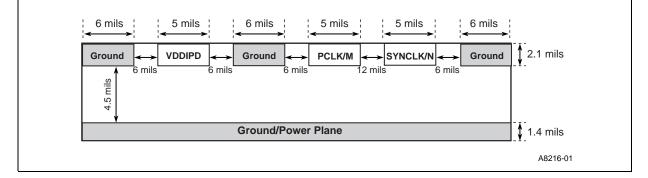

|    | 19.1<br>19.2 | General Design Considerations         Design Consideration         19.2.1       FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors         82840 Memory Controller Hub (MCH)         19.3.1       System Bus Interface         19.3.2       RDRAM Interface         19.3.2.1       Ground Isolation         19.3.2.2       V <sub>TERM</sub> Layout Guidelines for Low Noise         19.3.2.3       CTM/CTM# Routing         19.3.2.4       DRCG Power Supply         19.3.2.5       DRCG Output Network Layout         19.3.2.6       RSL Transmission Line         19.3.2.7       V <sub>REF</sub> Routing         19.3.2.8       RSL Routing         19.3.2.9       RDRAM Clock Routing                                                                                                                             | 19-1<br>19-1<br>19-2<br>19-2<br>19-2<br>19-2<br>19-3<br>19-3<br>19-3<br>19-3<br>19-4<br>19-4<br>19-4<br>19-5<br>19-5                                                                                                                                                                                                                                                |

|    | 19.1<br>19.2 | General Design Considerations         Design Consideration         19.2.1       FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors         82840 Memory Controller Hub (MCH)         19.3.1       System Bus Interface         19.3.2       RDRAM Interface         19.3.2.1       Ground Isolation         19.3.2.2       V <sub>TERM</sub> Layout Guidelines for Low Noise         19.3.2.3       CTM/CTM# Routing         19.3.2.4       DRCG Power Supply         19.3.2.5       DRCG Output Network Layout         19.3.2.6       RSL Transmission Line         19.3.2.7       V <sub>REF</sub> Routing         19.3.2.8       RSL Routing         19.3.2.9       RDRAM Clock Routing         19.3.2.10       Hub Interface A                                                                                     | 19-1<br>19-1<br>19-2<br>19-2<br>19-2<br>19-2<br>19-3<br>19-3<br>19-3<br>19-3<br>19-4<br>19-4<br>19-4<br>19-5<br>19-5                                                                                                                                                                                                                                                |

|    | 19.1<br>19.2 | General Design Considerations         Design Consideration         19.2.1       FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors         82840 Memory Controller Hub (MCH)         19.3.1       System Bus Interface         19.3.2       RDRAM Interface         19.3.2.1       Ground Isolation         19.3.2.2       V <sub>TERM</sub> Layout Guidelines for Low Noise         19.3.2.3       CTM/CTM# Routing         19.3.2.4       DRCG Power Supply         19.3.2.5       DRCG Output Network Layout         19.3.2.6       RSL Transmission Line         19.3.2.7       V <sub>REF</sub> Routing         19.3.2.8       RSL Routing         19.3.2.9       RDRAM Clock Routing         19.3.2.10       Hub Interface A         19.3.2.11       AGP Interface                                               | 19-1<br>19-1<br>19-2<br>19-2<br>19-2<br>19-2<br>19-3<br>19-3<br>19-3<br>19-3<br>19-4<br>19-4<br>19-4<br>19-5<br>19-5<br>19-5<br>19-5                                                                                                                                                                                                                                |

|    | 19.1<br>19.2 | General Design Considerations         Design Consideration         19.2.1       FC-PGA Intel <sup>®</sup> Pentium <sup>®</sup> III Processors         82840 Memory Controller Hub (MCH)         19.3.1       System Bus Interface         19.3.2       RDRAM Interface         19.3.2.1       Ground Isolation         19.3.2.2       V <sub>TERM</sub> Layout Guidelines for Low Noise         19.3.2.3       CTM/CTM# Routing         19.3.2.4       DRCG Power Supply         19.3.2.5       DRCG Output Network Layout         19.3.2.6       RSL Transmission Line         19.3.2.7       V <sub>REF</sub> Routing         19.3.2.8       RSL Routing         19.3.2.9       RDRAM Clock Routing         19.3.2.10       Hub Interface A         19.3.2.11       AGP Interface         19.3.3       I/O Controller Hub (ICH) | 19-1<br>19-1<br>19-2<br>19-2<br>19-2<br>19-2<br>19-3<br>19-3<br>19-3<br>19-3<br>19-4<br>19-4<br>19-5<br>19-5<br>19-5<br>19-6                                                                                                                                                                                                                                        |