# int<sub>el</sub>®

## Intel<sup>®</sup> 440BX AGPset / PGA370 Scalable Performance Board Design Guide

October 2001

Order Number: 273296-005

# intel

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 440BX AGPset, Intel Celeron<sup>™</sup> processor, and Intel Pentium<sup>®</sup> III processor may contain design defects or errors known as errata which may cause the products to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

#### Copyright © Intel Corporation, 2000

\*Third-party brands and names are the property of their respective owners.

Intel<sup>®</sup> 440BX AGPset / PGA370 Scalable Performance Board Design Guide

# intel Contents

| 1.0 | Intro | duction                                                                                   | 7 |

|-----|-------|-------------------------------------------------------------------------------------------|---|

|     | 1.1   | Notation and Terminology                                                                  | 7 |

|     | 1.2   | Reference Documents and Resources                                                         |   |

|     | 1.3   | Design Features                                                                           |   |

|     | 110   | 1.3.1 PGA370-Based Processors                                                             |   |

|     |       | 1.3.2 Intel <sup>®</sup> 440BX AGPset                                                     |   |

|     | 1.4   | General Considerations                                                                    |   |

|     |       | 1.4.1 Voltage Definitions                                                                 |   |

|     |       | 1.4.2 General Design Recommendations                                                      |   |

|     | 1.5   | Transitioning from an Intel <sup>®</sup> Pentium <sup>®</sup> II Processor / 440BX AGPset |   |

|     |       | Design                                                                                    |   |

|     |       | 1.5.1 AGTL+ Termination                                                                   |   |

|     |       | 1.5.2 V <sub>REF</sub> Inputs                                                             |   |

|     |       | 1.5.3 System Bus Clock                                                                    |   |

|     |       | 1.5.4 CMOS Compatibility with Future Processors                                           |   |

|     |       | 1.5.5 Processor Core Voltage Decoupling                                                   |   |

|     |       | 1.5.6 VID[4] Pin                                                                          |   |

|     |       | 1.5.7 Phase Lock Loop (PLL) Power1                                                        |   |

|     |       | 1.5.7.1 PLL Topology12                                                                    |   |

|     |       | 1.5.7.2 PLL Filter Specification                                                          |   |

|     |       | 1.5.7.3 PLL Filter Recommendation                                                         |   |

|     |       | 1.5.8 Bus Frequency Selection                                                             |   |

|     |       | 1.5.9 New Pin Definitions                                                                 |   |

|     |       | 1.5.10 VCORE <sub>DET</sub>                                                               | 5 |

| 2.0 | Layo  | out and Routing Guidelines1                                                               | 6 |

|     | 2.1   | BGA Quadrant Assignment1                                                                  | 6 |

|     | 2.2   | PGA370-Based Processor Signal Quadrants1                                                  | 7 |

|     | 2.3   | Board Description                                                                         | 0 |

|     | 2.4   | Routing Guidelines                                                                        | 1 |

|     |       | 2.4.1 AGTL+ Description                                                                   | 1 |

|     | 2.5   | AGTL+ Layout Recommendations2                                                             | 1 |

|     |       | 2.5.1 Network Topology and Conditions                                                     | 1 |

|     |       | 2.5.2 Recommended Trace Lengths                                                           | 2 |

|     |       | 2.5.2.1 Board Layout Rules2                                                               | 2 |

|     |       | 2.5.3 Additional Guidelines                                                               | 3 |

|     | 2.6   | Pre-Layout Simulation (Sensitivity Analysis)2                                             | 3 |

|     |       | 2.6.1 Simulation Parameter Values                                                         |   |

|     |       | 2.6.2 Simulation Methodology                                                              |   |

|     |       | 2.6.2.1 Flight Time Simulation                                                            |   |

|     |       | 2.6.2.2 Signal Quality Measurement                                                        |   |

|     | 2.7   | Post-Layout Simulation                                                                    |   |

|     |       | 2.7.1 Crosstalk and the Multi-Bit Adjustment Factor                                       |   |

|     | 2.8   | Timing Analysis                                                                           |   |

|     | 2.9   | Host Clock Routing Spacing                                                                |   |

|     |       | 2.9.1 System Clock Layout                                                                 |   |

|     | 2.10  | Other Buses                                                                               |   |

|     |       |                                                                                           |   |

| 3.0 | Scala | ble Performance Board Guidelines                                | . 30 |

|-----|-------|-----------------------------------------------------------------|------|

|     | 3.1   | Processor Guidelines                                            | . 30 |

|     |       | 3.1.1 Scalable Performance System Design DC Guidelines          | . 30 |

|     |       | 3.1.2 System Bus AC Guidelines                                  |      |

|     |       | 3.1.3 Thermal Guidelines                                        |      |

|     | 3.2   | PGA370 Socket Design Guidelines                                 |      |

|     |       | 3.2.1 V <sub>TT</sub> and V <sub>CCCORE</sub> Power Plane Split |      |

|     |       | 3.2.2 BSEL[1:0] Implementation                                  |      |

|     |       | 3.2.3 CLKREF Circuit Implementation                             |      |

|     |       | 3.2.4 AGTL+ Reset Implementation                                |      |

|     |       | 3.2.4.1 AGTL+ Reset Layout Topology                             |      |

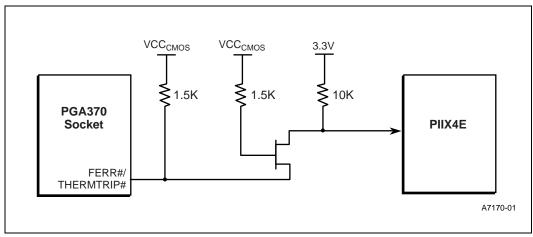

|     |       | 3.2.5 CMOS Voltage Conversion Logic                             | .40  |

| 4.0 | Desig | In Checklist                                                    | . 41 |

|     | 4.1   | Overview                                                        |      |

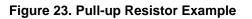

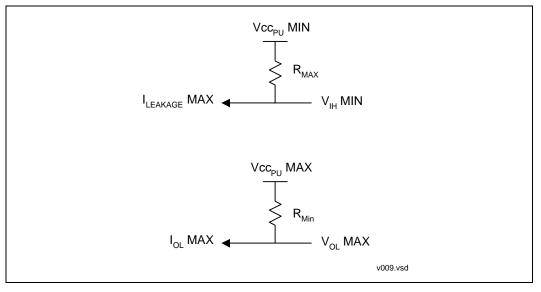

|     | 4.2   | Pull-up and Pull-down Resistor Values                           | .41  |

|     | 4.3   | Processor Checklist                                             |      |

|     |       | 4.3.1 PGA370-Based Processors                                   |      |

|     |       | 4.3.2 GND and Power Pin Definition                              |      |

|     |       | 4.3.3 Processor Clocks                                          |      |

|     |       | 4.3.4 Processor Signals                                         |      |

|     |       | 4.3.5 Processor Decoupling Capacitors                           |      |

|     |       | 4.3.5.1 Core Voltage High-Frequency Decoupling                  |      |

|     |       | 4.3.5.2 VTT Decoupling<br>4.3.5.3 VREF Decoupling               |      |

|     | 4.4   | Board Component Keep-Out.                                       |      |

|     | 4.5   | Thermals/Cooling Solutions                                      |      |

|     |       | 4.5.1 Thermal Solution Design Considerations                    |      |

|     | 4.6   | Mechanical Design Considerations                                |      |

|     | 4.7   | Electrical Design Considerations                                |      |

| 5.0 | Third | -Party Vendor Information                                       | .51  |

|     | 5.1   | Voltage Regulator Control Silicon                               | .51  |

|     | 5.2   | Clock Drivers                                                   | .51  |

|     | 5.3   | PGA370 Socket                                                   | .51  |

|     | Index | · · · · · · · · · · · · · · · · · · ·                           | .53  |

# intel®

Intel<sup>®</sup> 440BX AGPset / PGA370 Scalable Performance Board Design Guide

# Figures

| 1  | PLL Filter Topology                                                      | 12 |

|----|--------------------------------------------------------------------------|----|

| 2  | PLL Filter Specification                                                 | 13 |

| 3  | Using Discrete R                                                         | 15 |

| 4  | No Discrete R                                                            | 15 |

| 5  | Major Signal Sections of the 82443BX (Top View)                          | 16 |

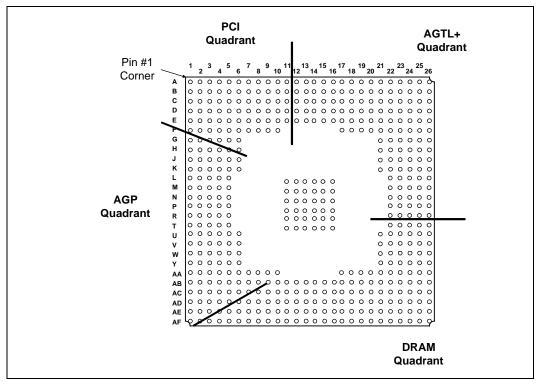

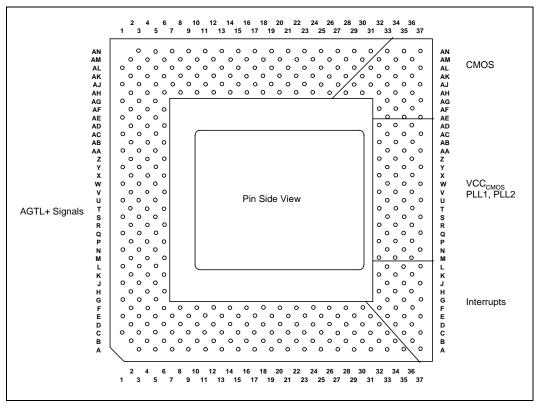

| 6  | PGA370-Based Processor Quadrants                                         |    |

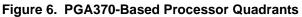

| 7  | Example ATX Placement for Intel <sup>®</sup> 440BX AGPset / PGA370-Based |    |

|    | Processor Designs                                                        | 18 |

| 8  | Example NLX Placement for Intel <sup>®</sup> 440BX AGPset / PGA370-Based |    |

|    | Processor Design                                                         |    |

| 9  | Four-Layer Board Stack-up Example                                        |    |

| 10 | Recommended Topology                                                     |    |

| 11 | Test Load vs. Actual System Load                                         |    |

| 12 | Clock Trace Spacing Guidelines                                           | 27 |

| 13 | Host Clock Topology                                                      |    |

| 14 | BCLK Waveform                                                            | 33 |

| 15 | Processor System Bus Valid Delay Timings Waveform                        | 34 |

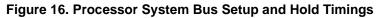

| 16 | Processor System Bus Setup and Hold Timings                              | 34 |

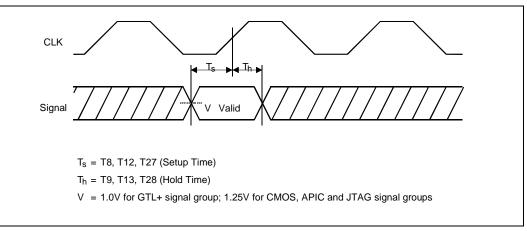

| 17 | Power-On Reset and Configuration Timings                                 | 35 |

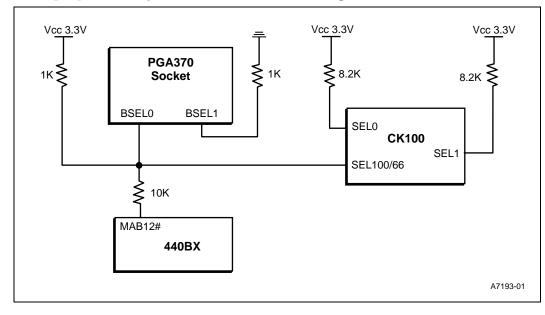

| 18 | BSEL[1:0] Circuit Implementation for PGA370 Designs                      | 36 |

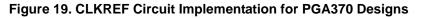

| 19 | CLKREF Circuit Implementation for PGA370 Designs                         | 37 |

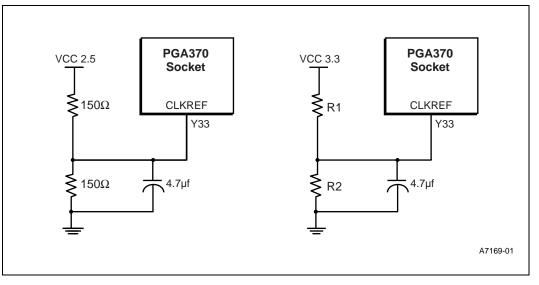

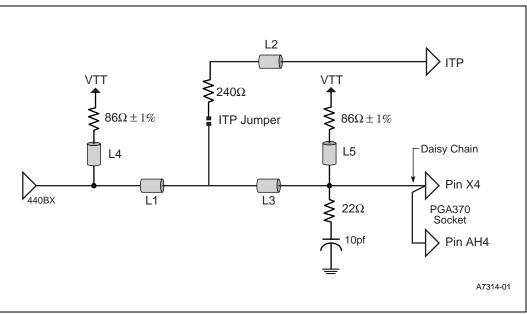

| 20 | AGTL+ Reset Implementation                                               | 38 |

| 21 | AGTL+ Reset Layout Topology                                              | 39 |

| 22 | CMOS Conversion Logic                                                    | 40 |

| 23 | Pull-up Resistor Example                                                 | 42 |

| 24 | Example Capacitor Placement Within the PGA370 Socket                     | 47 |

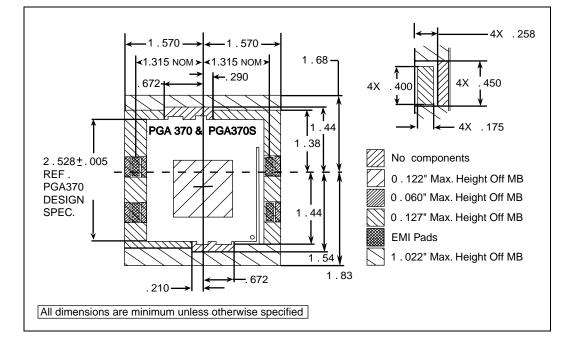

| 25 | Board Component Keep-Out                                                 | 48 |

|    |                                                                          |    |

## Tables

| 1  | Reference Documents and Resources                                                   | 8                    |

|----|-------------------------------------------------------------------------------------|----------------------|

| 2  | Recommended Inductor for PLL Filter                                                 | 14                   |

| 3  | Recommended Capacitor for PLL Filter                                                | 14                   |

| 4  | Recommended Resistor for PLL Filter                                                 | 14                   |

| 5  | Recommended Trace Lengths                                                           | 22                   |

| 6  | Parameter Values for Interconnect AGTL+ Simulations                                 |                      |

| 7  | PGA370-Based Processor and Intel <sup>®</sup> 440BX AGPset System                   |                      |

|    | Timing Equations                                                                    |                      |

| 8  | PGA370-Based Processor and Intel <sup>®</sup> 440BX AGPset System                   |                      |

|    | Timing Terms                                                                        |                      |

| 9  | Recommended 66/100 MHz System Bus Timing Parameters                                 | 27                   |

| 10 | Host Clock Trace Lengths                                                            |                      |

| 11 | Voltage and Current Specifications <sup>1, 2</sup> for PGA370-Based Processors      |                      |

| 12 | Scalable Performance Board Processor System Bus AC Guidelines (Clo                  | ck) <sup>1,2,3</sup> |

|    | at the Processor Pins                                                               |                      |

| 13 | Processor System Bus AC Guidelines (AGTL+ Signal Group) <sup>1, 2, 3, 4</sup>       |                      |

|    | at the Processor Pins                                                               |                      |

| 14 | Intel <sup>®</sup> Celeron <sup>™</sup> Processor PPGA Thermal Design Power         | 35                   |

| 15 | Intel <sup>®</sup> Pentium <sup>®</sup> III Processor for the PGA370 Socket Thermal |                      |

|    | Design Power                                                                        | 35                   |

| 16 | Resistor Values for CLKREF Divider (3.3 V Source)                                   |                      |

| 17 | AGTL+ Connectivity                                                                  |                      |

| 18 | CMOS Connectivity                                                                   |                      |

| 19 | TAP Connectivity (optional)                                                         |                      |

| 20 | Clock Connectivity                                                                  |                      |

| 21 | Miscellaneous Connectivity                                                          |                      |

| 22 | Power Connectivity                                                                  | 45                   |

| 23 | No Connects                                                                         |                      |

## **Revision History**

| Revision | Date  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 005      | 10/01 | Updated note on page 36.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 004      | 5/00  | Removed $V_{TT}$ and $V_{CCCORE}$ Voltage Sequencing section (3.2.2 in the -003 version).                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 003      | 5/00  | Renamed document to remove references to "motherboard" and<br>"flexible platform." The corrected term is now "scalable performance board." Clarified<br>"CMOS Compatibility with Future Processors" on page 11. Clarified "BSEL[1:0]<br>Implementation" on page 36. Updated Figure 25 with new component keep-out<br>restrictions. Corrected power dissipation specification to 26.7 W. Added V <sub>TT</sub> and<br>V <sub>CCCORE</sub> Power Plane Split section and V <sub>TT</sub> and V <sub>CCCORE</sub> Voltage Sequencing sec-<br>tion. |  |  |

| 002      | 2/00  | Clarified core voltage high frequency decoupling recommendations. Updated Figure 20 and Figure 21.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 001      | 11/99 | First publication of this document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

## 1.0 Introduction

Int

The Intel<sup>®</sup> Celeron<sup>TM</sup> and Intel Pentium<sup>®</sup> III processor families include processors that can be installed in a PGA370 socket. This document provides design recommendations and considerations for developing systems based on the Celeron processor in a PPGA package or the Pentium III processor in an FC-PGA package, together with the Intel 440BX AGPset. Likely design considerations are included to alleviate problems during the design and debug phases.

The information contained in this document should be used in conjunction with the *Intel*<sup>®</sup> 440BX AGPset Design Guide, which covers Intel 440BX AGPset designs with the Intel Pentium II processor. Refer to that document for topics not covered in this design guide. Exceptions to the *Intel*<sup>®</sup> 440BX AGPset Design Guide are listed in this document.

## 1.1 Notation and Terminology

In this document, a '#' symbol after a signal name identifies the signal as active low; that is, a signal that is in the active state, based on the name of the signal, when driven to a low level. For example, when FLUSH# is low, a flush has been requested. When NMI is high, a nonmaskable interrupt has occurred. When a signal name does not imply an active state, a # symbol indicates that the signal is inverted. For example, D[3:0] = 'HLHL' refers to a hex 'A', and D[3:0]# = 'LHLH' also refers to a hex 'A' (H= High logic level, L= Low logic level).

The term "PGA370-based processor(s)" refers to the Celeron processor in a PPGA or FC-PGA package and the Pentium III processor in an FC-PGA package.

## 1.2 Reference Documents and Resources

#### Table 1. Reference Documents and Resources

| Document Name or Information Source                                                                       | Order Number                                     |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Pentium <sup>®</sup> III Processor for the PGA370 Socket at 500E MHz and 550E MHz datasheet               | 245264                                           |

| Intel <sup>®</sup> Pentium <sup>®</sup> III Processor Specification Update                                | 244453                                           |

| Intel <sup>®</sup> Pentium <sup>®</sup> III Processor Thermal Metrology for CPUID 068xh Family Processors | 245301                                           |

| Intel <sup>®</sup> Celeron™ Processor datasheet                                                           | 243658                                           |

| Intel <sup>®</sup> Celeron™ Processor Specification Update                                                | 243748                                           |

| Intel <sup>®</sup> 440BX AGPset: 82443BX Host Bridge/Controller datasheet                                 | 290633                                           |

| 82443BX Host Bridge/Controller Electrical and Thermal Timing Specification -<br>Datasheet Addendum        | 273218                                           |

| Intel <sup>®</sup> 440BX AGPset Design Guide                                                              | 290634                                           |

| Intel <sup>®</sup> 440BX AGPset Design Guide Update                                                       | 290641                                           |

| 82443BX Application Notes                                                                                 | Contact your Intel Field<br>Sales Representative |

| Intel <sup>®</sup> 440BX AGPset: 82443BX Host Bridge/Controller Specification Update                      | 290639                                           |

| Pentium <sup>®</sup> II Processor Developer's Manual                                                      | 243502                                           |

| Pentium <sup>®</sup> II Processor Thermal Design Guidelines                                               | 243331                                           |

| 82371AB PCI-TO-ISA/IDE Xcelerator (PIIX4) datasheet                                                       | 290562                                           |

| 82371AB PCI-TO-ISA/IDE Xcelerator (PIIX4) Timing Specifications - Datasheet<br>Addendum                   | 290548                                           |

| Intel <sup>®</sup> 82371EB (PIIX4E) Specification Update                                                  | 290635                                           |

| 370-pin Socket (PGA370) Design Guidelines                                                                 | 244410                                           |

| PGA370 Heat Sink Cooling in MicroATX Chassis                                                              | 245025                                           |

| CK97 CLock Synthesizer Design Guidelines                                                                  | 243867                                           |

| P6 Family of Processors Hardware Developer's Manual                                                       | 244001                                           |

## 1.3 Design Features

### 1.3.1 PGA370-Based Processors

The PGA370-based processors implement a dynamic execution microarchitecture and execute Intel MMX<sup>TM</sup> technology instructions for enhanced media and communication performance. Additionally, the Pentium III processors feature streaming single instruction, multiple data (SIMD) extensions for enhanced floating-point and 3-D application performance. The PGA370-based processors also use the same multi-transaction system bus used in the Intel Pentium II processor. The PGA370-based processors support multiple low-power states such as AutoHALT, Stop-Grant, Sleep, and Deep Sleep to conserve power during idle times.

The PGA370-based processors are based on the P6 processor core. The Celeron processor is provided in a Plastic Pin Grid Array (PPGA) package and a Flip-Chip Pin Grid Array (FC-PGA) package, and the Pentium III processor is optionally provided in a FC-PGA package for use in low cost systems in the value embedded computing market segment. The PGA370-based processors utilize the AGTL+ system bus used by the Pentium II processor with support limited to single processor-based systems. The Celeron processor (PPGA) includes an integrated 128-Kbyte level-two cache with a separate 16-Kbyte instruction and 16-Kbyte data level-one caches. The Pentium III processor (FC-PGA) includes an integrated 256-Kbyte level-two cache with separate 16-Kbyte data level-one caches. The level-two cache is capable of caching 64 Gbyte of system memory address space.

### 1.3.2 Intel<sup>®</sup> 440BX AGPset

The Intel 440BX AGPset is a two-component chipset that includes the 82443BX AGP Host Bridge Controller and the 82371AB PCI-TO-ISA/IDE Xcelerator (PIIX4).

The chipset has the following features:

- Support for single Celeron or Pentium III processor configuration

- 64-bit AGTL+ based host bus interface

- 32-bit AGTL+ based host address interface

- 64-bit main memory interface with optimized support for SDRAM at 100 MHz and 66 MHz

- 32-bit primary PCI bus interface (PCI) with an integrated PCI arbiter

- AGP interface (AGP) with 133 MHz data transfer capability configurable as a secondary PCI bus

- Extensive data buffering between all interfaces for high throughput and concurrent operations

- Mobile and "Deep Green" desktop power management support

## 1.4 General Considerations

### 1.4.1 Voltage Definitions

For the purposes of this document, the following nominal voltage definitions are used:

| V <sub>CC</sub>     | 5.0 V                                            |

|---------------------|--------------------------------------------------|

| V <sub>CC3.3</sub>  | 3.3 V                                            |

| V <sub>CCCORE</sub> | Voltage is dependent on the four bit VID setting |

| V <sub>CC2.5</sub>  | 2.5 V                                            |

| V <sub>CC1.5</sub>  | 1.5 V                                            |

| V <sub>CCCMOS</sub> | 1.5 V or 2.5 V depending on processor            |

| V <sub>TT</sub>     | 1.5 V                                            |

| V <sub>REF</sub>    | 1.0 V                                            |

| AGPVREF             | 1.32 V                                           |

*Note:*  $V_{CC1.5}$  and  $V_{TT}$  must be sourced by the same voltage regulator.

#### 1.4.2 General Design Recommendations

- Intel recommends using a widely available, programmable Voltage Regulator Module (VRM) installed in a VRM header or an on-board programmable voltage regulator. Please see the *VRM 8.4 DC-DC Converter Design Guidelines*.

- Board designs targeted for system integrators should be designed according to the boxed processor electrical, mechanical, and thermal specifications provided in the boxed processor section of the *Intel<sup>®</sup> Celeron<sup>TM</sup> Processor* datasheet and the *Pentium<sup>®</sup> III Processor for the PGA370 Socket* datasheet. The most notable items are the required fan power header and fan/ heatsink physical clearance on the board.

## 1.5 Transitioning from an Intel<sup>®</sup> Pentium<sup>®</sup> II Processor / 440BX AGPset Design

The following sections detail the considerations for transitioning from a Intel 440BX AGPset / SC-242 connector design to a PGA370 socket design.

## 1.5.1 AGTL+ Termination

Intel recommends 56  $\Omega\pm 5\%$  resistors for AGTL+ termination on the board. In addition, high frequency  $V_{TT}$  decoupling is also required on the system board. Intel recommends 19 or more 0.1  $\mu F$  capacitors in the 0603 package with one capacitor for every two resistor packs (assumes four resistors per pack).

### 1.5.2 V<sub>REF</sub> Inputs

$V_{REF}$  (<sup>2</sup>/<sub>3</sub>  $V_{TT}$ ) must be supplied to the processor through each of the eight  $V_{REF}$  inputs. Intel recommends using one 75  $\Omega \pm 1\%$  and 150  $\Omega \pm 1\%$  resistor divider of the  $V_{TT}$  supply to generate  $V_{REF}$ . Intel also recommends placing four 0.1  $\mu$ F capacitors in the 0603 package within 500 mils of the processor's  $V_{REF}$  pins.

### 1.5.3 System Bus Clock

Due to the change in system bus trace lengths in the FC-PGA and PPGA packages, the chipset and processor clocks must be tied together to minimize pin-to-pin clock skew. Implementation details are provided in Section 2.5, "AGTL+ Layout Recommendations" on page 21.

It is also recommended that a capacitor site be placed near the processor BCLK input to allow the clock skew to be minimized through tuning. This can be done by changing the value at the capacitor site to compensate for the actual board trace lengths.

#### 1.5.4 CMOS Compatibility with Future Processors

All PGA370-based processor CMOS outputs are open drain and require a pull-up to drive to external logic. The 0.18 micron process technology utilizes 1.5 V-compatible CMOS signals and the 0.25 micron process technology utilizes 2.5 V-compatible CMOS signals. Intel recommends the following CMOS design guidelines.

Intel has defined three new pins for the all PGA370-based processors:

- $V_{CC2.5}$ : This pin should be connected to the system's 2.5 V supply.

- $V_{CC1.5}$ : This pin should be connected to the system's 1.5 V supply.

- $V_{CCCMOS}$ : This pin should be used as the system CMOS pull-up voltage. A 0.1  $\mu$ F decoupling capacitor is recommended.

$V_{CC1.5}$  and  $V_{TT}$  are recommended to be sourced by the same voltage regulator.

The V<sub>CCCMOS</sub> pin provides the CMOS voltage for the pull-up resistors required on the system board. A 2.5 V source must be provided to the V<sub>CC2.5</sub> pin and a 1.5 V source must be provided to the V<sub>CC1.5</sub> pin. The source for V<sub>CC1.5</sub> must be the same as the one supplying V<sub>TT</sub>. The processor routes the compatible CMOS voltage source (1.5 V or 2.5 V) through the package and out to the

$V_{CCCMOS}$  output pin. Processors based on 0.25 micron process technology (such as the Intel Celeron processor) use 2.5 V CMOS buffers. Processors based on 0.18 micron process technology (such as the Pentium III processor for the PGA370 socket) use 1.5 V CMOS buffers.

These pins have been defined to permit a maximum current of 500 mA.

#### 1.5.5 Processor Core Voltage Decoupling

The system board must implement high frequency decoupling for the processor core voltage. Intel recommends that ten or more 4.7  $\mu$ F capacitors in the 1206 package (ceramic X5R or better material) be placed within the socket cavity. Placement of the capacitors should minimize overall inductance between V<sub>CC</sub>/V<sub>SS</sub> power pins. Implementation details are provided in Section 4.3.5.1, "Core Voltage High-Frequency Decoupling" on page 47.

#### 1.5.6 VID[4] Pin

The Voltage ID pin VID[4] is not available on the processor. Therefore, according to the *VRM 8.4 DC-DC Converter Guidelines*, VID[4] must be connected to ground on the voltage regulator in order to provide the correct VID[3:0] for 1.30 V to 2.05 V voltage ID encoding.

#### 1.5.7 Phase Lock Loop (PLL) Power

All PGA370-based processors have internal PLL clock generators that are analog and require quiet power supplies to minimize jitter.

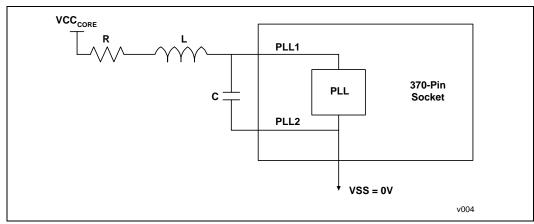

#### 1.5.7.1 PLL Topology

The general desired topology is shown in Figure 1. Not shown are parasitic routing and local decoupling capacitors. Excluded from the external circuitry are parasitics associated with each component. See Section 1.5.7.3, "PLL Filter Recommendation" on page 14 for R, L, and C values.

# intel®

## 1.5.7.2 PLL Filter Specification

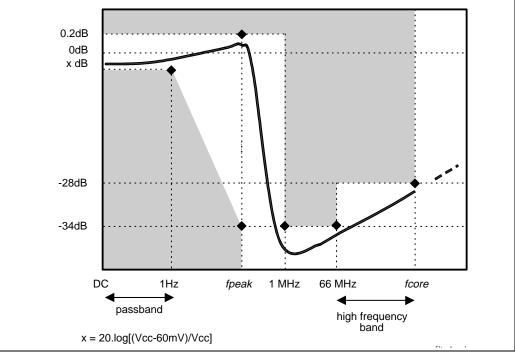

The function of the filter is to protect the PLL from external noise through low-pass attenuation. In general, the low-pass description forms an adequate description for the filter.

The low-pass specification, with input at  $V_{CCCORE}$  and output measured across the capacitor, is as follows:

- < 0.2 dB gain in pass band

- < 0.5 dB attenuation in pass band (see DC drop in the notes that follow Figure 2)

- > 34 dB attenuation from 1 MHz to 66 MHz

- > 28 dB attenuation from 66 MHz to core frequency

The filter specification is graphically shown in Figure 2.

#### Figure 2. PLL Filter Specification

#### NOTES:

- 1. Diagram not to scale.

- 2. No specification for frequencies beyond fcore.

- 3. fpeak, if it exists, should be less than 0.05 MHz.

Other requirements of the PLL filter are:

- The filter should support DC current > 30 mA.

- A shielded type inductor is required to minimize magnetic pickup.

- The DC voltage drop from  $V_{CC}$  to PLL1 should be < 60 mV, which in practice implies series  $R < 2 \Omega$ ; this also means that pass band attenuation (from DC to 1 Hz) is < 0.5 dB for  $V_{CC} = 1.1$  V, and < 0.35 dB for  $V_{CC} = 1.5$  V.

#### 1.5.7.3 PLL Filter Recommendation

The following tables are examples of components that meet Intel's recommendations, when configured in the topology shown in Figure 1.

#### Table 2. Recommended Inductor for PLL Filter

| Part Number           | Value  | Tolerance | SRF    | Rated I | DCR    |

|-----------------------|--------|-----------|--------|---------|--------|

| TDK MLF2012A4R7KT     | 4.7 µH | 10%       | 35 MHz | 30 mA   | 0.56 Ω |

| Murata LQG21N4R7K00T1 | 4.7 µH | 10%       | 47 MHz | 30 mA   | 0.70 Ω |

| Murata LQG21C4R7N00   | 4.7 µH | 30%       | 35 MHz | 30 mA   | 0.30 Ω |

#### Table 3. Recommended Capacitor for PLL Filter

| Part Number          | Value | Tolerance | ESL    | ESR     |

|----------------------|-------|-----------|--------|---------|

| Kemet T495D336M016AS | 33 µF | 20%       | 2.5 nH | 0.225 Ω |

| AVX TPSD336M020S0200 | 33 µF | 20%       | TBD    | 0.200 Ω |

#### Table 4. Recommended Resistor for PLL Filter

| Value | Tolerance | Power                          | Note                                                                                  |

|-------|-----------|--------------------------------|---------------------------------------------------------------------------------------|

| 1 Ω   | 10%       | <sup>1</sup> / <sub>16</sub> W | Resistor may be implemented with trace resistance, in which discrete R is not needed. |

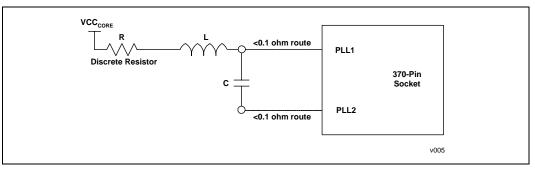

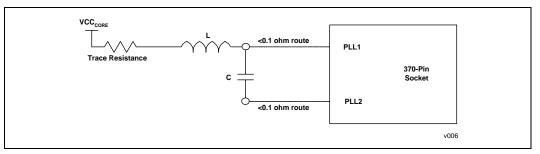

To satisfy damping requirements, total series resistance in the filter (from  $V_{CCCORE}$  to the top plate of the capacitor) must be at least 0.35  $\Omega$ . This resistor can be in the form of a discrete component, or routing, or both. For example, if the selected inductor has a minimum DCR of 0.25  $\Omega$ , then a routing resistance of at least 0.10  $\Omega$  is required. Be careful not to exceed the maximum resistance rule (2  $\Omega$ ). For example, if using discrete R1, the maximum DCR of the L should be less than 2.0 -1.1 = 0.9  $\Omega$ , which precludes using some inductors.

Other routing requirements:

- C should be close to PLL1 and PLL2 pins,  $< 0.1 \Omega$  per route. These routes do not count towards the minimum damping R requirement.

- The PLL2 route should be parallel and next to PLL1 route (to minimize loop area).

- L should be close to C; any routing resistance should be inserted between V<sub>CCCORE</sub> and L.

- Any discrete R should be inserted between V<sub>CCCORE</sub> and L.

Figure 3. Using Discrete R

#### Figure 4. No Discrete R

#### 1.5.8 **Bus Frequency Selection**

The PGA370-based processors utilize the BSEL[0] pins to select 66 MHz and 100 MHz from the CK100 clock synthesizer. Implementation details are provided in Section 3.0, "Scalable Performance Board Guidelines" on page 30.

#### 1.5.9 **New Pin Definitions**

The following new pins are required for correct operation of the processor. Implementation details are provided in Section 3.0, "Scalable Performance Board Guidelines" on page 30.

| CLKREF   | Requires a 1.25 V source                            |

|----------|-----------------------------------------------------|

| EDGCTRL  | Requires a 51 $\Omega$ ± 5% pull-up to $V_{CCCORE}$ |

| RESET2#  | Additional reset pin to the processor               |

| RTTCTRL  | Requires a 110 $\Omega$ ± 1% pull-down to $V_{SS}$  |

| SLEWCTRL | Requires a 110 $\Omega$ ± 1% pull-down to $V_{SS}$  |

#### 1.5.10 VCOREDET

The VCOREDET pin is not used in the Intel 440BX AGPset / PGA370 scalable performance board design.

Intel<sup>®</sup> 440BX AGPset / PGA370 Scalable Performance Board Design Guide

## 2.0 Layout and Routing Guidelines

This section describes layout and routing recommendations for ensuring a robust design. Follow these guidelines as closely as possible. Any deviations from the guidelines listed here should be simulated to ensure that adequate margin is maintained in the design.

## 2.1 BGA Quadrant Assignment

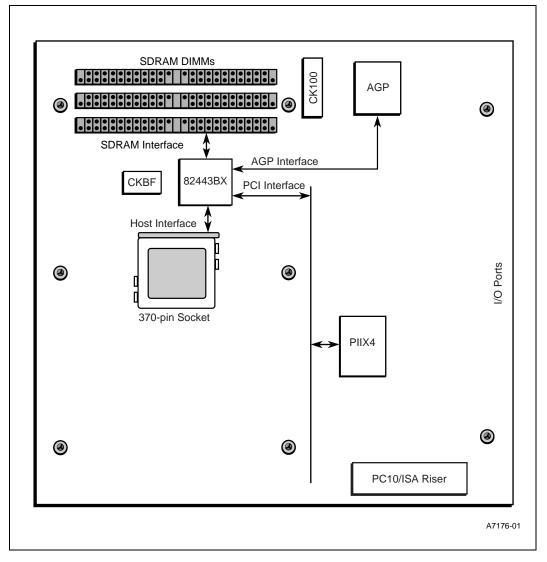

Intel assigned pins on the 82443BX to simplify routing and keep board fab costs down by permitting a board to be routed in four layers. Figure 5 shows the four signal quadrants of the 82443BX. The component placement on the board should be done with this general flow in mind. This simplifies routing and minimizes the number of signals that must cross. The individual signals within the respective groups have also been optimized in order to be routed using only two PCB layers.

For a complete list of signals and ball assignments, see the *Intel*<sup>®</sup> 440BX AGPset: 82443BX Host Bridge/Controller datasheet.

#### Figure 5. Major Signal Sections of the 82443BX (Top View)

## 2.2 PGA370-Based Processor Signal Quadrants

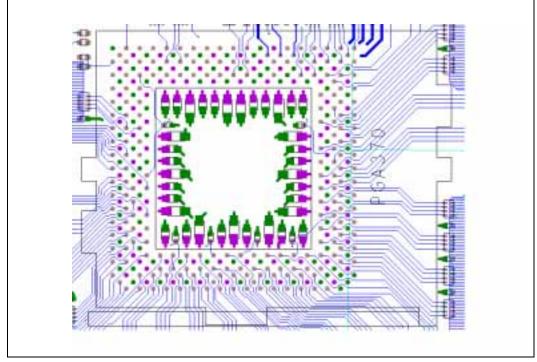

Figure 6 indicates the signal quadrants for all PGA370-based processors. These quadrants are defined to facilitate layout and placement and illustrate the proposed component placement for a PGA370-based processor for both ATX and NLX form factor designs.

ATX Form Factor:

- The ATX placement and layout shown in Figure 7 is recommended for a PGA370-based processor / Intel 440BX AGPset system design.

- The example placement shown in Figure 7 shows 4 PCI slots, 2 ISA slots, 3 DIMM sockets, and one AGP connector.

- For an ATX form factor design, the AGP-compliant graphics device can reside either on the board (device down option) or on an AGP connector (up option).

- The trace length limitation between critical connections is addressed in Section 2.5.2, "Recommended Trace Lengths" on page 22.

- Figure 7 is for *reference only*. The trade-off between the number of PCI and ISA slots, number of DIMM sockets, and other board peripherals must be evaluated for each design.

## Figure 7. Example ATX Placement for Intel<sup>®</sup> 440BX AGPset / PGA370-Based Processor Designs

# intel

NLX Form Factor:

- The NLX placement and layout shown in Figure 8 is recommended for a PGA370-based processor / Intel 440BX AGPset system design.

- The example placement below shows 3 DIMM sockets and an AGP compliant device down on the board. For an NLX form factor design, the AGP compliant graphics device may readily be integrated on the board (device down option). The trace length limitation between critical connections is addressed in Section 2.5.2, "Recommended Trace Lengths" on page 22.

- Figure 8 is for *reference only*; the trade-off between the number of DIMM sockets and other board peripherals must be evaluated for each design.

## Figure 8. Example NLX Placement for Intel<sup>®</sup> 440BX AGPset / PGA370-Based Processor Design

## 2.3 Board Description

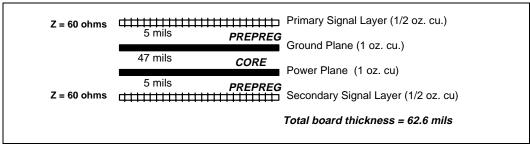

A 4-layer stack-up arrangement is recommended for the system board. An example of a 4-layer stack-up is shown in Figure 9. The impedance of all the signal layers should be between 55  $\Omega$  and 75  $\Omega$ . A lower trace impedance reduces signal edge rates, overshoot, and undershoot, and has less crosstalk than a higher trace impedance. A higher trace impedance increases edge rates and may slightly decrease signal flight times.

Figure 9. Four-Layer Board Stack-up Example

Note that the top and bottom routing layers specify 1/2 oz. cu. However, after the board is plated, the traces will be about 1 oz. cu. Check with your fab vendor for the exact value and ensure that any signal simulation accounts for this variation.

Note: A thicker core may help reduce board warpage issues.

Additional guidelines on board stack-up, placement, and layout include the following.

- The board impedance (Z) should be between 55  $\Omega$  and 75  $\Omega$  (65  $\Omega \pm 15\%$  is recommended).

- FR-4 material should be used for the board fabrication.

- The dielectric process variation in the PCB fabrication should be minimized.

- The ground plane should not be split on the ground plane layer. If a signal must be routed for a short distance on a power or ground plane, then it should be routed on a V<sub>CC</sub> plane, not the ground plane.

- Keep vias for decoupling capacitors as close to the capacitor pads as possible.

## 2.4 Routing Guidelines

This section lists guidelines to be followed when routing the signal traces during board design. The order in which signals are routed first and last will vary in different designs. Some designers prefer routing all of the clock signals first, while others prefer routing all of the high-speed bus signals first. Either order can be used, as long as the guidelines listed here are followed. If the guidelines listed here are not followed, it is important that your design is simulated, especially on the AGTL+ signals. Even when the guidelines are followed, it is recommended that you simulate as many signals as possible for proper signal integrity, flight time, and crosstalk.

## 2.4.1 AGTL+ Description

AGTL+ is the electrical bus technology used in the P6 family processors host bus architecture. AGTL+ is a low-output swing, incident wave switching, open-drain bus with external pull-up resistors that provide both the high logic level and termination at the end of the bus. The AGTL+ specification is contained in the *Intel*<sup>®</sup> *P6 Family Processor Developer's Manual*.

## 2.5 AGTL+ Layout Recommendations

This section contains the layout recommendations for the AGTL+ signals. The layout recommendations are derived from pre-layout simulations that Intel has performed.

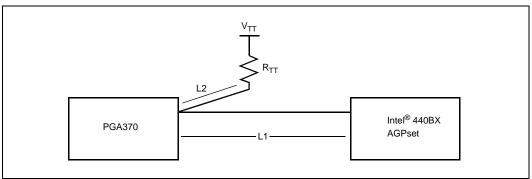

### 2.5.1 Network Topology and Conditions

Figure 10 shows the recommended topology for 66/100 MHz single processor systems. A termination resistor is placed on the system board. The recommended value for the termination resistor ( $R_{TT}$ ) is 56  $\Omega \pm 5\%$ .

#### Figure 10. Recommended Topology

#### 2.5.2 Recommended Trace Lengths

Table 5 summarizes trace length recommendations. The recommended lengths are derived from the parametric sweeps and Monte Carlo analysis.

#### Table 5. Recommended Trace Lengths

| Trace | Minimum Length | Maximum Length |  |  |

|-------|----------------|----------------|--|--|

| L1    | 1.8"           | 4.3"           |  |  |

| L2    | 0.5"           | 2.0"           |  |  |

The recommended topology for the AGTL+ bus is a single-ended termination topology. A resistor near the processor acts as the pull-up for the bus. In this case, it is recommended that the board trace length be L1.

The actual AGTL+ bus trace width is a standard 5 mil, with minimum edge-to-edge trace spacing set at 12 mils. This helps minimize possible crosstalk effects. The V<sub>TT</sub> voltage must be held to  $1.5 \text{ V} \pm 9\%$  (transient condition). It is required that V<sub>TT</sub> be held to  $1.5 \text{ V} \pm 3\%$  while the processor system bus is idle (static condition). This is measured at the PGA370 socket pins on the bottom side of the baseboard.

Intel recommends running analog simulations using the available I/O buffer models together with layout information extracted from your specific design. Simulation will confirm that the design adheres to the guidelines.

#### 2.5.2.1 Board Layout Rules

#### **AGTL+ Signals**

- AGTL+ signals should be routed with lengths between L1 of trace from the processor pin to the chipset.

- The AGTL+ signals trace length between the processor pin and the resistor pack should be within L2.

- Traces are to be routed with a minimum of 12 mil edge-to-edge spacing, and the ratio of this spacing to the dielectric thickness of the layer should be at least 2:1.

- The trace width is recommended to be 5 mils and not greater than 6 mils.

- The minimum spacing can be decreased to 5 mils for escaping the FC-PGA/PPGA and the BGA areas, for a length of less than 0.25".

- Intel recommends breaking out all signals from the CPU connector on the same layer. If routing is tight, break out from the connector on the opposite routing layer over a ground reference and cross over to the main signal layer near the CPU connector.

- It is strongly recommended that AGTL+ signals be routed on the signal layer next to the ground layer (referenced to ground).

- It is strongly recommended that splits be avoided in the reference plane. Splits disrupt signal return paths and increase overshoot/undershoot due to significantly increased inductance.

- Eliminate parallel traces between layers not separated by a power or ground plane.

- It is strongly recommended that AGTL+ signals do not traverse multiple signal layers.

- *Note:* Following the above layout rules is *critical* for AGTL+ signal integrity, particularly for processors based on the 0.18 micron process technology.

### 2.5.3 Additional Guidelines

General rules for minimizing the impact of crosstalk and other practical considerations in the design of a high speed AGTL+ bus, are provided in the  $Intel^{\mbox{\ensuremath{\mathbb{R}}}} 440BX AGPset Design Guide.$

## 2.6 Pre-Layout Simulation (Sensitivity Analysis)

#### 2.6.1 Simulation Parameter Values

#### **Parametric Sweeps**

The interconnect parameter values that were used in all parametric sweeps are summarized in Table 6.

| Parameter                    | Symbol                 | Min   | Min Typical |       | Tolerance |

|------------------------------|------------------------|-------|-------------|-------|-----------|

| FC-PGA On-die<br>Termination | R <sub>TT</sub> [Ω]    | 90    | 90 110      |       | 18%       |

| Board Impedance              | Ζ <sub>0</sub> [Ω]     | 74.75 | 65.00       | 55.25 | 15%       |

| Board Velocity               | S <sub>0</sub> [ns/ft] | 1.6   | 2.0         | 2.2   | 10-20%    |

| Board Termination            | R <sub>TT</sub> [Ω]    | 53    | 56          | 59    | 5%        |

|                              | V <sub>TT</sub> [V]    | 1.455 | 1.5         | 1.545 | 3%        |

| GTL Reference<br>Voltage     | V <sub>REF</sub> [V]   | 0.95  | 1.0         | 1.05  | 2%        |

| Connector<br>Impedance       | Ζ <sub>0</sub> [Ω]     | 50    | 65          | 75    | N/A       |

| Connector Velocity           | S <sub>0</sub> [ns/ft] | 30    | 100         | 120   | N/A       |

#### Table 6. Parameter Values for Interconnect AGTL+ Simulations

*Note:* For simulation purposes, the socket connector can be modeled as a transmission line. The length of the line and the propagation speed must be selected such that they give a total delay of 120 ps in the slow case and 30 ps in the fast case.

#### 2.6.2 Simulation Methodology

Analog simulations are recommended for high-speed system bus designs. Start simulations prior to layout. Pre-layout simulations provide a detailed picture of the working "solution space" that meets flight time and signal quality requirements. The layout recommendations in Section 2.5.2 are based on pre-layout simulations conducted at Intel. By basing board layout guidelines on the solution space, the iterations between layout and post-layout simulations can be reduced.

Intel recommends running simulations at the device pads for signal quality and at the device pins for timing analysis. However, simulation results at the device pins may be used later to correlate simulation performance against actual system measurements.

Pre-layout analysis includes timing analysis in Section 2.8 and sensitivity analysis using parametric sweeps. Parametric sweep analysis involves varying one or two system parameters while all others, such as driver strength, package,  $Z_0$ , and  $S_0$ , are held constant. This way, the

sensitivity of the proposed bus topology to varying parameters can be analyzed systematically. The sensitivity of the bus to minimum flight time, maximum flight time, and signal quality should be analyzed as follows:

- Minimum flight time is typically analyzed using fast I/O buffers, a fast package, a fast PGA370 socket, and fast interconnects.

- Maximum flight time is typically analyzed using slow I/O buffers, a slow package, a slow PGA370 socket, and slow interconnects.

- Signal quality is typically analyzed using fast I/O buffers, a slow package, a slow PGA370 socket, and fast interconnects.

The recommended sweep parameter values shown in Table 6 should be used for simulation. The values in Table 6 may be replaced if your supplier's specific capabilities are known. The corner values should comprehend the full range of manufacturing variation. The PGA370-based processor models include the I/O buffer models, core package and socket connector parasitics, package and socket connector trace length, impedance, and velocity. Intel 440BX AGPset models are available and include the I/O buffers and package traces. Termination resistors should be controlled to within  $\pm 5\%$ .

Outputs from each sweep should be analyzed to determine which regions meet timing and signal quality specifications. To establish the working solution space, find the common space across all the sweeps that result in passing timing and signal quality. The solution space should allow enough design flexibility for a feasible, cost-effective layout.

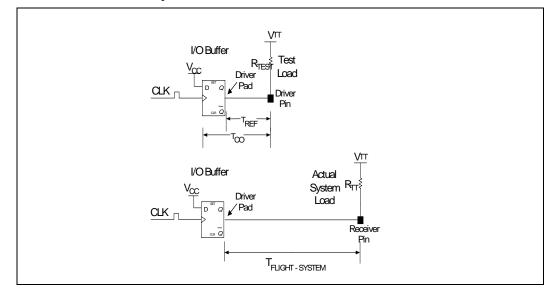

#### 2.6.2.1 Flight Time Simulation

Flight time is the time difference between a signal crossing  $V_{REF}$  at the input pin of the receiver and the output pin of the driver crossing  $V_{REF}$  where it drives a test load. The timings in the tables and topology discussed in this guideline assume the actual system load is 25  $\Omega$  for PPGA and 50  $\Omega$ for FC-PGA and is equal to the test load. The test load can be found in the Processor System Bus AC Specifications (GTL+ Signal Group) section of *Intel<sup>®</sup> Celeron<sup>TM</sup> Processor* datasheet and the *Pentium<sup>®</sup> III Processor for the PGA370 Socket* datasheet.

Figure 11. Test Load vs. Actual System Load

Figure 11 shows the different configurations for  $T_{CO}$  testing and flight time simulation. The flipflop represents the logic input and driver stage of a typical AGTL+ I/O buffer.  $T_{CO}$  timings are specified at the driver pin output.  $T_{FLIGHT-SYSTEM}$  is usually reported by a simulation tool as the time from the driver pad starting its transition to the time when the receiver's input pin sees a valid data input. Since both timing numbers ( $T_{CO}$  and  $T_{FLIGHT-SYSTEM}$ ) will include propagation time from the pad to the pin, it is necessary to subtract this time ( $T_{REF}$ ) from the reported flight time to avoid double counting.  $T_{REF}$  is defined as the time that it takes for the driver output pin to reach the measurement voltage,  $V_{REF}$ , starting from the beginning of the driver transition at the pad.  $T_{REF}$ must be generated using the same test load for  $T_{CO}$ . Intel provides this timing value in the AGTL+ I/O buffer models.

In this manner, the following valid delay equation is satisfied:

Valid Delay =  $T_{CO} + T_{FLIGHT-SYS} - T_{REF} = T_{CO-MEASURED} + T_{FLIGHT-MEASURED}$

The valid delay equation is the total time from when the driver sees a valid clock pulse to the time when the receiver sees a valid data input.

#### 2.6.2.2 Signal Quality Measurement

In addition to flight time simulations, waveforms on the AGTL+ bus must conform to signal quality specifications to ensure that system performance is not limited by interconnect noise. The signal quality specifications of the PGA370-based processors can be found in the *Intel<sup>®</sup> Celeron<sup>TM</sup> Processor* datasheet and the *Pentium<sup>®</sup> III Processor for the PGA370 Socket* datasheet.

## 2.7 Post-Layout Simulation

Following layout, extract the traces and run simulations to verify that the layout meets timing and noise requirements. A small amount of trace "tuning" may be required, but experience at Intel has shown that a sensitivity analysis significantly reduces the amount of tuning required.

The post layout simulations should take into account the expected variation for all interconnect parameters. Intel recommends running simulations at the device pads for signal quality and at the device pins for timing analysis. However, simulation results at the device pins may be used later to correlate simulation performance against actual system measurements. For timing simulations, use a  $V_{REF}$  of 2/3  $V_{TT} \pm 2\%$  for both the processor and Intel 440BX AGPset components. Flight times measured from the processor pins to other system components use the normal flight time method.

#### 2.7.1 Crosstalk and the Multi-Bit Adjustment Factor

Coupled lines should be included in the post-layout simulations. The flight times listed in Table 7 apply to single bit simulations only. They do not include an allowance for crosstalk. Crosstalk effects are accounted for separately, as part of the multi-bit timing adjustment factor ( $T_{adj}$ ), which is defined in Table 8. The recommended timing budget includes 400 ps for the adjustment factor.

Use caution in applying  $T_{adj}$  to coupled simulations. This adjustment factor encompasses effects other than board coupling, such as processor and package crosstalk and ground return inductances.

## 2.8 Timing Analysis

To determine the available flight time window, perform an initial timing analysis. Analysis of setup and hold conditions will determine the minimum and maximum flight time bounds for the system bus. Use the following equations to establish the system flight time limits.

### Table 7. PGA370-Based Processor and Intel<sup>®</sup> 440BX AGPset System Timing Equations

| Driver   | Receiver | Equation                                                                                                                                                            |  |  |  |  |

|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CPU      | 440BX    | $T_{\text{flight, min}} \ge T_{\text{hold}} - T_{\text{co,min}} + T_{\text{skew, CLK (CPU leads BX)}}$                                                              |  |  |  |  |

| CF0 440E | 44087    | T <sub>flight, max</sub> ≤ T <sub>cycle</sub> - T <sub>co,max</sub> - T <sub>su</sub> - T <sub>skew, CLK</sub> (BX leads CPU) - T <sub>jit</sub> - T <sub>adj</sub> |  |  |  |  |

| 440BX    | CPU      | T <sub>flight, min</sub> ≥ T <sub>hold</sub> - T <sub>co,min</sub> + T <sub>skew, CLK</sub> (BX leads CPU)                                                          |  |  |  |  |

|          | 010      | T <sub>flight, max</sub> ≤ T <sub>cycle</sub> - T <sub>co,max</sub> - T <sub>su</sub> - T <sub>skew, CLK</sub> (CPU leads BX) - T <sub>jit</sub> - T <sub>adj</sub> |  |  |  |  |

The terms used in the equations are described in Table 8.

### Table 8. PGA370-Based Processor and Intel<sup>®</sup> 440BX AGPset System Timing Terms

| Term                    | Description                                                                                                                                                                                                                                                                                                       |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>cycle</sub>      | System cycle time, defined as the reciprocal of the frequency.                                                                                                                                                                                                                                                    |

| T <sub>flight,min</sub> | Minimum system flight time.                                                                                                                                                                                                                                                                                       |

| T <sub>flight,max</sub> | Maximum system flight time.                                                                                                                                                                                                                                                                                       |

| T <sub>co,max</sub>     | Maximum driver delay from input clock to output data.                                                                                                                                                                                                                                                             |

| T <sub>co,min</sub>     | Minimum driver delay from input clock to output data.                                                                                                                                                                                                                                                             |

| T <sub>su</sub>         | Minimum setup time. Defined as the time for which the input data must be valid prior to the input clock.                                                                                                                                                                                                          |

| T <sub>h</sub>          | Minimum hold time. Defined as the time for which the input data must remain valid after the input clock.                                                                                                                                                                                                          |

| T <sub>skew,CLK</sub>   | Clock generator skew. Defined as the maximum delay variation between output clock signals from the system clock generator, the maximum delay variation between clock signals due to system board variation and Intel 440BX AGPset loading variation, and skew due to delay in the PGA370 socket.                  |

| T <sub>jit</sub>        | Clock jitter. Defined as the maximum edge to edge variation in a given clock signal.                                                                                                                                                                                                                              |

| T <sub>adj</sub>        | Multi-bit timing adjustment factor. This term accounts for the additional delay that occurs in the network when multiple data bits switch in the same cycle. The adjustment factor includes such mechanisms as package and PCB crosstalk, high inductance current return paths, and simultaneous switching noise. |

Component timings for the PGA370-based processors are available in the  $Intel^{\text{®}}$  Celeron<sup>TM</sup> Processor datasheet and the Pentium<sup>®</sup> III Processor for the PGA370 Socket datasheet, respectively.

Recommended values for system timings are contained in Table 9. Skew and jitter values for the clock generator device come from the clock driver vendor's datasheet. The PCB skew specification is based on the results of extensive simulations at Intel. The  $T_{adj}$  value is based on Intel's experience with systems that use the Pentium Pro and Pentium II processors.

| Timing Term                               | Value           |

|-------------------------------------------|-----------------|

| PGA370-based processors                   | PPGA<br>FC-PGA  |

| T <sub>skew,CLK</sub> (CPU leads BX) [ns] | 0.600<br>0.250  |

| T <sub>skew,CLK (BX leads CPU)</sub> [ns] | -0.250<br>0.100 |

| T <sub>jit</sub> [ns]                     | 0.25            |

| T <sub>adj</sub> [ns]                     | 0.40            |

#### Table 9. Recommended 66/100 MHz System Bus Timing Parameters

The flight time requirements that result from using the component timing specifications and recommended system timings are summarized in Table 7. All component values should be verified against the latest specifications before proceeding with analysis.

## 2.9 Host Clock Routing Spacing

The PGA370-based processor / Intel 440BX AGPset scalable performance board requires a clock synthesizer for supplying 66/100 MHz system bus clocks, PCI clocks, APIC clocks, SDRAM clocks, and 14 MHz clocks.

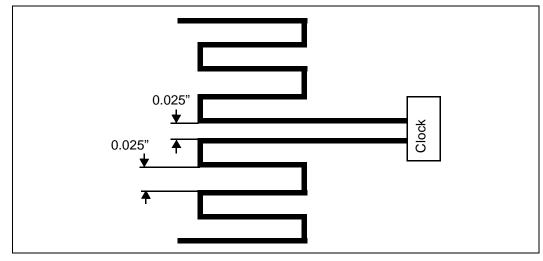

To minimize the impact of crosstalk, a minimum of 0.025" spacing should be maintained between the clock traces and other traces. A minimum spacing of 0.025" is also recommended for serpentines.

Figure 12. Clock Trace Spacing Guidelines

#### 2.9.1 System Clock Layout

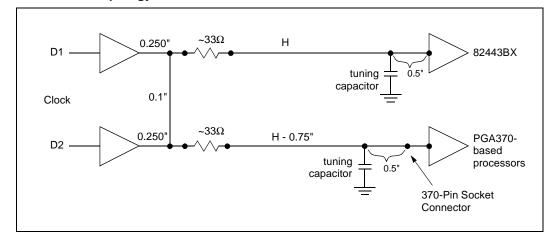

Intel recommends approximately 33  $\Omega$  series termination for all system bus clocks; this requirement is design-specific and may vary depending on the system bus clocks' signal integrity and the clock skew requirements. The pin-to-pin skew of the clock generator can be reduced by tying the clock driver pins together at the clock chip. The connection should be at a maximum distance of 0.250" from each driver and be at most 0.100" long. Also, the maximum trace length should not exceed 9.0". The recommended topology and trace lengths are defined in Table 10 and Figure 13.

The followings are additional recommended layout rules for the system bus clocks:

- It is recommended that system bus clocks be routed on the signal layer next to the ground layer (referenced to ground).

- It is strongly recommended that system bus clocks do not traverse multiple signal layers.

- System clock routing over power plane splits should be minimized.

Two items that must be considered when determining the clock lengths are the additional delay due to the socket (30 ps - 120 ps) and loading differences between the 82443BX and the processor. It is recommended that the total clock skew  $T_{skew, CLK}$ , including  $T_{skew, CLK}$  (CPU leads BX) and  $T_{skew, CLK}$  (BX leads CPU) be kept to the values specified in Table 9 in order to avoid affecting the timing budget.

Tuning capacitors are recommended on each clock signal. This requires placing 0603 package capacitor sites within 0.5" of both the socket connector and 82443BX ball. Each capacitor site should have a pad placed on the clock trace itself, avoiding the creation of a stub that can affect signal integrity on the clock line. The capacitor site allows the system designer the flexibility of adjusting the skew rate of each clock (adjusting the load), thereby minimizing the skew between them.

| Table 10. Host Clock Trace Length | Table 10. | Host C | lock Trace | Lengths |

|-----------------------------------|-----------|--------|------------|---------|

|-----------------------------------|-----------|--------|------------|---------|

| Net                        | Trace Length | Min   | Мах   |

|----------------------------|--------------|-------|-------|

| Clock Chip - PGA370 socket | H - 0.75"    | 1.25" | 8.25" |

| Clock Chip - 440BX         | Н            | 2.00" | 9.0"  |

Figure 13. Host Clock Topology

## 2.10 Other Buses

Buses not mentioned in the previous sections should adhere to the recommendations set forth in the Intel<sup>®</sup> 440BX AGPset Design Guide.

## 3.0 Scalable Performance Board Guidelines

## 3.1 **Processor Guidelines**

#### 3.1.1 Scalable Performance System Design DC Guidelines

The processor DC guidelines for scalable system designs provided in this section are defined at the processor pins. Table 11 lists the guidelines for PGA370-based processors. Specifications are valid only if specifications for case temperature, clock frequency, and input voltages are met. Be sure to read all notes associated with each parameter.

### Table 11. Voltage and Current Specifications<sup>1, 2</sup> for PGA370-Based Processors (Sheet 1 of 2)

| Symbol                                                      | Parameter                                                                           | Core Freq | Min    | Тур                 | Max   | Unit | Notes                    |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------|--------|---------------------|-------|------|--------------------------|

| V <sub>CCCORE</sub>                                         | V <sub>CC</sub> for processor core                                                  |           |        | 1.65                |       | V    | 3, 4, 17                 |

| V <sub>TT</sub> , V <sub>CC1.5</sub>                        | Static AGTL+ bus termination voltage                                                |           | 1.455  | 1.50                | 1.545 | V    | 1.5 ±3% <sup>5, 16</sup> |

| V <sub>TT</sub> , V <sub>CC1.5</sub>                        | Transient AGTL+ bus termination voltage                                             |           | 1.365  | 1.50                | 1.635 | V    | 1.5 ±9% <sup>5</sup>     |

| V <sub>REF</sub>                                            | AGTL+ input<br>reference voltage                                                    |           | -2%    | 2/3 V <sub>TT</sub> | +2%   | V    | ±2%, 7                   |

| V <sub>CLKREF</sub>                                         | CLKREF input<br>reference voltage                                                   |           | 1.169  | 1.25                | 1.331 | V    | ±6.5%, 15                |

| Baseboard<br>V <sub>CCCORE</sub><br>Tolerance,<br>Static    | Processor core<br>voltage static<br>tolerance level at the<br>PGA370 socket pins    |           | -0.080 |                     | 0.040 | V    | 6                        |

| Baseboard<br>V <sub>CCCORE</sub><br>Tolerance,<br>Transient | Processor core<br>voltage transient<br>tolerance level at the<br>PGA370 socket pins |           | -0.130 |                     | 0.080 | V    | 6                        |

| I <sub>CCCORE</sub>                                         | I <sub>CC</sub> for processor core                                                  |           |        |                     | 16.2  | А    | 3, 8, 9                  |

| ICCCMOS                                                     | I <sub>CC</sub> for V <sub>CCCMOS</sub>                                             |           |        |                     | 250   | mA   |                          |

| I <sub>CLKREF</sub>                                         | CLKREF voltage<br>supply current                                                    |           |        |                     | 60    | μA   |                          |

| I <sub>VTT</sub>                                            | Termination voltage supply current                                                  |           |        |                     | 2.7   | A    | 10                       |

| I <sub>SGnt</sub>                                           | I <sub>CC</sub> Stop-Grant for<br>processor core                                    |           |        |                     | 2.5   | А    | 8, 11                    |

| I <sub>SLP</sub>                                            | I <sub>CC</sub> Sleep for processor core                                            |           |        |                     | 2.5   | А    | 8                        |

| Table 11. Voltage and Current Specifications <sup>1, 2</sup> | <sup>2</sup> for PGA370-Based Processors (Sheet 2 of 2) |

|--------------------------------------------------------------|---------------------------------------------------------|

|--------------------------------------------------------------|---------------------------------------------------------|

| Symbol                   | Parameter                                        | Core Freq | Min | Тур | Max | Unit | Notes      |

|--------------------------|--------------------------------------------------|-----------|-----|-----|-----|------|------------|

| I <sub>DSLP</sub>        | I <sub>CC</sub> Deep Sleep for<br>processor core |           |     |     | 2.2 | А    |            |

| dl <sub>CCCORE</sub> /dt | Power supply current slew rate                   |           |     |     | 240 | A/µs | 12, 13, 14 |

| dl <sub>VTT</sub> /dt    | Termination current slew rate                    |           |     |     | 8   | A/µs | 12, 13     |

#### NOTES:

- 1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

- 2. All specifications in this table apply only to the PGA370-based processors.

- 3. V<sub>CCCORE</sub> and I<sub>CCCORE</sub> supply the processor core and the on-die L2 cache.

- Use the "typical voltage" specification with the "tolerance specifications" to provide correct voltage regulation to the processor.

- 5. V<sub>TT</sub> and V<sub>CC1.5</sub> must be held to 1.5 V ± 9% while the AGTL+ bus is active. It is required that V<sub>TT</sub> and V<sub>CC1.5</sub> be held to 1.5 V ± 3% while the processor system bus is static (idle condition). The required design target is ±3%; transient noise will add ±9%. This is measured at the PGA370 socket pins on the bottom side of the baseboard.

- These are the tolerance requirements, across a 20 MHz frequency bandwidth, measured at the processor socket pin on the soldered-side of the board. V<sub>CCCORE</sub> must return to within the static voltage specification within 100 ms after a transient event; see the VRM 8.4 DC-DC Converter Design Guidelines for further details.

- V<sub>REF</sub> should be generated from V<sub>TT</sub> by a voltage divider of 1% resistors or 1% matched resistors. Refer to the Intel<sup>®</sup> Pentium<sup>®</sup> II Processor Developer's Manual for more details on V<sub>REF</sub>.

- Max I<sub>CC</sub> measurements are measured at V<sub>CC</sub> typical voltage, under maximum signal loading conditions.

Voltage regulators may be designed with a minimum equivalent internal resistance to ensure that the output voltage, at maximum current output, is no greater than the nominal (i.e., typical) voltage level of V<sub>CCCORE</sub> (V<sub>CCCORE\_TYP</sub>). In this case, the maximum current level for the regulator, I<sub>CCCORE\_REG</sub> can be reduced from the specified maximum current I<sub>CCCORE\_MAX</sub> and is calculated by the equation:

ICCCORE\_REG = ICCCORE\_MAX × (VCCCORE\_TYP - VCCCORE\_STATIC\_TOLERANCE) / VCCCORE\_TYP

- 10. The current specified is the current required for a single processor. A similar amount of current is drawn through the termination resistors on the opposite end of the AGTL+ bus, unless single-ended termination is used.

- 11. The current specified is also for AutoHALT state.

- 12. Maximum values are specified by design/characterization at nominal V<sub>CCCORE</sub>.

- 13. These values are based on simulation and are averaged over the duration of any change in current. Use these values to compute the maximum inductance tolerable and the reaction time of the voltage regulator. This parameter is not tested.

- 14.dl<sub>CC</sub>/dt specifications are measured and specified at the PGA370 socket pins.

- 15.CLKREF must be held to 1.25 V ± 6.5%. This tolerance accounts for a ±5% power supply and ±1% resistor divider tolerance. It is recommended that the board generate the CLKREF reference from either the 2.5 V or 3.3 V supply. V<sub>TT</sub> should not be used due to risk of AGTL+ switching noise coupling to this analog reference.

- 16. Static voltage regulation includes: DC output initial voltage set point adjust, output ripple and noise, and output load ranges specified in the tables above.

- 17.Listed value is for the Pentium III processor at 850 MHz. Refer to the datasheet for other processor V<sub>CCCORE</sub> values.

#### 3.1.2 System Bus AC Guidelines

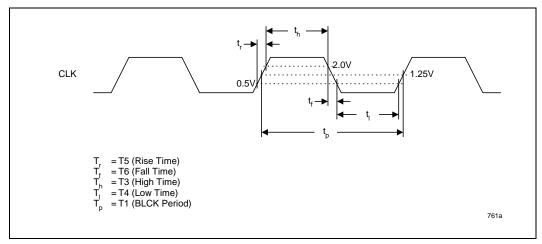

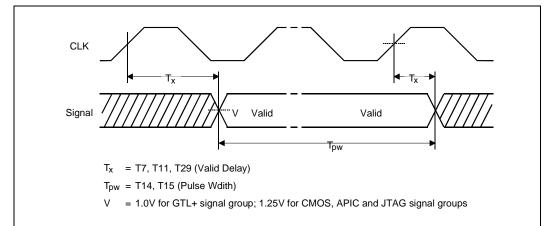

Table 12 and Table 13 contain 100 MHz system bus AC guidelines defined at the processor pins.

Table 12 contains the BCLK guidelines and Table 13 contains the AGTL+ system bus guidelines. Processor system bus AC specifications for the AGTL+ signal group at the processor pins for 100 MHz are equivalent to those at 66 MHz. The 66 MHz specification is documented in the processor datasheet.

## Table 12. Scalable Performance Board Processor System Bus AC Guidelines (Clock)<sup>1,2,3</sup> at the Processor Pins

| T# Parameter              | Min  | Nom | Max  | Unit | Figure | Notes                             |

|---------------------------|------|-----|------|------|--------|-----------------------------------|

| System Bus Frequency      |      |     | 100  | MHz  |        | All processor core<br>frequencies |

| T1: BCLK Period           | 10.0 |     |      | ns   | 14     | 4, 5                              |

| T2: BCLK Period Stability |      |     | ±250 | ps   | 14     | 5, 6, 7                           |

| T3: BCLK High Time        | 2.5  |     |      | ns   | 14     | @>2.0 V <sup>5</sup>              |

| T4: BCLK Low Time         | 2.4  |     |      | ns   | 14     | @<0.5 V                           |

| T5: BCLK Rise Time        | 0.4  |     | 1.6  | ns   | 14     | (0.5 V–2.0 V) <sup>5</sup>        |

| T6: BCLK Fall Time        | 0.4  |     | 1.6  | ns   | 14     | (2.0 V–0.5 V) <sup>5</sup>        |

#### NOTES:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies and cache sizes. 2. All AC timings for the AGTL+ signals are referenced to the BCLK rising edge at 1.25 V at the processor core pin. All AGTL+ signal timings (address bus, data bus, etc.) are referenced at 1.00 V at the processor

core pin. All AGTL+ signal timings (address bus, data bus, etc.) are referenced at 1.00 V at the processor core pins.3. All AC timings for the CMOS signals are referenced to the BCLK rising edge at 1.25 V at the processor