# Intel<sup>®</sup> Pentium<sup>®</sup> M Processor with 2-MB L2 Cache and 533-MHz System Bus for Embedded Applications

**Thermal Design Guide**

February 2005

Order Number: 305993, Revision: 1.0 February 2005

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® Pentium® M Processor with 2-MB L2 Cache and 533-MHz System Bus for Embedded Applications may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AlertVIEW, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Celeron M, Chips, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel Centrino, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Thermal Monitor, Intel Xeon, Intel XScale, IPLink, Itanium, LANDesk, LanRover, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, II Xeon, Pentium III Xeon, Pentium M, Performance at Your Command, RemoteExpress, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, Trillium, VoiceBrick, VTune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Order Number: 305993, Revision: 1.0

\*Other names and brands may be claimed as the property of others.

Copyright © 2005, Intel Corporation. All Rights Reserved.

| 1.0 | Intro                    | duction                                                                                                  |                                                                                                                                                                                                                                                                                                                                          | 7                                  |

|-----|--------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|     | 1.1<br>1.2<br>1.3<br>1.4 | Docum<br>Docum                                                                                           | nent Goalsnent Scopenent References                                                                                                                                                                                                                                                                                                      | 7<br>7                             |

| 2.0 | Desi                     | gn Guid                                                                                                  | lelines                                                                                                                                                                                                                                                                                                                                  | g                                  |

|     | 2.1                      | 2.1.1<br>2.1.2<br>Therm<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8<br>2.2.9 | Processor Package Volumetric Constraint Zones al Guidelines Processor Power Thermal Diode Thermal Monitor Power Density and Non-Uniform Heating Thermal Solution Requirements Reference Heatsink Design Thermal Interface Material (TIM) Recommended Thermal Solution Attachment Method Intel® Pentium® M Processor Thermal Test Vehicle | 9 17 17 19 20 21 23 23 25 28 29 29 |

| 3.0 | Third                    | _                                                                                                        | Vendor-Enabled Active Heatsinks                                                                                                                                                                                                                                                                                                          |                                    |

|     | 3.1                      | 3.1.1<br>3.1.2<br>3.1.3                                                                                  | ations  EEP-N41ES-02 and EEB-N41ES-02  EEP-N41CS-01 and EEB-N41CS-01  EEP-N41SS-01 and EEB-N41SS-01  al Interface Material and Considerations                                                                                                                                                                                            | 30<br>31<br>32                     |

| 4.0 | Vend                     | dor Infor                                                                                                | rmation                                                                                                                                                                                                                                                                                                                                  | 35                                 |

| Α   | Heat                     | sink Me                                                                                                  | chanical Drawings                                                                                                                                                                                                                                                                                                                        | 36                                 |

# **Figures**

| 1  | Micro-FCBGA Package Top and Bottom Isometric View                                          | 10 |

|----|--------------------------------------------------------------------------------------------|----|

| 2  | Micro-FCBGA Package Top and Side View                                                      | 10 |

| 3  | Micro-FCBGA Package Bottom View                                                            | 12 |

| 4  | Micro-FCPGA Package Top and Bottom Isometric View                                          |    |

| 5  | Micro-FCPGA Package – Bottom View                                                          | 14 |

| 6  | Micro-FCPGA Package – Top and Side View                                                    | 15 |

| 7  | Intel® Pentium® M Processor in the Micro-FCBGA Package Mechanical Stack-up                 |    |

|    | in the AdvancedTCA* Form Factor                                                            | 17 |

| 8  | Intel® Pentium® M Processor in the micro-FCPGA Package Mechanical Stack-up                 |    |

|    | in the AdvancedTCA* Form Factor                                                            | 18 |

| 9  | Intel® Pentium® M Processor in the micro-FCPGA Package Mechanical Stack-up                 |    |

|    | in the 1U Form Factor                                                                      | 18 |

| 10 | Thermal Resistance Values for the Intel® Pentium® M Processor 760                          |    |

|    | at Various Local Ambient Operating Temperatures                                            | 24 |

| 11 | Intel <sup>®</sup> Pentium <sup>®</sup> M Processor AdvancedTCA* Reference Design Heatsink |    |

|    | Thermal Performance Curve                                                                  |    |

| 12 | Heatsink Orientation Relative to Airflow Direction                                         |    |

| 13 | Active Aluminum Heatsink, EEP-N41ES-02 and EEB-N41ES-02                                    |    |

| 14 | Active Copper Heatsink, EEP-N41CS-01 and EEB-N41CS-01                                      |    |

| 15 | Copper Active Heatsink, EEP-N41SS-01 and EEB-N41SS-01                                      |    |

| 16 | Intel® Pentium® M Processor Reference Heatsink for ATCA Form Factor                        | 36 |

| 17 | Active Heatsink Volumetric Constraint Zone (Primary Side)                                  | 37 |

| 18 | Heatsink Volumetric Constraint Zone (Secondary Side)                                       | 38 |

| 19 | Recommended PCB Volumetric Constraint Zone for the                                         |    |

|    | Intel® Pentium® M Processor in the AdvancedTCA* Form Factor                                | 39 |

# **Tables**

| 1 | Document References                                    |    |

|---|--------------------------------------------------------|----|

|   | Definitions of Terms                                   |    |

|   | Micro-FCBGA Package Dimensions                         |    |

|   | Micro-FCPGA Package Dimensions                         |    |

| 5 | Intel® Pentium® M Processor 760 Thermal Specifications | 19 |

|   | Aluminum Active Heatsink Thermal Performance           |    |

|   | Active Copper Heatsink Thermal Performance             |    |

|   | Copper Active Heatsink Thermal Performance             |    |

|   | Vendor Contact Information                             |    |

# **Revision History**

| Date          | Revision | Description                      |

|---------------|----------|----------------------------------|

| February 2005 | 1.0      | Initial release of this document |

## 1.0 Introduction

This document describes thermal design guidelines for the Intel<sup>®</sup> Pentium<sup>®</sup> M Processor with 2-MB L2 Cache and 533-MHz System Bus for Embedded Applications in the Micro-Flip Chip Ball Grid Array (micro-FCBGA) package and the Micro-Flip Chip Pin Grid Array (micro-FCPGA) package. Detailed mechanical and thermal specifications for this processor can be found in the *Intel<sup>®</sup> Pentium<sup>®</sup> M Processor with 2-MB L2 Cache and 533-MHz System Bus Datasheet* (305262).

The information provided in this document is for reference only; additional validation must be performed prior to implementing the thermal designs into final production. The intent of this document is to assist OEMs with the development of thermal solutions for their individual designs. It is the responsibility of each OEM to validate the thermal solution design, including the heatsink, attachment method, and thermal interface material (TIM) with their specific applications.

#### 1.1 Document Goals

This document describes the thermal characteristics of the Intel<sup>®</sup> Pentium<sup>®</sup> M Processor and provides guidelines for meeting the thermal requirements. The thermal solutions presented in this document are specifically designed for applied computing applications in the AdvancedTCA<sup>\*</sup> and larger form factors.

## 1.2 Document Scope

This document discusses the thermal management techniques for the Intel<sup>®</sup> Pentium<sup>®</sup> M Processor, specifically in embedded computing applications. The physical dimensions and power numbers used in this document are for reference only. Please refer to the processor's datasheet for the product dimensions, thermal power dissipation, and maximum junction temperature. In case of conflict, the data in the datasheet supersedes any data in this document.

#### 1.3 Document References

#### Table 1. Document References

| Title                                                                           | Number |

|---------------------------------------------------------------------------------|--------|

| Intel® Pentium® M Processor with 2-MB L2 Cache and 533-MHz System Bus Datasheet | 305262 |

| Intel® Mobile Processor Micro-FCPGA Socket (mPGA479M) Design Guidelines         | 298520 |

Thermal Design Guide February 2005

Order Number: 305993, Revision: 1.0 7

## 1.4 Definition of Terms

#### Table 2. Definitions of Terms

| Term                                          | Definition                                                                                                                                                                                                                                                                                        |  |  |  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CFM                                           | Cubic Feet per Minute                                                                                                                                                                                                                                                                             |  |  |  |

| LFM                                           | Linear Feet per Minute                                                                                                                                                                                                                                                                            |  |  |  |

| РСВ                                           | Printed Circuit Board                                                                                                                                                                                                                                                                             |  |  |  |

| $\Psi_{JA}$                                   | Junction-to-Ambient thermal characterization parameter (psi), which is a measure of thermal solution performance using total package power. It is defined as (T $_J$ - T $_A$ ) / Total Package Power. NOTE: Heat source must be specified for $\Psi$ measurements.                               |  |  |  |

| $\Psi_{JS}$                                   | Junction-to-Sink thermal characterization parameter, which is a measure of thermal interface material performance using total package power. It is defined as $(T_J - T_S)$ / Total Package Power, also referred to as $\Psi_{TIM}.$ NOTE: Heat source must be specified for $\Psi$ measurements. |  |  |  |

| Ψ <sub>SA</sub>                               | Sink-to-Ambient thermal characterization parameter, which is a measure of the heatsink performance using total package power. It is defined as (T <sub>S</sub> - T <sub>A</sub> )/Total Package Power.  NOTE: Heat source must be specified for Ψ measurements.                                   |  |  |  |

| T <sub>junction</sub>                         | The measured junction temperature of the processor. Also referred to as $T_{j}$ .                                                                                                                                                                                                                 |  |  |  |

| T <sub>junction-max</sub>                     | The maximum junction temperature of the processor, as specified in the processor datasheet. Also referred to as T <sub>j-max</sub> .                                                                                                                                                              |  |  |  |

| T <sub>LA</sub> (T <sub>Local-Ambient</sub> ) | The measured ambient temperature locally surrounding the processor. The ambient temperature must be measured approximately one inch (25.4 mm) upstream of a passive heatsink, or at the fan inlet of an active heatsink                                                                           |  |  |  |

| Thermal Design Power (TDP)                    | A power dissipation target based on worst-case applications. Thermal solutions must be designed to dissipate the thermal design power.                                                                                                                                                            |  |  |  |

| Thermal Interface Material (TIM)              | The thermally conductive compound between the heatsink and processor die. This material fills air gaps and voids, and improves the spread of heat from the die to the heatsink.                                                                                                                   |  |  |  |

| U                                             | A unit of measure used to define server rack spacing height. 1U is equal to 1.75 inches, 2U equals 3.50 inches, etc.                                                                                                                                                                              |  |  |  |

## 2.0 Design Guidelines

The thermal solutions presented in this document were designed to fit within the maximum component height allowed by certain embedded form-factor specifications, including the AdvancedTCA\* form factor. The thermal solutions may be valid for other form factors; however, individual applications must be verified.

In some cases, prototype parts have been fabricated for verification testing. It is important to note that the thermal verification information described in this document is not adequate for statistical purposes. The intent of testing was only to verify that the thermal components were performing within reasonable expectations, based on computer modeling and component specifications.

#### 2.1 Mechanical Guidelines

### 2.1.1 Processor Package

The Intel<sup>®</sup> Pentium<sup>®</sup> M Processor is available in the 479-Ball Micro-Flip Chip Ball Grid Array (micro-FCBGA) package and the 478-pin Micro-Flip Chip Pin Grid Array (micro-FCPGA) package technology. Detailed mechanical specifications for the processor can be obtained from the processor datasheet.

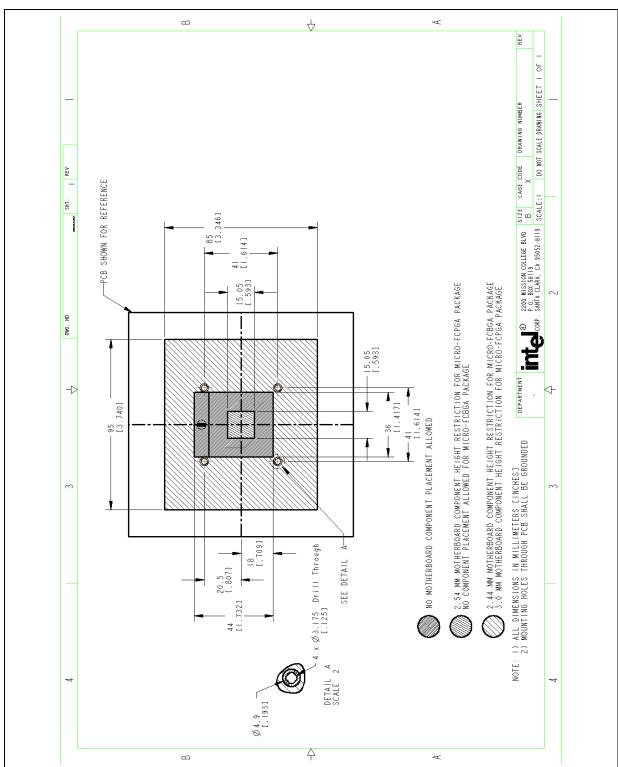

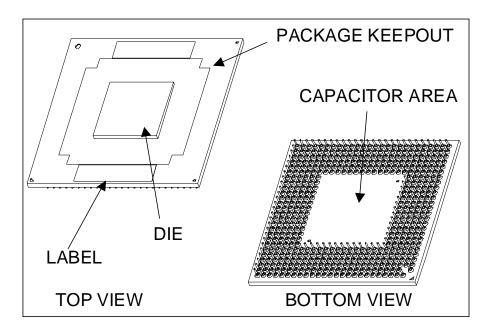

Figure 1, Figure 2, and Figure 3 show different views of the micro-FCBGA package; dimensions are provided in Table 3.

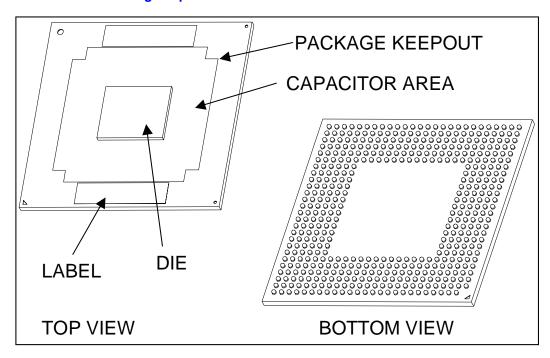

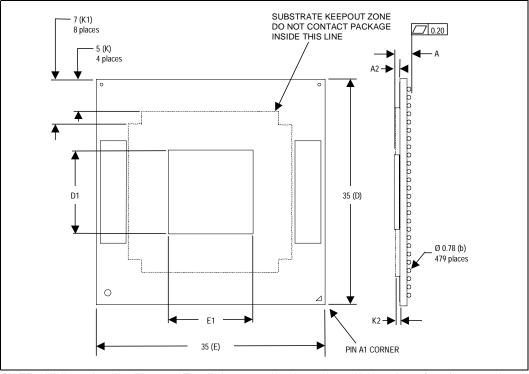

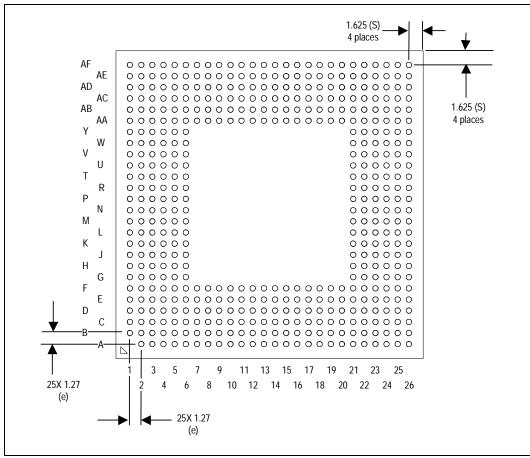

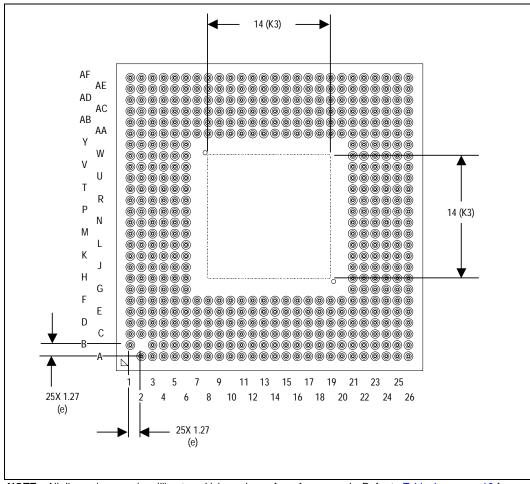

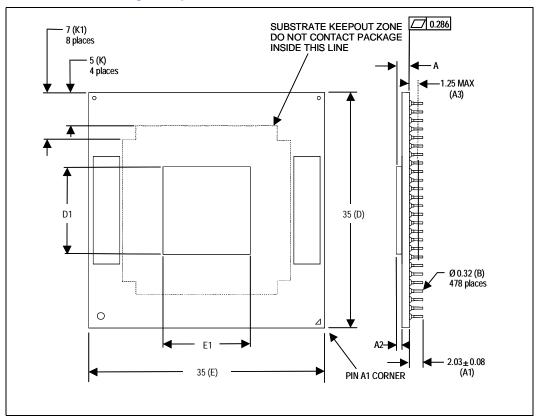

Figure 4, Figure 5, and Figure 6 show different views of the micro-FCPGA package; dimensions in Table 4.

Refer to the Intel® Pentium® M Processor with 2-MB L2 Cache and 533-MHz System Bus Datasheet for detailed information.

The micro-FCBGA package may have capacitors placed in the area surrounding the die. Since die-side capacitors are electrically conductive, and only slightly shorter than the die height, care must be taken to avoid contacting the capacitors with electrically conductive materials. Doing so can short-circuit the capacitors and possibly damage the device or render it inactive. The use of an insulating material between the capacitors and the thermal solution must be considered to prevent capacitor shorting.

Thermal Design Guide February 2005

Order Number: 305993, Revision: 1.0 9

Figure 1. Micro-FCBGA Package Top and Bottom Isometric View

Figure 2. Micro-FCBGA Package Top and Side View

NOTE: All dimensions in millimeters. The die is centered on the package. Values shown for reference only. Refer to Table 3 on page 11 for details.

February 2005

10 Order Number: 305993, Revision: 1.0

## Intel®Pentium® M Processor with 2-MB L2 Cache and 533-MHz System Bus

#### Table 3. Micro-FCBGA Package Dimensions

| Symbol           | Parameter                                          | Min. | Max.  | Unit |

|------------------|----------------------------------------------------|------|-------|------|

| Α                | Overall height, as delivered (see Note 1)          | 2.60 | 2.85  | mm   |

| A2               | Die height                                         | 0.   | 0.82  |      |

| b                | Ball diameter                                      | 0.   | 78    | mm   |

| D                | Package substrate length                           | 34.9 | 35.1  | mm   |

| E                | Package substrate width                            | 34.9 | 35.1  | mm   |

| D1               | Die length                                         | 12   | .54   | mm   |

| E1 Die width     |                                                    | 6.99 |       | mm   |

| е                | Ball pitch                                         | 1.27 |       | mm   |

| K                | Package edge keep-out                              | 5    |       | mm   |

| K1               | Package corner keep-out                            | -    | 7     | mm   |

| K2               | Die-side capacitor height                          | _    | 0.7   | mm   |

| S                | Package edge to first ball center                  | 1.6  | 1.625 |      |

| N                | N Ball count                                       |      | 479   |      |

| _                | Solder ball co-planarity                           |      | .2    | mm   |

| Pdie             | Allowable pressure on the die for thermal solution | _    | 689   | kPa  |

| W Package weight |                                                    | 4    | .5    | g    |

#### NOTE:

Thermal Design Guide February 2005

Order Number: 305993, Revision: 1.0 February 2005

Overall height as delivered. Values are based on design specifications and tolerances. This dimension is subject to change based on OEM motherboard design or OEM SMT process.

Figure 3. Micro-FCBGA Package Bottom View

NOTE: All dimensions in millimeters. Values shown for reference only. Refer to Table 3 on page 11 for details.

Figure 4. Micro-FCPGA Package Top and Bottom Isometric View

Figure 5. Micro-FCPGA Package - Bottom View

NOTE: All dimensions are in millimeters. Values shown for reference only. Refer to Table 4 on page 16 for details.

Figure 6. Micro-FCPGA Package – Top and Side View

**NOTE:** All dimensions are in millimeters. The die is centered on the package. Values shown for reference only. Refer to Table 4 on page 16 for details.

#### Table 4. Micro-FCPGA Package Dimensions

| Symbol                         | Parameter                                                                | Min. | Max. | Unit |

|--------------------------------|--------------------------------------------------------------------------|------|------|------|

| Α                              | Overall height, top of die to package seating plane                      | 1.88 | 2.02 | mm   |

| -                              | Overall height, top of die to PCB surface, including socket (See Note 1) | 4.74 | 5.16 | mm   |

| A1                             | Pin length                                                               | 1.95 | 2.11 | mm   |

| A2                             | Die height                                                               | 0.0  | 320  | mm   |

| А3                             | Pin-side capacitor height                                                | _    | 1.25 | mm   |

| В                              | Pin diameter                                                             | 0.28 | 0.36 | mm   |

| D                              | Package substrate length                                                 | 34.9 | 35.1 | mm   |

| Е                              | Package substrate width                                                  | 34.9 | 35.1 | mm   |

| D1                             | Die length                                                               | 12   | .54  | mm   |

| E1                             | E1 Die width                                                             |      | 6.99 |      |

| е                              | e Pin pitch                                                              |      | 1.27 |      |

| K                              | K Package edge keep-out                                                  |      | 5    |      |

| K1                             | K1 Package corner keep-out                                               |      | 7    |      |

| K3 Pin-side capacitor boundary |                                                                          | 14   |      | mm   |

| N                              | N Pin count                                                              |      | 78   | each |

| Pdie                           | Allowable pressure on the die for thermal solution                       | _    | 689  | kPa  |

| W                              | Package weight                                                           | 4    | .5   | g    |

|                                | Package Surface Flatness                                                 | 0.2  | 286  | mm   |

#### NOTE:

<sup>1.</sup> Overall height with socket is based on design dimensions of the Micro-FCPGA package with no thermal solution attached. Values are based on design specifications and tolerances. This dimension is subject to change based on socket design, OEM motherboard design or OEM SMT process.

#### 2.1.2 Volumetric Constraint Zones

The volumetric constraint zone for the reference AdvancedTCA\* thermal solution reserved for the processor package, heatsink, and heatsink attachment method for the baseboard is shown in Figure 18, "Heatsink Volumetric Constraint Zone (Secondary Side)" on page 38 and Figure 19, "Recommended PCB Volumetric Constraint Zone for the Intel® Pentium® M Processor in the AdvancedTCA\* Form Factor" on page 39 in the appendix. This constraint zone is based on the reference solution for the AdvancedTCA\* form factor. Volumetric constraint zones might differ for other thermal solution designs.

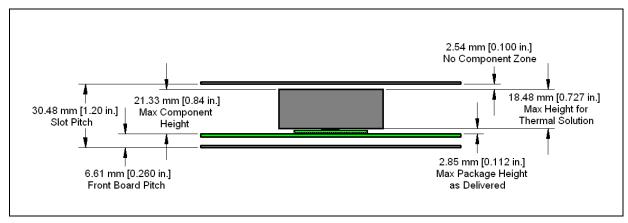

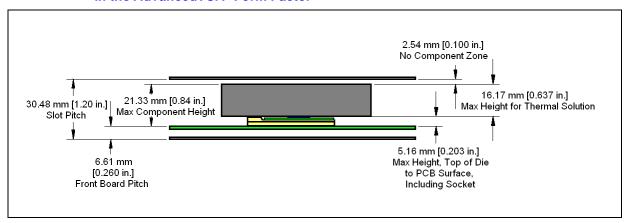

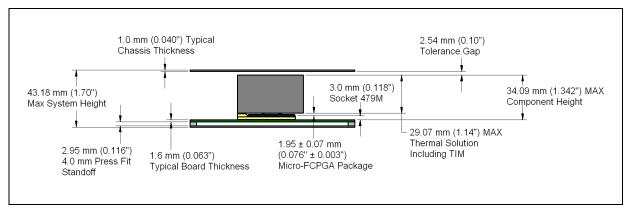

The volumetric constraint zone for the Intel® Pentium® M Processor for the third-party vendor enabled heatsinks are shown in Figure 17 and Figure 18 in the appendix. Figure 7 (below) shows the micro-FCBGA processor package mechanical stack-up in the AdvancedTCA\* form factor and the allowable z-height for the thermal solution. Figure 8 on page 18 shows the Intel® Pentium® M Processor in the micro-FCPGA package in the AdvancedTCA\* form factor. Figure 9 on page 18 shows the mechanical stack-up in the 1U form factor.

Figure 7. Intel® Pentium® M Processor in the Micro-FCBGA Package Mechanical Stack-up in the AdvancedTCA\* Form Factor

Intel® Pentium® M Processor in the micro-FCPGA Package Mechanical Stack-up Figure 8. in the AdvancedTCA\* Form Factor

Intel® Pentium® M Processor in the micro-FCPGA Package Mechanical Stack-up Figure 9. in the 1U Form Factor

February 2005 Thermal Design Guide Order Number: 305993, Revision: 1.0

#### 2.2 Thermal Guidelines

The performance of the thermal solution depends on many parameters, including the following processor characteristics:

- Thermal design power (TDP)

- Maximum junction temperature (T<sub>junction-max</sub>)

- · Operating ambient temperature

- System airflow

The guidelines and recommendations presented in this document are based on specific parameters. It is the responsibility of each product design team to verify that thermal solutions are suitable for their specific use.

To develop a reliable thermal solution, all of the appropriate variables must be considered. Thermal simulations and characterizations must be carried out while accounting for all system parameters. The solutions presented in this document must be validated as specified in their final intended system.

Thermal data for the Intel<sup>®</sup> Pentium<sup>®</sup> M Processor are presented in Table 5. The data is provided for informational purposes only. Please refer to the processor's datasheet for the most current data. In the event of conflict, the processor's datasheet supersedes information provided in this document.

#### Table 5. Intel® Pentium® M Processor 760 Thermal Specifications

| Processor | Core Frequency | Thermal Design | Minimum        | Maximum        |  |

|-----------|----------------|----------------|----------------|----------------|--|

| Number    | (GHz)          | Power (W)      | Tjunction (°C) | Tjunction (°C) |  |

| 760       | 2.0            | 27.0           | 0              |                |  |

#### 2.2.1 Processor Power

The processor's power is specified as Thermal Design Power (TDP) for thermal solution design. TDP is defined as the worst-case power dissipated by the processor while executing publicly available software under normal operation conditions, at nominal voltages that meet the load line specifications. The Intel TDP specification is a recommended design point and is not representative of the absolute maximum power the processor may dissipate under worst-case conditions. For any excursions beyond TDP, the Thermal Monitor feature is available to maintain the processor thermal specifications. Refer to the processor datasheet for details regarding the thermal design power specifications and the Thermal Monitor.

Thermal Design Guide February 2005

Order Number: 305993, Revision: 1.0 February 2005

#### 2.2.2 **Thermal Diode**

The Intel<sup>®</sup> Pentium<sup>®</sup> M processor incorporates two methods of monitoring die temperature, the Intel® Thermal Monitor and the thermal diode. The Intel Thermal Monitor must be used to determine when the maximum specified processor junction temperature has been reached. The second method, the thermal diode, can be read by an off-die analog/digital converter (a thermal sensor) located on the motherboard, or by a stand-alone measurement kit. The thermal diode can be used to monitor the die temperature of the processor for thermal management or instrumentation purposes but cannot be used to indicate that the maximum  $T_I$  of the processor has been reached. The thermal diode can only be used for long-term, steady-state measurement of die temperature. It is not suitable for real-time thermal management. For more information, refer to the Intel® Pentium® M Processor with 2 MB L2 Cache and 533 MHz System Bus Datasheet.

Note: The reading of the external thermal sensor (on the motherboard) connected to the processor thermal diode signals does not necessarily reflect the temperature of the hottest location on the die. Inaccuracies can include the following:

- the external thermal sensor

- on-die temperature gradients between the location of the thermal diode and the hottest location on the die

- time-based variations in the die temperature measurement

Time-based variations can occur when the sampling rate of the thermal diode (by the thermal sensor) is slower than the rate at which the T<sub>I</sub> temperature changes.

February 2005 Thermal Design Guide Order Number: 305993, Revision: 1.0 20

#### Intel®Pentium® M Processor with 2-MB L2 Cache and 533-MHz System Bus

#### 2.2.3 Thermal Monitor

The Intel<sup>®</sup> Thermal Monitor is a feature of the Intel<sup>®</sup> Pentium<sup>®</sup> M processor that allows system designers to lower the cost of thermal solutions without compromising system integrity.

*Note:* The Intel<sup>®</sup> Thermal Monitor Automatic Mode must be enabled for the processor to operate within specifications.

By using a factory-tuned on-die temperature sensor and a fast-acting thermal control circuit (TCC), the processor, without the aid of any additional software or hardware, can restrict its die temperature to remain within factory specifications under typical real-world operating conditions. The Intel Thermal Monitor thus allows the processor and system thermal solutions to be designed much closer to the power envelopes of real applications, instead of being designed to the processor maximum power envelope.

The Intel Thermal Monitor helps control the processor temperature by activating the TCC when the processor silicon reaches its maximum operating temperature. The temperature at which the Intel Thermal Monitor activates the thermal control circuit is not user-configurable and is not software-visible. Bus traffic is snooped in the normal manner, and interrupt requests are latched (and serviced during the time that the clocks are on) while the TCC is active.

The Intel Thermal Monitor controls the processor temperature by modulating (starting and stopping) the processor core clocks or by initiating an Enhanced Intel SpeedStep<sup>®</sup> technology transition when the processor silicon reaches its maximum operating temperature. The Intel Thermal Monitor uses two modes to activate the TCC: Automatic Mode and On-Demand Mode. If both modes are activated, Automatic Mode takes precedence. There are two Automatic Modes called Intel Thermal Monitor 1 and Intel Thermal Monitor 2. These modes are selected by writing values to the Model Specific Registers (MSRs) of the processor.

Automatic Mode is required for the processor to operate within specifications and must first be enabled through BIOS. After Automatic Mode is enabled, the TCC activates only when the internal die temperature reaches the maximum allowed value for operation.

Likewise, when Intel Thermal Monitor 2 is enabled and a high-temperature situation exists, the processor performs an Enhanced Intel SpeedStep technology transition to a lower operating point. When the processor temperature drops below the critical level, the processor makes an Enhanced Intel SpeedStep technology transition to the last requested operating point. Intel Thermal Monitor 2 is the recommended mode on Intel<sup>®</sup> Pentium<sup>®</sup> M processors.

If a processor load-based Enhanced Intel SpeedStep technology transition through MSR write is initiated when an Intel Thermal Monitor 2 period is active, there are two possible results:

- 1. If the processor load-based Enhanced Intel SpeedStep technology transition target frequency is **higher** than the Intel Thermal Monitor 2 transition-based target frequency, the processor load-based transition is deferred until the Intel Thermal Monitor 2 event has been completed.

- 2. If the processor load-based Enhanced Intel SpeedStep technology transition target frequency is **lower** than the Intel Thermal Monitor 2 transition-based target frequency, the processor transitions to the processor load-based Enhanced Intel SpeedStep technology target frequency point.

Thermal Design Guide February 2005

Order Number: 305993, Revision: 1.0 21

When Intel Thermal Monitor 1 is enabled and a high-temperature situation exists, the clocks are modulated by alternately turning the clocks off and on at a 50% duty cycle. Cycle times are processor-speed-dependent and decrease linearly as processor core frequencies increase. After the temperature returns to a non-critical level, modulation ceases and TCC goes inactive. A small amount of hysteresis is included to prevent rapid active/inactive transitions of the TCC when the processor temperature is near the trip point. The duty cycle is factory-configured and cannot be modified. Also, Automatic Mode does not require any additional hardware, software drivers, or interrupt-handling routines. Processor performance is decreased by the same amount as the duty cycle when the TCC is active; however, with a properly designed and characterized thermal solution, the TCC will most likely never be activated, or will be activated only briefly during the most power-intensive applications.

The TCC can also be activated via On-Demand Mode. If a 1 is written to bit[4] of the ACPI Intel Thermal Monitor Control Register, the TCC is activated immediately, independent of the processor temperature. When using On-Demand Mode to activate the TCC, the duty cycle of the clock modulation is programmable via bits[3:1] of the same ACPI Intel Thermal Monitor Control Register. In Automatic Mode, the duty cycle is fixed at 50% on, 50% off; however in On-Demand Mode, the duty cycle can be programmed from 12.5% on/87.5% off, to 87.5% on/12.5% off, in 12.5% increments. On-Demand Mode can be used at the same time Automatic Mode is enabled; however, if the system tries to enable the TCC via On-Demand Mode at the same time Automatic Mode is enabled and a high-temperature condition exists, Automatic Mode takes precedence.

An external signal, PROCHOT# (processor hot) is asserted when the processor detects that its temperature is above the thermal trip point. Bus snooping and interrupt latching are also active while the TCC is active.

Note: PROCHOT# is not asserted when the processor is in the Stop Grant, Sleep, Deep Sleep and Deeper Sleep low-power states (internal clocks stopped); hence, the thermal diode reading must be used as a safeguard to maintain the processor junction temperature within the 100 °C (maximum) specification. If the platform thermal solution is not able to maintain the processor junction temperature within the maximum specification, the system must initiate an orderly shutdown to prevent damage. If the processor enters one of the above low-power states with PROCHOT# already asserted, PROCHOT# remains asserted until the processor exits the low-power state and the processor junction temperature drops below the thermal trip point.

If Automatic Mode is disabled, the processor is operating out of specification. Regardless of enabling the Automatic or On-Demand Modes, in the event of a catastrophic cooling failure, the processor automatically shuts down when the silicon has reached a temperature of approximately 125 °C. At this point, the FSB signal THERMTRIP# goes active. THERMTRIP# activation is independent of processor activity and does not generate any bus cycles. When THERMTRIP# is asserted, the processor core voltage must be shut down within the time specified in the Intel® Pentium® M Processor with 2-MB L2 Cache and 533-MHz System Bus Datasheet.

February 2005 Thermal Design Guide Order Number: 305993, Revision: 1.0

#### 2.2.4 Power Density and Non-Uniform Heating

The Intel<sup>®</sup> Pentium<sup>®</sup> M processor die does not exhibit an even power distribution over its surface area. Non-uniform power distributions might adversely affect the overall thermal solution performance. The thermal interface material, which functions as the first layer of heat spreading above the die, is most susceptible to non-uniform die power characteristics.

The power density factor for the Intel<sup>®</sup> Pentium<sup>®</sup> M processor is higher than on previous processors. Processor thermal solution designers must account for the increase in expected thermal impedance (or resistance) from the thermal interface material when it is attached to the processor die. Processor heatsink performance is not affected to the same degree as the TIM and is dependent on many factors, including heatsink size, base thickness, and material used. It is the responsibility of the OEM thermal solution designer to validate overall thermal solution performance.

#### 2.2.5 Thermal Solution Requirements

The thermal solutions in this document were designed based on the processor thermal specifications as outlined in the processor's datasheet for the worst-case conditions (i.e., Intel<sup>®</sup> Pentium<sup>®</sup> M Processor 760); hence, the solutions are suitable for other SKUs of the processor with equivalent or lower thermal specifications. The maximum allowable processor local ambient temperature will vary depending on the thermal solution and the amount of system airflow for the Intel<sup>®</sup> Pentium<sup>®</sup> M processor. The ambient temperature and airflow are based on a measurement approximately one inch (25.4 mm) upstream from the processor.

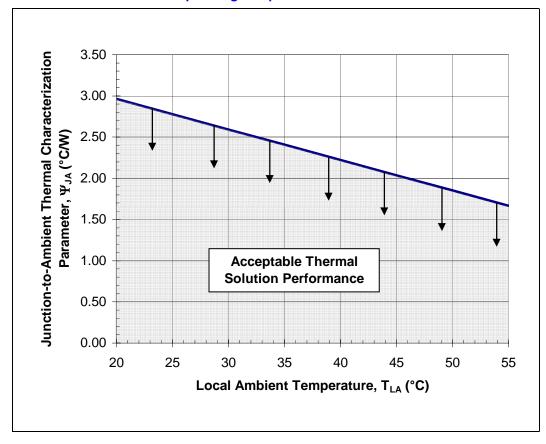

The thermal performance required for the heatsink is determined by calculating the junction-to-ambient thermal characterization parameter,  $\Psi_{JA}$ . This is a thermal engineering parameter that can be used to evaluate and compare different thermal solutions. For this particular processor,  $\Psi_{JA}$  is calculated as shown in Equation 1.

#### Equation 1. Calculation of $\Psi_{JA}$

$$\Psi_{JA} = \frac{T_{Jmax} \circ C - T_{LA} \circ C}{TDP(W)} = \frac{100 \circ C - 40 \circ C}{27.0 W} = 2.22 \frac{\circ C}{W}$$

Figure 10 further illustrates the required thermal performance for the Intel<sup>®</sup> Pentium<sup>®</sup> M Processor 760 at different operating ambient temperatures. The thermal solution used to cool the processor must have a junction-to-ambient thermal resistance less than or equal to the values shown for the given local ambient temperature.

Figure 10. Thermal Resistance Values for the Intel<sup>®</sup> Pentium<sup>®</sup> M Processor 760 at Various Local Ambient Operating Temperatures

#### 2.2.6 Reference Heatsink Design

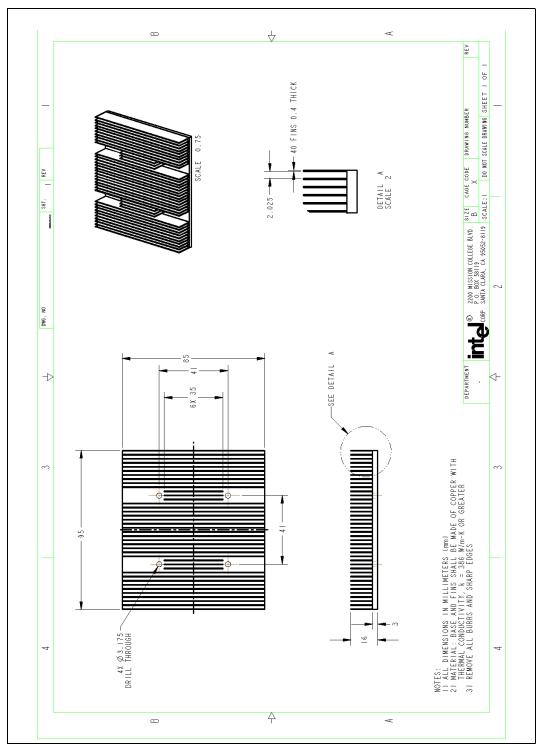

# 2.2.6.1 Intel<sup>®</sup> Pentium<sup>®</sup> M Processor Reference Design Heatsink for the AdvancedTCA\* Form Factor

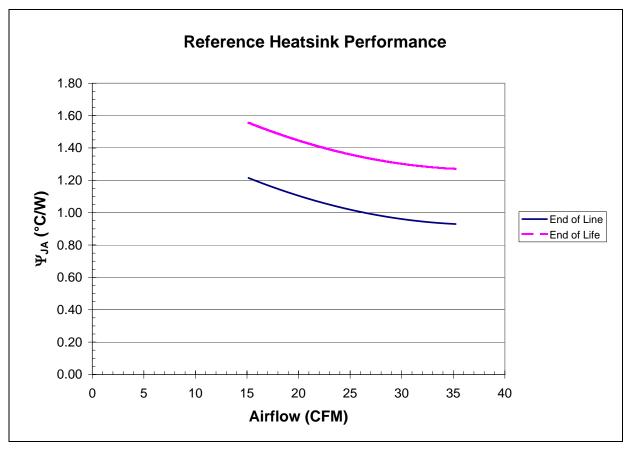

This heatsink is designed to meet the form factor volumetric constraints and thermal performance requirements for the AdvancedTCA form factor. The heatsink shown in Figure 16 was optimized using computational fluid dynamic (CFD) and thermal modeling software. The heatsink is optimized for non-ducted airflow, as measured approximately one inch upstream from the processor.

Figure 11 on page 26 shows the thermal performance for the heatsink in a non-ducted configuration. The junction-to-ambient thermal resistance depends significantly on the performance of the thermal interface material (TIM). The performance of the TIM degrades over time, which results in a higher thermal impedance. Figure 11 shows the performance of the reference heatsink with the TIM material at the End of Line and the estimated performance at the End of Life of the material. This thermal solution used the Honeywell\* PCM45F high-performance phase-change material TIM. Note that the resistance of the thermal solution has increased considerably at the end of life due to the TIM degradation. End of Line for a TIM material is when the TIM is first installed on the heatsink. End of Life is defined as a time in the future at which the material is deemed to be at the end of its useful life. The End of Life time varies for TIM material. It is recommended that thermal solution designers work with TIM manufacturers to determine the performance of the thermal interface material and its expected End of Life time length. System integrators might wish to replace the TIM during regularly scheduled maintenance periods in order maintain End of Line performance of the thermal solution.

The **performance of the reference thermal solution** is shown in Figure 11 at various rates of airflow through the slot. The maximum allowable local ambient temperature varies depending on the amount of airflow in the chassis. The performance of the heatsink is based on lab verification testing to ensure that the solution is performing within expectations. It is the responsibility of the system integrator to perform thermal solution validation, including heatsink, thermal interface material, and heatsink attach method.

Figure 11. Intel<sup>®</sup> Pentium<sup>®</sup> M Processor AdvancedTCA\* Reference Design Heatsink Thermal Performance Curve

#### 2.2.6.2 Heatsink Orientation Relative to Airflow

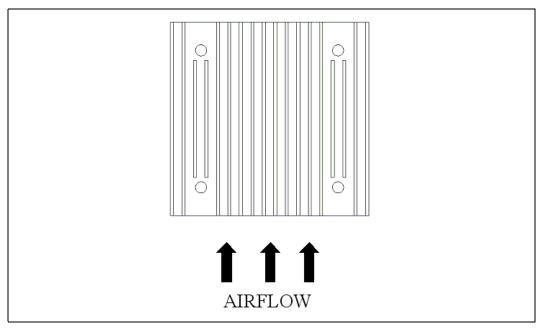

The heatsinks are designed to maximize the available space within the volumetric constraint zone. These heatsinks must be oriented in a specific direction relative to the processor volumetric constraint zone and airflow. In order to use this design, the processor must be placed on the PCB in an orientation such that the heatsink fins are parallel to the airflow. Figure 12 illustrates this orientation. A top view of the heatsink assembly is shown.

Figure 12. Heatsink Orientation Relative to Airflow Direction

#### 2.2.7 Thermal Interface Material (TIM)

It is important to understand and consider the impact that the interface between the processor and heatsink base has on the overall thermal solution. Specifically, the bond line thickness, interface material area, and interface material thermal conductivity must be selected to optimize the thermal solution.

It is important to minimize the thickness of the thermal interface material, commonly referred to as the bond line thickness. A large gap between the heatsink base and processor die yields a greater thermal resistance. The thickness of the gap is determined by the flatness of both the heatsink base and the die, plus the thickness of the thermal interface material, and the clamping force applied by the heatsink attachment method. To ensure proper and consistent thermal performance, the TIM and application process must be properly designed.

Another important aspect about Thermal Interface Materials is the degradation of the thermal impedance over the life of the material. It is critical to note that the impedance of the TIM increases over the life of the material; this must be taken into account when designing a thermal solution.

Note that the resistance of the thermal solution increases considerably at the End of Life due to the TIM degradation. End of Line for a TIM material is when the TIM is first installed on the heatsink. End of Life is defined as a time in the future at which the material is deemed to be at the end of its useful life. The End of Life time varies for TIM material. It is recommended that thermal solution designers work with TIM manufacturers to determine the performance of the thermal interface material and its expected End of Life time length. System integrators might wish to replace the TIM during regularly scheduled maintenance periods in order maintain End-of-Line performance of the thermal solution.

The heatsink solution was optimized using a high-performance phase-change material (PCM) Thermal Interface Material (TIM) with low thermal impedance. The heatsinks were designed using Honeywell\* PCM45F thermal phase-change material. Vendor information for this material is provided in "Vendor Information" on page 35. Alternative materials may be used at the user's discretion. The entire heatsink assembly, including the heatsink, attach method, and thermal interface material, must be validated together for specific applications.

February 2005 Thermal Design Guide

#### 2.2.8 Recommended Thermal Solution Attachment Method

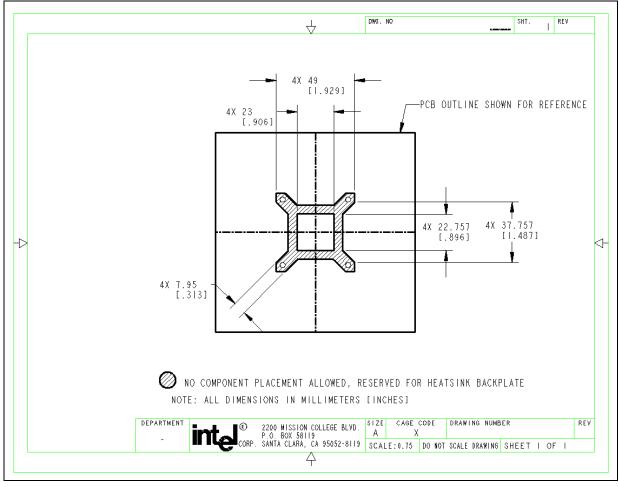

The reference thermal solution for the AdvancedTCA\* form factor is designed to attach to the processor and PCB with the use of a backplate. The heatsink is attached to the backplate with the use of a retaining cup, springs, and screws. The PCB keepout zone for the backplate can be seen in Figure 18, "Heatsink Volumetric Constraint Zone (Secondary Side)" on page 38 (in the appendix).

The entire heatsink assembly must be validated together for specific applications, including the heatsink, attach method, and thermal interface material.

## 2.2.9 Intel<sup>®</sup> Pentium<sup>®</sup> M Processor Thermal Test Vehicle

The Intel<sup>®</sup> Pentium<sup>®</sup> M Thermal Test Vehicle (TTV) must be used to perform thermal verification testing of heatsinks. This is due to the fact that the amount of power can be controlled and measured, whereas on a real processor in a system it is very difficult to accurately measure processor power dissipation. System-level thermal testing must still be performed using an actual processor to assess the system-level thermal performance of the actual system in its intended operating environment. For more information contact your Intel field representative.

Thermal Design Guide February 2005

Order Number: 305993, Revision: 1.0 29

## 3.0 Third-Party Vendor-Enabled Active Heatsinks

## 3.1 Applications

CoolerMaster\* has developed a number of active fan heatsinks that can be used to provide cooling for the Intel<sup>®</sup> Pentium<sup>®</sup> M Processor for Embedded Applications. These heatsinks are a good fit for platforms requiring an active thermal solution (integrated fan heatsink) if z-height allows for 1U or greater of clearance. The following sections provide details on the different active fansinks.

#### 3.1.1 EEP-N41ES-02 and EEB-N41ES-02

The following active heatsink was developed to minimize footprint on the motherboard while still providing an effective means to dissipate heat from processors in the micro-FCPGA and micro-FCBGA packages. The part number for this heatsink has either a P for Micro-FCPGA package or a B for the Micro-FCBGA package. This is an aluminum heatsink that has approximate dimensions of  $50 \text{ mm} \times 50 \text{ mm} \times 35.5 \text{ mm}$ . This heatsink is too tall for 1U server applications but is a good fit for form factors that have the available height.

Figure 13. Active Aluminum Heatsink, EEP-N41ES-02 and EEB-N41ES-02

#### 3.1.1.1 Thermal Performance

Thermal performance for the heatsink was verified with the Pentium  $^{\circledR}$  M Thermal Test Vehicle (TTV). The heatsink is capable of cooling a Pentium  $^{\circledR}$  M and Celeron  $^{\circledR}$  M processor at 27.0 W with local ambient temperatures up to  $T_{LA}=54$  °C. The performance of the thermal solution is a verification test only to ensure that the heatsink is performing within expectations. This test does not imply any statistical significance; the system integrator must perform validation in the final intended system, including the heatsink, attach method, and thermal interface material.

Table 6. Aluminum Active Heatsink Thermal Performance

| Thermal Performance (°C/W) | Ψ <sub>JA</sub> = 1.67 °C/W |

|----------------------------|-----------------------------|

|----------------------------|-----------------------------|

February 2005 30 Order Number: 305993, Revision: 1.0

#### 3.1.1.2 Mechanical Retention and Volumetric Constraint Zones

The active heatsink is attached to the motherboard using a backplate that is fastened to the motherboard by four screws. This attach method uses spring-loaded fasteners to apply an even load on the processor die. The backplate, when assembled, is flush against the backside of the motherboard.

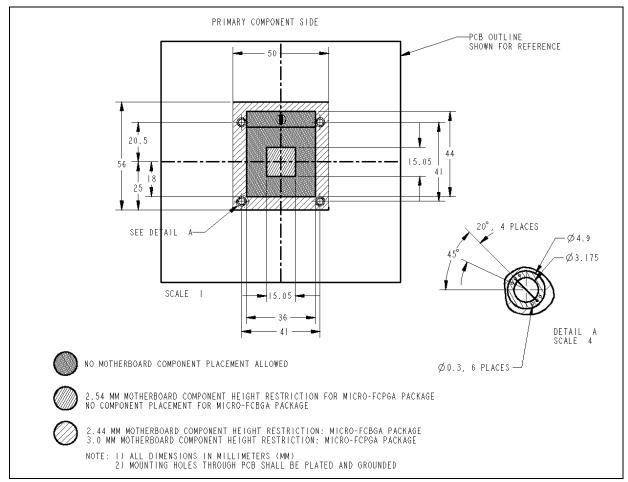

The volumetric constraint zone for this heatsink is shown in Figure 17 and Figure 18. Figure 17 (on page 37) shows the primary side volumetric constraint for processors in the micro-FCPGA and micro-FCBGA packages. This drawing is based on the standard mobile Intel<sup>®</sup> processor hole mounting pattern of 41 mm × 41 mm. Figure 18 (on page 38) shows the secondary side volumetric constraint zone for backplate assembly. It is important to adhere to both the primary and secondary side volumetric constraint zones to prevent interference with the assembly of the heatsink onto the motherboard.

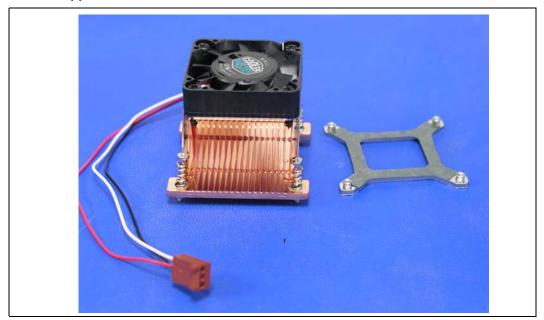

#### 3.1.2 EEP-N41CS-01 and EEB-N41CS-01

The following active heatsink was developed to minimize footprint on the motherboard while still providing an effective means to dissipate heat from processors in the micro-FCPGA and micro-FCBGA packages. The part number for this heatsink has either a P for Micro-FCPGA package or a B for the Micro-FCBGA package. This is a copper heatsink that has approximate dimensions of  $50~\text{mm} \times 50~\text{mm} \times 40.5~\text{mm}$ . This heatsink is too tall for 1U server applications but is a good fit for form factors that have the available height.

Figure 14. Active Copper Heatsink, EEP-N41CS-01 and EEB-N41CS-01

#### 3.1.2.1 **Thermal Performance**

Thermal performance for the heatsink was verified with the Pentium® M TTV. The heatsink is capable of cooling an Intel<sup>®</sup> Pentium<sup>®</sup> M processor at 27.0 W with local ambient temperatures up to  $T_{I,A} = 59$  °C. The performance of the thermal solution is a verification test only to ensure that the heatsink is performing within expectations. This test does not imply any statistical significance; the system integrator must perform validation in the final intended system, including the heatsink, attach method, and thermal interface material.

#### Table 7. **Active Copper Heatsink Thermal Performance**

| Thermal Performance (°C/W) | Ψ <sub>JA</sub> = 1.52 °C/W |

|----------------------------|-----------------------------|

|----------------------------|-----------------------------|

#### **Mechanical Retention and Volumetric Constraint Zones** 3.1.2.2

The active heatsink is attached to the motherboard using a backplate that is fastened to the motherboard by four screws. This attach method uses spring-loaded fasteners to apply an even load on the processor die. The backplate, when assembled, is flush against the backside of the motherboard.

The volumetric constraint zone for this heatsink is shown in Figure 17 and Figure 18. Figure 17 (on page 37) shows the primary side volumetric constraint zone, including processors in the micro-FCPGA and micro-FCBGA packages. This drawing is based on the standard mobile Intel® processor hole mounting pattern of 41 mm × 41 mm. Figure 18 (on page 38) shows the secondary side volumetric constraint zone for backplate assembly. It is important to adhere to both the primary and secondary side volumetric constraint zones so that there will be no interference with the assembly of the heatsink onto the motherboard.

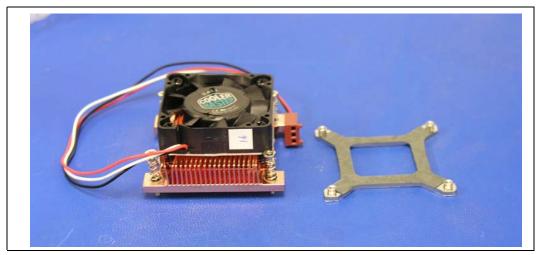

#### 3.1.3 **EEP-N41SS-01 and EEB-N41SS-01**

The following active heatsink was developed to minimize footprint on the motherboard while still providing an effective means to dissipate heat from processors in the micro-FCPGA and micro-FCBGA packages. The part number for this heatsink has either a P for micro-FCPGA package or a B for the micro-FCBGA package. This is a copper heatsink that has approximate dimensions of 50 mm × 50 mm × 23 mm. This heatsink is ideal for 1U or larger form factors that require the use of an active fansink.

February 2005 Order Number: 305993, Revision: 1.0 32

#### 3.1.3.1 Thermal Performance

Thermal performance for the heatsink was verified with the Pentium  $^{\circledR}$  M TTV. The heatsink is capable of cooling an Intel  $^{\circledR}$  Pentium  $^{\circledR}$  M processor at 27.0 W with local ambient temperatures up to  $T_{LA} = 49$  °C. The performance of the thermal solution is a verification test only to ensure that the heatsink is performing within expectations. This test does not imply any statistical significance; the system integrator must perform validation in the final intended system, including the heatsink, attach method, and thermal interface material.

#### Table 8. Copper Active Heatsink Thermal Performance

| Thermal Performance (°C/W) | Ψ <sub>JA</sub> = 1.89 °C/W |

|----------------------------|-----------------------------|

#### 3.1.3.2 Mechanical Retention and Volumetric Constraint Zones

The active heatsink is attached to the motherboard using a backplate that is fastened to the motherboard by four screws. This attach method uses spring-loaded fasteners to apply an even load on the processor die. The backplate, when assembled, is flush against the backside of the motherboard.

The volumetric constraint zone for this heatsink is shown in Figure 17 and Figure 18. Figure 17 (on page 37) shows the primary side volumetric constraint zone, including processors in the micro-FCPGA and micro-FCBGA packages. This drawing is based on the standard mobile Intel<sup>®</sup> processor hole mounting pattern of 41 mm × 41 mm. Figure 18 (on page 38) shows the secondary side volumetric constraint zone for backplate assembly. It is important to adhere to both the primary and secondary side volumetric constraint zones to prevent interference with the assembly of the heatsink onto the motherboard.

#### 3.2 **Thermal Interface Material and Considerations**

The CoolerMaster\* active heatsinks are delivered with preapplied thermal interface material. This material, Powerstrate\* 51, manufactured by Power Devices\*, Inc., is a phase-change thermal interface material. This implies that the material changes properties at elevated temperatures to increase thermal performance. You must account for this phase change when testing the CoolerMaster\* active heatsink. At low temperatures, the heatsink performance is significantly degraded, but at elevated junction temperatures, the material changes phase and improves in performance. For more information, see the Power Devices website at http://www.powerdevices.com.

# 4.0 Vendor Information

Table 9. Vendor Contact Information

| Supplier                                                                          | Contact     | Phone                | Email                       | Components                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------|-------------|----------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cooler Master<br>4124 Clipper Ct<br>Fremont, CA 94538<br>USA                      | Wendy Lin   | (510) 770-8566, x211 | wendy@coolermaster.com      | AdvancedTCA* Reference Thermal Solution (not currently available) Active Heatsink, Part Number, Micro-FCPGA Package: EEP-N41ES-02, EEP-N41CS-01, EEP-N41SS-01 Active Heatsink, Part Number, Micro-FCBGA Package: EEB-N41ES-02, EEB-N41CS-01, EEB-N41SS-01 |

| Honeywell                                                                         | Paula Knoll | (858) 279-2956       | paula_knoll@honeywell.com   | Thermal Interface Material, P/N PCM45F                                                                                                                                                                                                                    |

| Power Devices Inc.<br>26941 Cabot Rd., Bldg. 124<br>Laguna Hills, CA 92653<br>USA |             | (949) 582-6712       | http://www.powerdevices.com | Thermal Interface Material (Powerstrate* 51)                                                                                                                                                                                                              |

# **Appendix A Heatsink Mechanical Drawings**

Intel® Pentium® M Processor Reference Heatsink for ATCA Form Factor Figure 16.

Figure 17. Active Heatsink Volumetric Constraint Zone (Primary Side)

Figure 19. Recommended PCB Volumetric Constraint Zone for the Intel<sup>®</sup> Pentium<sup>®</sup> M Processor in the AdvancedTCA\* Form Factor