# Intel® EP80579 Integrated Processor with Intel® QuickAssist Technology Development Kit

**User's Guide**

October 2008

Order Number: 320067-002US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting Intel's Web Site.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, 1960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel VPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright  $\ @$  2008, Intel Corporation. All rights reserved.

# **Contents**

| 1.0 | Intro | duction                                            | 8    |

|-----|-------|----------------------------------------------------|------|

|     | 1.1   | Document Organization                              | 8    |

|     | 1.2   | Related Documents                                  | 8    |

|     | 1.3   | Acronyms                                           | 9    |

| 2.0 | Prod  | uct Specification                                  | . 11 |

|     | 2.1   | Overview                                           |      |

|     |       | 2.1.1 Product Description and Board Architecture   |      |

|     |       | 2.1.2 Feature List                                 |      |

|     | 2.2   | Package Components                                 |      |

|     | 2.3   | System I/O                                         | . 14 |

|     |       | 2.3.1 Intel® EP80579 Development Board I/O         | . 14 |

|     |       | 2.3.2 Super I/O (SIO)                              |      |

|     |       | 2.3.3 PEX 8508 PCI Express* Switch                 |      |

|     |       | 2.3.4 Marvell* 88E1141 Quad Ethernet Transceiver   |      |

|     | 2.4   | System Memory                                      |      |

|     |       | 2.4.1 Supported DIMM Slot Populations              |      |

|     | 2.5   | Supported Operating Systems                        |      |

|     | 2.6   | Supported Pre-boot Firmware Features               |      |

|     | 2.7   | Intel® EP80579 Development Board Overview          |      |

|     | 2.8   | Mezzanine Cards                                    |      |

|     | 2.9   | Power Supply                                       |      |

|     | 2.10  | Ordering Information                               |      |

| 3.0 | Syste | em Overview                                        |      |

|     | 3.1   | Power Distribution                                 |      |

|     | 3.2   | Platform Clocking                                  |      |

|     | 3.3   | Platform Reset                                     |      |

|     | 3.4   | SMBus                                              | . 24 |

| 4.0 | Tech  | nical Reference                                    | . 25 |

|     | 4.1   | Board Components Layout                            |      |

|     | 4.2   | IA-32 Core Frequency Selection                     |      |

|     | 4.3   | SMBus Address                                      |      |

|     | 4.4   | System LEDs                                        |      |

|     | 4.5   | Fixed I/O Map and Interrupts                       |      |

|     | 4.6   | Jumper Block                                       |      |

|     | 4.7   | Header Blocks                                      |      |

|     | 4.8   | Connector/Header Pinout Information                |      |

|     |       | 4.8.1 ITP-XDP Connector Pinout                     |      |

|     |       |                                                    |      |

|     |       | 4.8.3 LEB CompactFlash* Connector Pinout           |      |

|     |       | 4.8.5 CAN Header Pinout                            |      |

|     |       | 4.8.6 IEEE 1588-2008 Hardware-Assist Header Pinout |      |

|     |       | 4.8.7 Front Panel Header                           |      |

|     |       | 4.8.8 SMBus Header                                 |      |

|     |       | 4.8.9 SSP Header                                   |      |

|     |       | 4.8.10 SIO Tertiary (Third) UART Header            |      |

|     |       | 4.8.11 JTAG Access Headers                         |      |

|     |       | 4.8.12 GPIO Header                                 |      |

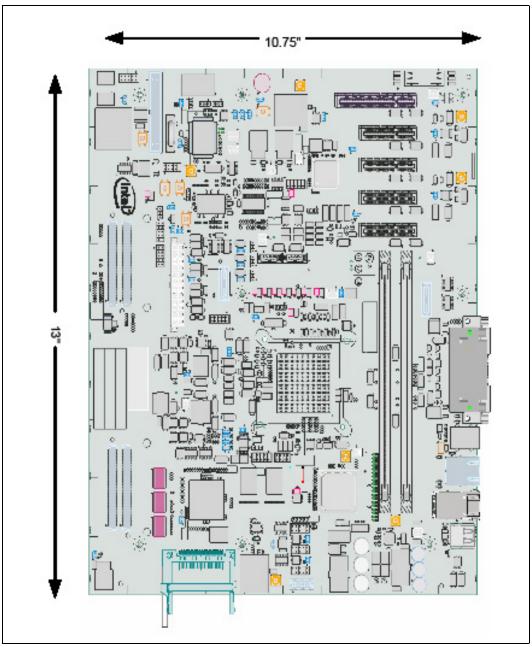

|     | 4.9   | Mechanical Considerations                          | . 45 |

|     |       | 4.9.1 Form Factor                                  | 45   |

|     | 4.10  | Electrical Considerations                                                                              |    |

|-----|-------|--------------------------------------------------------------------------------------------------------|----|

|     |       | 4.10.1 DC Loading                                                                                      |    |

|     |       | 4.10.2 PCI Express Add-in Connector Considerations                                                     | 47 |

|     |       | 4.10.3 Fan Connector Current Capability                                                                |    |

|     | 4.11  | Thermal Considerations                                                                                 | 48 |

| 5.0 | Pre-k | poot Firmware                                                                                          | 49 |

| 0.0 | 5.1   | Introduction                                                                                           |    |

|     | 5.2   | Pre-boot Firmware Boot Flow                                                                            |    |

|     | 5.3   | Pre-boot Firmware Features                                                                             |    |

|     | 0.0   | 5.3.1 Pre-boot Firmware Setup Menu                                                                     |    |

|     | 5.4   | Serial Console Redirection                                                                             |    |

|     |       | 5.4.1 Default Settings                                                                                 |    |

|     | 5.5   | PXE Boot Support                                                                                       | 51 |

|     | 5.6   | System Management BIOS (SMBIOS)                                                                        | 51 |

|     | 5.7   | Legacy USB Support                                                                                     | 51 |

|     | 5.8   | Pre-boot Firmware Recovery and Updates                                                                 | 51 |

|     |       | 5.8.1 Updating Pre-boot Firmware                                                                       | 52 |

|     |       | 5.8.2 AMI's Aptio* Flash Update Utility (AFUEFI)                                                       |    |

|     | 5.9   | Boot Options                                                                                           |    |

|     |       | 5.9.1 Changing the Boot Device                                                                         |    |

|     |       | 5.9.2 Booting without Attached Devices                                                                 |    |

|     | 5.10  | Security Features                                                                                      |    |

|     | 5.11  | Clearing CMOS                                                                                          | 54 |

| 6.0 | Platf | orm Setup                                                                                              | 56 |

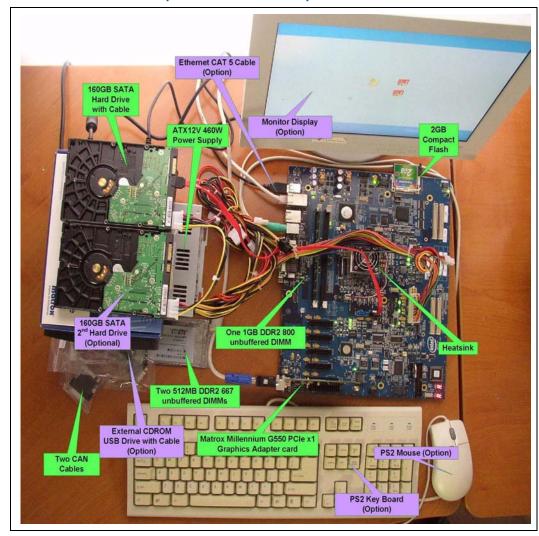

|     | 6.1   | Setting up the Platform                                                                                | 56 |

|     |       | 6.1.1 Safety                                                                                           |    |

|     |       | 6.1.2 Connecting the SATA Cables                                                                       | 58 |

|     |       | 6.1.3 Installing Memory                                                                                | 59 |

|     |       | 6.1.4 Connecting the Processor Heatsink and Fan                                                        |    |

|     |       | 6.1.5 Installing the PCI Express Video Card                                                            |    |

|     |       | 6.1.6 Connecting the Keyboard and Mouse                                                                |    |

|     |       | 6.1.7 Connecting the Serial Cable for Console Redirection                                              |    |

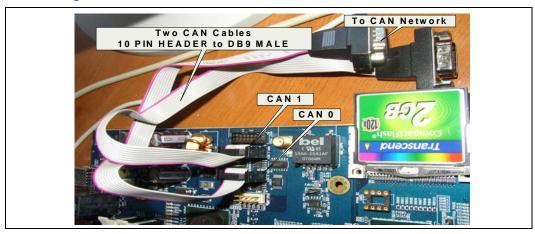

|     |       | 6.1.8 Connecting the CAN Interface Cables (optional)                                                   |    |

|     |       | 6.1.9 Connecting the DVD-ROM Drive and GbE Ethernet Port                                               |    |

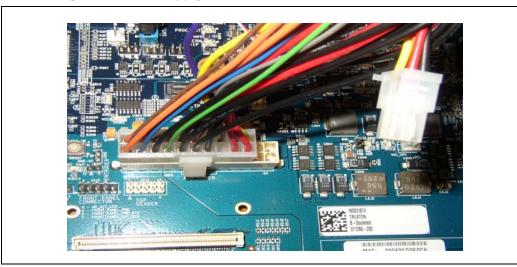

|     |       | 6.1.10 Connecting the Power Cables                                                                     |    |

|     |       | 6.1.11 Stand-alone Target Platform                                                                     |    |

|     |       | 6.1.12 Powering Up the System                                                                          |    |

|     |       | 6.1.13 Connecting Mezzanine Cards (optional)                                                           |    |

| 7.0 | Error | Messages and Beep Codes                                                                                |    |

|     | 7.1   | Pre-boot Firmware Beep Codes                                                                           |    |

|     | 7.2   | Pre-boot Firmware Error Messages                                                                       |    |

|     | 7.3   | Debugging the EFI                                                                                      | 68 |

| 8.0 | Sock  | eted Intel $^{	exttt{@}}$ EP80579 Integrated Processor with Intel $^{	exttt{@}}$ QuickAssist Technolog | VĽ |

|     | Extra | action and Insertion Instructions                                                                      | 69 |

|     | 8.1   | Tools and Preparation                                                                                  | 69 |

|     | 8.2   | Extraction Instructions — Intel® EP80579 Development Board with Advanced                               |    |

|     |       | Interconnects Interposer                                                                               | 73 |

|     | 8.3   | Insertion Instructions — Intel® EP80579 Development Board with Advanced                                | =  |

|     |       | Interconnects Interposer                                                                               | 78 |

| Fig | ur  | res                                                                       |    |

|-----|-----|---------------------------------------------------------------------------|----|

| 1   |     | Block Diagram of the Intel® EP80579 Development Board                     | 12 |

| 2   |     | Intel® EP80579 Development Board                                          | 18 |

| 3   |     | Mezzanine Cards                                                           |    |

| 4   |     | Power Distribution Block Diagram                                          |    |

| 5   |     | Clock Block Diagram                                                       |    |

| 6   | )   | Reset Diagram                                                             |    |

| 7   | ,   | SMBus System Block Diagram                                                |    |

| 8   | 3   | Front View of the Board Components                                        |    |

| 9   | )   | Back View of the Board Components                                         |    |

| 1   | 0   | Side View of the Board Connectors                                         |    |

| 1   | 1   | Layout of LEDs                                                            |    |

| 1   | 2   | Jumper Block Locations                                                    |    |

|     | 3   | SPI and FWH Boot Option Jumpers                                           |    |

|     | 4   | Header Locations                                                          |    |

|     | 5   | Form Factor of Intel® EP80579 Development Board                           | 46 |

| 1   | 6   | CMOS Location                                                             |    |

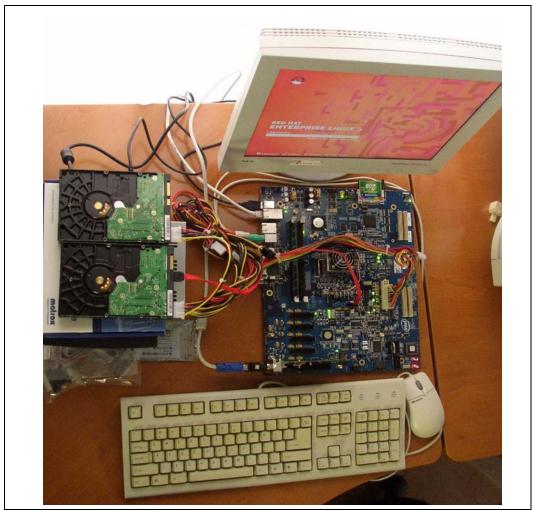

|     | 7   | Intel® EP80579 Development Kit Basic Setup                                | 57 |

|     | 8   | Connecting SATA Port 0                                                    |    |

|     | 9   | Close-up of Connection SATA Port 0                                        |    |

|     | 20  | Memory Installation - 1 GB DDR-800 DIMM in DIMM 0 Socket                  |    |

|     | 21  | Proper Installation of Heatsink                                           |    |

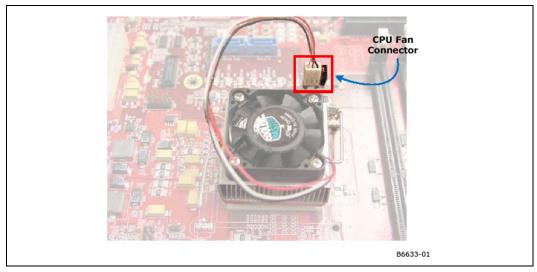

|     | 22  | Location of CPU FAN Connector                                             |    |

| 2   | 23  | Graphics Adapter Installation - PICe Slot 0                               |    |

|     | 24  | Connecting the PS/2 Keyboard and PS/2 Mouse                               |    |

| 2   | 25  | Connecting the CAN Interface Cables                                       |    |

|     | 26  | Connecting Ethernet Cable Port 0                                          |    |

| 2   | 27  | Connecting ATX Power Supply Cable                                         |    |

| 2   | 28  | Intel® EP80579 Stand-alone Target Platform                                |    |

| 2   | 9   | Connecting the Mezzanine Cards (optional)                                 |    |

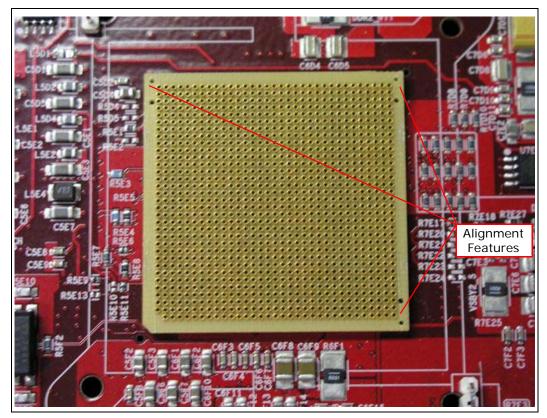

| 3   | 80  | EP80579 Processor Location                                                |    |

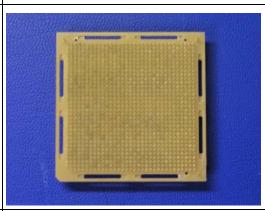

| 3   | 31  | Advanced Interconnections 1088 POS PGA-to-BGA Socket                      |    |

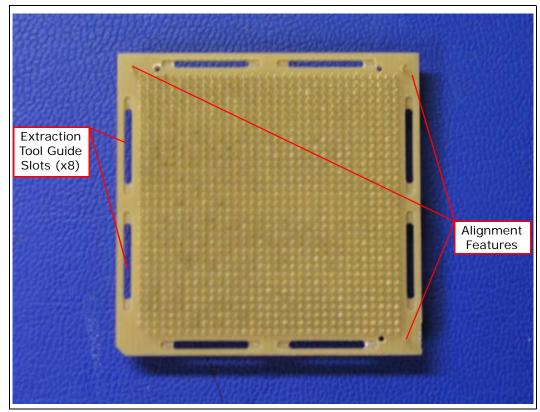

| 3   | 32  | Advanced Interconnections 1088 BGA-to-PGA Interposer (pin side facing up) |    |

|     |     | 3 · [·                                                                    |    |

| Tal | ماہ |                                                                           |    |

| Га  |     |                                                                           | _  |

| 1   |     | Related Documents                                                         |    |

| 2   |     | Acronym Table                                                             |    |

| 3   |     | Feature List                                                              |    |

| 4   |     | DDR2 Memory Configuration                                                 |    |

| 5   |     | Supported DIMM Slot Populations                                           |    |

| 6   |     | Pre-boot Firmware Features                                                |    |

| 7   |     | Intel® EP80579 Development Kit Revision Identification and Color Scheme   |    |

| 8   |     | Ordering Information                                                      |    |

| 9   |     | Component and Connector Layout Description                                |    |

|     | 0   | Intel® EP80579 IA-32 core Frequency Selection                             |    |

|     | 1   | SMBus Connectivity                                                        |    |

|     | 2   | Signal and Voltage LED Indicators                                         |    |

|     | 3   | Jumper Block Descriptions                                                 |    |

|     | 4   | Header Block Descriptions                                                 |    |

|     | 5   | ITP-XDP Connector                                                         |    |

| 1   | 6   | Main ATX Power Supply Connector                                           | 3/ |

# Intel<sup>®</sup> EP80579 Integrated Processor with Intel<sup>®</sup> QuickAssist Technology— Contents

October 2008 Order Number: 320067-002US

| 20 | Expansion Mezzanine Connector                         | 40 |

|----|-------------------------------------------------------|----|

| 21 | CAN Header Pinout                                     | 42 |

| 22 | IEEE 1588-2008 Hardware-Assist Signal Header Pinout   | 42 |

| 23 | Front Panel Header Pinout                             | 42 |

| 24 | SMBus Header Pinout                                   | 43 |

| 25 | SSP Header Pinout                                     | 43 |

| 26 | Tertiary UART Pinout                                  | 44 |

|    | Intel® EP80579, PEX8508 and 88E1141JTAG Header Pinout |    |

| 28 | FPGA JTAG Header Pinout                               |    |

| 29 | GPIO Header Pinout                                    | 45 |

| 30 | DC Loading Characteristics Mode                       | 47 |

| 31 | Fan Connector Current Capability                      | 48 |

|    | Pre-boot Firmware Setup Main Menu                     |    |

|    | Pre-boot Firmware Setup Program Function Keys         |    |

| 34 |                                                       |    |

| 35 |                                                       |    |

| 36 | Pre-boot Firmware Error Messages                      | 68 |

# **Revision History**

| Date                                                                                      | Revision | Description                                                              |

|-------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------|

| August 2008 001 Initial release                                                           |          |                                                                          |

| October 2008 002 Updated Section 6.1.13 and included new graphics in Sections 2, 3, 5, 6. |          | Updated Section 6.1.13 and included new graphics in Sections 2, 3, 5, 6. |

# 1.0 Introduction

This document provides user guide information for the Intel<sup>®</sup> EP80579 Integrated Processor with Intel<sup>®</sup> QuickAssist Technology Development Kit. The document contains a high-level description of the Intel<sup>®</sup> EP80579 Integrated Processor with Intel<sup>®</sup> QuickAssist Technology Development Kit, technical reference, configuration and setup information. The document also includes Pre-boot Firmware usage and recovery information.

Note:

The "Intel® EP80579 Integrated Processor with Intel® QuickAssist Technology Development Board" is referred to as "Intel® EP80579 Development Board" throughout this document.

The "Intel® EP80579 Integrated Processor with Intel® QuickAssist Technology Development Kit" is referred to as "Intel® EP80579 Development Kit" throughout this document.

# 1.1 Document Organization

The following chapters are included in this document:

- Chapter 1.0, "Introduction" gives an overview of the information contained in this document, as well as a list of acronyms.

- Chapter 2.0, "Product Specification" introduces key features of the Intel® EP80579 Development Board.

- Chapter 3.0, "System Overview" provides a system overview of the Intel<sup>®</sup> EP80579 Development Board.

- Chapter 4.0, "Technical Reference" includes an illustration of LEDs, connector locations, connector/header descriptions, and pinout tables.

- Chapter 5.0, "Pre-boot Firmware" provides an introduction to AMI Aptio\* 4.5 Pre-boot Firmware on the Intel<sup>®</sup> EP80579 Development Board.

- Chapter 6.0, "Platform Setup" provides specifics for configuring the Intel<sup>®</sup> EP80579 Development Board.

- Chapter 7.0, "Error Messages and Beep Codes" lists Port 80h POST codes, system

initialization checkpoints and provides a brief description of each.

- Chapter 8.0, "Socketed Intel<sup>®</sup> EP80579 Integrated Processor with Intel<sup>®</sup>

QuickAssist Technology Extraction and Insertion Instructions" provides instructions

how to extract and insert the Intel<sup>®</sup> EP80579 Integrated Processor from the Intel<sup>®</sup>

EP80579 Development Board.

October 2008 Order Number: 320067-002US

8

#### 1.2 **Related Documents**

Table 1 lists the hardware, software and platform documents that will assist in the development process:

#### Table 1. **Related Documents**

| Document Title                                                         | Document Number |

|------------------------------------------------------------------------|-----------------|

| Intel® EP80579 Integrated Processor Product Line Datasheet             | 320066-001      |

| Intel® EP80579 Integrated Processor Product Line Platform Design Guide | 320068-001      |

## **Acronyms** 1.3

Table 2 describes acronyms that are used throughout this document.

#### Table 2. Acronym Table (Sheet 1 of 2)

| Acronym | Description                                                                                                                                                              |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACPI    | Advanced Configuration and Power Interface specification                                                                                                                 |

| APIC    | Advanced Programmable Interrupt Controller                                                                                                                               |

| ASU     | Acceleration Services Unit                                                                                                                                               |

| BIOS    | Basic Input/Output System                                                                                                                                                |

| CAN     | Controller Area Network specification                                                                                                                                    |

| DDR2    | Double Data Rate 2                                                                                                                                                       |

| DEC     | Double-bit Error Detection                                                                                                                                               |

| DIMM    | Dual In-line Memory Module                                                                                                                                               |

| ECC     | Error Checking and Correction                                                                                                                                            |

| EFI     | Extensible Firmware Interface specification                                                                                                                              |

| EHCI    | The Enhanced Host Controller Interface (EHCI) specification describes the register-level interface for a Host Controller for the Universal Serial Bus (USB) Revision 2.0 |

| FPGA    | Field-Programmable Gate Array                                                                                                                                            |

| FSB     | Front Side Bus                                                                                                                                                           |

| FXO     | Foreign Exchange Office                                                                                                                                                  |

| FXS     | Foreign Exchange Subscriber                                                                                                                                              |

| FWH     | Firmware Hub                                                                                                                                                             |

| GbE     | Gigabit Ethernet                                                                                                                                                         |

| HSS     | High Speed Serial Bus                                                                                                                                                    |

| IA      | Intel Architecture                                                                                                                                                       |

| LEB     | Local Expansion Bus                                                                                                                                                      |

| MAC     | Media Access Controller                                                                                                                                                  |

| PCIe    | PCI Express*                                                                                                                                                             |

| PHY     | Physical Layer Device                                                                                                                                                    |

| POST    | Power-On Self-Test                                                                                                                                                       |

| PXE     | Pre-Boot Execution Environment                                                                                                                                           |

| SATA    | Serial ATA                                                                                                                                                               |

| SEC     | Single-bit Error Correction                                                                                                                                              |

Development Kit User's Guide Order Number: 320067-002US

October 2008

# Table 2. Acronym Table (Sheet 2 of 2)

| Acronym | Description                                 |  |

|---------|---------------------------------------------|--|

| SIO     | Super IO Controller                         |  |

| SMBIOS  | System Management BIOS specification        |  |

| SPI     | Serial Peripheral Interface Bus             |  |

| SOC     | System on Chip                              |  |

| UART    | Universal Asynchronous Receiver/Transmitter |  |

| UHCI    | Universal Host Controller Interface         |  |

| USB     | Universal Serial Bus                        |  |

§ §

# 2.0 Product Specification

## 2.1 Overview

This chapter contains an overview of the Intel  $^{\circledR}$  EP80579 Development Kit product specifications. See the *Intel ^{\circledR} EP80579 Integrated Processor Product Line Platform Design Guide* for implementation details.

# 2.1.1 Product Description and Board Architecture

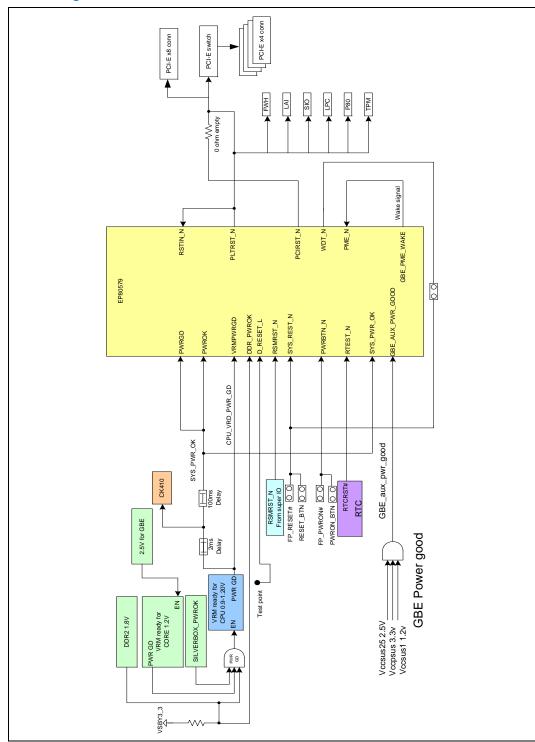

Figure 1 shows the functional blocks of the Intel<sup>®</sup> EP80579 Development Board.

Mezz 2 Mezz 1 DIMM 0 Primary Mezz 0 IEEE 1 DIMM 1 GPIO DDR2 SSP HSS1 HSS2 LEB IEEE 1588 I2C/ SMB SPI 32.786 KHz EP80579 SATA(0,1) USB(0,1) UART(0,1) MDIO Gb EE GbE1 CAN PCle 臣 Marvell 88E1141 Quad GbE RGMII PHY Mid Bus LAI 9 pin D-sub Stacked Type A RJ45 w/mag/led PEX 8508 PCI-E switch 4 Port Switch Slot 1

X4 Conn 1 Lane

Slot 2

X4 Conn 1 Lane Slot 3

X4 Conn 1 Lane

Slot 4

X4 Conn 1 Lane

Block Diagram of the Intel<sup>®</sup> EP80579 Development Board Figure 1.

October 2008 Order Number: 320067-002US

## 2.1.2 Feature List

Table 3 summarizes the major features of the Intel® EP80579 Development Board.

## Table 3. Feature List

| Feature                                  | Description                                                                                                                                                                                                                                                                                                                                  | Comments                                                                                                                                                                                               |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Form Factor                              | 13.00 inches x 10.75 inches                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                        |

| SOC (processor and chipset)              | Intel <sup>®</sup> EP80579 Integrated Processor with Intel <sup>®</sup> QuickAssist Technology                                                                                                                                                                                                                                               | Integrated IA SOC                                                                                                                                                                                      |

| Video                                    | External PCIe card                                                                                                                                                                                                                                                                                                                           | Matrox Millennium G550 PCIe                                                                                                                                                                            |

| System Memory                            | Support for two 240-pin DDR2 DIMMs Support for 400\533\667\800 MHz DDR2 Support for 256 MB to 4 GB memory Support for ECC and non-ECC Support for both registered and unbuffered DIMMs                                                                                                                                                       | For DDR2-800 MHz, only single<br>rank or dual rank DIMM on<br>DIMM 0 slot is supported                                                                                                                 |

| Pre-boot Firmware                        | EFI v1.1 compliant based on AMI Aptio* 4.5                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                        |

| Peripheral/IO<br>Interfaces              | <ul> <li>Three UART ports</li> <li>Three Gigabit Ethernet (GbE) with RJ45 ports</li> <li>Two Controller Area Network (CAN) buses with 2x5 headers</li> <li>Two USB ports</li> <li>Two SATA ports</li> <li>One floppy drive interface</li> <li>PS/2 mouse and keyboard</li> <li>One parallel port</li> <li>CompactFlash* connector</li> </ul> | Two USB ports support UHCI or EHCI configurations Two serial ports supported from SOC connected to 9-pin D-sub and the 3rd serial port from SIO connected to 2x5 header Two SATA ports support Gen 2.0 |

| Expansion Capabilities                   | One PCI Express x4 interface in x8 slot     Four PCI Express x1 interfaces in x4 slots     Three HSS/SSP/LEB mezzanine slots                                                                                                                                                                                                                 | Mezzanine slots provide support for acceleration services SKU applications                                                                                                                             |

| Firmware Hub and SPI<br>Flash            | Socketed 2 MB FWH     Socketed 2 MB SPI Flash                                                                                                                                                                                                                                                                                                | Selectable Boot Options between FWH and SPI Flash.                                                                                                                                                     |

| Hardware Control or<br>Monitor Subsystem | Voltage sensor to detect out of range voltage values Thermal sensor to detect out of range thermal values One processor and three AUX fan connectors Fan speed control                                                                                                                                                                       |                                                                                                                                                                                                        |

# 2.2 Package Components

The complete package for the Intel $^{\mathbb{B}}$  EP80579 Integrated Processor with Intel $^{\mathbb{B}}$  QuickAssist Technology Development Kit includes the following:

- Intel<sup>®</sup> EP80579 Integrated Processor:

- One Intel $^{\rm @}$  EP80579 Integrated Processor with Intel $^{\rm @}$  QuickAssist Technology at 1200 MHz (installed with heatsink and fan)

- One Intel<sup>®</sup> EP80579 Integrated Processor with Intel<sup>®</sup> QuickAssist Technology at 600 MHz (supplied)

- · Hardware:

- Memory SDRAM: One 1 GB DDR2 800 MHz

- Video Card: One PCI Express\* x1 Graphics Adapter card

- Hard drive: SATA hard drive

- DVD-ROM drive: SATA DVD-ROM drive

- · Cable:

- 10-pin header to DB9 Serial cable: CAN interface adapter cables (also used for SIO Tertiary UART)

- Serial ATA cables

- Power cord

- Power Supply:

- One standard ATX12V power supply

### 2.3 System I/O

## Intel® EP80579 Development Board I/O 2.3.1

The Intel® EP80579 Integrated Processor provides the following I/O capabilities on the Intel® EP80579 Development Board:

- · Two DDR2 DIMM sockets

- · Two UART ports

- · Two SATA ports

- Two USB ports

- · Two CAN interfaces

- · Three HSS/SSP/LEB mezzanine slots

- One x4 PCI Express\* interface in x8 slot

- Four x1 PCI Express interfaces in x4 slots through PEX 8508 PCIe switch

- · Three GbE RJ45 ports

Note: The mezzanine slots support add-in cards. See Section 2.10 for order information for supported add-in cards.

#### 2.3.2 Super I/O (SIO)

The Intel® EP80579 Development Board utilizes SIO to provide the following I/O capabilities:

- · PS/2 mouse and keyboard port

- · One parallel port

- · One floppy drive interface

- · One UART port

#### PEX 8508 PCI Express\* Switch 2.3.3

The Intel® EP80579 Integrated Processor provides a x8 PCI Express interface that is configured as two independent x4 PCI Express interfaces. One of the x4 PCI Express interfaces is connected to a PEX 8508 PCI Express switch to provide support for four x1 PCI Express interfaces in x4 slots.

October 2008 Development Kit User's Guide Order Number: 320067-002US

#### 2.3.4 Marvell\* 88E1141 Quad Ethernet Transceiver

The Quad Ethernet transceiver is a Gigabit Ethernet physical layer device (PHY). The three GbE MAC controllers from the Intel<sup>®</sup> EP80579 Integrated Processor are connected to a 88E1141 Quad Ethernet Transceiver to provide three GbE RJ45 ports over copper.

The Intel® EP80579 Development Board does not support Wake On LAN (WOL), but the Note: Intel® EP80579 Integrated Processor does support WOL.

#### **System Memory** 2.4

The Intel® EP80579 Development Board has two DIMM sockets and supports the following memory features:

- DDR2-400, DDR2-533, DDR2-667, DDR2-800 registered/unbuffered DIMM

- Two single-rank or one dual-rank DIMM(s) (for DDR2-800 MHz, only one singlerank or dual-rank DIMM on DIMM 0 slot is supported)

- · ECC or Non-ECC (with ECC enabled, SEC/DED are supported)

- Total system memory: Minimum 256 MB and maximum 4 GB

- 256 Mbit, 512 Mbit, 1 Gbit, and 2 Gbit density parts in the x8 configuration

Table 4 shows the memory configurations that are supported by the Intel® EP80579 Development Board.

#### Table 4. **DDR2 Memory Configuration**

| DDR2 <sup>1</sup><br>Frequency                                  | DIMM 1     | DIMM 0     |

|-----------------------------------------------------------------|------------|------------|

| 400                                                             | Registered | Registered |

| 400                                                             | Empty      | Registered |

| 400                                                             | Unbuffered | Unbuffered |

| 400                                                             | Empty      | Unbuffered |

| 533                                                             | Registered | Registered |

| 533                                                             | Empty      | Registered |

| 533                                                             | Unbuffered | Unbuffered |

| 533                                                             | Empty      | Unbuffered |

| 667                                                             | Registered | Registered |

| 667                                                             | Empty      | Registered |

| 667                                                             | Unbuffered | Unbuffered |

| 667                                                             | Empty      | Unbuffered |

| 800                                                             | Empty      | Registered |

| 800                                                             | Empty      | Unbuffered |

| 1. Actual supported frequencies are determined by the SKU used. |            |            |

Note: Certain restrictions apply when two ranks are used. Both ranks need to be either:

- · Registered or unbuffered. Mixing of registered and unbuffered ranks is not supported.

- 64-bit mode only. 32-bit mode does not supported dual rank.

# 2.4.1 Supported DIMM Slot Populations

Table 5 shows the supported DDR2 DIMM populations.

## Table 5. Supported DIMM Slot Populations

| DIMM Configuration | DIMM1     | DIMMO     |

|--------------------|-----------|-----------|

| 1 Single Rank      | Empty     | Populated |

| 2 Single Rank      | Populated | Populated |

| 1 Dual Rank        | Empty     | Populated |

# 2.5 Supported Operating Systems

The Intel® EP80579 Development Kit is validated with the following operating systems:

- Red Hat Enterprise Linux\* 5

- FreeBSD\* 6.2

- Microsoft Windows\* XP Embedded\* SP2

Note: Operating systems are not distributed with the Intel® EP80579 Development Board, kit, or processor.

# 2.6 Supported Pre-boot Firmware Features

The Intel $^{\circledR}$  EP80579 Integrated Processor Pre-boot Firmware is based on the AMI Aptio $^*$  4.5 core and is compliant with the EFI v1.1 specification.

Table 6 provides an overview of the Pre-boot Firmware features.

## Table 6. Pre-boot Firmware Features (Sheet 1 of 2)

| Feature               | Description                                                                                                                                                                                                          |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Boot devices          | Supports booting from:  SATA hard drive  SATA DVD-ROM drive  USB drive  Floppy drive  LAN card in PCIe slot  PXE boot from internal GbE ports                                                                        |  |

| PCI Express           | Initializes and supports PCI Express cards that are plugged into the Intel® EP80579 Integrated Processor Product Line                                                                                                |  |

| USB                   | Supports USB 1.1 and USB 2.0 interfaces                                                                                                                                                                              |  |

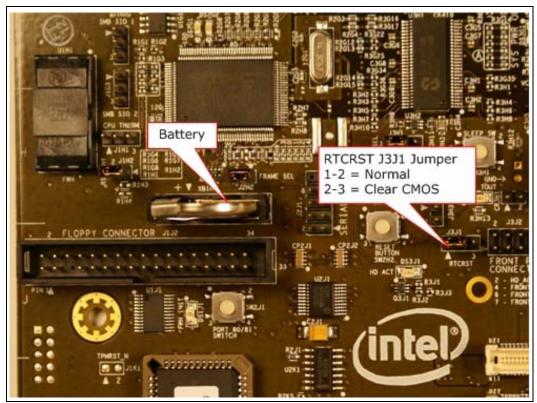

| CMOS header           | Detects clearing CMOS with clear CMOS header                                                                                                                                                                         |  |

| Watchdog timer        | Supports two-stage Watchdog timer                                                                                                                                                                                    |  |

| APIC and ACPI control | Provides ability to enable and disable APIC and ACPI support.  Supported ACPI states:  G0(S0) - Working  G1(S3) - Sleeping [Suspend to RAM]  S4 - Suspend to disk  G2(S5) - Soft Off  Supports C0, C1, and C2 states |  |

# Table 6. Pre-boot Firmware Features (Sheet 2 of 2)

| Feature                    | Description                                                                                                                                                                                                             |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Memory                     | Detects and supports ECC/Non-ECC memory                                                                                                                                                                                 |  |  |

| Functionality control      | Provides all possible options for enabling or disabling Intel® EP80579 Integrated Processor functionality:  Parallel Port  USB 0/1  SATA 0/1  SATA Gen2  CAN 0/1  SSP 0/1  PCI Express Controller Port A0/A1  GbE 0/1/2 |  |  |

| Serial console redirection | Provides console redirection through serial port                                                                                                                                                                        |  |  |

# 2.7 Intel<sup>®</sup> EP80579 Development Board Overview

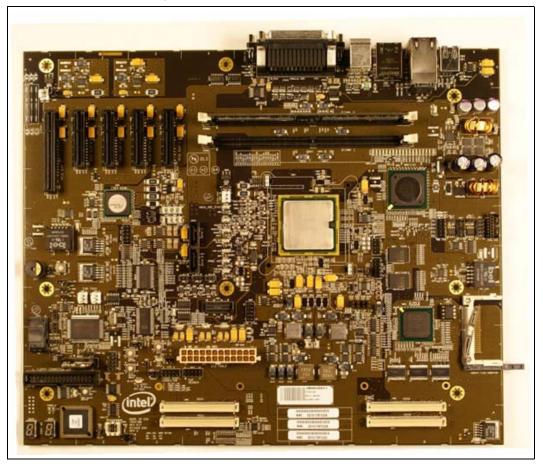

Table 7 and Figure 2 identify the Intel® EP80579 Development Board.

# Table 7. Intel® EP80579 Development Kit Revision Identification and Color Scheme

| Product                          | GPIO 1 | GPIO 0 | Board Solder<br>Mask Color |

|----------------------------------|--------|--------|----------------------------|

| Intel® EP80579 Development Board | 1      | 1      | Black                      |

Figure 2. Intel<sup>®</sup> EP80579 Development Board

# 2.8 Mezzanine Cards

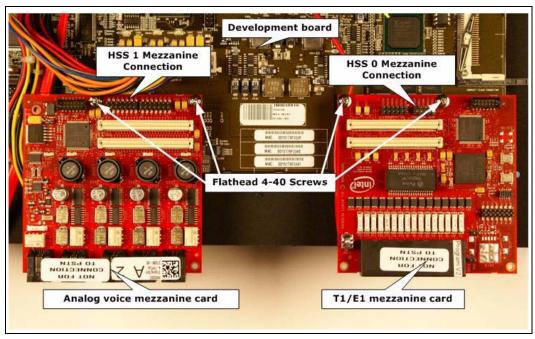

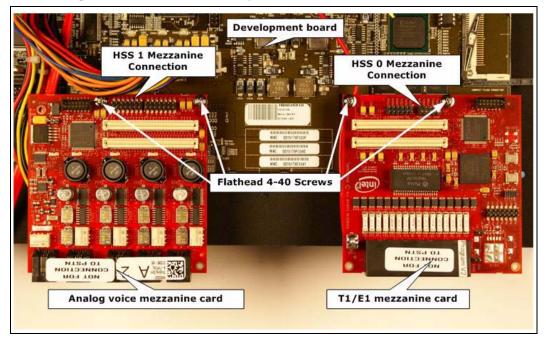

The Intel® EP80579 Development Board supports two types of mezzanine cards: the Intel® EPAVM80579 Analog Voice Mezzanine Card (4-port analog voice card) and the Intel® EPTEM80579 Quad T1/E1 Mezzanine Card (quad T1/E1 card). Figure 3 shows the mezzanine cards installed onto the Intel® EP80579 Development Board. The mezzanine card(s) can be installed into any HSS port connector. See Section 2.10 for ordering information.

Figure 3. Mezzanine Cards

# 2.9 Power Supply

The Intel $^{\circledR}$  EP80579 Development Kit comes with a standard, off-the-shelf ATX12V power supply.

# 2.10 Ordering Information

# Table 8. Ordering Information

| Product Name                                                                                                   | Product Code   | MM#    |

|----------------------------------------------------------------------------------------------------------------|----------------|--------|

| Intel <sup>®</sup> EP80579 Integrated Processor with Intel <sup>®</sup> QuickAssist Technology Development Kit | EP80579TRXDK   | 898430 |

| Intel® EPTEM80579 Quad T1/E1 Mezzanine Card (quad T1/E1 card)                                                  | EP80579TRXT1E1 | 898435 |

| Intel® EPAVM80579 Analog Voice Mezzanine<br>Card (4-port analog voice card)                                    | EP80579TRXVOI  | 898436 |

§ §

# 3.0 System Overview

## 3.1 Power Distribution

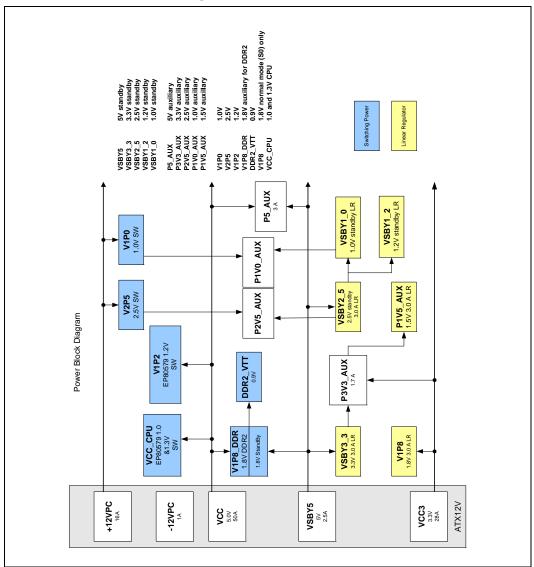

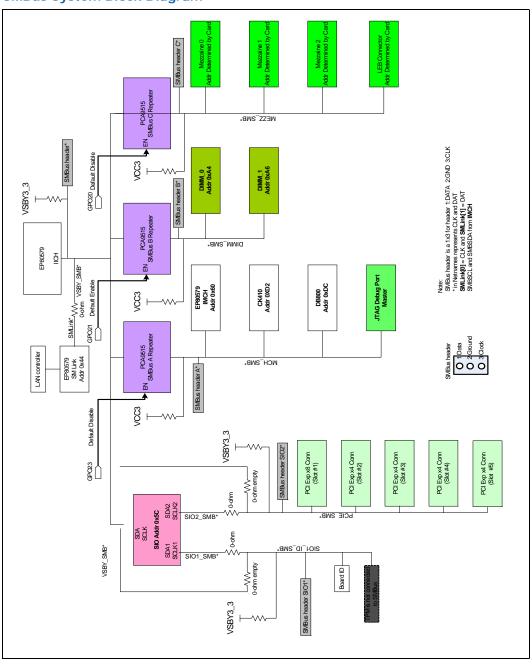

Figure 4 shows the power distribution for the Intel<sup>®</sup> EP80579 Development Board. For details on power distribution logic, see the Schematics and bill of materials for the Intel<sup>®</sup> EP80579 Integrated Processor with Intel<sup>®</sup> QuickAssist Technology Development Kit

Figure 4. Power Distribution Block Diagram

# 3.2 Platform Clocking

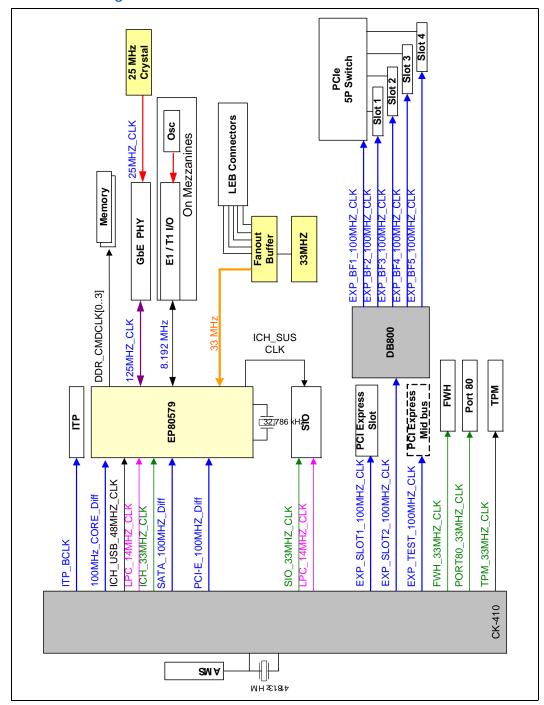

The Intel<sup>®</sup> EP80579 Development Board uses one CK-410 clock synthesizer to generate the host differential pair clocks and the 100 MHz differential clock to the DB800. The DB800 then generates the 100 MHz differential pair clock for PCI Express devices. Figure 5 shows the board clocking configuration.

Figure 5. Clock Block Diagram

October 2008 Order Number: 320067-002US

# 3.3 Platform Reset

Figure 6 depicts the reset logic for the Intel<sup>®</sup> EP80579 Development Board.

Figure 6. Reset Diagram

## 3.4 SMBus

The Intel® EP80579 Development Board provides system management communication through SMBus connectivity. The SMBus is implemented as a single bus with three repeaters used for voltage translation, fan out and isolation on the Intel® EP80579 Development Board. Figure 7 shows the block diagram of the SMBus system on the Intel® EP80579 Development Board.

Figure 7. SMBus System Block Diagram

# 4.0 Technical Reference

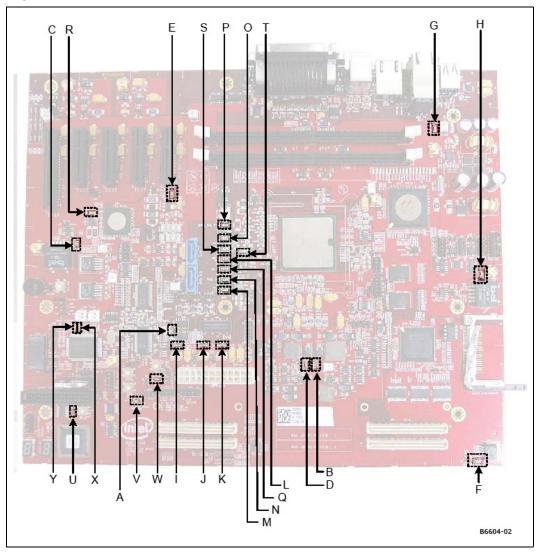

This chapter provides hardware reference information for the Intel<sup>®</sup> EP80579 Development Board, including location of components, connector/header pinout information, jumper settings and switch settings. Figure 8 shows the Intel<sup>®</sup> EP80579 Development Board components layout.

# 4.1 Board Components Layout

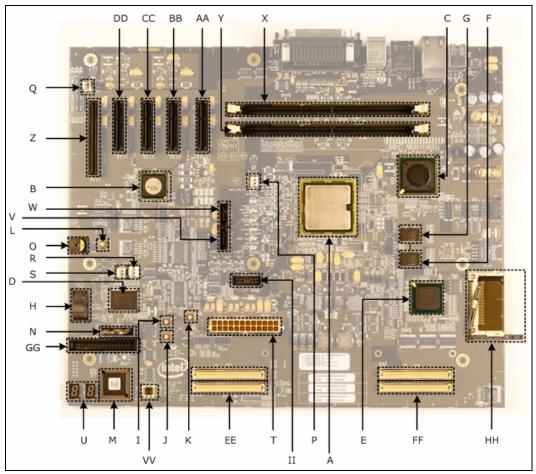

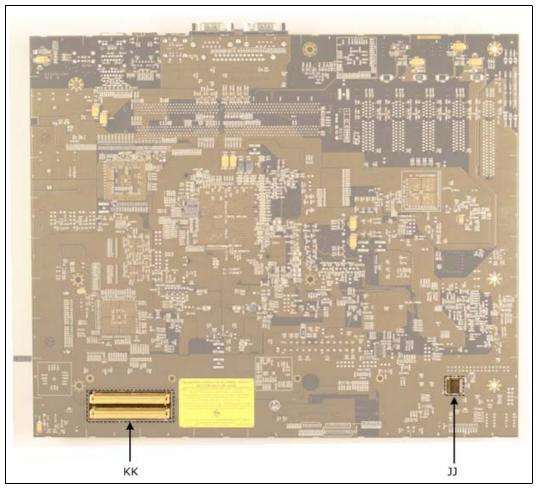

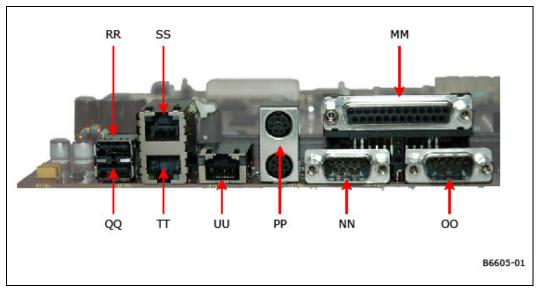

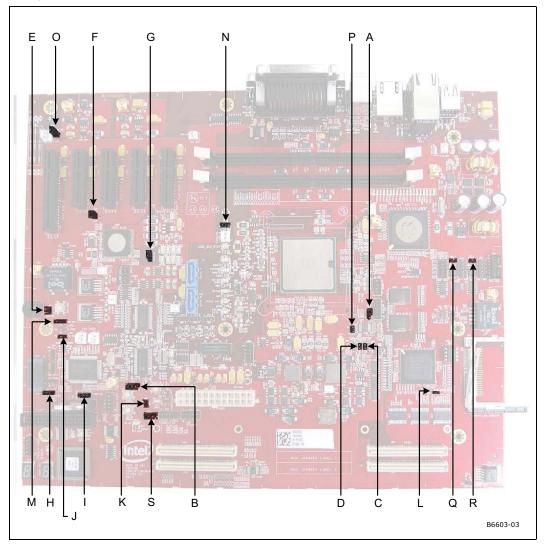

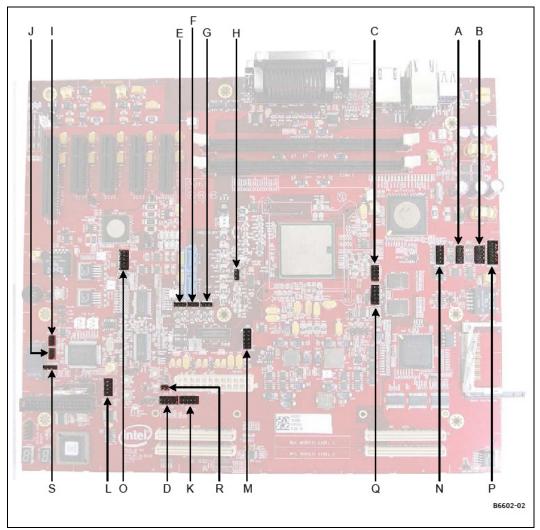

Figure 8 and Figure 9 show the front view and back view of the Intel<sup>®</sup> EP80579 Development Board. Figure 10 shows the external peripheral connectors. Table 9 identifies the components and connectors called out in Figure 8, Figure 9, and Figure 10.

Figure 8. Front View of the Board Components

Figure 9. Back View of the Board Components

October 2008 Order Number: 320067-002US

Figure 10. **Side View of the Board Connectors**

Table 9. Component and Connector Layout Description (Sheet 1 of 2)

| Call-out | Component/Connector                 |

|----------|-------------------------------------|

| А        | Intel® EP80579 Integrated Processor |

| В        | PEX PCIe Switch Chip                |

| С        | Marvell 88E1141 Quad PHY            |

| D        | Super IO Controller                 |

| E        | FPGA                                |

| F        | Flash memory 0                      |

| G        | Flash memory 1                      |

| Н        | FWH                                 |

| 1        | Power button                        |

| J        | Reset button                        |

| K        | Sleep button                        |

| L        | PCIe Wake button                    |

| М        | Port 80 IC                          |

| N        | CMOS battery                        |

| 0        | On-board speaker                    |

| Р        | CPU FAN connector                   |

| Q        | AUX FAN connector                   |

| R        | AUX0 FAN connector                  |

| S        | AUX1 FAN connector                  |

| Т        | ATX power connector                 |

| U        | Two 7-segment display (Port 80)     |

| ٧        | SATA port 0                         |

| W        | SATA port 1                         |

## Table 9. Component and Connector Layout Description (Sheet 2 of 2)

| Call-out | Component/Connector                     |

|----------|-----------------------------------------|

| Х        | DDR2 DIMMO                              |

| Υ        | DDR2 DIMM1                              |

| Z        | Slot 0 x8 connector 4 lanes PCI Express |

| AA       | Slot 1 x4 connector 1 lane PCI Express  |

| ВВ       | Slot 2 x4 connector 1 lane PCI Express  |

| СС       | Slot 3 x4 connector 1 lane PCI Express  |

| DD       | Slot 4 x4 connector 1 lane PCI Express  |

| EE       | Mezzanine connector 1                   |

| FF       | Mezzanine connector 0                   |

| GG       | Floppy Connector                        |

| НН       | CF connector                            |

| П        | ITP-XDP connector                       |

| IJ       | Trusted Platform Module                 |

| KK       | Mezzanine connector 2                   |

| MM       | Parallel port                           |

| NN       | COM0 (Intel® EP80579 UART Port 0)       |

| 00       | COM1 (Intel® EP80579 UART Port 1)       |

| PP       | PS/2 mouse (top)/keyboard (bottom)      |

| QQ       | USB port 0                              |

| RR       | USB port 1                              |

| SS       | RJ-45 Ethernet port 0                   |

| TT       | RJ-45 Ethernet port 1                   |

| UU       | RJ-45 Ethernet port 2                   |

| VV       | SPI Flash                               |

# 4.2 IA-32 Core Frequency Selection

The Intel<sup>®</sup> EP80579 Integrated Processor Product Line is offered in SKUs with a 1200 MHz, 1066 MHz or 600 MHz IA-32 core frequency. The Intel<sup>®</sup> EP80579 Development Board is designed to use the Intel<sup>®</sup> EP80579 Integrated Processor's V\_SEL and BSEL signals to provide the required input clocks and voltages for each of these IA-32 cores. For Intel<sup>®</sup> EP80579 Integrated Processor SKUs with the 1200 MHz IA-32 core, V\_SEL can be used to force the IA-32 core to run at 1066MHz.

Note: 1200 MHz SKUs can be run at 1066 MHz (but not at 600 MHz).

1066 MHz SKUs can only run at 1066 MHz.

600 MHz SKUs can only run at 600 MHz

Table 10 describes how to configure the Intel<sup>®</sup> EP80579 Development Board to support the different IA-32 core frequencies.

Development Kit User's Guide October 2008

28 Order Number: 320067-002US

Intel® EP80579 IA-32 core Frequency Selection Table 10.

| IA-32 core<br>Maximum<br>Operating<br>Frequency<br>(MHz) | Desired IA-32 core Operating Frequency (MHz) | J7F2 Jumper<br>Setting<br>(V_SEL in<br>Table 13) | J7G6 Jumper<br>Setting<br>(BSEL in<br>Table 13) | Comments                                               |  |  |  |  |

|----------------------------------------------------------|----------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------------------------|--|--|--|--|

| 600                                                      | 600                                          | Short 2-3 <sup>1</sup>                           | Short 2-3 <sup>1</sup>                          | Requires a SKU with a 600 MHz IA-<br>32 core frequency |  |  |  |  |

| 1066                                                     | 1066                                         | Short 2-3 <sup>1</sup>                           | Short 2-3 <sup>1</sup>                          |                                                        |  |  |  |  |

| 1200                                                     | 1066                                         | Short 1-2-3 <sup>2</sup>                         | Short 2-3 <sup>1</sup>                          | Allows 1200 MHz IA-32 core to run at 1066 MHz          |  |  |  |  |

| 1200                                                     | 1200                                         | Short 2-3 <sup>1</sup>                           | Short 2-3 <sup>1</sup>                          |                                                        |  |  |  |  |

|                                                          | , , , , , , , , , , , , , , , , , , ,        |                                                  |                                                 |                                                        |  |  |  |  |

<sup>&</sup>quot;Short 1-2-3" means to use a jumper to shunt pins 1-2-3 together

#### 4.3 **SMBus Address**

Table 11 shows the SMBus device addresses on the Intel® EP80579 Development Board.

#### Table 11. **SMBus Connectivity**

| Devices                               | Address                 | Power<br>Rail |

|---------------------------------------|-------------------------|---------------|

| Primary from Inte                     | el <sup>®</sup> EP80579 |               |

| SIO                                   | 0x5C                    | 3.3V          |

| EP80579 Processor - IICH slave device | 0x44                    | 3.3V          |

| SMBus                                 | A                       |               |

| EP80579 Processor - IMCH slave device | 0x60                    | 3.3V          |

| DB800                                 | 0xDC                    | 3.3V          |

| CK410                                 | 0xD2                    | 3.3V          |

| ITP                                   | Master                  | 3.3V          |

| SMBus                                 | В                       |               |

| DIMM 0                                | 0xA4                    | 3.3V          |

| DIMM 1                                | 0xA6                    | 3.3V          |

| SMBus                                 | С                       |               |

| HSS Mezzanine 0                       | Determined by card      | 3.3V          |

| HSS Mezzanine 1                       | Determined by card      | 3.3V          |

| HSS Mezzanine 2                       | Determined by card      | 3.3V          |

# 4.4 System LEDs

The Intel $^{\circledR}$  EP80579 Development Board provides LEDs as indicators for system signals and voltages, as provided in Table 12. Figure 11 shows the location of the LEDs. System LEDs are lit when the signal or voltage is active.

Figure 11. Layout of LEDs

Table 12. Signal and Voltage LED Indicators (Sheet 1 of 2)

| Call-out | Signal  | Label<br>Name | LED Color | Description           |

|----------|---------|---------------|-----------|-----------------------|

| Α        | PWRGD   | DS3G1         | Green     | Power-good LED        |

| В        | VCC_CPU | DS6H2         | Green     | VCC for processor LED |

| С        | 1.0V    | DS2E1         | Green     | 1.0V LED              |

| D        | 1.2V    | DS6H1         | Green     | Front Panel Power LED |

| Е        | 1.5V    | DS3D1         | Green     | 1.5V Auxiliary LED    |

# Table 12. Signal and Voltage LED Indicators (Sheet 2 of 2)

| Call-out | Signal         | Label<br>Name | LED Color | Description                                                                       |

|----------|----------------|---------------|-----------|-----------------------------------------------------------------------------------|

| F        | 1.8V           | DS9K1         | Green     | 1.8V LED                                                                          |

| G        | 1.8V DDR       | DS8B1         | Green     | 1.8V DDR LED                                                                      |

| Н        | 2.5V           | DS9F1         | Green     | 2.5V LED                                                                          |

| I        | 3.3V           | CR3G1         | Green     | 3.3V LED                                                                          |

| J        | 5.0V           | CR4G1         | Green     | 5V LED                                                                            |

| K        | 5.0V Standby   | CR4G2         | Green     | 5V standby LED                                                                    |

| L        | CPU_RESET#     | DS4E3         | Red       | Processor reset                                                                   |

| М        | CPU_THERMTRIP# | DS4F3         | Red       | Processor Thermtrip triggered                                                     |

| N        | CPU_PROCHOT    | DS4F2         | Red       | Processor PROC_HOT signal triggered                                               |

| 0        | IMCH_CPUSLP    | DS4E1         | Red       | Processor entering sleep state                                                    |

| Р        | IMCH_SUS_STAT  | DS4D1         | Red       | Suspend status. System entering a low power state.                                |

| Q        | IMCH_STPCLK    | DS4F1         | Red       | Suspend Clock: output clock from RTC generator circuit to use as a refresh clock. |

| R        | PEX_FATAL_ERR  | DS2D1         | Red       | Error in PCIe switch                                                              |

| S        | IERR           | DS4E2         | Red       | Processor encountered an error. May require a reboot.                             |

| Т        | SLP_S3#        | DS5E1         | Green     | Sleep S3                                                                          |

| U        | INIT33V        | DS1J1         | Red       | Firmware Hub Init                                                                 |

| V        | SATA LED       | DS3J1         | Green     | SATA hard drive activity status                                                   |

| W        | WDT_Timer_Out  | CR3H1         | Green     | Watchdog timer expired                                                            |

| Х        | SIO_LED_GRN    | DS2G2         | Green     | General purpose LED for SIO                                                       |

| Υ        | SIO_LED_YLW    | DS2G1         | Yellow    | General purpose LED for SIO                                                       |

# 4.5 Fixed I/O Map and Interrupts

See the  $Intel^{\it @}$  EP80579 Integrated Processor Product Line Platform Design Guide for information about fixed I/O maps and interrupts.

# 4.6 Jumper Block

Figure 12 shows the location of the jumper blocks. Table 13 lists the settings and usage of the jumpers. Review Figure 12 and Table 13 before changing the default jumper settings.

## Warning:

Do not move jumpers when the power is on. Always turn off the power and unplug the power cord from the power supply before changing a jumper setting. Otherwise, the Intel $^{\circledR}$  EP80579 Integrated Processor may be damaged.

Figure 12. Jumper Block Locations

Table 13. Jumper Block Descriptions (Sheet 1 of 3)

| Location | Jumper Name              | Ref Des       | Description                                                                                                                                                                                                  | Default<br>Position |

|----------|--------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| А        | V_SEL                    | J7F2          | SKU and Voltage Selection:<br>See Table 10                                                                                                                                                                   | 2-3                 |

| В        | BSEL                     | J3H1,<br>J7G6 | FSB frequency selection:<br>See Table 10                                                                                                                                                                     | 2-3                 |

| С        | 1.0V Override<br>(V_SEL) | J7G4          | Intel Internal Test Only 1.0V override selection: Short = Force IA core voltage to 1.0V Note: R3U6 0 ohms resistor needs to be removed.  Open = IA core voltage is determined based on V_SEL signal and BSEL | Open                |

Table 13. Jumper Block Descriptions (Sheet 2 of 3)

| Location | Jumper Name                       | Ref Des | Description                                                                                                                                                                                                 | Default<br>Position |

|----------|-----------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| D        | 1.3V Override<br>(V_SEL)          | J7G3    | Intel Internal Test Only 1.3V override selection: Short = Force IA core voltage to 1.3V Note: R3U7 0 ohms resistor needs to be removed. Open = IA core voltage is determined based on V_SEL signal and BSEL | Open                |

| E        | No Reboot Strap                   | J1F1    | Short = No reboot on second time-out of TCO timer  Open = Reboot on second time-out of TCO timer                                                                                                            | Open                |

| F        | PLX PCIe Switch<br>EEPROM Present | J2D1    | Manually disable PLX PCIe switch EEPROM: Short = EEPROM is present Open = EEPROM is not present                                                                                                             | Short               |

| G        | PLX PCIe Switch<br>Reset          | J3E1    | Manually reset PLX PCI Express switch:  1-2 = Normal  2-3 = Resetting PLX PCI Express Switch                                                                                                                | 1-2                 |

| Н        | Quad GbE PHY Reset                | J1H2    | Manually reset Quad GbE PHY: Short = Normal Open = Resetting Quad GbE PHY                                                                                                                                   | Short               |

| I        | SIO Disable                       | J2H2    | Manually disable SIO:<br>Short = Normal<br>Open = Disabling SIO                                                                                                                                             | Short               |

| J        | Top Block Lock                    | J1G1    | Locking FWH Top Block: Short = Locking Top Block Open = Top Block is not locked                                                                                                                             | Open                |

| К        | Watchdog Timer<br>Reset           | ЈЗНЗ    | Enable to generate reset when WDT expires:<br>Short= Generates WDT reset<br>Open = No WDT reset                                                                                                             | Open                |

| L        | FPGA Program                      | J8H1    | Enable to program FPGA:<br>Short = Programs FPGA<br>Open = Normal                                                                                                                                           | Open                |

| М        | FWH Program                       | J1F2    | Enable to program and erase FWH:<br>Short = Allow normal program or erase of FWH<br>Open = No program or erase allowed                                                                                      | Open                |

| N        | CPU FAN Speed<br>Override         | J4D1    | Processor speed override: Short = Full speed Open = SIO PWM speed control                                                                                                                                   | Open                |

| 0        | Aux FAN Speed<br>Override         | J1B1    | Aux fan speed override:<br>Short = Full speed<br>Open = SIO PWM speed control                                                                                                                               | Open                |

| Р        | Front Panel Sleep<br>Signal       | J7G1    | GPIO 30 is configured to external sleep signal jumper: Short = Manually generate sleep signal Open = Normal                                                                                                 | Open                |

| Q        | CANO Termination                  | J9E1    | CAN Bus 0 Termination:<br>Short = Terminate CAN Bus 0<br>Open = CAN Bus 0 not terminated                                                                                                                    | Open                |

| R        | CAN1 Termination                  | J9E2    | CAN Bus 1 Termination:<br>Short = Terminate CAN Bus 1<br>Open = CAN Bus 1 not terminated                                                                                                                    | Open                |

## Table 13. Jumper Block Descriptions (Sheet 3 of 3)

| Location | Jumper Name                                          | Ref Des       | Description                                                                                                                                                                                 | Default<br>Position |

|----------|------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| S        | CMOS Clear<br>Section 5.11                           | J3J1          | Reset CMOS:<br>1-2 = Normal<br>2-3 = Clear CMOS                                                                                                                                             | 1-2                 |

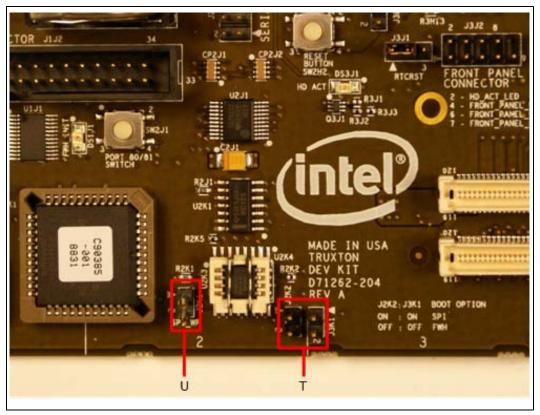

| Т        | Boot Option for SPI<br>Boot or FWH Boot<br>Selection | J2K2,<br>J3K1 | Boot Option Selection: Figure 13  J2K2, J3K1 = GPIO17, GPIO33  Open, Open -> Boot From FWH (default)  Open, Short -> RESERVED  Short, Open -> RESERVED  Short, Short -> Boot From SPI Flash | 1-2                 |

| U        | SPI Flash Write<br>Protection                        | J2K1          | SPI Flash WP: Figure 13 Short = Write Protected Open = Normal (default)                                                                                                                     | 1-2                 |

Figure 13 shows the SPI and FWH boot selection option.

Figure 13. SPI and FWH Boot Option Jumpers

Development Kit User's Guide October 2008

34 Order Number: 320067-002US

#### 4.7 **Header Blocks**

Figure 14 and Table 14 describe the location of the headers.

Warning:

Before applying power to the  $Intel^{\circledR}$  EP80579 Integrated Processor, ensure that the headers are connected correctly. Improper configuration of the  $Intel^{\circledR}$  EP80579 Development Board headers may result in board damage.

#### Figure 14. **Header Locations**

Table 14. **Header Block Descriptions (Sheet 1 of 2)**

| Location | Header Name                    | Ref Des | Pinout Signal Description |

|----------|--------------------------------|---------|---------------------------|

| А        | CANO                           | J9E3    | Table 21                  |

| В        | CAN1                           | J9E4    | Table 21                  |

| С        | IEEE 1588-2008 Hardware-assist | J7E1    | Table 22                  |

| D        | Front panel                    | J3J2    | Table 23                  |

| Е        | SMBUS_A                        | J4F2    | Table 24                  |

## Table 14. Header Block Descriptions (Sheet 2 of 2)

| Location | Header Name                     | Ref Des | Pinout Signal Description                                                 |  |

|----------|---------------------------------|---------|---------------------------------------------------------------------------|--|

| F        | SMBUS_B                         | J4F3    | Table 24                                                                  |  |

| G        | SMBUS_C                         | J4F4    | Table 24                                                                  |  |

| Н        | VSBY_SMB                        | J5E1    | Table 24                                                                  |  |

| Ţ        | SIO1 SMBUS                      | J1G2    | Table 24, connected to Board ID EEPROM                                    |  |

| J        | SIO2 SMBUS                      | J1G3    | Table 24, connected to PCIe slot                                          |  |

| K        | SSP                             | J4J1    | Table 25                                                                  |  |

| L        | COM3 (Tertiary SIO UART)        | J2J1    | Table 26                                                                  |  |

| М        | Intel <sup>®</sup> EP80579 JTAG | J5G2    | Table 27                                                                  |  |

| N        | 88E1141 JTAG                    | J8E1    | Table 27                                                                  |  |

| 0        | PEX 8058 JTAG                   | J3E2    | Table 27                                                                  |  |

| Р        | FPGA JTAG                       | J9E5    | Table 28                                                                  |  |

| Q        | GPIO header                     | J7F1    | Table 29                                                                  |  |

| R        | Intruder                        | J3H4    | Optional intruder switch header: 1: MICH_INTRUDER 2: GND                  |  |

| S        | CPU thermal diode               | J1H1    | Access to processor thermal diode: 1: CPU_THERM_DC 2: CPU_THERM_DA 3: GND |  |

# 4.8 Connector/Header Pinout Information

## 4.8.1 ITP-XDP Connector Pinout

The Intel  $^{\circledR}$  EP80579 Development Board provides a 60-pin ITP-XDP connector for system debugging purposes. For ITP-XDP pinout, refer to Table 15.

Table 15. ITP-XDP Connector (Sheet 1 of 2)

| Pin | Name            | Pin | Name      |

|-----|-----------------|-----|-----------|

| 1   | GND             | 2   | GND       |

| 3   | PREQ_N          | 4   | NOA_CLK_0 |

| 5   | PRDY_N          | 6   | NOA_CLK_1 |

| 7   | GND             | 8   | GND       |

| 9   | BPM_3 / NOA_0   | 10  | NOA_8     |

| 11  | BPM_2_N / NOA_1 | 12  | NOA_9     |

| 13  | GND             | 14  | GND       |

| 15  | BPM_1_N / NOA_2 | 16  | NOA_10    |

| 17  | BPM_0_N / NOA_3 | 18  | NOA_11    |

| 19  | GND             | 20  | GND       |

| 21  | NC              | 22  | NC        |

| 23  | NC              | 24  | NC        |

| 25  | GND             | 26  | GND       |

| 27  | NOA_4           | 28  | NOA_12    |

Development Kit User's Guide October 2008

36 Order Number: 320067-002US

Table 15. ITP-XDP Connector (Sheet 2 of 2)

| Pin | Name       | Pin | Name        |

|-----|------------|-----|-------------|

| 29  | NOA_5      | 30  | NOA_13      |

| 31  | GND        | 32  | GND         |

| 33  | NOA_6      | 34  | NOA_14      |

| 35  | NOA_7      | 36  | NOA_15      |

| 37  | GND        | 38  | GND         |

| 39  | PWRGOOD    | 40  | BCLK_P      |

| 41  | DFXTEST    | 42  | BCLK_N      |

| 43  | 1.8V       | 44  | 1.8V        |

| 45  | PCICLK     | 46  | RESET_N     |

| 47  | PCICLK REF | 48  | DBR_N       |

| 49  | GND        | 50  | GND         |

| 51  | SMBUS_DATA | 52  | TDO         |

| 53  | SMBUS_CLK  | 54  | TRST_N      |

| 55  | NC         | 56  | TDI         |

| 57  | TCK        | 58  | TMS         |

| 59  | GND        | 60  | XDP_PRSNT_N |

#### 4.8.2 ATX12V Power Connector Pinout

The Intel<sup>®</sup> EP80579 Development Board comes with a 2x12 main power connector. This connector is compatible with a 2x10 power connector. The board supports the use of ATX12V power supplies with either 2x10 or 2x12 main power cables. Table 16 shows the pinout of the main power supply.

Table 16. Main ATX Power Supply Connector

| Pin | Description    | Pin | Description |

|-----|----------------|-----|-------------|

| 1   | +3.3 V         | 13  | +3.3 V      |

| 2   | +3.3 V         | 14  | -12 V       |

| 3   | GND            | 15  | GND         |

| 4   | +5 V           | 16  | PS-ON#      |

| 5   | GND            | 17  | GND         |

| 6   | +5 V           | 18  | GND         |

| 7   | GND            | 19  | GND         |

| 8   | PWROK          | 20  | NC          |

| 9   | +5 V (Standby) | 21  | +5 V        |

| 10  | +12 V          | 22  | +5 V        |

| 11  | +12 V*         | 23  | +5 V*       |

| 12  | +3 V*          | 24  | GND*        |

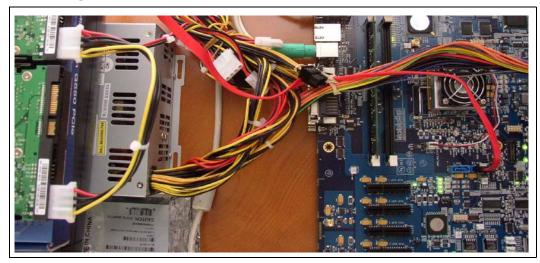

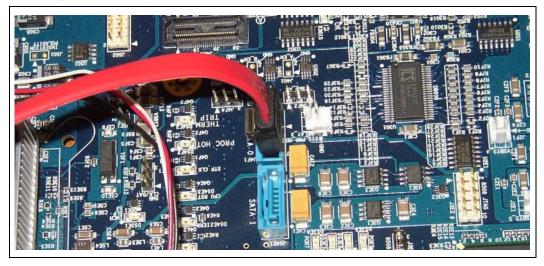

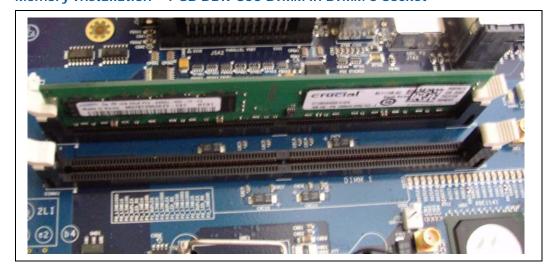

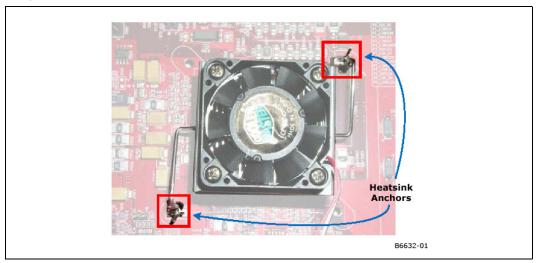

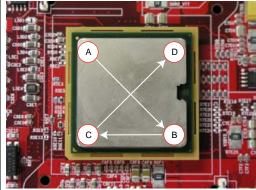

$<sup>^{\</sup>star}$  The pin is not connected when using a 2x12 power supply cable.