# Intel® Core™2 Duo Processors and Intel® Core™2 Extreme Processors for Platforms Based on Mobile Intel® 965 Express Chipset Family

**Datasheet**

January 2008

Document Number: 316745-005

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Enabling Execute Disable Bit functionality requires a PC with a processor with Execute Disable Bit capability and a supporting operating system. Check with your PC manufacturer on whether your system delivers Execute Disable Bit functionality.

Enhanced Intel SpeedStep® Technology for specified units of this processor available Q2/06. See the Processor Spec Finder at http://processorfinder.intel.com or contact your Intel representative for more information.

Intel® Virtualization Technology requires a computer system with an enabled Intel® processor, BIOS, virtual machine monitor (VMM) and, for some uses, certain platform software enabled for it. Functionality, performance or other benefits will vary depending on hardware and software configurations and may require a BIOS update. Software applications may not be compatible with all operating systems. Please check with your application vendor.

This device is protected by U.S. patent numbers 5,315,448 and 6,516,132, and other intellectual property rights. The use of Macrovision's copy protection technology in the device must be authorized by Macrovision and is intended for home and other limited pay-per-view uses only, unless otherwise authorized in writing by Macrovision. Reverse engineering or disassembly is prohibited.

64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel® 64 architecture. Processors will not operate (including 32-bit operation) without an Intel® 64 architecture-enabled BIOS. Performance will vary depending on your hardware and software configurations. Consult with your system vendor for more information.

Intel, Pentium, Intel Core, Intel Core 2, Intel SpeedStep and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright  $\,^{\hbox{\tiny \sc C}}$  2007 - 2008, Intel Corporation. All rights reserved.

# **Contents**

| 1 | Intro      | oduction                                          | 7   |

|---|------------|---------------------------------------------------|-----|

|   | 1.1        | Terminology                                       | 8   |

|   | 1.2        | References                                        | 9   |

| 2 | Low        | Power Features                                    | 11  |

|   | 2.1        | Clock Control and Low Power States                |     |

|   |            | 2.1.1 Core Low Power State Descriptions           |     |

|   |            | 2.1.2 Package Low Power State Descriptions        |     |

|   | 2.2        | Enhanced Intel SpeedStep® Technology              |     |

|   |            | 2.2.1 Dynamic FSB Frequency Switching             | 19  |

|   |            | 2.2.2 Intel® Dynamic Acceleration Technology      |     |

|   | 2.3        | Extended Low Power States                         |     |

|   | 2.4        | FSB Low Power Enhancements                        |     |

|   | 2.5        | VID-x                                             |     |

|   | 2.6        | Processor Power Status Indicator (PSI-2) Signal   | 21  |

| 3 | Elect      | rical Specifications                              | 23  |

|   | 3.1        | Power and Ground Pins                             | 23  |

|   | 3.2        | FSB Clock (BCLK[1:0]) and Processor Clocking      |     |

|   | 3.3        | Voltage Identification                            |     |

|   | 3.4        | Catastrophic Thermal Protection                   |     |

|   | 3.5        | Reserved and Unused Pins                          |     |

|   | 3.6        | FSB Frequency Select Signals (BSEL[2:0])          |     |

|   | 3.7<br>3.8 | FSB Signal GroupsCMOS Signals                     |     |

|   | 3.8<br>3.9 | Maximum Ratings                                   |     |

|   | 3.10       | Processor DC Specifications                       |     |

| _ |            | ·                                                 |     |

| 4 |            | age Mechanical Specifications and Pin Information |     |

|   | 4.1        | Package Mechanical Specifications                 |     |

|   | 4.2        | Processor Pinout and Pin List                     |     |

|   | 4.3        | Alphabetical Signals Reference                    |     |

| 5 | Ther       | mal Specifications and Design Considerations      |     |

|   | 5.1        | Thermal Specifications                            |     |

|   |            | 5.1.1 Thermal Diode                               |     |

|   |            | 5.1.2 Thermal Diode Offset                        |     |

|   |            | 5.1.3 Intel® Thermal Monitor                      |     |

|   |            | 5.1.4 Digital Thermal Sensor                      |     |

|   |            | 5.1.5 Out of Specification Detection              |     |

|   |            | 5.1.6 PROCHOT# Signal Pin                         | റ / |

| _ |   |   | ~ |   |

|---|---|---|---|---|

|   | ш | u |   | - |

|   | - |   |   | _ |

| 1        | Core Low Power States                                                                                                                | 12  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2        | Package Low Power States                                                                                                             | 13  |

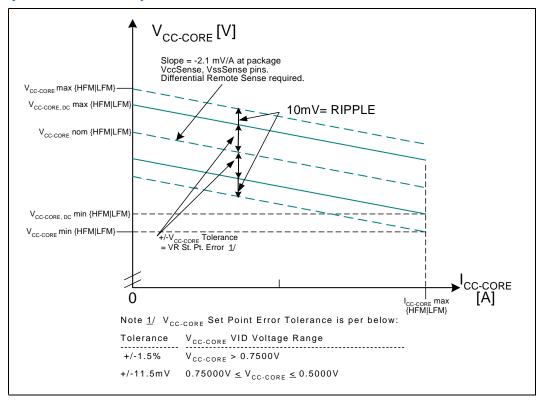

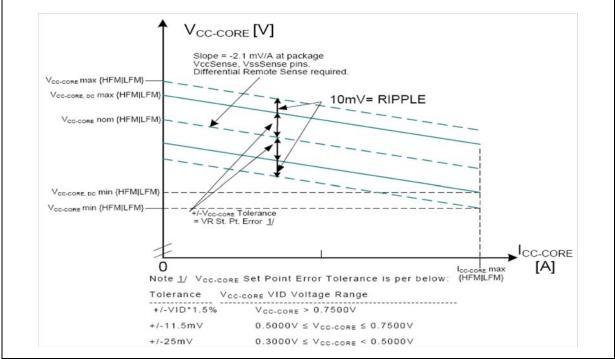

| 3        | Active VCC and ICC Loadline Intel Core 2 Duo Processors - Standard Voltage,                                                          |     |

|          | Low Voltage and Ultra Low Voltage and Intel Core 2 Extreme Processors                                                                |     |

|          | (PSI# Not Asserted)                                                                                                                  | 36  |

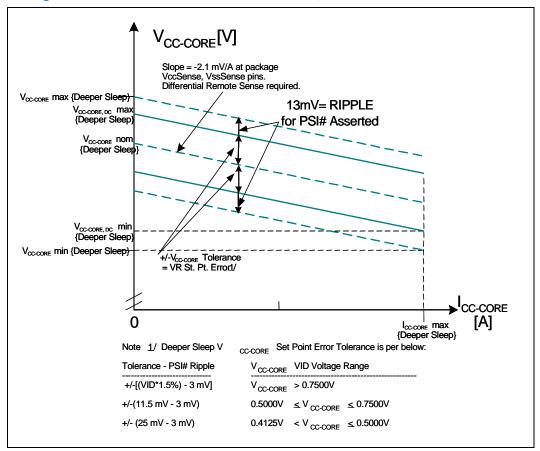

| 4        | Deeper Sleep VCC and ICC Loadline Intel Core 2 Duo Processors -                                                                      | 2.7 |

| E        | Standard Voltage and Intel Core 2 Extreme Processors (PSI# Asserted)  Deeper Sleep VCC and ICC Loadline Intel Core 2 Duo Processor - |     |

| 5        | Low Voltage and Ultra Low Voltage (PSI# Asserted)                                                                                    | 38  |

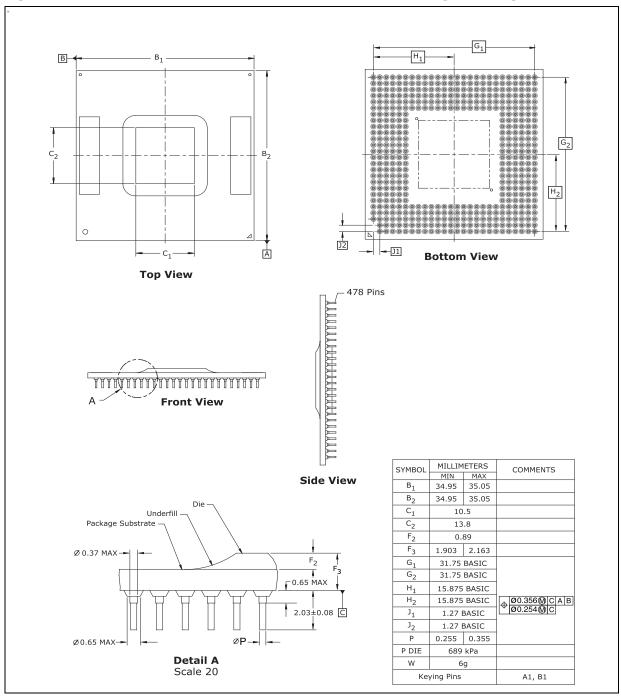

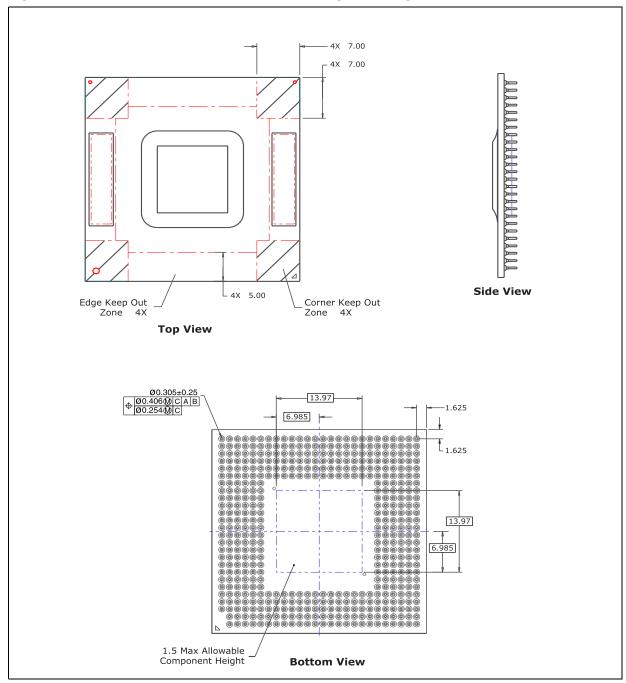

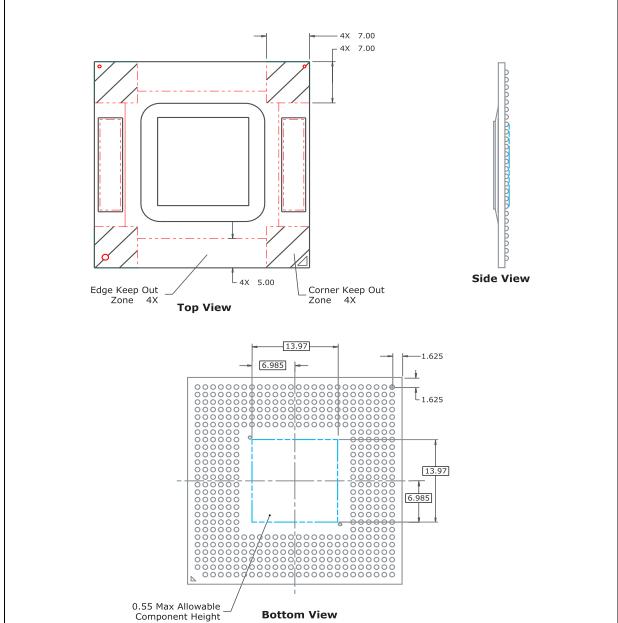

| 6        | 4-MB and Fused 2-MB Micro-FCPGA Processor Package Drawing (Sheet 1 of 2)                                                             | 42  |

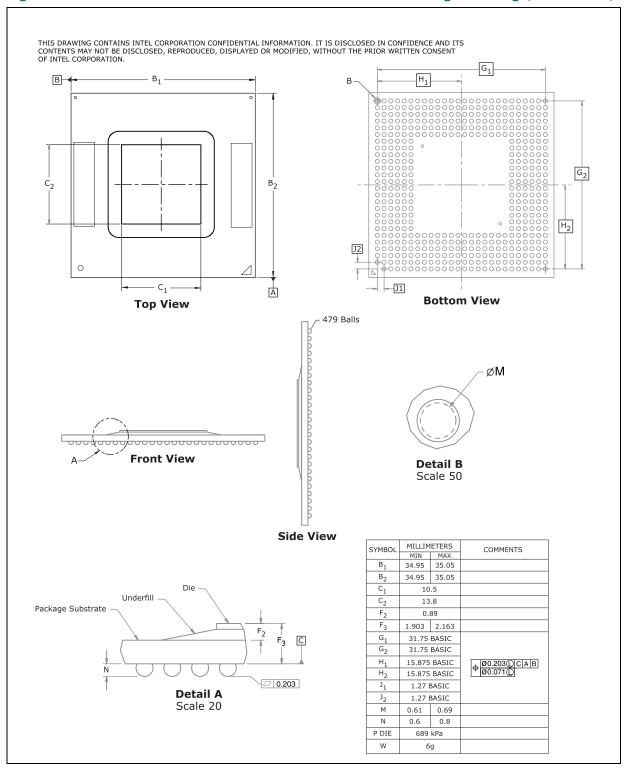

| 7        | 4-MB and Fused 2-MB Micro-FCPGA Processor Package Drawing (Sheet 2 of 2)                                                             |     |

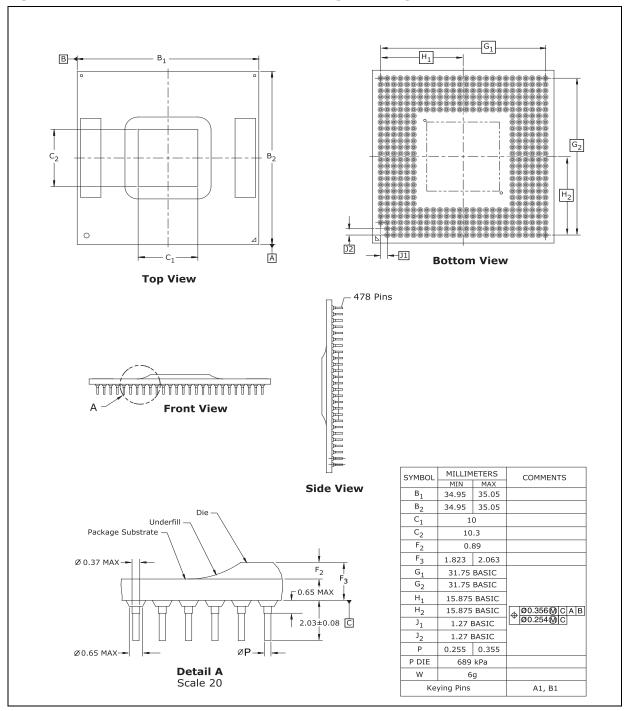

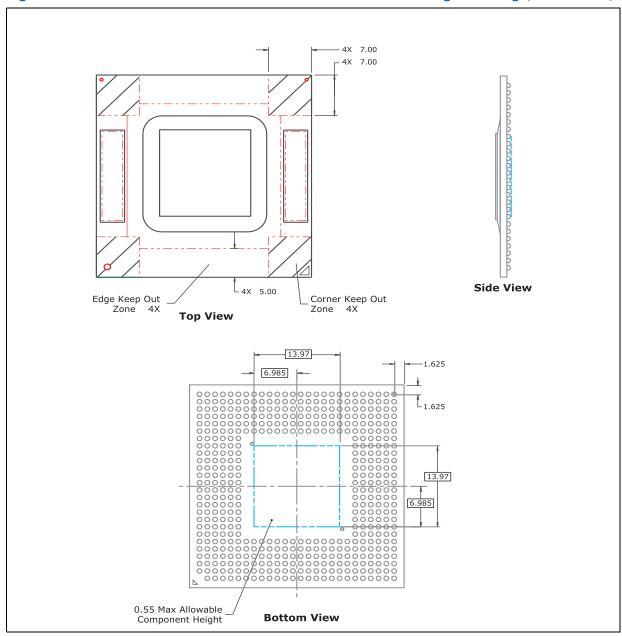

| 8        | 2-MB Micro-FCPGA Processor Package Drawing (Sheet 1 of 2)                                                                            |     |

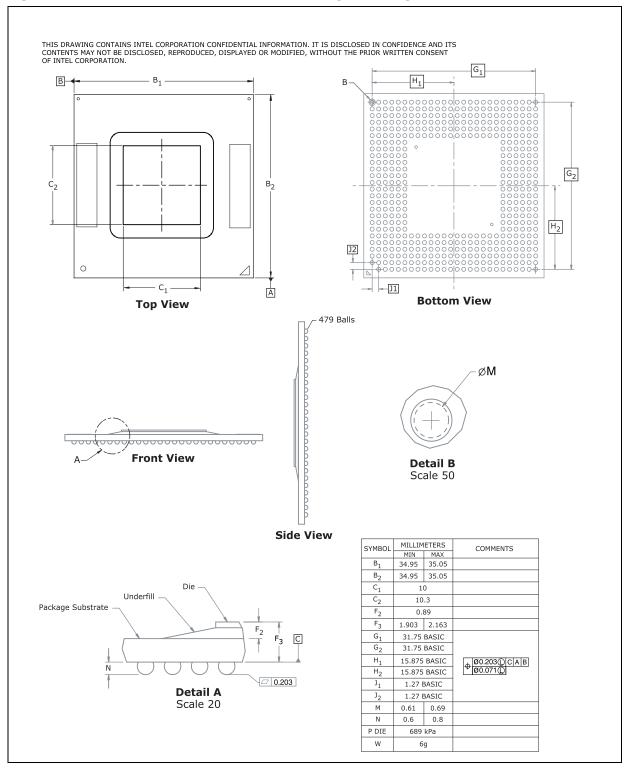

| 9        | 2-MB Micro-FCPGA Processor Package Drawing (Sheet 2 of 2)                                                                            |     |

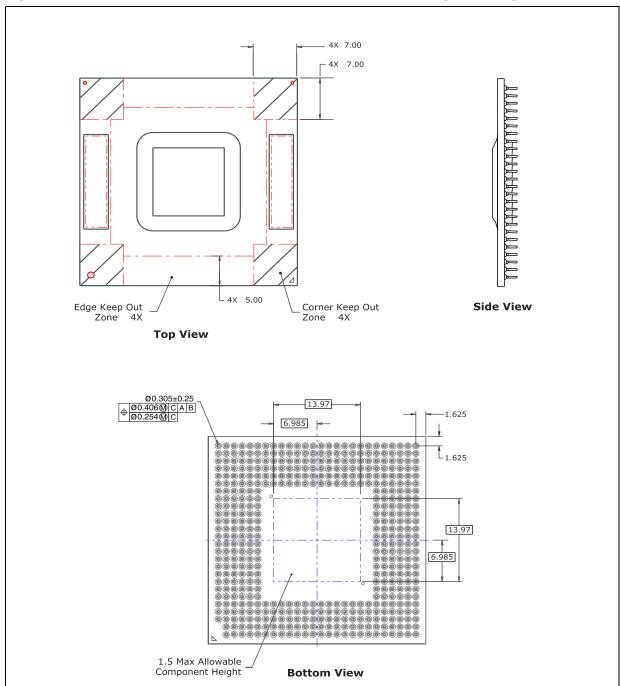

| 10       | 4-MB and Fused 2-MB Micro-FCBGA Processor Package Drawing (Sheet 1 of 2)                                                             |     |

| 11       | 4-MB and Fused 2-MB Micro-FCBGA Processor Package Drawing (Sheet 2 of 2)                                                             | 47  |

| 12       | 2-MB Micro-FCBGA Processor Package Drawing (Sheet 1 of 2)                                                                            |     |

| 13       | 2-MB Micro-FCBGA Processor Package Drawing (Sheet 2 of 2)                                                                            | 49  |

|          |                                                                                                                                      |     |

| Table    | es                                                                                                                                   |     |

| 1        | Coordination of Core Low Power States at the Package Level                                                                           | 13  |

| 2        | Voltage Identification Definition                                                                                                    |     |

| 3        | BSEL[2:0] Encoding for BCLK Frequency                                                                                                |     |

| 4        | FSB Pin Groups                                                                                                                       |     |

| 5        | Processor Absolute Maximum Ratings                                                                                                   |     |

| 6        | Voltage and Current Specifications for the Intel Core 2 Duo Processors -                                                             |     |

|          | Standard Voltage                                                                                                                     | 30  |

| 7        | Voltage and Current Specifications for the Intel Core 2 Duo Processors -                                                             |     |

| •        | Low Voltage                                                                                                                          | 32  |

| 8        | Voltage and Current Specifications for the Intel Core 2 Duo -Ultra Low                                                               | 2.2 |

| 9        | Voltage Processors                                                                                                                   |     |

| 10       | FSB Differential BCLK Specifications                                                                                                 |     |

| 11       | AGTL+ Signal Group DC Specifications                                                                                                 |     |

| 12       | CMOS Signal Group DC Specifications                                                                                                  |     |

| 13       | Open Drain Signal Group DC Specifications                                                                                            |     |

| 14       | The Coordinates of the Processor Pins as Viewed from the Top of the Package                                                          |     |

|          | (Sheet 1 of 2)                                                                                                                       | 50  |

| 15       | The Coordinates of the Processor Pins as Viewed from the Top of the Package                                                          |     |

|          | (Sheet 2 of 2)                                                                                                                       |     |

| 16       |                                                                                                                                      |     |

| 17       | Pin Listing by Pin Number                                                                                                            |     |

| 18       | Signal Description                                                                                                                   |     |

| 19       | Power Specifications for the Intel Core 2 Duo Processor - Standard Voltage                                                           |     |

| 20       | Power Specifications for the Intel Core 2 Duo Processor - Low Voltage                                                                |     |

| 21       | Power Specifications for the Intel Core 2 Duo Processor - Ultra Low Voltage                                                          |     |

| 22       | Power Specifications for the Intel Core 2 Extreme Processor                                                                          |     |

| 23       | Thermal Diode Interface                                                                                                              |     |

| 24<br>25 | Thermal Diode Parameters Using Diode Model                                                                                           |     |

| 25<br>26 | Thermal Diode Parameters Using Transistor Moder                                                                                      |     |

| ~ ( )    |                                                                                                                                      |     |

# **Revision History**

| Document<br>Number | Revision<br>Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Date         |

|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 316745             | -001               | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | May 2007     |

| 316745             | -002               | <ul> <li>Updates         <ul> <li>Chapter 1 added Intel® Core™2 Duo processor - Ultra Low Voltage information</li> <li>Chapter 3 added Table 8 with Intel Core 2 Duo processor - Ultra Low Voltage U7600 and U7500 specifications</li> <li>Chapter 3 updated Figure 3 and 5 with Intel Core 2 Duo processor - Ultra Low Voltage information</li> <li>Chapter 5 added Table 19 with Intel Core 2 Duo processor - Ultra Low Voltage U7600 and U7500 specifications</li> </ul> </li> </ul>         | June 2007    |

| 316745             | -003               | <ul> <li>Updates         <ul> <li>Chapter 1 added Intel® Core™2 Extreme processor</li> <li>Chapter 3 added Table 9 with Intel Core 2 Extreme processor X7800 specifications</li> <li>Chapter 3 updated Figure 3 and 4 with Intel Core 2 Extreme processor information</li> <li>Chapter 5 added Table 20 with Intel Core 2 Extreme processor X7800 specifications</li> <li>Corrected the pin diagram for 4-MB Micro-FCPGA and 2-MB Micro-FCPGA Processor Package Drawings</li> </ul> </li> </ul> | July 2007    |

| 316745             | -004               | Updates     Chapter 3 added Intel Core 2 Extreme processor X7900 and Low Voltage processor L7700 specifications     Chapter 5 added Intel Core 2 Extreme processor X7900 and Low Voltage processor L7700 specifications                                                                                                                                                                                                                                                                         | August 2007  |

| 316745             | -005               | <ul> <li>Updates</li> <li>Chapter 3 added Table 8 with Intel Core 2 Duo processor - Ultra Low Voltage U7700 specifications</li> <li>Chapter 5 added Table 21 with Intel Core 2 Duo processor -Ultra Low Voltage U7700 specifications</li> </ul>                                                                                                                                                                                                                                                 | January 2007 |

## 1 Introduction

The Intel® Core<sup>™</sup>2 Duo processor on 65-nm process technology is the next generation high-performance, low-power processor based on the Intel® Core<sup>™</sup> microarchitecture. The Intel Core 2 Duo processor supports the Mobile Intel® 965 Express Chipset and Intel® 82801HBM ICH8M Controller Hub Based Systems. This document contains electrical, mechanical and thermal specifications for the following processors:

- Intel Core 2 Duo processor Standard Voltage

- · Intel Core 2 Duo processor Low Voltage

- Intel Core 2 Duo processor Ultra Low Voltage

- · Intel Core 2 Extreme processor

#### Note:

In this document, the Intel Core 2 Duo and Intel Core 2 Extreme processors are referred to as the processor and Mobile Intel® 965 Express Chipset family is referred to as the (G)MCH.

The following list provides some of the key features on this processor:

- · Dual core processor for mobile with enhanced performance

- Intel architecture with Intel® Wide Dynamic Execution

- · L1 Cache to Cache (C2C) transfer

- On-die, primary 32-KB instruction cache and 32-KB write-back data cache in each core

- On-die, up to 4-MB second level shared cache with advanced transfer cache architecture

- Streaming SIMD Extensions 2 (SSE2), Streaming SIMD Extensions 3 (SSE3) and Supplemental Streaming SIMD Extensions 3 (SSSE3)

- 800-MHz Source-Synchronous Front Side Bus (FSB) for Intel Core 2 Extreme processors, Intel Core 2 Duo standard and low voltage processors. 533-MHz FSB for Intel Core 2 Duo ultra low voltage processors

- Advanced power management features including Enhanced Intel SpeedStep® Technology and Dynamic FSB frequency switching.

- Intel Enhanced Deeper Sleep state with P\_LVL5 I/O support

- Digital Thermal Sensor (DTS)

- Intel® 64 Technology

- · Enhanced Intel® Virtualization Technology

- Intel® Dynamic Acceleration Technology

- Enhanced Multi Threaded Thermal Management (EMTTM)

- PSI2 functionality

- Standard voltage processors are offered in Micro-FCPGA and Micro-FCBGA packaging. Low voltage and Ultra low voltage processors are offered in Micro-FCBGA packaging only. Intel Core 2 Extreme processors are offered in Micro-FCPGA packaging only.

- · Execute Disable Bit support for enhanced security

## 1.1 Terminology

| Term                                       | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #                                          | A "#" symbol after a signal name refers to an active low signal, indicating a signal is in the active state when driven to a low level. For example, when RESET# is low, a reset has been requested. Conversely, when NMI is high, a nonmaskable interrupt has occurred. In the case of signals where the name does not imply an active state but describes part of a binary sequence (such as address or data), the "#" symbol implies that the signal is inverted. For example, D[3:0] = "HLHL" refers to a hex 'A', and D[3:0]# = "LHLH" also refers to a hex "A" (H= High logic level, L= Low logic level). XXXX means that the specification or value is yet to be determined. |

| Front Side Bus<br>(FSB)                    | Refers to the interface between the processor and system core logic (also known as the chipset components).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AGTL+                                      | Advanced Gunning Transceiver Logic. Used to refer to Assisted GTL+ signaling technology on some Intel processors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Storage<br>Conditions                      | Refers to a non-operational state. The processor may be installed in a platform, in a tray, or loose. Processors may be sealed in packaging or exposed to free air. Under these conditions, processor landings should not be connected to any supply voltages, have any I/Os biased or receive any clocks. Upon exposure to "free air" (i.e., unsealed packaging or a device removed from packaging material) the processor must be handled in accordance with moisture sensitivity labeling (MSL) as indicated on the packaging material.                                                                                                                                          |

| Enhanced Intel<br>SpeedStep®<br>Technology | Technology that provides power management capabilities to laptops.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Processor Core                             | Processor core die with integrated L1 and L2 cache. All AC timing and signal integrity specifications are at the pads of the processor core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Intel® 64<br>Technology                    | 64-bit memory extensions to the IA-32 architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Intel®<br>Virtualization<br>Technology     | Processor virtualization which when used in conjunction with Virtual Machine Monitor software enables multiple, robust independent software environments inside a single platform.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TDP                                        | Thermal Design Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>CC</sub>                            | The processor core power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>SS</sub>                            | The processor ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## 1.2 References

Material and concepts available in the following documents may be beneficial when reading this document.

| Document                                                                                            | Document Number <sup>1,2</sup>                                             |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Intel® Core™ 2 Duo Processors For Intel® Centrino® Duo Processor<br>Technology Specification Update | 314079                                                                     |

| Mobile Intel® 965 Express Chipset Family Datasheet                                                  | 316273                                                                     |

| Mobile Intel® 965 Express Chipset Family Specification Update                                       | 316274                                                                     |

| Intel® I/O Controller Hub 8 (ICH8)/ I/O Controller Hub 8M (ICH8M)<br>Datasheet                      | See http://<br>www.intel.com/design/<br>chipsets/datashts/<br>313056.htm   |

| Intel® I/O Controller Hub 8 (ICH8)/ I/O Controller Hub 8M (ICH8M)<br>Specification Update           | See http://<br>www.intel.com/design/<br>chipsets/specupdt/<br>313057.htm   |

| Intel® 64 and IA-32 Architectures Software Developer's Manual                                       | See http://<br>www.intel.com/design/<br>pentium4/manuals/<br>index_new.htm |

| Intel® 64 and IA-32 Architectures Software Developer's Manuals<br>Documentation Change              | See http:// developer.intel.com/ design/processor/ specupdt/252046.htm     |

| Volume 1: Basic Architecture                                                                        | 253665                                                                     |

| Volume 2A: Instruction Set Reference, A-M                                                           | 253666                                                                     |

| Volume 2B: Instruction Set Reference, N-Z                                                           | 253667                                                                     |

| Volume 3A: System Programming Guide                                                                 | 253668                                                                     |

| Volume 3B: System Programming Guide                                                                 | 253669                                                                     |

#### NOTES:

1. Contact your local Intel representative for the latest revision of this document.

§

#### Introduction

10

## 2 Low Power Features

#### 2.1 Clock Control and Low Power States

The processor supports low power states both at the individual core level and the package level for optimal power management.

A core may independently enter the C1/AutoHALT, C1/MWAIT, C2, C3, and C4 low power states. When both cores coincide in a common core low power state, the central power management logic ensures that the entire processor enters the respective package low power state by initiating a P\_LVLx (P\_LVL2, P\_LVL3, P\_LVL4, or P\_LVL5) I/O read to the chipset.

The processor implements two software interfaces for requesting low power states: MWAIT instruction extensions with sub-state hints or P\_LVLx reads to the ACPI P\_BLK register block mapped in the processor's I/O address space. The P\_LVLx I/O reads are converted to equivalent MWAIT C-state requests inside the processor and do not directly result in I/O reads on the processor FSB. The P\_LVLx I/O monitor address does not need to be set up before using the P\_LVLx I/O read interface. The sub-state hints used for each P\_LVLx read can be configured through the Model Specific Register (MSR).

If a core encounters a chipset break event while STPCLK# is asserted, then it asserts the PBE# output signal. Assertion of PBE# when STPCLK# is asserted indicates to system logic that individual cores should return to the CO state and the processor should return to the Normal state.

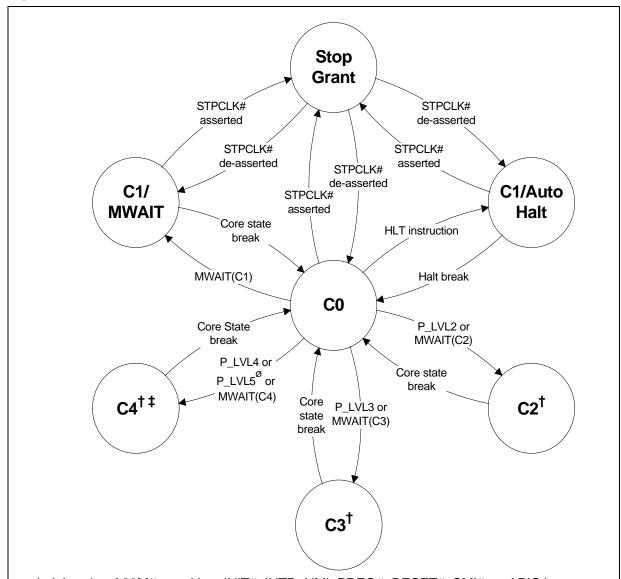

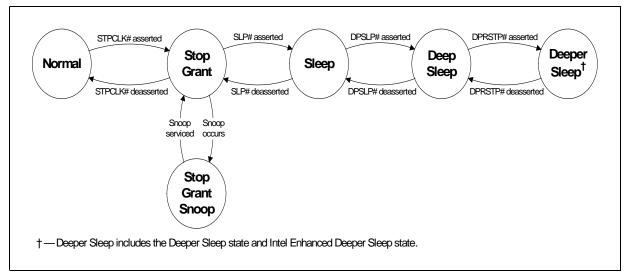

Figure 1 shows the core low power states and Figure 2 shows the package low power states. Table 1 maps the core low power states to the package low power states.

Figure 1. Core Low Power States

halt break = A20M# transition, INIT#, INTR, NMI, PREQ#, RESET#, SMI#, or APIC interrupt core state break = (halt break OR Monitor event) AND STPCLK# high (not asserted)

- † STPCLK# assertion and de-assertion have no effect if a core is in C2, C3, or C4.

- ‡ Core C4 state supports the package level Intel Enhanced Deeper Sleep state

- Ø P LVL5 read is issued once the L2 cache is reduced to zero.

Figure 2. Package Low Power States

Table 1. Coordination of Core Low Power States at the Package Level

| Package State   | Core1 State |                 |            |            |                                                      |  |  |

|-----------------|-------------|-----------------|------------|------------|------------------------------------------------------|--|--|

| CoreO State     | СО          | C1 <sup>1</sup> | C2         | С3         | C4                                                   |  |  |

| CO              | Normal      | Normal          | Normal     | Normal     | Normal                                               |  |  |

| C1 <sup>1</sup> | Normal      | Normal          | Normal     | Normal     | Normal                                               |  |  |

| C2              | Normal      | Normal          | Stop-Grant | Stop Grant | Stop Grant                                           |  |  |

| C3              | Normal      | Normal          | Stop-Grant | Deep Sleep | Deep Sleep                                           |  |  |

| C4              | Normal      | Normal          | Stop-Grant | Deep Sleep | Deeper Sleep<br>/ Intel®<br>Enhanced<br>Deeper Sleep |  |  |

#### NOTES:

1. AutoHALT or MWAIT/C1.

#### 2.1.1 Core Low Power State Descriptions

#### 2.1.1.1 Core CO State

This is the normal operating state for cores in the processor.

#### 2.1.1.2 Core C1/AutoHALT Powerdown State

C1/AutoHALT is a low power state entered when a core executes the HALT instruction. The processor transitions to the C0 state upon occurrence of SMI#, INIT#, LINT[1:0] (NMI, INTR), or FSB interrupt messages. RESET# causes the processor to immediately initialize itself.

A System Management Interrupt (SMI) handler returns execution to either Normal state or the AutoHALT Powerdown state. See the *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A/3B: System Programmer's Guide* for more information.

The system can generate a STPCLK# while the processor is in the AutoHALT Powerdown state. When the system deasserts the STPCLK# interrupt, the processor returns execution to the HALT state.

While in AutoHALT Powerdown state, the dual core processor processes bus snoops and snoops from the other core. The processor enters a snoopable sub-state (not shown in Figure 1) to process the snoop and then return to the AutoHALT Powerdown state.

#### 2.1.1.3 Core C1/MWAIT Powerdown State

C1/MWAIT is a low power state entered when the processor core executes the MWAIT(C1) instruction. Processor behavior in the MWAIT state is identical to the AutoHALT state except that Monitor events can cause the processor core to return to the C0 state. See the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M and Volume 2B: Instruction Set Reference, N-Z, for more information.

#### 2.1.1.4 Core C2 State

Individual cores of the dual core processor can enter the C2 state by initiating a P\_LVL2 I/O read to the P\_BLK or an MWAIT(C2) instruction, but the processor does not issue a Stop-Grant Acknowledge special bus cycle unless the STPCLK# pin is also asserted.

While in the C2 state, the dual core processor processes bus snoops and snoops from the other core. The processor enters a snoopable sub-state (not shown in Figure 1) to process the snoop and then return to the C2 state.

#### 2.1.1.5 Core C3 State

Individual cores of the dual core processor can enter the C3 state by initiating a P\_LVL3 I/O read to the P\_BLK or an MWAIT(C3) instruction. Before entering C3, the processor core flushes the contents of its L1 caches into the processor's L2 cache. Except for the caches, the processor core maintains all its architectural state in the C3 state. The monitor remains armed if it is configured. All of the clocks in the processor core are stopped in the C3 state.

Because the core's caches are flushed the processor keeps the core in the C3 state when the processor detects a snoop on the FSB or when the other core of the dual core processor accesses cacheable memory. The processor core transitions to the C0 state upon occurrence of a Monitor event, SMI#, INIT#, LINT[1:0] (NMI, INTR), or FSB interrupt message. RESET# causes the processor to immediately initialize itself.

#### 2.1.1.6 Core C4 State

Individual cores of the dual core processor can enter the C4 state by initiating a P\_LVL4 I/O read to the P\_BLK or an MWAIT(C4) instruction. The processor core behavior in the C4 state is nearly identical to the behavior in the C3 state. The only difference is that if both processor cores are in C4, then the central power management logic requests that the entire processor enter the Deeper Sleep package low power state (see Section 2.1.2.6).

To enable the package level Intel Enhanced Deeper Sleep state, Dynamic Cache Sizing and Intel Enhanced Deeper Sleep state fields must be configured in the software programmable MSR. Refer to Section 2.1.2.6 for further details on Intel Enhanced Deeper Sleep state.

### 2.1.2 Package Low Power State Descriptions

#### 2.1.2.1 Normal State

This is the normal operating state for the processor. The processor remains in the Normal state when at least one of its cores is in the CO, C1/AutoHALT, or C1/MWAIT state.

#### 2.1.2.2 Stop-Grant State

When the STPCLK# pin is asserted by the chipset, each core of the dual core processor enters the Stop-Grant state within 20-bus clocks after the response phase of the processor-issued Stop-Grant Acknowledge special bus cycle. Processor cores that are already in the C2, C3, or C4 state remain in their current low power state. When the STPCLK# pin is deasserted, each core returns to its previous core low power state.

Since the AGTL+ signal pins receive power from the FSB, these pins should not be driven (allowing the level to return to  $V_{\text{CCP}}$ ) for minimum power drawn by the termination resistors in this state. In addition, all other input pins on the FSB should be driven to the inactive state.

RESET# causes the processor to immediately initialize itself, but the processor stays in Stop-Grant state. When RESET# is asserted by the system, the STPCLK#, SLP#, DPSLP#, and DPRSTP# pins must be deasserted prior to RESET# deassertion. When re-entering the Stop-Grant state from the Sleep state, STPCLK# should be deasserted after the deassertion of SLP#.

While in Stop-Grant state, the processor services snoops and latch interrupts delivered on the FSB. The processor latches SMI#, INIT# and LINT[1:0] interrupts and services only one of each upon return to the Normal state.

The PBE# signal may be driven when the processor is in Stop-Grant state. PBE# asserts if there is any pending interrupt or Monitor event latched within the processor. Pending interrupts that are blocked by the EFLAGS.IF bit being clear causes assertion of PBE#. Assertion of PBE# indicates to system logic that the entire processor should return to the Normal state.

A transition to the Stop-Grant Snoop state occurs when the processor detects a snoop on the FSB (see Section 2.1.2.3). A transition to the Sleep state (see Section 2.1.2.4) occurs with the assertion of the SLP# signal.

#### 2.1.2.3 Stop-Grant Snoop State

The processor responds to snoop or interrupt transactions on the FSB while in Stop-Grant state by entering the Stop-Grant Snoop state. The processor stays in this state until the snoop on the FSB has been serviced (whether by the processor or another agent on the FSB) or the interrupt has been latched. The processor returns to the Stop-Grant state once the snoop has been serviced or the interrupt has been latched.

#### 2.1.2.4 Sleep State

The Sleep state is a low power state in which the processor maintains its context, maintains the phase-locked loop (PLL), and stops all internal clocks. The Sleep state is entered through assertion of the SLP# signal while in the Stop-Grant state. The SLP# pin should only be asserted when the processor is in the Stop-Grant state. SLP# assertions while the processor is not in the Stop-Grant state is out of specification and may result in unapproved operation.

In the Sleep state, the processor is incapable of responding to snoop transactions or latching interrupt signals. No transitions or assertions of signals (with the exception of SLP#, DPSLP# or RESET#) are allowed on the FSB while the processor is in Sleep state. Snoop events that occur while in Sleep state or during a transition into or out of Sleep state causes unpredictable behavior. Any transition on an input signal before the processor has returned to the Stop-Grant state results in unpredictable behavior.

If RESET# is driven active while the processor is in the Sleep state, and held active, then the processor resets itself, ignoring the transition through Stop-Grant state. If RESET# is driven active while the processor is in the Sleep state, the SLP# and STPCLK# signals should be deasserted immediately after RESET# is asserted to ensure the processor correctly executes the Reset sequence.

While in the Sleep state, the processor is capable of entering an even lower power state, the Deep Sleep state, by asserting the DPSLP# pin (See Section 2.1.2.5). While the processor is in the Sleep state, the SLP# pin must be deasserted if another asynchronous FSB event needs to occur.

#### 2.1.2.5 Deep Sleep State

The Deep Sleep state is entered through assertion of the DPSLP# pin while in the Sleep state. BCLK may be stopped during the Deep Sleep state for additional platform-level power savings. BCLK stop/restart timings on appropriate chipset based platforms with the CK505 clock chip are as follows:

- Deep Sleep entry: the system clock chip may stop/tristate BCLK within 2 BCLKs of DPSLP# assertion. It is permissible to leave BCLK running during Deep Sleep.

- Deep Sleep exit: the system clock chip must drive BCLK to differential DC levels within 2-3 ns of DPSLP# deassertion and start toggling BCLK within 10 BCLK periods.

To re-enter the Sleep state, the DPSLP# pin must be deasserted. BCLK can be restarted after DPSLP# deassertion as described above. A period of 15 microseconds (to allow for PLL stabilization) must occur before the processor can be considered to be in the Sleep state. Once in the Sleep state, the SLP# pin must be deasserted to re-enter the Stop-Grant state.

While in Deep Sleep state, the processor is incapable of responding to snoop transactions or latching interrupt signals. No transitions of signals are allowed on the FSB while the processor is in Deep Sleep state. When the processor is in Deep Sleep state, it does not respond to interrupts or snoop transactions. Any transition on an input signal before the processor has returned to Stop-Grant state results in unpredictable behavior.

#### 2.1.2.6 Deeper Sleep State

The Deeper Sleep state is similar to the Deep Sleep state but further reduces core voltage levels. One of the potential lower core voltage levels is achieved by entering the base Deeper Sleep state. The Deeper Sleep state is entered through assertion of the DPRSTP# pin while in the Deep Sleep state. The other lower core voltage level, the lowest possible in the processor, is achieved by entering the Intel Enhanced Deeper Sleep state which is a sub-state of Deeper Sleep state. Intel Enhanced Deeper Sleep state is entered through assertion of the DPRSTP# pin while in the Deep Sleep only when the L2 cache has been completely shut down. Refer to Section 2.1.2.6.1 and Section 2.1.2.6.2 for further details on reducing the L2 cache and entering Intel Enhanced Deeper Sleep state.

In response to entering Deeper Sleep, the processor drives the VID code corresponding to the Deeper Sleep core voltage on the VID[6:0] pins.

Exit from Deeper Sleep or Intel Enhanced Deeper Sleep state is initiated by DPRSTP# deassertion when either core requests a core state other than C4 or either core requests a processor performance state other than the lowest operating point.

#### 2.1.2.6.1 Intel Enhanced Deeper Sleep State

Intel Enhanced Deeper Sleep state is a sub-state of Deeper Sleep that extends power-saving capabilities by allowing the processor to further reduce core voltage once the L2 cache has been reduced to zero ways and completely shut down. The following events occur when the processor enters Intel Enhanced Deeper Sleep state:

- The last core entering C4 causes the package to issue a P\_LVL4 IO Read.

- Every concurrent package C4 entry reduces the L2 Cache a certain number of cache ways, after which another P\_LVL4 IO Read is issued to the chipset. By default, half the cache is flushed per concurrent C4 entry.

- Once the cache is flushed, P LVL4 IO Reads continue to be issued.

- The processor drives the VID code corresponding to the Intel Enhanced Deeper Sleep state core voltage on the VID[6:0] pins.

At this point, snoops to the L2 are still serviced, which reduces the amount of time the processor can reside at the Intel Enhanced Deeper Sleep state core voltage.

To improve the Intel Enhanced Deeper Sleep state residency, the (G)MCH features P\_LVL5 IO Read support. When enabled, the CPU issues a P\_LVL5 IO read, once the L2 cache is flushed. The P\_LVL5 IO read triggers a special chipset sequence to notify the chipset to redirect all FSB traffic, except APIC messages, to memory instead of L2 cache. Therefore, the processor remains at the Intel Enhanced Deeper Sleep state core voltage for a longer period of time.

#### 2.1.2.6.2 Dynamic Cache Sizing

Dynamic Cache Sizing allows the processor to flush and disable a programmable number of L2 cache ways upon each Deeper Sleep entry under the following conditions:

- The second core is already in C4 and the Intel Enhanced Deeper Sleep state is enabled (as specified in Section 2.1.1.6).

- The C0 timer, which tracks continuous residency in the Normal package state, has not expired. This timer is cleared during the first entry into Deeper Sleep to allow consecutive Deeper Sleep entries to shrink the L2 cache as needed.

- The FSB speed to processor core speed ratio is below the predefined L2 shrink threshold.

If the FSB speed to processor core speed ratio is above the predefined L2 shrink threshold, then L2 cache expansion is requested. If the ratio is zero, then the ratio is not taken into account for Dynamic Cache Sizing decisions.

Upon STPCLK# deassertion, the first core exiting Intel Enhanced Deeper Sleep state expands the L2 cache to two ways and invalidate previously disabled cache ways. If the L2 cache reduction conditions stated above still exist when the last core returns to C4 and the package enters Intel Enhanced Deeper Sleep state, then the L2 is shrunk to zero again. If a core requests a processor performance state resulting in a higher ratio than the predefined L2 shrink threshold, the C0 timer expires, or the second core (not the one currently entering the interrupt routine) requests the C1, C2, or C3 states, then all of L2 expands upon the next interrupt event.

L2 cache shrink prevention may be enabled as needed on occasion through an MWAIT(C4) sub-state field. If shrink prevention is enabled the processor does not enter Intel Enhanced Deeper Sleep state because the L2 cache remains valid and in full size.

## 2.2 Enhanced Intel SpeedStep® Technology

The processor features Enhanced Intel SpeedStep Technology. Following are the key features of Enhanced Intel SpeedStep Technology:

- Multiple voltage and frequency operating points provide optimal performance at the lowest power.

- Voltage and frequency selection is software-controlled by writing to processor MSRs:

- If the target frequency is higher than the current frequency, Vcc is ramped up in steps by placing new values on the VID pins, and the PLL then locks to the new frequency.

- If the target frequency is lower than the current frequency, the PLL locks to the new frequency, and the  $V_{CC}$  is changed through the VID pin mechanism.

- Software transitions are accepted at any time. If a previous transition is in progress the new transition is deferred until the previous transition completes.

- The processor controls voltage ramp rates internally to ensure glitch-free transitions.

- Low transition latency and large number of transitions possible per second:

- Processor core (including L2 cache) is unavailable for up to 10 ms during the frequency transition.

- The bus protocol (BNR# mechanism) is used to block snooping.

- Improved Intel® Thermal Monitor mode:

- When the on-die thermal sensor indicates that the die temperature is too high, the processor can automatically perform a transition to a lower frequency and voltage specified in a software-programmable MSR.

- The processor waits for a fixed time period. If the die temperature is down to acceptable levels, an up-transition to the previous frequency and voltage point occurs.

- An interrupt is generated for the up and down Intel Thermal Monitor transitions enabling better system-level thermal management.

- · Enhanced thermal management features:

- Digital Thermal Sensor and Out of Specification detection

- Intel Thermal Monitor 1 in addition to Intel Thermal Monitor 2 in case of unsuccessful Intel Thermal Monitor 2 transition.

- Dual core thermal management synchronization.

Each core in the dual processor implements an independent MSR for controlling Enhanced Intel SpeedStep Technology, but both cores must operate at the same frequency and voltage. The processor has performance state coordination logic to resolve frequency and voltage requests from the two cores into a single frequency and voltage request for the package as a whole. If both cores request the same frequency and voltage, then the processor transitions to the requested common frequency and voltage. If the two cores have different frequency and voltage requests, then the processor takes the highest of the two frequencies and voltages as the resolved request, and transition to that frequency and voltage.

The processor also supports Dynamic FSB Frequency Switching and Intel® Dynamic Acceleration Technology mode on select SKUS. The operating system can take advantage of these features and request a lower operating point called SuperLFM (due to Dynamic FSB Frequency Switching) and a higher operating point Intel Dynamic Acceleration Technology mode.

## 2.2.1 Dynamic FSB Frequency Switching

Dynamic FSB frequency switching effectively reduces the internal bus clock frequency in half to further decrease the minimum processor operating frequency from the Enhanced Intel SpeedStep Technology performance states and achieve the Super Low Frequency Mode (SuperLFM). This feature is supported at FSB frequencies of 800-MHz and does not entail a change in the external bus signal (BCLK) frequency. Instead, both the processor and (G)MCH internally lower their BCLK reference frequency to 50% of the externally visible frequency. Both the processor and (G)MCH maintain a virtual BCLK signal ("VBCLK") that is aligned to the external BCLK but at half the frequency. After a downward shift, it would appear externally as if the bus is running with a 100-MHz base clock in all aspects, except that the actual external BCLK remains at 200 MHz. The transition into SuperLFM, a "down-shift", is done following a handshake between the processor and (G)MCH. A similar handshake is used to indicate an "upshift", a change back to normal operating mode.

#### 2.2.2 Intel® Dynamic Acceleration Technology

The processor supports Intel Dynamic Acceleration Technology mode on select platforms. The Intel Dynamic Acceleration Technology mode feature allows one core of the processor to temporarily operate at a higher frequency point when the other core is inactive and the operating system requests increased performance. This higher frequency is called the opportunistic frequency and the maximum rated operating frequency is the guaranteed frequency.

**Note:** Intel Core 2 Extreme processors do not support Intel Dynamic Acceleration mode.

Intel Dynamic Acceleration Technology mode enabling requires:

- Exposure, via BIOS, of the opportunistic frequency as the highest ACPI P state.

- Enhanced Multi-Threaded Thermal Management (EMTTM).

- Intel Dynamic Acceleration Technology mode and EMTTM MSR configuration via BIOS

When in Intel Dynamic Acceleration Technology mode, it is possible for both cores to be active under certain internal conditions. In such a scenario the processor may draw a Instantaneous current ( $I_{CC\_CORE\_INST}$ ) for a short duration of  $t_{INST}$ ; however, the average  $I_{CC}$  current is lesser than or equal to  $I_{CCDES}$  current specification. Please refer to the Processor DC Specifications section for more details.

#### 2.3 Extended Low Power States

Extended low power states (CxE) optimize for power by forcibly reducing the performance state of the processor when it enters a package low power state. Instead of directly transitioning into the package low power state, the extended package low power state first reduces the performance state of the processor by performing an Enhanced Intel SpeedStep Technology transition down to the lowest operating point. Upon receiving a break event from the package low power state, control returns to the software while an Enhanced Intel SpeedStep Technology transition up to the initial operating point occurs. The advantage of this feature is that it significantly reduces leakage while in low power states.

**Note:** Long-term reliability cannot be assured unless all the Extended Low Power states are enabled.

The processor implements two software interfaces for requesting extended package low power states: MWAIT instruction extensions with sub-state hints and via BIOS by configuring MSR bits to automatically promote package low power states to extended package low power states.

Extended Stop-Grant and Extended Deeper Sleep must be enabled via the BIOS for the processor to remain within specification. Any attempt to operate the processor outside these operating limits may result in permanent damage to the processor. As processor technology changes, enabling the extended low power states becomes increasingly crucial when building computer systems. Maintaining the proper BIOS configuration is key to reliable, long-term system operation. Not complying with this guideline may affect the long-term reliability of the processor.

Enhanced Intel SpeedStep Technology transitions are multistep processes that require clocked control. These transitions cannot occur when the processor is in the Sleep or Deep Sleep package low power states since processor clocks are not active in these states. Extended Deeper Sleep state configuration lowers core voltage to the Deeper Sleep level while in Deeper Sleep and, upon exit, automatically transitions to the lowest operating voltage and frequency to reduce snoop service latency. The transition to the lowest operating point or back to the original software requested point may not be instantaneous. Furthermore, upon very frequent transitions between active and idle states, the transitions may lag behind the idle state entry resulting in the processor either executing for a longer time at the lowest operating point or running idle at a high operating point. Observations and analyses show this behavior should not significantly impact total power savings or performance score while providing power benefits in most other cases.

#### 2.4 FSB Low Power Enhancements

The processor incorporates FSB low power enhancements:

- · Dynamic FSB Power Down

- BPRI# control for address and control input buffers

- · Dynamic Bus Parking

- Dynamic On Die Termination disabling

- Low V<sub>CCP</sub> (I/O termination voltage)

The processor incorporates the DPWR# signal that controls the data bus input buffers on the processor. The DPWR# signal disables the buffers when not used and activates them only when data bus activity occurs, resulting in significant power savings with no performance impact. BPRI# control also allows the processor address and control input buffers to be turned off when the BPRI# signal is inactive. Dynamic Bus Parking allows a reciprocal power reduction in chipset address and control input buffers when the processor deasserts its BRO# pin. The On Die Termination on the processor FSB buffers is disabled when the signals are driven low, resulting in additional power savings. The low I/O termination voltage is on a dedicated voltage plane, independent of the core voltage, enabling low I/O switching power at all times.

#### 2.5 VID-x

The processor implements the VID-x feature when in Intel Dynamic Acceleration Technology mode. VID-x provides the ability for the processor to request core voltage level reductions greater than one VID tick. The quantity of VID ticks to be reduced depends on the specific performance state in which the processor is running. This improved voltage regulator efficiency during periods of reduced power

consumption allows for leakage current reduction, which results in platform power savings and extended battery life. There is no platform-level change required to support this feature as long as the VR vendor supports the VID-x feature.

## 2.6 Processor Power Status Indicator (PSI-2) Signal

The processor incorporates the PSI# signal that is asserted when the processor is in a reduced power consumption state. PSI# can be used to improve intermediate and light load efficiency of the voltage regulator, resulting in platform power savings and extended battery life. The algorithm that the processor uses for determining when to assert PSI# is different from the algorithm used in previous mobile processors. PSI-2 functionality improves overall voltage regulator efficiency over a wide power range based on the C-state and P-state of the two cores. The combined C-state and P-state of both cores are used to dynamically predict processor power. PSI-2 functionality is expanded further to support three processor states:

- · Both cores are in idle state

- · Only one core is in active state

- · Both cores are in active state

§

#### Low Power Features

22

# 3 Electrical Specifications

#### 3.1 Power and Ground Pins

For clean, on-chip power distribution, the processor has a large number of  $V_{CC}$  (power) and  $V_{SS}$  (ground) inputs. All power pins must be connected to  $V_{CC}$  power planes while all  $V_{SS}$  pins must be connected to system ground planes. Use of multiple power and ground planes is recommended to reduce I\*R drop. The processor  $V_{CC}$  pins must be supplied the voltage determined by the VID (Voltage ID) pins.

## 3.2 FSB Clock (BCLK[1:0]) and Processor Clocking

BCLK[1:0] directly controls the FSB interface speed as well as the core frequency of the processor. As in previous generation processors, the processor core frequency is a multiple of the BCLK[1:0] frequency. The processor uses a differential clocking implementation.

## 3.3 Voltage Identification

The processor uses seven voltage identification pins,VID[6:0], to support automatic selection of power supply voltages. The VID pins for processor are CMOS outputs driven by the processor VID circuitry. Table 2 specifies the voltage level corresponding to the state of VID[6:0]. A 1 refers to a high-voltage level and a 0 refers to low-voltage level.

#### Table 2. Voltage Identification Definition (Sheet 1 of 4)

| VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VIDO | V <sub>CC</sub> (V) |

|------|------|------|------|------|------|------|---------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1.5000              |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1.4875              |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1.4750              |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1.4625              |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1.4500              |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1.4375              |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1.4250              |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1.4125              |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1.4000              |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1.3875              |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1.3750              |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1.3625              |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1.3500              |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1.3375              |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1.3250              |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1.3125              |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 1.3000              |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1.2875              |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1.2750              |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1.2625              |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1.2500              |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1.2375              |

Table 2. Voltage Identification Definition (Sheet 2 of 4)

| VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VIDO | V <sub>CC</sub> (V) |

|------|------|------|------|------|------|------|---------------------|

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 1.2250              |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1.2125              |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1.2000              |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1.1875              |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1.1750              |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1.1625              |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1.1500              |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1.1375              |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1.1250              |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1.1125              |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1.1000              |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1.0875              |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1.0750              |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1.0625              |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1.0500              |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1.0375              |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1.0250              |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1.0125              |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1.0000              |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0.9875              |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0.9750              |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0.9625              |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0.9500              |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0.9375              |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0.9250              |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0.9125              |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0.9000              |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0.8875              |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0.8750              |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0.8625              |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0.8500              |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0.8375              |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0.8250              |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 0.8125              |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0.8000              |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0.7875              |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0.7750              |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0.7625              |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0.7500              |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0.7375              |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0.7250              |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 0.7125              |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0.7000              |

| 1    | 0    | 0    | 0    | 0    | 0    | 1    | 0.6875              |

| 1    | 0    | 0    | 0    | 0    | 1    | 0    | 0.6750              |

| 1    | 0    | 0    | 0    | 0    | 1    | 1    | 0.6625              |

| 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0.6500              |

Table 2. Voltage Identification Definition (Sheet 3 of 4)

| VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VIDO | V <sub>CC</sub> (V) |

|------|------|------|------|------|------|------|---------------------|

| 1    | 0    | 0    | 0    | 1    | 0    | 1    | 0.6375              |

| 1    | 0    | 0    | 0    | 1    | 1    | 0    | 0.6250              |

| 1    | 0    | 0    | 0    | 1    | 1    | 1    | 0.6125              |

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0.6000              |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 0.5875              |

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 0.5750              |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 0.5625              |

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0.5500              |

| 1    | 0    | 0    | 1    | 1    | 0    | 1    | 0.5375              |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 0.5250              |

| 1    | 0    | 0    | 1    | 1    | 1    | 1    | 0.5125              |

| 1    | 0    | 1    | 0    | 0    | 0    | 0    | 0.5000              |

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 0.4875              |

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 0.4750              |

| 1    | 0    | 1    | 0    | 0    | 1    | 1    | 0.4625              |

| 1    | 0    | 1    | 0    | 1    | 0    | 0    | 0.4500              |

| 1    | 0    | 1    | 0    | 1    | 0    | 1    | 0.4375              |

| 1    | 0    | 1    | 0    | 1    | 1    | 0    | 0.4250              |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 0.4125              |

| 1    | 0    | 1    | 1    | 0    | 0    | 0    | 0.4000              |

| 1    | 0    | 1    | 1    | 0    | 0    | 1    | 0.3875              |

| 1    | 0    | 1    | 1    | 0    | 1    | 0    | 0.3750              |

| 1    | 0    | 1    | 1    | 0    | 1    | 1    | 0.3625              |

| 1    | 0    | 1    | 1    | 1    | 0    | 0    | 0.3500              |

| 1    | 0    | 1    | 1    | 1    | 0    | 1    | 0.3375              |

| 1    | 0    | 1    | 1    | 1    | 1    | 0    | 0.3250              |

| 1    | 0    | 1    | 1    | 1    | 1    | 1    | 0.3125              |

| 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0.3000              |

| 1    | 1    | 0    | 0    | 0    | 0    | 1    | 0.2875              |

| 1    | 1    | 0    | 0    | 0    | 1    | 0    | 0.2750              |

| 1    | 1    | 0    | 0    | 0    | 1    | 1    | 0.2625              |

| 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0.2500              |

| 1    | 1    | 0    | 0    | 1    | 0    | 1    | 0.2375              |

| 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0.2250              |

| 1    | 1    | 0    | 0    | 1    | 1    | 1    | 0.2125              |

| 1    | 1    | 0    | 1    | 0    | 0    | 0    | 0.2000              |

| 1    | 1    | 0    | 1    | 0    | 0    | 1    | 0.1875              |

| 1    | 1    | 0    | 1    | 0    | 1    | 0    | 0.1750              |

| 1    | 1    | 0    | 1    | 0    | 1    | 1    | 0.1625              |

| 1    | 1    | 0    | 1    | 1    | 0    | 0    | 0.1500              |

| 1    | 1    | 0    | 1    | 1    | 0    | 1    | 0.1375              |

| 1    | 1    | 0    | 1    | 1    | 1    | 0    | 0.1250              |

| 1    | 1    | 0    | 1    | 1    | 1    | 1    | 0.1125              |

| 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0.1000              |

| 1    | 1    | 1    | 0    | 0    | 0    | 1    | 0.0875              |

| 1    | 1    | 1    | 0    | 0    | 1    | 0    | 0.0750              |

| 1    | 1    | 1    | 0    | 0    | 1    | 1    | 0.0625              |

#### Table 2. Voltage Identification Definition (Sheet 4 of 4)

| VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VIDO | V <sub>CC</sub> (V) |

|------|------|------|------|------|------|------|---------------------|

| 1    | 1    | 1    | 0    | 1    | 0    | 0    | 0.0500              |

| 1    | 1    | 1    | 0    | 1    | 0    | 1    | 0.0375              |

| 1    | 1    | 1    | 0    | 1    | 1    | 0    | 0.0250              |

| 1    | 1    | 1    | 0    | 1    | 1    | 1    | 0.0125              |

| 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0.0000              |

| 1    | 1    | 1    | 1    | 0    | 0    | 1    | 0.0000              |

| 1    | 1    | 1    | 1    | 0    | 1    | 0    | 0.0000              |

| 1    | 1    | 1    | 1    | 0    | 1    | 1    | 0.0000              |

| 1    | 1    | 1    | 1    | 1    | 0    | 0    | 0.0000              |

| 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0.0000              |

| 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0.0000              |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0.0000              |

## 3.4 Catastrophic Thermal Protection

The processor supports the THERMTRIP# signal for catastrophic thermal protection. An external thermal sensor should also be used to protect the processor and the system against excessive temperatures. Even with the activation of THERMTRIP#, which halts all processor internal clocks and activity, leakage current can be high enough that the processor cannot be protected in all conditions without power removal to the processor. If the external thermal sensor detects a catastrophic processor temperature of  $125\,^{\circ}\text{C}$  (maximum), or if the THERMTRIP# signal is asserted, the  $V_{CC}$  supply to the processor must be turned off within 500 ms to prevent permanent silicon damage due to thermal runaway of the processor. THERMTRIP# functionality is not guaranteed if the PWRGOOD signal is not asserted.

#### 3.5 Reserved and Unused Pins

All RESERVED (RSVD) pins must remain unconnected. Connection of these pins to  $V_{CC}$ ,  $V_{SS}$ , or to any other signal (including each other) may result in component malfunction or incompatibility with future processors. See Section 4.2 for a pin listing of the processor and the location of all RSVD pins.

For reliable operation, always connect unused inputs or bidirectional signals to an appropriate signal level. Unused active low AGTL+ inputs may be left as no connects if AGTL+ termination is provided on the processor silicon. Unused active high inputs should be connected through a resistor to ground  $(V_{SS})$ . Unused outputs can be left unconnected.

The TEST1 and TEST2 pins must have a stuffing option of separate pull-down resistors to  $V_{\text{SS}}$ .

For the purpose of testability, route the TEST3 and TEST5 signals through a ground-referenced  $Zo=55-\Omega$  trace that ends in a via that is near a GND via and is accessible through an oscilloscope connection.

## 3.6 FSB Frequency Select Signals (BSEL[2:0])

The BSEL[2:0] signals are used to select the frequency of the processor input clock (BCLK[1:0]). These signals should be connected to the clock chip and the appropriate chipset on the platform. The BSEL encoding for BCLK[1:0] is shown in Table 3.

#### Table 3. BSEL[2:0] Encoding for BCLK Frequency

| BSEL[2] | BSEL[1] | BSEL[0] | BCLK Frequency |

|---------|---------|---------|----------------|

| L       | L       | L       | RESERVED       |

| L       | L       | Н       | 133 MHz        |

| L       | Н       | Н       | RESERVED       |

| L       | Н       | L       | 200 MHz        |

| Н       | Н       | L       | RESERVED       |

| Н       | Н       | Н       | RESERVED       |

| Н       | L       | Н       | RESERVED       |

| Н       | L       | L       | RESERVED       |

## 3.7 FSB Signal Groups

The FSB signals have been combined into groups by buffer type in the following sections. AGTL+ input signals have differential input buffers, which use GTLREF as a reference level. In this document, the term "AGTL+ Input" refers to the AGTL+ input group as well as the AGTL+ I/O group when receiving. Similarly, "AGTL+ Output" refers to the AGTL+ output group as well as the AGTL+ I/O group when driving.

With the implementation of a source synchronous data bus, two sets of timing parameters need to be specified. One set is for common clock signals, which are dependent upon the rising edge of BCLKO (ADS#, HIT#, HITM#, etc.) and the second set is for the source synchronous signals, which are relative to their respective strobe lines (data and address) as well as the rising edge of BCLKO. Asychronous signals are still present (A20M#, IGNNE#, etc.) and can become active at any time during the clock cycle. Table 4 identifies which signals are common clock, source synchronous, and asynchronous.

Table 4. FSB Pin Groups

| Signal Group                 | Туре                         | Signals <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| AGTL+ Common Clock Input     | Synchronous to BCLK[1:0]     | BPRI#, DEFER#, PREQ# <sup>5</sup> , RESET#, RS[2:0]#, TRDY#                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |