# intel®

# Intel<sup>®</sup> IXDPG425 Gateway Reference Platform

**User's Guide**

November 2004

Document Number: 303146-002

# intel®

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> IXDPG425 Network Gateway Reference Platform may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's Web site at http://www.intel.com.

BunnyPeople, Celeron, Chips, Dialogic, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantlP, Intel, Intel Centrino, Intel Centrino logo, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Xeon, Intel XScale, IPLink, Itanium, MCS, MMX logo, Optimizer logo, OverDrive, Paragon, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, Sound Mark, The Computer Inside, The Journey Inside, VTune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation, 2004

# int<sub>e</sub>l<sub>®</sub> Contents

| 1.0 | Introd                                                                                                                      | luction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                                                                                    |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

|     | 1.1<br>1.2<br>1.3<br>1.4<br>1.5                                                                                             | Purpose<br>Intended Audience<br>Related Information<br>Acronyms and Terminology<br>Signal Naming Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5<br>5<br>6                                                                                          |

| 2.0 |                                                                                                                             | IXDPG425 Network Gateway<br>ence Platform Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                                                                                                    |

|     | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12<br>2.13<br>2.14<br>2.15<br>2.16<br>2.17 | Intel <sup>®</sup> IXP425 Network Processor<br>Memory Map<br>SDRAM Memory<br>Expansion Bus<br>2.4.1 Devices on the Expansion Bus<br>2.4.2 Configuration Straps<br>Flash / Boot ROM<br>ADSL WAN Port<br>PCI Interface<br>Ethernet Interfaces — Four-Port LAN, One-Port WAN<br>Voice Ports<br>USB Ports<br>Console Serial Port<br>JTAG Emulator Interface<br>Front-Panel Indicator LEDs<br>Platform-Reset Circuitry<br>2.14.1 Erase Button<br>General-Purpose I/O<br>Power Supplies, Regulators<br>Intel <sup>®</sup> IXDPG425 Network Gateway<br>Reference Platform Hardware Design Kit | $\begin{array}{c} 10\\ 12\\ 14\\ 14\\ 15\\ 16\\ 18\\ 20\\ 22\\ 23\\ 24\\ 25\\ 25\\ 25\\ \end{array}$ |

| 3.0 |                                                                                                                             | lation and Configuration<br>riew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                      |

|     | 3.1<br>3.2<br>3.3                                                                                                           | Installing and Configuring the Hardware<br>Verifying RedBoot* Operation<br>Download Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27                                                                                                   |

|     |                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                      |

# Figures

| 1  | Intel® IXDPG425 Network Gateway Reference Platform Block Diagram | 9  |

|----|------------------------------------------------------------------|----|

| 2  | Intel® IXDPG425 Network Gateway Reference Platform Photograph    |    |

|    | Intel® IXP425 Network Processor High-Level Block Diagram         |    |

|    | Software Implementation of Ethernet Bridging and Router Modes    |    |

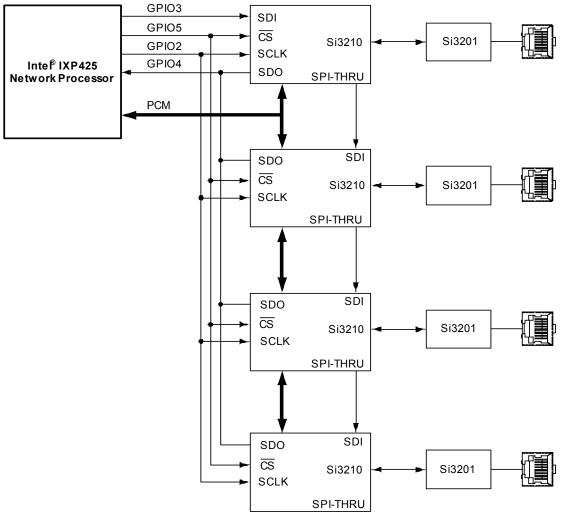

| 5  | Four Voice Ports (Two Shown)                                     | 21 |

| ah |                                                                  |    |

# **Tables**

| 1  | Related Documents                                              | 5   |

|----|----------------------------------------------------------------|-----|

| 2  | Signal Naming Conventions                                      | 7   |

| 3  | Intel <sup>®</sup> IXP425 Network Processor Memory Map         | .12 |

| 4  | Chip Selects For Devices Connected to Expansion Bus            |     |

| 5  | Intel <sup>®</sup> IXDPG425 Network Gateway Reference Platform |     |

|    | Configuration Strappings                                       | 15  |

| 6  | CON 7 ADSL Mezzanine Board Connector                           | .17 |

| 7  | PCI Reset ID Select and Interrupt Assignments                  | .18 |

| 8  | Voice Ports                                                    | 20  |

| 9  | Serial Port, CON 4, 10-Pin, Dual-Row Header                    | 22  |

| 10 | JTAG Interface Connector Signals                               | .23 |

| 11 | Intel® IXDPG425 Network Gateway Reference Platform LEDs        | .24 |

| 12 | GPIO Pin Assignments                                           |     |

# **Revision History**

| Date          | Revision | Description                                                                                                                                                                                                                              |  |  |

|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| November 2004 | 002      | Added caution statement to Section 2.0, replaced Table 3, slightly modified Section 2.3, changed TRST_N "Connect to:" entry in Table 10, and added notes regarding RedHat* version to Section 3.0. Change bars indicate areas of change. |  |  |

| October 2004  | 001      | Initial release.                                                                                                                                                                                                                         |  |  |

intel®

# 1.0 Introduction

### 1.1 Purpose

This document provides an overview of the Intel<sup>®</sup> IXDPG425 Network Gateway Reference Platform, which is based on the Intel<sup>®</sup> IXP425 Network Processor. This document outlines procedures for demonstrating the typical functionality of a residential gateway.

The IXDPG425 network gateway reference platform comprises a set of building blocks and provides the functionality needed for a typical residential gateway. The platform features an IXP425 network processor, SDRAM memory, flash, a four-port Ethernet switch for LAN, an additional Ethernet port for WAN, four telephone line interfaces, a miniPCI interface to connect to a 802.11 WLAN, an ADSL mezzanine card interface, two USB 2.0 host ports, plus power-regulator devices.

The IXDPG425 is designed to be a turn-key solution so that original-equipment manufacturers can adopt the platform's design, select/deselect features, and quickly develop a desired solution. The platform also demonstrates the IXP425 network processor's scalability and processing power — delivered by an Intel XScale<sup>®</sup> Core and network processing engines (NPEs) — in supporting residential-gateway applications.

#### 1.2 Intended Audience

This document is intended for residential-gateway architects and developers evaluating the performance, functions, or basic applications of the IXP425 network processor and IXDPG425.

This user's guide does not explore the entire architecture of the IXDPG425 nor the details on the various components that are used. Instead, it briefly discusses the platform's interfaces used to achieve desired functionality.

### 1.3 Related Information

#### Table 1. Related Documents

| Document Title                                                                                                                 | Document Number/<br>URL <sup>a</sup> |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Intel <sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane<br>Processor Developer's Manual         | 252480                               |

| Intel <sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane<br>Processor Hardware Design Guidelines | 252817                               |

| Intel <sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane<br>Processor Datasheet                  | 252479                               |

#### Table 1. Related Documents (Continued)

| Intel <sup>®</sup> IXP400 Digital Signal Processing (DSP) Software Documentation | http://www.intel.com/<br>design/network/<br>products/npfamily/<br>docs/ixp4xx.htm#                               |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 3-Volt Intel StrataFlash <sup>®</sup> Memory Datasheet                           | 290667                                                                                                           |

| Intel <sup>®</sup> PRO/100+ Adapter Technical Specifications                     | http://www.intel.com/<br>network/connectivity/<br>resources/<br>doc_library/<br>tech_specs/<br>pro100_dsktop.htm |

a. For Intel<sup>®</sup> IXP42X product line documentation, see http://www.intel.com/design/network/products/npfamily/docs/ ixp4xx.htm#.

# 1.4 Acronyms and Terminology

| ADSL                     | Asymmetric Digital Subscriber Line          |

|--------------------------|---------------------------------------------|

| AP                       | Access Point                                |

| ATM                      | Asynchronous Transfer Mode                  |

| CFI                      | Common Flash Interface                      |

| CPE                      | Customer-Premises Equipment                 |

| CS                       | Chip Select                                 |

| DHCP                     | Dynamic Host Configuration Protocol         |

| DNP                      | Do Not Populate                             |

| DSP                      | Digital Signal Processor                    |

| DTMF                     | Dual Tone Multi-Frequency                   |

| GPIO                     | General-Purpose Input/Output                |

| HPI                      | Host-Port Interface                         |

| HSS                      | High-Speed Serial                           |

| IXP425 network processor | Intel <sup>®</sup> IXP425 Network Processor |

| JTAG                     | Joint Test Access Group                     |

| LAN                      | Local Area Network                          |

| LED                      | Light-Emitting Diode                        |

| MII                      | Media-Independent Interface                 |

| NPE                      | Network Processor Engine                    |

| PCA                      | Printed Circuit Assembly                    |

| PCI                      | Peripheral Component Interconnect           |

| PCM                      | Pulse Code Modulation                       |

|                          |                                             |

#### Introduction

# intel®

| РНҮ    | Physical layer                                           |

|--------|----------------------------------------------------------|

| ROM    | Read-Only Memory                                         |

| SDRAM  | Synchronous Dynamic Random Access Memory                 |

| SLIC   | Subscriber Line Interface Circuit                        |

| SPI    | Serial Peripheral Interface                              |

| ТСК    | Test Clock                                               |

| TDI    | Test Data In                                             |

| TDO    | Test Data Out                                            |

| TFTP   | Trivial File Transfer Protocol                           |

| TMS    | Test-Mode Strobe                                         |

| TP     | Test Point                                               |

| UART   | Universal Asynchronous Receiver Transceiver              |

| USB    | Universal Serial Bus                                     |

| UTOPIA | Universal Test and Operations Physical Interface for ATM |

| WAN    | Wide-Area Network                                        |

| WLAN   | Wireless LAN                                             |

| WiFi   | Wireless Fidelity                                        |

| WEP    | Wired Equivalent Privacy                                 |

# 1.5 Signal Naming Conventions

Table 2 shows the conventions used to identify and classify signal names:

#### Table 2.Signal Naming Conventions

| Convention                      | Description                                           |  |  |

|---------------------------------|-------------------------------------------------------|--|--|

| _N                              | (Placed after a signal name) The signal is active-low |  |  |

| I Pin is input-only             |                                                       |  |  |

| 0                               | Pin is output-only                                    |  |  |

| I/O                             | Pin is bidirectional                                  |  |  |

| Z                               | Tri-state                                             |  |  |

| TTL Transistor-Transistor Logic |                                                       |  |  |

| OD                              | Open drain pin                                        |  |  |

| U                               | Resistor is a pull-up resistor                        |  |  |

| D                               | Resistor is a pull-down resistor                      |  |  |

| h                               | (after numerals) Hexadecimal value (example: 2F8000h) |  |  |

#### Table 2.Signal Naming Conventions

| Convention  | Description                                                |  |  |

|-------------|------------------------------------------------------------|--|--|

| b           | (Behind numerals) Binary value (example: 010110b)          |  |  |

| _DNP        | (In a schematic) A component that should not be populated. |  |  |

| GND_DIGITAL | Ground plane for the base-card I/O card                    |  |  |

| TP          | Test points.                                               |  |  |

| #           | The signal name preceding the "#" character is negated     |  |  |

# 2.0 Intel<sup>®</sup> IXDPG425 Network Gateway Reference Platform Overview

The IXDPG425 has all the components of a residential gateway, including the interface for LAN, WAN, and telephone. The 802.11 WLAN connectivity is implemented by an OEM-supplied miniPCI card.

The IXDPG425 consists of:

- Intel<sup>®</sup> IXP425 Network Processor

- SDRAM (32 Mbyte) 48LC8M16A2 (x2)

- One flash memory (16 Mbyte) E28F128J3x-150 (provision for second flash device)

- Five-port Ethernet switch with four-port LAN and a one-port WAN the Realtek\* RTL8305SB-VD

- UTOPIA ADSL mezzanine board interface

- Four-voice-port interface Silicon Labs\* 3201KS (x4); 3210KT (x4)

*Caution:* The IXDPG425 cannot be directly or indirectly connected to any telecommunication network. Telephones to be connected must be within the same building.

- One miniPCI connector for 802.11 WLAN (plus available option of a second connector on the rear of the PCA)

- One serial port

- Two high-speed USB 2.0 host ports

- One USB 1.1 device port

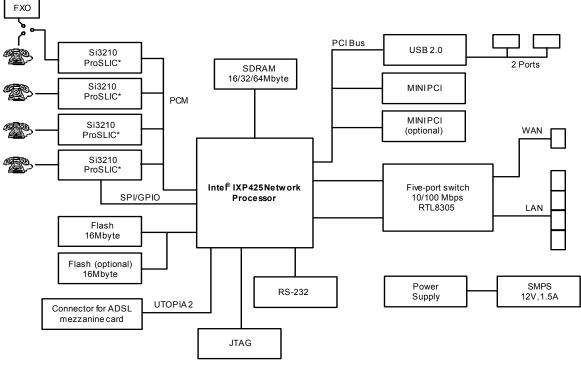

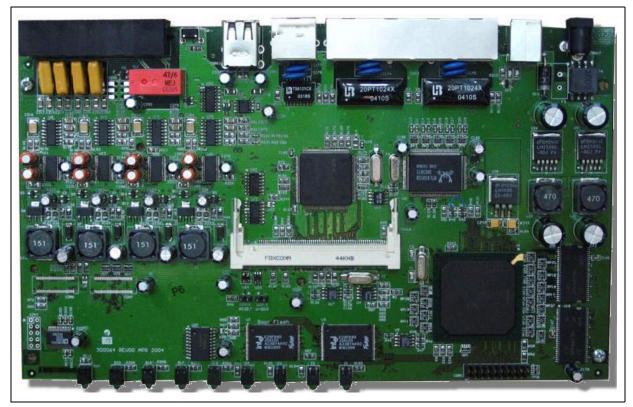

Figure 1 provides a basic block diagram of the platform and its connections for external devices. Figure 2 presents a photograph showing the external-device connections.

# intel

#### Figure 1. Intel<sup>®</sup> IXDPG425 Network Gateway Reference Platform Block Diagram

Revision 001

#### Figure 2. Intel<sup>®</sup> IXDPG425 Network Gateway Reference Platform Photograph

# 2.1 Intel<sup>®</sup> IXP425 Network Processor

The IXP425 network processor can operate at clock speeds of 266, 400, or 533 MHz. The IXDPG425 is the reference platform for the IXP425 network processor. An external 33.33-MHz crystal acts as the input clock signal for the IXP425 network processor.

The IXP425 network processor's primary features include:

- Intel XScale® Core running the system clock rate of 133 MHz at ratios of x2, x3, and x4

- Three NPEs for Layer-2 packet/frame network processing

- Two 10/100-Mbps, full-duplex IEEE-802.3 MAC with MII interface

- Dedicated SDRAM with 32-bit memory interface operating at 133 MHz (equal to system-clock frequency)

- Supports up to two banks each with two chips of two- and three-cycle CAS latency

- 13-bit address maximum: 256 Mbyte; minimum: 8 Mbyte.

- Expansion Bus

- 24-bit address

- 16-bit data

- Eight chip selects

# intel

- Glueless interface to Intel flash and Motorola\*- and Intel-mode peripherals

- DSP support for:

- Texas Instruments\* DSPs supporting HPI-8 bus cycles

- Texas Instruments\* DSPs supporting HPI-16 bus cycles

- UTOPIA-2 interface, 8-bit data path

- Two high-speed, serial TDM buses: HSS-0 and HSS-1

- Two UARTs, each supporting 921 Kbaud

- PCI 2.2 bus

- 32-bit address/data bus

- 33 and 66 MHz

- Built-in arbiter supports up to four external bus masters

- 16 GPIOs

- USB 1.1 device controller supporting full-speed, USB v1.1 data rate

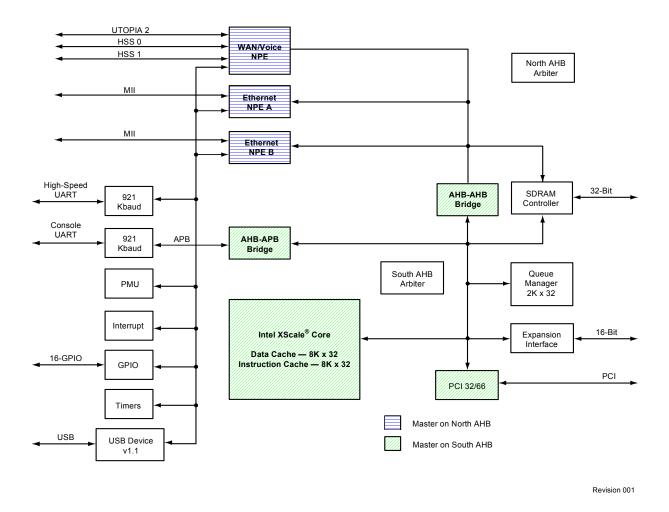

The high-level view of the IXP425 network processor is shown in Figure 3. The internal bus is partitioned into three segments and data transactions between the network processing elements SDRAM and CPU may be performed concurrently. The SDRAM controller can support fast SDRAMs with different memory sizes and bank organizations.

#### Figure 3. Intel<sup>®</sup> IXP425 Network Processor High-Level Block Diagram

### 2.2 Memory Map

The IXP425 network processor implements a single address map used for all internal memory and register space. The complete address space consists of  $2^{32}$ -byte, addressable locations.

#### Table 3. Intel<sup>®</sup> IXP425 Network Processor Memory Map (Sheet 1 of 2)

| Start Address | End Address | Size   | Description                     |

|---------------|-------------|--------|---------------------------------|

| 0000_0000     | OFFF_FFFF   | 256 MB | Expansion Bus Data <sup>†</sup> |

| 0000_0000     | 2FFF_FFFF   | 756 MB | SDRAM Data <sup>†</sup>         |

| 3000_0000     | 3FFF_FFFF   | 256 MB | (Reserved)                      |

| 4000_0000     | 47FF_FFFF   | 128 MB | (Reserved)                      |

# Int

| Table 3. | Intel <sup>®</sup> IXP425 Network Processor Memory Map (Sheet 2 of 2) |             |          |                                                                                |  |

|----------|-----------------------------------------------------------------------|-------------|----------|--------------------------------------------------------------------------------|--|

|          | Start Address                                                         | End Address | Size     | Description                                                                    |  |

| 1        | 4800_0000                                                             | 4FFF_FFFF   | 128 MB   | PCI Data                                                                       |  |

| 1        | 5000_0000                                                             | 5FFF_FFFF   | 256 MB   | Expansion Bus Data                                                             |  |

| 1        | 6000_0000                                                             | 63FF_FFFF   | 64 MB    | Queue manager                                                                  |  |

| T        | 6400_0000                                                             | BFFF_FFFF   |          | (Reserved)                                                                     |  |

| 1        | C000_0000                                                             | C3FF_FFFF   | 64 MB    | PCI Controller Configuration and Status Registers                              |  |

| T        | C400_0000                                                             | C7FF_FFFF   | 64 MB    | Expansion Bus Configuration Registers                                          |  |

| T        | C800_0000                                                             | C800_0FFF   | 1 KB     | High-Speed UART                                                                |  |

| T        | C800_1000                                                             | C800_1FFF   | 1 KB     | Console UART                                                                   |  |

| T        | C800_2000                                                             | C800_2FFF   | 1 KB     | Internal Bus Performance Monitoring Unit                                       |  |

| T        | C800_3000                                                             | C800_3FFF   | 1 KB     | Interrupt Controller                                                           |  |

| T        | C800_4000                                                             | C800_4FFF   | 1 KB     | GPIO Controller                                                                |  |

| T        | C800_5000                                                             | C800_5FFF   | 1 KB     | Timers                                                                         |  |

|          | C800_6000                                                             | C800_6FFF   | 1 KB     | WAN/Voice NPE = NPE-A (IXP400 software<br>Definition)– Not User Programmable   |  |

|          | C800_7000                                                             | C800_7FFF   | 1 KB     | Ethernet NPE A = NPE-B (IXP400 software<br>Definition) – Not User Programmable |  |

|          | C800_8000                                                             | C800_8FFF   | 1 KB     | Ethernet NPE B = NPE-C (IXP400 software<br>Definition) – Not User Programmable |  |

| 1        | C800_9000                                                             | C800_9FFF   | 1 KB     | Ethernet MAC A                                                                 |  |

| 1        | C800_A000                                                             | C800_AFFF   | 1 KB     | Ethernet MAC B                                                                 |  |

| 1        | C800_B000                                                             | C800_BFFF   | 1 KB     | USB Controller                                                                 |  |

| 1        | C800_C000                                                             | C800_FFFF   |          | (Reserved)                                                                     |  |

| 1        | C801_0000                                                             | CBFF_FFFF   |          | (Reserved)                                                                     |  |

| 1        | CC00_0000                                                             | CC00_00FF   | 256 Byte | SDRAM Configuration Registers                                                  |  |

| T        | CC00_0100                                                             | FFFF_FFFF   |          | (Reserved)                                                                     |  |

† The lowest 256 MB of address space is configurable based on the value of a configuration register located in the Expansion Bus Controller.

• When the configuration register is set to logic 1, the Expansion Bus occupies the lowest 256 MB of address space.

• When the configuration register is set to logic 0 the SDRAM occupies the lowest 256 MB of address. In both cases, the SDRAM occupies the 768 MB immediately following the lowest 256 MB and the Expansion Bus can be accessed starting at address 5000 0000.

The largest SDRAM memory size supported by the Intel<sup>®</sup> IXP42X product line and IXC1100 control plane processors is 256 MB. The actual memory implemented in any given configuration will be aliased (repeated) to fill the 1 GB SDRAM address space. Due to aliasing, all of the SDRAM will be accessible even when the Expansion Bus occupies the lowest 256 MB of address space. On reset, the configuration register in the Expansion Bus will be set to logic 1. This setting is required because the dedicated boot memory is flash memory located on the Expansion Bus.

### 2.3 SDRAM Memory

The IXP425 network processor supports PC-133-compatible SDRAM only for both 16-bit-wide and 32-bit-wide devices. The banks are accessed 32 bits at a time. The IXDPG425 supports 32 Mbyte, using two chips each of 2M x 16 x 4 banks internal configuration.

The SDRAM controller is optimized for handling 8-word bursts from the SDRAM. The SDRAM controller throttles the data throughput by controlling the CKE pin of the SDRAM and the Wait signal of internal bus.

Byte-handling is performed — only for write operations to the SDRAM — by controlling the DQM pins of the SDRAM. All read operations are performed by reading the complete bus width of data.

The SDRAM controller has a policy to keep up to eight pages open simultaneously (four per SDRAM bank). If a request is received for an open page, the row access (RAS) address cycle is not performed. If the requested page is not currently open, the SDRAM controller first closes the currently open page in that bank, then opens the new page.

### 2.4 Expansion Bus

The expansion bus in the IXP425 network processor has 16-bit data and 24-bit address for each of its eight independent chip selects. This allows an addressing range of 512 byte to 16 Mbyte and connection of up to eight independent, external devices.

#### 2.4.1 Devices on the Expansion Bus

Table 4 shows the chip selects of IXDPG425 devices that are connected to the expansion bus.

#### Table 4. Chip Selects For Devices Connected to Expansion Bus

| Chip Select | Assignment               |  |  |

|-------------|--------------------------|--|--|

| CS0         | Flash 0 (Boot device)    |  |  |

| CS1         | Flash 1 (Optional Flash) |  |  |

| CS2         | Front Panel LED Latch    |  |  |

| CS3         | Not used                 |  |  |

| CS4         | ADSL CTRLE Interface     |  |  |

| CS5         | Not used                 |  |  |

| CS6         | Not used                 |  |  |

| CS7         | Not used                 |  |  |

On the IXDPG425, GPIO 15 provides a programmable CLK output (CLK\_GPIO15) to the expansion bus clock input (EXP\_CLK) — at speeds of up to 33 MHz — through a clock driver. This same clock signal is used by the UTOPIA interface.

#### 2.4.2 Configuration Straps

The expansion bus address lines (EXP\_A [23:0]) are used for configuration strapping options during boot-up or whenever the reset is de-asserted. At the first cycle after the de-assertion of reset, the values on these lines are read (the expansion bus address outputs are switched to inputs) to determine the configuration of the IXDPG425 and its plug-in cards.

These values are stored in Configuration Register 0, bit [23:0]. All defined configuration strappings are shown in Table 5.

For more information about Configuration Register 0, see the Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Developer's Manual.

# Table 5.Intel<sup>®</sup> IXDPG425 Network Gateway Reference Platform<br/>Configuration Strappings

| Bit   | Name                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23:21 | Intel XScale <sup>®</sup><br>Core Clock<br>Set[2:0] | Processor speed select<br>23, 22, 21 = Processor frequency core speed selected. The IXDPG425 is fitted with<br>a 533-MHz IXP425. The core speed may be regulated by fitting pull-down resistors<br>on Expansion address lines 23:21.<br>1 0 0 = 533 MHz<br>0 0 1 = 400 MHz<br>0 1 1 = 266 MHz<br>The pull-down resistors will be included in the schematics, allowing test and debug<br>at different speeds, though not assembled on the platform. |

| 20:17 | _                                                   | (Not currently used.)                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16:5  |                                                     | (Reserved)                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4     | PCI_CLK                                             | Clock speed of the PCI Interface<br>0 = 33 MHz (IXDPG425 setting)<br>1 = 66 MHz                                                                                                                                                                                                                                                                                                                                                                    |

| 3     | —                                                   | (Reserved)                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2     | PCI_ARB                                             | Enables the PCI Arbiter<br>0 = PCI arbiter disabled<br>1 = PCI arbiter enabled (IXDPG425 setting)                                                                                                                                                                                                                                                                                                                                                  |

| 1     | PCI_HOST                                            | Configures the IXP425 network processor as PCI Bus Host<br>0 = IXP425 network processor as non-host<br>1 = IXP425 network processor as host (IXDPG425 setting)                                                                                                                                                                                                                                                                                     |

| 0     | 8/16 flash                                          | Specifies the data bus width of the flash memory device<br>0 = 16-bit data bus (IXDPG425 setting)<br>1 = 8-bit data bus                                                                                                                                                                                                                                                                                                                            |

### 2.5 Flash / Boot ROM

The boot ROM for the IXDPG425 is the Intel StrataFlash<sup>®</sup> E28F128J3x-150 16-Mbyte memory connected through the expansion bus. The flash is organized as 16 Mbytes (or 8 Mwords by 16 bits) or 128 128-Kbyte (131,072 bytes) erase blocks. The E28F128J3x supports the common flash interface (CFI).

For more information about the E28F128J3x Intel StrataFlash Memory, see the 3-Volt Intel StrataFlash<sup>®</sup> Memory Datasheet.

There are two flash devices on the IXDPG425: Flash 0, which is the Boot flash; and Flash 1, which is not currently used. The IXDPG425 may only boot from the Flash 0 device. The designer needs to be sure to program the CS1 output before any attempt is made to access the Flash 1 address space.

The size of the data transfer (8- or 16-bit) is set on the board using the expansion-bus address 0 strapping jumper. The EXP\_A0 strap is set to 0 at the de-assertion of reset to select 16-bit data bus. The FLASH\_STS pin on the flash is unused on the IXP425 network processor.

### 2.6 ADSL WAN Port

The main features of the ADSL interface include:

- Control Interface (CTRLE) Expansion bus

- Data Interface UTOPIA Level 2

- Chip Select EXP\_CS4\_N

- Ready Signal On IO\_WAIT\_N

- Interrupt GPIO 16 Mbytes 12, active low

- Clock External, 33-MHz, UTP\_IP\_CLK and UTP\_OP\_CLK

The ADSL WAN interface is provided by a mezzanine card plugged into the ADSL board socket. The ADSL chipset is interfaced with the host, through the expansion bus, for control and initialization purposes. The chip set needs nine address lines and its data bus is eight bits wide.

The ADSL CTRLE interface is enabled by the expansion-bus Chip-Select 4 output. The ADSL interrupt is recognized by the IXP425 network processor on GPIO 12. The user data interface is provided through the UTOPIA Level 2 interface. The ADSL mezzanine card requires 3.3-V and 12-V supplies. Table 6 shows the mezzanine card pin numbers and functions.

# intel®

#### Table 6. CON 7 ADSL Mezzanine Board Connector

| 1         2         3         4         5         6         7         8         9         10         11         12         13         14         15         16         17         18         19         20 | CTRLE-A6<br>CTRLE-A8<br>Ground<br>Ground<br>CTRLE-A3<br>CTRLE-A4<br>Ground<br>Ground<br>CTRLE-A1<br>CTRLE-A1<br>CTRLE-A1<br>CTRLE-A2<br>Ground<br>Ground<br>CTRLE-D4<br>CTRLE-D4<br>CTRLE-A7<br>Ground<br>Ground<br>Ground |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 3         4         5         6         7         8         9         10         11         12         13         14         15         16         17         18         19                                | Ground<br>Ground<br>CTRLE-A3<br>CTRLE-A4<br>Ground<br>Ground<br>CTRLE-A1<br>CTRLE -ADSL_SEL#<br>Ground<br>Ground<br>CTRLE-D4<br>CTRLE-A7<br>Ground                                                                         |  |  |  |

| 4         5         6         7         8         9         10         11         12         13         14         15         16         17         18         19                                          | Ground<br>CTRLE-A3<br>CTRLE-A4<br>Ground<br>Ground<br>CTRLE-A1<br>CTRLE -ADSL_SEL#<br>Ground<br>Ground<br>CTRLE-D4<br>CTRLE-A7<br>Ground                                                                                   |  |  |  |

| 5         6         7         8         9         10         11         12         13         14         15         16         17         18         19                                                    | CTRLE-A3<br>CTRLE-A4<br>Ground<br>Ground<br>CTRLE-A1<br>CTRLE -ADSL_SEL#<br>Ground<br>Ground<br>CTRLE-D4<br>CTRLE-A7<br>Ground                                                                                             |  |  |  |

| 6         7         8         9         10         11         12         13         14         15         16         17         18         19                                                              | CTRLE-A4<br>Ground<br>Ground<br>CTRLE-A1<br>CTRLE -ADSL_SEL#<br>Ground<br>Ground<br>CTRLE-D4<br>CTRLE-A7<br>Ground                                                                                                         |  |  |  |

| 7         8         9         10         11         12         13         14         15         16         17         18         19                                                                        | Ground<br>Ground<br>CTRLE-A1<br>CTRLE -ADSL_SEL#<br>Ground<br>Ground<br>CTRLE-D4<br>CTRLE-A7<br>Ground                                                                                                                     |  |  |  |

| 8       9       10       11       12       13       14       15       16       17       18       19                                                                                                        | Ground<br>CTRLE-A1<br>CTRLE -ADSL_SEL#<br>Ground<br>Ground<br>CTRLE-D4<br>CTRLE-A7<br>Ground                                                                                                                               |  |  |  |

| 9       10       11       12       13       14       15       16       17       18       19                                                                                                                | CTRLE-A1<br>CTRLE -ADSL_SEL#<br>Ground<br>Ground<br>CTRLE-D4<br>CTRLE-A7<br>Ground                                                                                                                                         |  |  |  |

| 10       11       12       13       14       15       16       17       18       19                                                                                                                        | CTRLE -ADSL_SEL#<br>Ground<br>Ground<br>CTRLE-D4<br>CTRLE-A7<br>Ground                                                                                                                                                     |  |  |  |

| 11       12       13       14       15       16       17       18       19                                                                                                                                 | Ground<br>Ground<br>CTRLE-D4<br>CTRLE-A7<br>Ground                                                                                                                                                                         |  |  |  |

| 12       13       14       15       16       17       18       19                                                                                                                                          | Ground<br>CTRLE-D4<br>CTRLE-A7<br>Ground                                                                                                                                                                                   |  |  |  |

| 13       14       15       16       17       18       19                                                                                                                                                   | CTRLE-D4<br>CTRLE-A7<br>Ground                                                                                                                                                                                             |  |  |  |

| 14       15       16       17       18       19                                                                                                                                                            | CTRLE-A7<br>Ground                                                                                                                                                                                                         |  |  |  |

| 15<br>16<br>17<br>18<br>19                                                                                                                                                                                 | Ground                                                                                                                                                                                                                     |  |  |  |

| 16           17           18           19                                                                                                                                                                  |                                                                                                                                                                                                                            |  |  |  |

| 17<br>18<br>19                                                                                                                                                                                             | Ground                                                                                                                                                                                                                     |  |  |  |

| 18<br>19                                                                                                                                                                                                   | oround                                                                                                                                                                                                                     |  |  |  |

| 19                                                                                                                                                                                                         | CTRLE-RDY#                                                                                                                                                                                                                 |  |  |  |

| _                                                                                                                                                                                                          | CTRLE-A2                                                                                                                                                                                                                   |  |  |  |

| 20                                                                                                                                                                                                         | Ground                                                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                                                            | Ground                                                                                                                                                                                                                     |  |  |  |

| 21                                                                                                                                                                                                         | CTRLE-A0                                                                                                                                                                                                                   |  |  |  |

| 22                                                                                                                                                                                                         | CTRLE-D6                                                                                                                                                                                                                   |  |  |  |

| 23                                                                                                                                                                                                         | Ground                                                                                                                                                                                                                     |  |  |  |

| 24                                                                                                                                                                                                         | Ground                                                                                                                                                                                                                     |  |  |  |

| 25                                                                                                                                                                                                         | CTRLE-D5                                                                                                                                                                                                                   |  |  |  |

| 26                                                                                                                                                                                                         | CTRLE-D2                                                                                                                                                                                                                   |  |  |  |

| 27                                                                                                                                                                                                         | Ground                                                                                                                                                                                                                     |  |  |  |

| 28                                                                                                                                                                                                         | Ground                                                                                                                                                                                                                     |  |  |  |

| 29                                                                                                                                                                                                         | CTRLE-D3                                                                                                                                                                                                                   |  |  |  |

| 30                                                                                                                                                                                                         | CTRLE-D1                                                                                                                                                                                                                   |  |  |  |

| 31                                                                                                                                                                                                         | Ground                                                                                                                                                                                                                     |  |  |  |

| 32                                                                                                                                                                                                         | Ground                                                                                                                                                                                                                     |  |  |  |

| 33                                                                                                                                                                                                         | CTRLE-D0                                                                                                                                                                                                                   |  |  |  |

| 34                                                                                                                                                                                                         | CTRLE-WR#                                                                                                                                                                                                                  |  |  |  |

| 35                                                                                                                                                                                                         | Ground                                                                                                                                                                                                                     |  |  |  |

| 36                                                                                                                                                                                                         |                                                                                                                                                                                                                            |  |  |  |

| <b></b> |                 |  |  |  |

|---------|-----------------|--|--|--|

| Pin     | Function        |  |  |  |

| 37      | CTRLE-RD#       |  |  |  |

| 38      | CTRLE-ADSL-IRQ# |  |  |  |

| 39      | Ground          |  |  |  |

| 40      | Ground          |  |  |  |

| 41      | MODE            |  |  |  |

| 42      | CTRLE-A5        |  |  |  |

| 43      | Ground          |  |  |  |

| 44      | Ground          |  |  |  |

| 45      | CTRLE-D7        |  |  |  |

| 46      | UTP_RX_D6       |  |  |  |

| 47      | Ground          |  |  |  |

| 48      | Ground          |  |  |  |

| 49      | ADSL_CLK        |  |  |  |

| 50      | UTP_RX_D0       |  |  |  |

| 51      | Ground          |  |  |  |

| 52      | Ground          |  |  |  |

| 53      | UTP_TX_D2       |  |  |  |

| 54      | UTP_TX_CLAV     |  |  |  |

| 55      | Ground          |  |  |  |

| 56      | Ground          |  |  |  |

| 57      | UTP_TX_D1       |  |  |  |

| 58      | UTP_TX_D4       |  |  |  |

| 59      | Ground          |  |  |  |

| 60      | Ground          |  |  |  |

| 61      | UTP_TX_A1       |  |  |  |

| 62      | UTP_TX_A0       |  |  |  |

| 63      | Ground          |  |  |  |

| 64      | Ground          |  |  |  |

| 65      | UTP_TX_D3       |  |  |  |

| 66      | UTP_RX_D2       |  |  |  |

| 67      | Ground          |  |  |  |

| 68      | Ground          |  |  |  |

| 69      | UTP_RX_D5       |  |  |  |

| 70      | UTP_RX_D3       |  |  |  |

| 71      | Ground          |  |  |  |

| 72      | Ground          |  |  |  |

| 73      | UTP_TX_D6       |  |  |  |

| 74      | ADSL_CLK        |  |  |  |

| 75      | Ground          |  |  |  |

| L       | 1               |  |  |  |

| Pin | Function   |

|-----|------------|

| 76  | Ground     |

| 77  | UTP_RX_SOC |

| 78  | UTP_RX_D0  |

| 79  | Ground     |

| 80  | Ground     |

| 81  | UTP_RX_D7  |

| 82  | UTP_RX_D7  |

| 83  | Ground     |

| 84  | Ground     |

| 85  | UTP_TX_EN  |

| 86  | UTP_RX_D4  |

| 87  | Ground     |

| 88  | Ground     |

| Pin | Function    |  |

|-----|-------------|--|

| 89  | UTP_RX_D1   |  |

| 90  | UTP_TX_SOC  |  |

| 91  | Ground      |  |

| 92  | Ground      |  |

| 93  | UTP_RX_A1   |  |

| 94  | UTP_TX_D5   |  |

| 95  | Ground      |  |

| 96  | Ground      |  |

| 97  | UTP_RX_CLAV |  |

| 98  | UTP_RX_EN   |  |

| 99  | UTP_RX_A0   |  |

| 100 | +12V        |  |

#### 2.7 PCI Interface

The IXDPG425 is equipped with a PCI interface (only 33-MHz PCI is supported). The PCI peripherals include a USB 2.0 controller, and a miniPCI socket (CON 16). An optional second miniPCI socket (CON 15) can be mounted on the rear of the IXDPG425 printed circuit assembly.

Reset of the PCI bus is under control of the power-on reset controller and GPIO8. Table 7 lists the ID selects assignments used during PCI reset and initialization.

#### Table 7. PCI Reset ID Select and Interrupt Assignments

| PCI Peripheral           | IDSEL | Interrupt | GPIO  |

|--------------------------|-------|-----------|-------|

| MiniPCI Slot             | AD19  | INTB      | GPIO7 |

| Optional MiniPCI<br>Slot | AD20  | INTB      | GPIO7 |

| USB 2.0<br>Controller    | AD18  | INTA      | GPIO6 |

### 2.8 Ethernet Interfaces — Four-Port LAN, One-Port WAN

Interface:MDC/MDIO

Interface:NPE Ethernet 0 to 4x switch Clock: External, 25 MHz

Interface:NPE Ethernet 1 to 1x Ethernet WAN Clock:External, 25 MHz

The IXP425 network processor has two Ethernet 10/100BaseT interfaces, implemented with Ethernet coprocessors built into the NPEs.

The coprocessors provide support for an MII interface to the external PHY. They support both full-duplex and halfduplex mode of operation and also contain two 256-byte FIFOs, one for transmit data, and the other for receive data.

The IXP425 network processor includes a single management data interface — Management Data Input Output (MDIO) — and Management Data Clock (MDC) to program the Ethernet PHYs.

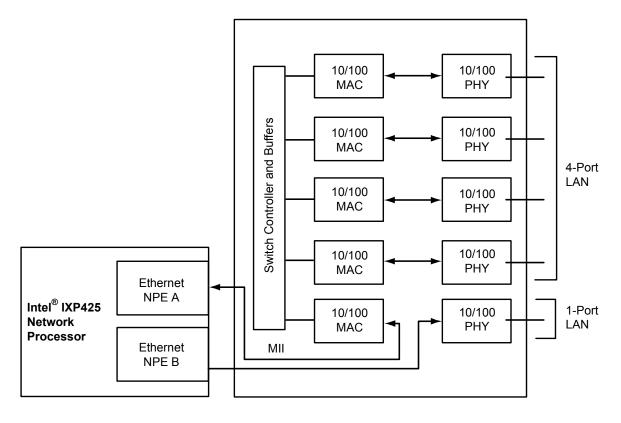

On the platform, the Realtek RTL8305-SBVD component is used. This component contains five physical-layer transceivers and five MAC units with an integrated Layer-2 switch.

On the platform, the integrated five-port switch provides the interface for up to four devices on the LAN. The LAN portion of the switch is connected to the IXP425 Ethernet Controller 0, via the MII-0 interface. The fifth port is directly connected to the IXP425 Ethernet Controller 1 via the MII-1 interface. Such configuration allows implementation of Ethernet bridge and router modes in software, and — at the same time — filters out the local traffic on the LAN to reduce the load on the Intel XScale core, as shown in Figure 4.

Each of the RJ45 connectors for each of the Ethernet ports have integrated LEDs that illuminate as follows:

Green: Link/activity Amber: 10/100 Mbps; illuminates when connected to a 100-Mbps network

#### Figure 4. Software Implementation of Ethernet Bridging and Router Modes

Revision 001

#### 2.9 Voice Ports

#### Table 8. Voice Ports

| Attributes           | Port                                                        | Port                                     |

|----------------------|-------------------------------------------------------------|------------------------------------------|

| Interface            | SPI to Si3210-0 to Si3210-3                                 | HSS0 – PCM to<br>Si3210–0 to<br>Si3210-3 |

| Chip Select#         | GPIO5 active low                                            |                                          |

| Clock                | GPIO2 (HSS0_TXCLK)                                          |                                          |

| Ready Signal         |                                                             |                                          |

| Interrupt#           | GPI011                                                      |                                          |

| Data IN              | SDI GPIO3 to Si3210-0, then Si3210-1, 2, 3. (Data to CODEC) |                                          |

| Data OUT             | SDO GPIO4 (Data from CODEC)                                 |                                          |

| Programmed<br>Reset# | GPIO13 active low                                           |                                          |

The line interface is implemented using four of the Silicon Laboratories\* ProSLIC\* Si3210 components that integrate a DC-DC converter for ring voltages, the A- and  $\mu$ -law linear companding, DTMF decoders, and dual-tone generators for a single telephone line. The Si3210 components are connected to the IXP425 network processor using the SPI and PCM buses. The voice data is sent to and from the codec on the PCM time-slotted, synchronous, serial interface.

The SLIC is programmed through the SPI interface that can work in 8-bit serial mode. The SPI is connected to the four SLICs in the daisy-chain mode, as shown in Figure 5.

The PCM common bus, with the time-slotted protocol, allows support of local line-looping and inserts dataprocessing elements into the data flow to support a variety of compression algorithms.

A fifth telephone connector is provided to allow a conventional telephone exchange line to be plugged in. In the event of power failure or software failure, the telephone plugged into voice port 4, will automatically fail-over to the exchange line, allowing continued operation of this telephone service.

The failover relay is organized such that the Normally-Closed contacts will connect the exchange line to port 4 when there is no power to the IXDPG425. Additionally, a retriggerable monostable is used to control the relay, such that if the monostable does not receive retrigger signals before its time-out period (approximately 600 ms), it will cause the relay to revert to its un-powered state and port 4 will fail over to the exchange line. The re-trigger signal used is the same signal used for the watchdog retrigger (GPIO10). This will ensure that a telephone call is still possible even if there has been a software failure on the IXDPG425.

#### Figure 5. Four Voice Ports (Two Shown)

Revision 001

The PCM works under control of NPE firmware, which is loaded at startup to configure the IXDPG425 HSS ports.

The DTMF signaling decoding is implemented in the SLICs, and the call progress and dialing is supported by the IXP425 network processor and the voice driver.

During initialization, the SLICs require a series of ordered steps for reset:

- 1. After the power-on reset is completed, I/O-reset pin GPIO13 needs to be kept active.

- 2. The HSS port must be initialized to provide a 2- or 1.5-MHz clock and an 8-KHz frame signal.

- 3. The PCM clock and frame signals must be present and stable prior to de-asserting the I/O-reset signal.

- 4. At this point, the I/O-reset pin GPIO13 can be de-asserted (high) along with the SPI clock signal, set to "high." Before this point (GPIO13 going high), no other I/O can be initialized.

- 5. In platform configurations where voice features are not required, the voice port should be disabled by keeping the PCM\_CLK (clock) and PCM\_FRAME (frame) signals and the SPI\_SCK (clock) signals "low" and the SPI\_CS0\_N signal "high."

### 2.10 USB Ports

The USB 1.1 interface utilizes the IXP425 network processor on-chip USB controller, and can work only as the USB peripheral at a 12-Mbps data rate.

A Type-B, USB 'device' receptacle is provided at the board edge. A 1.5-K, pull-up resistor is applied on the D+ USB pin to indicate that the IXP425 network processor is a full-speed USB device.

The USB board design meets USB-specification requirements.

The USB 2.0 interface is built around the NEC\* µPD720101 PCI USB 2.0 host adaptor chip. Two USB 2.0 host interfaces are implemented. Automatic voltage supply and over-current protection is included.

| USB Version            | USB Connector Number |

|------------------------|----------------------|

| USB 1.1 Slave          | CON 20               |

| USB 2.0 Host (2 Ports) | CON 11               |

#### 2.11 Console Serial Port

The IXP425 network processor provides two dedicated, asynchronous, serial, I/O ports (UART0 and UART1). These UARTs are 16550-compliant with flow control and enhanced with larger 64-byte transmit and receive buffers. Only UART0 is used on the IXDPG425.

The console serial interface is connected to (UART0) Port 0. Port 0 is routed to the 10-pin header connectors (CON 4) with RTS and CTS flow control. Additional signaling lines (DTR and DCD) are provided by GPIO port pins 0 and 1, respectively. Port 0 is wired according to the RS-232 specification for data terminal equipment. A cross-over serial cable will be used to connect to a host PC.

A simple 10-pin header-to-DB9 converter assembly can be created with a 10-pin socket and a 9-pin DB9 socket and a short section of 10-way ribbon cable.

| Pin<br>Number | Signal Name   |

|---------------|---------------|

| 1             | DCD# (GPIO 1) |

| 2             | N/C           |

| 3             | RXD           |

| 4             | RTS#          |

| 5             | TXD           |

#### Table 9. Serial Port, CON 4, 10-Pin, Dual-Row Header (Sheet 1 of 2)

| Table 9. | Serial Port. | CON 4. | 10-Pin. | <b>Dual-Row H</b> | leader ( | (Sheet 2 of 2) |  |

|----------|--------------|--------|---------|-------------------|----------|----------------|--|

|          |              |        |         |                   |          |                |  |

| Pin<br>Number | Signal Name   |

|---------------|---------------|

| 6             | CTS#          |

| 7             | DTR# (GPIO 0) |

| 8             | N/C           |

| 9             | GND           |

| 10            | N/C           |

### 2.12 JTAG Emulator Interface

During debug, the IXP425 network processor can be controlled through a JTAG interface to the Intel XScale core. The Macraigor\* Raven\* and Wind River Systems\* visionPROBE\* / visionICE\* systems plug into the JTAG interface through a 20-pin connector (CON 1), defined in Table 10.

#### Table 10. JTAG Interface Connector Signals (Sheet 1 of 2)

| Pin Number | Signal Name | Connect to:                                                                                                                                                                                                                                                                                   |

|------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VTREF       | 3 V3                                                                                                                                                                                                                                                                                          |

| 2          | VSUPPLY     | +3V3                                                                                                                                                                                                                                                                                          |

| 3          | TRST_N      | $10 K\Omega$ pull-down – The JTG_TRST_N signal must be asserted (driven low) during power-up, otherwise the TAP controller may not be initialized properly, and the processor may be locked. When the JTAG interface is not being used, the signal must be pulled low using a 10-K. resistor. |

| 4          | GND         | GND                                                                                                                                                                                                                                                                                           |

| 5          | TDI         | 10KΩ pull-up                                                                                                                                                                                                                                                                                  |

| 6          | GND         | GND                                                                                                                                                                                                                                                                                           |

| 7          | TMS         | 10KΩ pull-up                                                                                                                                                                                                                                                                                  |

| 8          | GND         | GND                                                                                                                                                                                                                                                                                           |

| 9          | ТСК         | 10KΩ pull-up                                                                                                                                                                                                                                                                                  |

| 10         | GND         | GND                                                                                                                                                                                                                                                                                           |

| 11         | RTCK        | GND                                                                                                                                                                                                                                                                                           |

| 12         | GND         | GND                                                                                                                                                                                                                                                                                           |

| 13         | TDO         | 10KΩ pull-up                                                                                                                                                                                                                                                                                  |

| 14         | GND         | GND                                                                                                                                                                                                                                                                                           |

| Pin Number | Signal Name | Connect to:             |

|------------|-------------|-------------------------|

| 15         | SRST_N      | Reset circuitry (/BDMR) |

| 16         | GND         | GND                     |

| 17         | DBGRQ       |                         |

| 18         | GND         | GND                     |

| 19         | DGBACK      |                         |

| 20         | GND         | GND                     |

#### Table 10. JTAG Interface Connector Signals (Sheet 2 of 2)

#### 2.13 Front-Panel Indicator LEDs

The IXDPG425 has LEDs (light-emitting diodes) indicating the activities shown in Table 11. The LEDs are controlled by an 8-bit, memory-mapped latch. Writing a 0 to a specific LED latch bit will cause the LED to illuminate. The base address for the LED latch is set by CS3#. The latch is write-only and it is not possible to read back the status of the latch.

#### Table 11. Intel<sup>®</sup> IXDPG425 Network Gateway Reference Platform LEDs

| LED Latch<br>(CS3#) | LED | Color | Description                |

|---------------------|-----|-------|----------------------------|

|                     | D24 | Green | Power to the system is on. |

| Bit 0               | D23 | Green | LED1                       |

| Bit 1               | D18 | Green | LED2                       |

| Bit 2               | D17 | Green | LED3                       |

| Bit 3               | D16 | Green | LED4                       |

| Bit 4               | D4  | Green | LED5                       |

| Bit 5               | D3  | Green | LED6                       |

| Bit 6               | D2  | Green | LED7                       |

| Bit 7               | D1  | Green | LED8                       |

#### 2.14 Platform-Reset Circuitry

The board generates a power-on reset when the required voltages reach valid levels. The power-on reset signal resets all the circuitry. A reset link (CON8) provided on the IXDPG425 also resets the entire board. Shorting the two pins of CON 8 together will cause a Reset.