# Intel<sup>®</sup> Internet Exchange Architecture

Programmable Network Processors for Today's Modular Networks

Intel<sup>®</sup> Internet Exchange Architecture

White Paper

## Contents

| Overview                                                             |

|----------------------------------------------------------------------|

| Intel® Internet Exchange Architecture (Intel® IXA)                   |

| Microengine Technology                                               |

| High-Speed Data-Plane Processing—Hyper Task Chaining4                |

| Intel <sup>®</sup> XScale <sup>™</sup> Technology                    |

| Intel® IXA Portability Framework                                     |

| Intel <sup>®</sup> IXA Network Processors: Families from CPE to Core |

| Intel® IXA Software Developer's Kit (SDK)                            |

| Complementary Technologies                                           |

| Intel <sup>®</sup> IXA Developer Network                             |

| Industry Standards                                                   |

| Summary                                                              |

#### Overview

As a leading innovator in network processing and Ethernet connectivity, Intel is helping to drive the evolution of nextgeneration IP (Internet Protocol)-based network services in applications from the customer premises (CPE) to the network core. As a part of its continuing leadership, Intel has created a packet-processing architecture focused on network processors, known as the Intel<sup>®</sup> Internet Exchange Architecture (Intel<sup>®</sup> IXA). The combination of unlimited programmability and robust packet handling performance of Intel IXA network processors support the rapid development and deployment of intelligent network services, while helping to extend product life cycles for lower total cost of ownership. Intel IXA includes multiple families of network processors, each one optimized to meet the varied, specialized and often exclusive packet-handling requirements of particular market segments including CPE, access, edge and core applications. Within each segment, Intel® IXA network processors provide developers with a consistent and cost-effective development environment that includes multiple operating systems, software, tools and development platforms. In this way, Intel IXA provides developers with a comprehensive packet-processing hardware and software architecture designed to support cost-effective code portability and re-use across multiple current and future generations of Intel IXA network processors. In addition, Intel is working with a robust network of thirdparty developers who are providing complementary products to enable customer solutions.

## Intel<sup>®</sup> Internet Exchange Architecture

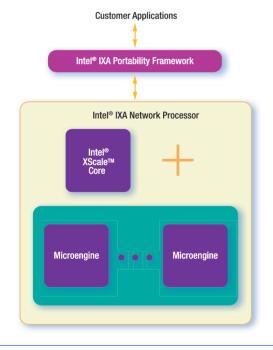

Intel IXA is a network processing architecture that has three defining elements:

- Microengine technology—a subsystem of programmable, multi-threaded RISC microengines that enable highperformance packet processing in the data plane through Intel<sup>®</sup> Hyper Task Chaining. This multiprocessing technology features software pipelining and low-latency sequence management hardware.

- Intel<sup>®</sup> XScale<sup>™</sup> technology—providing the highest performance-to-power ratio in the industry, with performance up to 1,000 MIPS and power consumption as low as 10 mW, for low-power, high-density processing of control-plane applications.

- The Intel<sup>®</sup> IXA Portability Framework—an easy-to-use modular programming framework providing the advantages of software investment protection and faster time-to-market through code portability and re-use between network processor-based projects, in addition to future generations of Intel IXA network processors.

Figure 1.

## Microengine Technology

Intel<sup>®</sup> IXA microengine technology enables faster deployment of intelligent network services through unlimited programming flexibility and high-performance processing. Scalable microengines provide support for a broad range of line rates, currently ranging from OC-3/155 Mbps through OC-192/10 Gbps. High performance and scalability are achieved through a multiprocessor, multi-threaded distributed architecture and pipelining features in software. The microengines feature innovative inter-thread communication capabilities for efficient processing at high line rates and general-purpose hardware elements that enable advanced networking algorithms.

Intel IXA microengine technology plays a key role in the network processor's store-and-forward architecture to provide flexible and rich network processing in converged communications environments. The multiprocessing subsystem of the network processor features an OEM-programmable compute platform for the development of new data-plane applications. Depending on their application segment, Intel IXA network processors feature varying numbers of independent RISC data engines with hardware multi-thread support. These microengine clusters provide the processing power to perform tasks traditionally reserved for high-speed ASICs, with the added advantage of flexible programmability. The instruction set for the microengines is specifically designed to forward data efficiently in networking and communications applications. The unique hardware architecture of the microengines is designed to support high-performance data-plane processing without assistance from the core processor.

Microengine technology delivers these important benefits:

- Flexibility and customizability—programmability enables ASIC-like special functions to be implemented and later changed if needed with less cost and engineering effort. New service capabilities can be added to equipment through software, helping to eliminate costly upgrades.

- Scalability—Microengine technology spans a wide range of speed and functionality requirements from Layer 2 through Layer 7.

- Wire-speed performance—The deep packet inspection required for intelligent applications can be performed at speeds up to OC-192 and beyond.

## High-Speed Data-Plane Processing—Hyper Task Chaining

As the network continues to evolve, the value of network processor technology will increasingly depend on intelligent packet processing at wire speed, rather than on raw performance alone. The ability of carriers to provision and bill for new services will require a combination of performance and flexible control over processing resources. As an example, for an OC-192/10 Gbps link, deep packet inspection must occur in an interval as short as 35 nanoseconds. The network processor must perform the necessary Layer-3 through Layer-7 applications on these packets, and then transmit them in the correct sequence and at the required rate without loss.

Intel's store-and-forward network processor architecture is ideally suited to this challenge, providing a high-performance, OEM-programmable platform for implementing new data-plane applications. The multiprocessing subsystem of the second-generation network processor ensures that aggregate processing capacity is available to enable rich packet processing, even for 10 Gbps wire-speeds in applications that traditionally required high-speed ASICs. In addition, the highly parallel design of the microengines allows a single-stream, packet analysis problem such as routing to be decomposed into multiple, sequential tasks, including packet-receive, route table look-up, and packet classification. The performance and flexibility provided by this software-defined processing pipeline allows multiple tasks to be completed simultaneously while preserving data and time dependencies. As network requirements evolve, this powerful and flexible network processor design will enable OEMs to easily scale performance and add features to meet new requirements.

The microengine design of second-generation Intel IXA network processors constitutes the first implementation of Intel's Hyper Task Chaining technology. This unique network processing approach provides hardware support for managing data-dependent operations among multiple parallel processing stages with low latency. Patented memory register technologies enable data and event signals to be shared among threads and microengines at virtually "zero latency," while maintaining coherency. Other innovations, known as Ring Buffers, establish FIFO "producer-consumer" relationships among microengines, providing a highly efficient mechanism for flexibly linking tasks among multiple software pipelines. Through this combination of flexible software pipelining and fast inter-process communication, Hyper Task Chaining enables Intel IXA network processors designed for core, access and edge applications to perform complex processing at wire speed.

### Intel<sup>®</sup> XScale<sup>™</sup> Technology

The Intel XScale core is designed to handle application processing, communication with the backplane, managing and updating data structures shared with the microengines, such as routing tables, and setting up and controlling media and switch fabric devices. In addition, the Intel XScale core handles exception packets that require additional complex processing.

Intel XScale microarchitecture achieves high performance with Intel® Superpipelined Technology, a multi-stage, highefficiency instruction-level processing pipeline architecture that minimizes latency and enables clock speeds with ultra-low power consumption. Based on the ARM\* Version 5TE instruction set (excluding the floating-point instruction set), Intel XScale technology delivers industry-leading mWatt/MIPS performance, while preserving software compatibility with Intel's first-generation network processors. Software development is made easier by the extensive Intel XScale technology tools environment, including compilers, debuggers, operating systems, models, emulators, support services from third-party vendors, and fully documented evaluation boards and kits. The compiler, assembler and linker support specific optimizations designed for the Intel XScale microarchitecture, the ARM instruction set v.5TE, and Intel® DSP extensions.

## Intel<sup>®</sup> IXA Portability Framework

The Intel IXA Portability Framework enables fast and costeffective code development with portability and re-use that protects investments in both Intel XScale core processor code and microengine code.

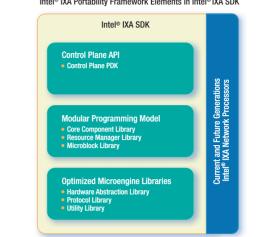

The Intel IXA Portability Framework includes:

- · Optimized microengine libraries and tools that provide continuity between changes in the microengine instruction set and architecture. The libraries include a hardware abstraction library to enable interoperability across multiple hardware configurations, a protocol library and a utility library for hardware-optimized operations on protocol headers and data structures.

- A modular programming model enables optimal application partitioning across microengines and threads and facilitates the integration of customer-developed, thirdparty and Intel® supplied micro-blocks (independent building blocks of code for microengines that perform a specific function). The modular model enables software components to be flexibly mixed, matched and re-used. The micro-block library is designed to support the pipelined architecture of the network processor microengines by enabling the flexible connection of micro-blocks.

- Intel XScale microarchitecture source code libraries enable modular core component development and enhance portability between multiple operating environments.

- The Intel XScale core control plane platform development kit (PDK) provides a common interface and interconnect protocol for control plane stacks running on external processors.

For ease of programming, micro-block code can be developed using the high-level Microengine C language. The Intel IXA Portability Framework is an integral part of the Intel® IXA Software Developer's Kit (SDK).

Figure 3.

## Intel<sup>®</sup> IXA Network Processors: Families from CPE to Core

In addition to the wide range of networking applications supported by the first generation of Intel IXA network processors, the latest Intel network processor families are designed for the specialized requirements of CPE applications, wide area networking at up to OC-48/2.5 Gbps line rates and core applications at OC-192/10 Gbps. Intel IXA meets a wide range of next-generation networking requirements in each of these application categories, including:

- Rapid deployment of new networking and communications services

- · Differentiated networking features and functionality

- Scalable performance

- · Software portability

- Reduced development cost and total cost of ownership.

#### **CPE** Applications

The Intel® IXP425 network processor family meets nextgeneration broadband CPE requirements with a distributed processing architecture that provides ample processing headroom for a manufacturer to port and add differentiating product features. Each network processor features an Intel XScale core for application and control processing, integrated on the same chip with three network processor engines (NPEs) that offload number crunching or bit level tasks for send/receive packet processing and encapsulated coprocessor functions. The NPEs and a fast-path design in the Intel IXP425 network processor are capable of providing wire-speed performance up to 52 Mb/s. The Intel IXP425 network processor also includes on-chip integration of voice and data functions and offers a full range of broadband and LAN access solutions through multiple integrated interfaces. With its Development Platform and choice of operating systems and development tools, the Intel IXP425 network processor provides a complete development environment for faster time-to-market of CPE applications such as residential gateways, small/medium enterprise routers, integrated access devices (IADs), cable modems, wireless access points, and multi-dwelling units (MxUs).

#### Access and Edge Applications

The Intel® IXP2400 network processor is a member of Intel's second-generation network processor family. It is designed for a wide range of access and edge applications including multi-service switches, routers, broadband access devices, and wireless infrastructure systems. Based on the first-generation Intel® IXP1200 network processor, the IXP2400 is a highly integrated, programmable data processor that provides a direct migration path to enhanced parallel processing performance in a wide variety of OC-12/622 Mbps to OC-48/2.5 Gbps networking, communications and data-intensive applications. The IXP2400 network processor integrates an Intel XScale core with eight multi-threaded, independent 32-bit microengines that cumulatively enable a total of 4.8 giga-operations per second.

#### **Core Applications**

The Intel<sup>®</sup> IXP2800 network processor is the highestperformance member of Intel's second-generation network processor family. It integrates a high-performance parallel processing architecture on a single chip designed for processing complex algorithms, deep packet inspection, traffic management and forwarding at wire speed in network edge and core applications. The IXP2800 integrates a high-performance Intel XScale core with sixteen 32-bit independent multi-threaded microengines that provide a total of 25.2 giga-operations per second.

## Intel<sup>®</sup> First-Generation Network Processors

The widely used Intel IXP1200 network processor family represents the first generation of Intel IXA network processors. These versatile network processors are designed to provide high-speed manipulation of network packets across multiple media types and enable efficient forwarding and modification of packet headers while reserving sufficient compute cycles for some network management and analysis tasks. The Intel IXP1200 network processor family includes the Intel<sup>®</sup> IXP1200, 1240 and 1250 network processors, providing a choice of 166-, 200-, or 232- MHz Intel<sup>®</sup> StrongARM\* cores with available features including Cyclic Redundancy Checking (CRC) and Error Correction Code (ECC) memory support for improved performance and reliability.

## Intel<sup>®</sup> IXA Software Developer's Kit (SDK)

As network processors become widely implemented, a clear differentiator is the quality and completeness of the hardware/software architecture and the supporting development environment. In order to really deliver on the performance and time-to-market advantages of network processors, developers need software in several crucial areas, including data-plane code-development, controlplane code and system development, and data and cycle accurate simulation. The Intel IXA SDK provides developers with a complete and advanced system to develop, simulate, optimize, debug and deliver advanced networking products.

Developers require a complete development package, including data-plane and control-plane tools and a choice of embedded operating systems, supported by a comprehensive hardware development platform. The Intel IXA SDK provides the integrated tools, advanced simulation capabilities, key building blocks and simplified programming environment needed to implement network applications using Intel IXA network processors and re-use the software. The SDK includes several tool categories designed to unite network processor applications and processes and assist in rapid code development:

- The Integrated Microengine Development Environment provides an integrated development environment for advanced graphical simulation, profiling and debugging by working entirely in software. It enables faster prototyping, intuitive optimization, and supports both dataplane and control-plane applications. The transactor assists in resolving concurrency issues by simulating packets going into and out of the network processor. It can be used to gather statistics that aid in architectural design and verification by providing a fine level of internal detail, including pipeline execution stages, that would not otherwise be visible.

- The Intel<sup>®</sup> Microengine C compiler supports a high-level programming language to facilitate code development for the microengines and improve time-to-market.

- The SDK is provided with the Wind River\* VxWorks\* or MontaVista\* Linux operating system, and the Intel IXA environment supports other third-party embedded operating systems.

- Intel IXA Portability Framework and libraries eliminate time-consuming development of crucial infrastructure software. These tools enable rapid development of modular, portable code blocks and the integration of third-party software products for extended time-in-market and easier modifications.

- A suite of completed building blocks and example applications speeds development through the use of common networking building blocks.

The Intel IXA SDK enables developers to work on their software designs in parallel with hardware design and prototyping. In addition, Intel complements the SDK with hardware development platforms featuring an industry standard form factor, designed to demonstrate Intel IXA network processors performing processing at OC-48/2.5 Gbps and OC-192/10 Gbps rates.

#### Complementary Technologies

Intel IXA network processors work together with a variety of complementary technologies, including:

- Embedded Intel<sup>®</sup> Architecture control processors that enable high performance, scalability, and broad software support in communications applications

- Intel<sup>®</sup> Media Signal Processors for high-performance Voice over Packet applications

- Intel® I/O processors for networked storage applications

- A comprehensive line of framers, media access controllers and physical layer devices.

Embedded Intel Architecture devices, media signal processors, I/O processors, framers and PHYs are easily integrated into system-level solutions through common interfaces to Intel IXA network processors.

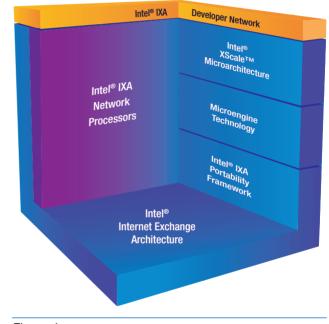

#### Intel® IXA Developer Network

Intel IXA network processors are supported by a robust community of third-party developers known as the Intel<sup>®</sup> IXA Developer Network. The network includes suppliers of operating systems, modular software, board-level products, development tools, complementary silicon, and professional services including design, training, and consulting. Through its network of third-party developers Intel is working to ensure that its customers have the broadest available choice of components and services for innovative, cost-effective multi-service solutions.

#### Industry Standards

Within Intel IXA, compliance with industry standards is achieved in two ways. With the high degree of programmability incorporated into the Intel IXA network processors through the Intel IXA SDK, new protocols can be easily defined using a high-level language. Similarly, modifications or extensions to existing protocols are easily incorporated by straightforward modification to existing source-level protocol definitions.

Intel is a member of the Network Processor Forum (NPF), an industry group devoted to defining and promoting common application programming interfaces (APIs) between network processors and other hardware and software components. This participation complements Intel's investment in the development of the Intel IXA SDK. Intel works actively along with other members of the Forum to initially specify interfaces between control processors that run networking code including routing algorithms, and network processors optimized for more in-depth packet processing.

Flexibility with respect to implementation of new protocols and services is a fundamental goal of Intel IXA. Intel will continue to participate in defining future standards, helping to ensure Intel IXA software and hardware components remain compatible with the most recent industry developments.

### Summary

Programmable network processors enable developers to define network functionality in software. While this approach enables great flexibility, the challenge is how to support this functionality as line rates move to OC-192 and beyond. Intel IXA solves this problem with network processors based on microengine technology, Intel XScale microarchitecture and the Intel IXA Portability Framework. Intel IXA network processors enable wire-speed performance without sacrificing the flexibility of software-based functionality, enabling network services and high-bandwidth network applications from the customer premises to the core of the network.

Figure 4.

#### For More Information

For additional information on Intel IXA and the Intel IXA Developer Network (formerly the Intel IXA Developers Forum) visit www.intel.com/IXA.

#### INTEL AROUND THE WORLD

#### UNITED STATES AND CANADA

Intel Corporation Robert Noyce Building 2200 Mission College Boulevard P.O. Box 58119 Santa Clara, CA 95052-8119 USA Phone: (800) 628-8686

#### EUROPE

Intel Corporation (UK) Ltd. Pipers Way Swindon Wiltshire SN3 1RJ UK

#### Phone

| THOME.      |                   |

|-------------|-------------------|

| England     | (44) 1793 403 000 |

| Germany     | (49) 89 99143 0   |

| France      | (33) 1 4571 7171  |

| Italy       | (39) 2 575 441    |

| Israel      | (972) 2 589 7111  |

| Netherlands | (31) 10 286 6111  |

| Sweden      | (46) 8 705 5600   |

|             |                   |

#### **ASIA-PACIFIC**

Intel Semiconductor Ltd. 32/F Two Pacific Place 88 Queensway, Central Hong Kong, SAR Phone: (852) 2844 4555

#### JAPAN

Intel Kabushiki Kaisha P.O. Box 115 Tsukuba-gakuen 5-6 Tokodai, Tsukuba-shi Ibaraki-ken 305 Japan Phone: (81) 298 47 8522

#### SOUTH AMERICA

Intel Semicondutores do Brazil Rue Florida, 1703-2 and CJ22 CEP 04565-001 Sao Paulo-SP Brazil Phone: (55) 11 5505 2296

#### For more information

To learn more about Intel Corporation, visit our site on the World Wide Web at www.intel.com