# Intel® Atom<sup>TM</sup> PROCESSOR Z6XX SERIES

Datasheet

For the Intel® Atom<sup>TM</sup> Processors Z600, Z605, Z610, Z612, Z615, Z620, and Z625 on 45-nm Process Technology

May 2011

**Revision 001**

Document Number: 325567-001US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See http://www.intel.com/products/processor\_number for details.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

45-nm products are manufactured on a lead-free process. Lead-free per EU RoHS directive July, 2006. Some E.U. RoHS exemptions may apply to other components used in the product package. Residual amounts of halogens are below November 2007 proposed IPC/JEDEC J-STD-709 standards.

Hyper-Threading Technology (HT Technology), requires an Intel®, HT Technology enabled system, check with your PC manufacturer. Performance will vary pending on the specific hardware and software used. Not available on Intel® Core<sup>TM</sup> i5-750. For more information including details on which processors support HT Technology, visit http://www.intel.com/info/hyper threading

Enhanced Intel SpeedStep® Technology, See the Processor Specification Finder at http://ark.intel.com or contact your Intel representative for more information.

Intel, Intel® Atom<sup>TM,</sup> Next-Generation Intel® Atom<sup>TM</sup> Processor-based Platform, Intel® Atom<sup>TM</sup> processor Z6xx series, Intel® Mobile Voltage Positioning (Intel® Atom<sup>10</sup> Next-Generation Intel® Atom<sup>10</sup> Processor-Josesor Patienty, Intel® Atom<sup>10</sup> Processor Jox Series, Intel® Mobile Voltage Posito (Intel® MVP), Intel® Graphics Media Accelerator 600 (Intel® GMA 600), Enhanced Intel SpeedStep® Technology, Intel® Burst Performance Technology (Intel® BPT), Intel® Smart Idle Technology (Intel® ST), Intel® Smart Power Technology (Intel® SPT), Intel® Hyper-Threading Technology (Intel® HT Technology), Intel® Platform Controller Hub MP30, Intel® Pentium® M Processor, Intel® Pentium® 4 Processor, Intel® Core<sup>TM</sup>2Duo Processor, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its

subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2011, Intel Corporation. All rights reserved.

# Contents

| 1 | <b>Read</b><br>1.1<br>1.2<br>1.3<br>1.4 | I Me First       .7         Abstract       .7         Audience       .7         Organization       .7         Reference Documents       .7 |    |  |  |  |

|---|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| 2 | <b>Intro</b><br>2.1<br>2.2              | duction<br>Chapter Contents<br>Acronyms                                                                                                    | 9  |  |  |  |

|   | 2.3                                     | Intel® Atom <sup>TM</sup> Processor Z6xx Series Architecture                                                                               | 10 |  |  |  |

|   | 2.4                                     | Intel® Atom <sup>TM</sup> Processor Z6xx Series Feature Set                                                                                | 10 |  |  |  |

|   |                                         | 2.4.1 Intel® Atom <sup>TM</sup> Processor Z6xx Series Processor Core                                                                       |    |  |  |  |

|   |                                         | 2.4.2 Memory Controller                                                                                                                    |    |  |  |  |

|   |                                         | 2.4.3 LPDDR1                                                                                                                               |    |  |  |  |

|   |                                         | <ul><li>2.4.4 DDR2</li><li>2.4.5 Intel® Graphics Media Accelerator 600 (Intel® GMA 600) Graphics</li></ul>                                 |    |  |  |  |

|   |                                         | 2.4.5 Intel® Graphics Media Accelerator 600 (Intel® GMA 600) Graphics                                                                      |    |  |  |  |

|   |                                         | 2.4.7 cDV0                                                                                                                                 |    |  |  |  |

|   |                                         | 2.4.8 LGI/LGIE/Debug                                                                                                                       |    |  |  |  |

|   | 2.5                                     | Intel® Atom <sup>TM</sup> Processor Z6xx Series Power Management                                                                           | 13 |  |  |  |

|   |                                         | 2.5.1 Intel® Burst Performance Technology (Intel® BPT)                                                                                     |    |  |  |  |

|   |                                         | 2.5.2 Intel® Smart Idle Technology (Intel® SIT)                                                                                            |    |  |  |  |

|   | 2.6                                     | External/Industry Standard Interfaces and Specifications                                                                                   |    |  |  |  |

| 3 | Signa                                   | I Descriptions                                                                                                                             | 15 |  |  |  |

|   | 3.1                                     | Chapter Contents                                                                                                                           | 15 |  |  |  |

|   | 3.2                                     | Acronyms                                                                                                                                   |    |  |  |  |

|   | 3.3                                     | Buffer Types                                                                                                                               |    |  |  |  |

|   | 3.4                                     | Signal Description                                                                                                                         |    |  |  |  |

|   |                                         | <ul><li>3.4.1 System Memory Interface</li></ul>                                                                                            |    |  |  |  |

|   |                                         | <ul><li>3.4.2 cDMI Interface</li><li>3.4.3 cDVO Interface</li></ul>                                                                        |    |  |  |  |

|   |                                         | 3.4.4 LVDS Display Port Interface                                                                                                          |    |  |  |  |

|   |                                         | 3.4.5 MIPI Display Port Interface                                                                                                          |    |  |  |  |

|   |                                         | 3.4.6 LGI/LGIE (Legacy) Interface                                                                                                          | 23 |  |  |  |

|   |                                         | 3.4.7 Debug and Miscellaneous                                                                                                              |    |  |  |  |

| 4 | Powe                                    | r Management                                                                                                                               | 27 |  |  |  |

| • | 4.1                                     | Chapter Contents                                                                                                                           |    |  |  |  |

|   | 4.2                                     | Acronyms                                                                                                                                   |    |  |  |  |

|   | 4.3                                     | Processor Voltage Rails                                                                                                                    |    |  |  |  |

|   | 4.4                                     | Processor Voltage Rail States                                                                                                              |    |  |  |  |

|   |                                         | 4.4.1 VNN                                                                                                                                  |    |  |  |  |

|   |                                         | 4.4.2 VCC                                                                                                                                  |    |  |  |  |

|   |                                         | 4.4.3 VCCPAOAC                                                                                                                             |    |  |  |  |

|   | 4.5                                     | 4.4.4 VCCP                                                                                                                                 |    |  |  |  |

|   | +.J                                     | 4.5.1 VID Enable                                                                                                                           |    |  |  |  |

|   |                                         | 4.5.2 VID Table for Variable Power Supplies                                                                                                |    |  |  |  |

|   | 4.6                                     | Valid Power States                                                                                                                         |    |  |  |  |

|   | 4.7                                                                                                                                                                                                                                                                                                                                                                                                       | Processor Core Low Power Features                                         |    |  |  |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----|--|--|

| 5 | Electrical Specifications         5.1       Chapter Contents         5.2       Acronyms         5.3       Storage Specifications         5.4       Absolute Maximum Ratings         5.5       DC Specifications                                                                                                                                                                                           |                                                                           |    |  |  |

| 6 | Thermal Specifications         6.1       Chapter Contents         6.2       Acronyms         6.3       Package and Die Thermal Characteristics         6.4       Thermal Design         6.5       Temperature Monitoring         6.5.1       Intel® Thermal Monitor         6.5.2       Digital Thermal Sensor         6.5.3       PROCHOT# Signal Pin         6.5.4       Out of Specification Detection |                                                                           |    |  |  |

| 7 | <b>Mech</b><br>7.1<br>7.2                                                                                                                                                                                                                                                                                                                                                                                 | anical Package Specifications.<br>Chapter Contents<br>Pin Out Information | 55 |  |  |

|   | 7.3                                                                                                                                                                                                                                                                                                                                                                                                       | Package Specifications                                                    | 65 |  |  |

# **Figures**

| 2-1 | Block Diagram of Intel® Atom <sup>TM</sup> Processor Z6xx Series Interfaces    | 10 |

|-----|--------------------------------------------------------------------------------|----|

|     | Interface Signal Diagram                                                       |    |

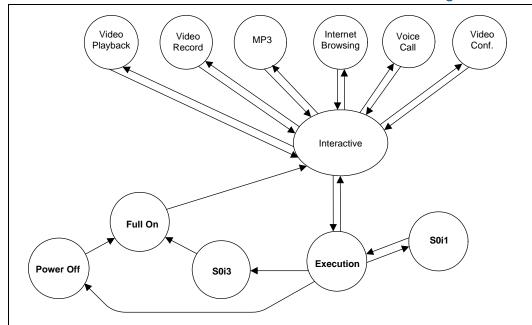

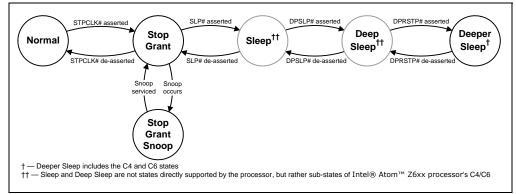

| 4-1 | Intel® Atom <sup>TM</sup> Processor Z6xx Series Power State Transition Diagram | 33 |

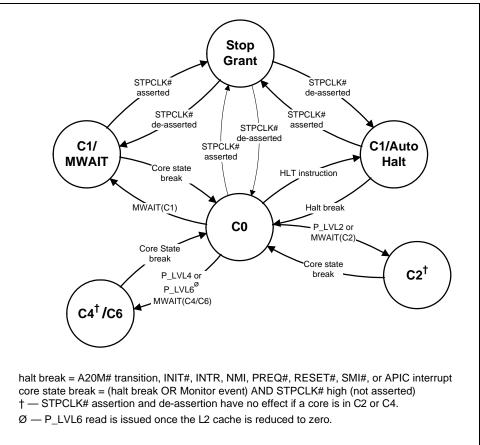

| 4-2 | Thread Low Power States                                                        | 34 |

| 4-3 | Package Low Power States                                                       | 34 |

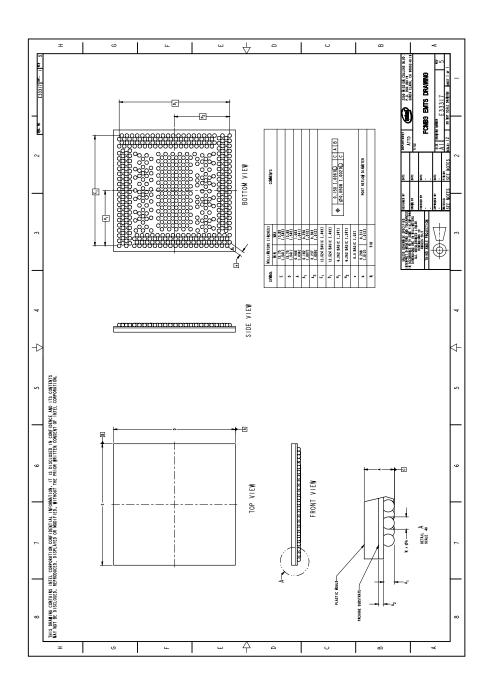

| 7-1 | Processor Package Drawing                                                      | 65 |

## **Tables**

| 2-1 Introduction—Acronyms               |    |

|-----------------------------------------|----|

| 3-1 Signal Descriptions—Acronyms        |    |

| 3-2 Buffer Types                        |    |

| 3-3 System Memory Interface Signals     |    |

| 3-4 cDMI Interface Signals              |    |

| 3-5 cDVO Interface Signals              |    |

| 3-6 LVDS Display Port Interface Signals |    |

| 3-7 MIPI Display Port Interface Signals |    |

| 3-8 LGI/LGIE Interface Signals          | 23 |

| 3-9 Debug and Miscellaneous Signals     | 25 |

| 4-1 Power Management—Acronyms           | 27 |

| 4-2 Voltage Rail Types                  |    |

| 4-3 Voltage Rail Descriptions           |    |

| 4-4 Voltage Rail States                 |    |

| 4-5 VIDEN Encoding                      |    |

| 4-6 VID Table                           |    |

| 4-7 Power States                        |    |

| 5-1  | Electrical Specifications—Acronyms                                                          | . 37 |

|------|---------------------------------------------------------------------------------------------|------|

| 5-2  | Electrical Specifications—Acronyms<br>Storage Conditions                                    | . 37 |

| 5-3  | Absolute Maximum Ratings                                                                    | . 38 |

| 5-4  | Voltage and Current Specifications for the Intel® Atom <sup>™</sup> Processors—             |      |

|      | Z600, Z610, Z612, and Z620                                                                  | . 40 |

| 5-5  | Voltage and Current Specifications for the Intel <sup>®</sup> Atom <sup>™</sup> Processors— |      |

|      | Z605, Z615, and Z625                                                                        | . 41 |

| 5-6  | Differential Clock DC Specifications                                                        | . 43 |

|      | AGTL+, CMOS, and CMOS Open Drain Signal Group DC Specifications                             |      |

| 5-8  | CMOS1.8 Signal Group DC Specifications                                                      | . 44 |

| 5-9  | LVDS Signal Group DC Specifications                                                         | . 44 |

| 5-10 | OMIPI Signal Group DC Specifications                                                        | . 45 |

| 6-1  | Thermal Specifications—Acronyms                                                             | . 47 |

| 6-2  | Package and Die Thermal Characteristics                                                     | . 48 |

| 6-3  | Power Specifications for Intel® Atom <sup>TM</sup> Processors—Z600, Z610, Z612, and Z620    | . 49 |

| 6-4  | Power Specifications for Intel® Atom <sup>TM</sup> Processors—Z605, Z615, and Z625          | . 49 |

| 6-5  | Support for PROCHOT#/THERMTRIP# in Active and Idle States                                   | . 52 |

| 7-1  | Processor Pin Out (Top View—Columns 21-31)                                                  | . 55 |

| 7-1  | Processor Pin Out (Top View—Columns 11-20)                                                  | . 56 |

|      | Processor Pin Out (Top View–Columns 1-10)                                                   |      |

|      | Pin Out—Ordered by Signal Name                                                              |      |

| Document<br>Number | Revision<br>Number | Description     | Revision Date |

|--------------------|--------------------|-----------------|---------------|

| 325567             | 001                | Initial release | May 2011      |

§§

# 1 Read Me First

# 1.1 Abstract

The Intel® Atom<sup>TM</sup> Processor Z6xx Series Datasheet describes the architecture, features, buffers, signal descriptions, power management, pin states, operating parameters, and specifications for the Intel® Atom<sup>TM</sup> processor Z6xx series.

# 1.2 Audience

The Intel® Atom<sup>TM</sup> Processor Z6xx Series Datasheet is intended for use by hardware developers who are designing and manufacturing products using the Intel® Atom<sup>TM</sup> processor Z6xx series.

# 1.3 Organization

The Intel® Atom<sup>TM</sup> Processor Z6xx Series Datasheet is composed of seven chapters that describe the Intel® Atom<sup>TM</sup> processor Z6xx series features, signal descriptions, power architecture, controller operation, and specifications. The datasheet is organized as follows;

- Chapter 1—"Read Me First"

- Chapter 2—"Introduction"

- Chapter 3—"Signal Descriptions"

- Chapter 4—"Power Management"

- Chapter 5—"Electrical Specifications"

- Chapter 6—"Thermal Specifications"

- Chapter 7—"Mechanical Package Specifications"

Chapters 2–7 contain a list of chapter contents and may contain a list of important acronyms and a description of the acronyms used in the chapter.

Some chapters also contain and architectural or functional overview that describes the design or operation of the Intel®  $Atom^{TM}$  processor Z6xx series.

# 1.4 Reference Documents

| Document                                                       | Document Number                                         | Notes |

|----------------------------------------------------------------|---------------------------------------------------------|-------|

| Intel® Platform Controller Hub MP30 Datasheet                  | 325565-001US                                            | 1     |

| Intel® 64 and IA-32 Architectures Software Developer's Manuals | http://www.intel.com/<br>products/processor/<br>manuals |       |

**NOTE:** <sup>1</sup>Contact your Intel representative for the latest revision and document number when obtaining these reference materials.

(This page intentionally left blank.)

# 2 Introduction

# 2.1 Chapter Contents

This chapter contains information about:

- "Acronyms"

- "Intel® Atom<sup>TM</sup> Processor Z6xx Series Architecture"

- "Intel® Atom<sup>TM</sup> Processor Z6xx Series Feature Set"

- "Intel® Atom<sup>TM</sup> Processor Z6xx Series Power Management"

- "External/Industry Standard Interfaces and Specifications"

## 2.2 Acronyms

Table 2-1 contains a list of acronyms used in this chapter.

#### Table 2-1. Introduction—Acronyms

| Acronym    | Description                                                                                                                       |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ACPI       | Advanced Control Programmable Interface                                                                                           |  |  |  |

| CMOS       | Complementary Metal-oxide Semiconductor                                                                                           |  |  |  |

| cDMI       | CMOS Direct Media Interface                                                                                                       |  |  |  |

| cDVO       | CMOS Digital Video Output                                                                                                         |  |  |  |

| FSB        | Front Side Bus                                                                                                                    |  |  |  |

| iFSB       | Internal Front Side Bus                                                                                                           |  |  |  |

| Lincroft   | Intel® Atom <sup>™</sup> Processor Z6xx Series                                                                                    |  |  |  |

| Langwell   | Intel® Platform Controller Hub MP30                                                                                               |  |  |  |

| LGI        | Legacy Interface                                                                                                                  |  |  |  |

| LVDS       | Low Voltage Differential Signaling, a high speed, low power data transmission standard used for display connections to LCD panels |  |  |  |

| MIPI       | Mobile Industry Processor Interface                                                                                               |  |  |  |

| MIPI D-PHY | MIPI Physical Layer Device                                                                                                        |  |  |  |

| MIPI-DCS   | MIPI Display Command Set                                                                                                          |  |  |  |

| MIPI-DSI   | MIPI Display Serial Interface                                                                                                     |  |  |  |

| РСН        | Intel® Platform Controller Hub MP30                                                                                               |  |  |  |

| PMIC       | Power Management Integrated Circuit                                                                                               |  |  |  |

| S0i1       | Intel® Smart Idle Technology (Intel® SIT) State 1                                                                                 |  |  |  |

| S0i3       | Intel® Smart Idle Technology (Intel® SIT) State 3                                                                                 |  |  |  |

| SIT        | Intel® Smart Idle Technology (Intel® SIT)                                                                                         |  |  |  |

| SPT        | Intel® Smart Power Technology (Intel® SPT)                                                                                        |  |  |  |

# 2.3 Intel® Atom<sup>TM</sup> Processor Z6xx Series Architecture

The Intel® Atom<sup>™</sup> processor Z6xx series is the next generation low power IA-32 processor that is based on the new re-partitioning architecture targeted for smart phones and tablets. The main components of the Intel® Atom<sup>™</sup> processor Z6xx series are: an IA-compatible processor core derived from the Intel® Atom<sup>™</sup> Z5xx Processor, a single-channel 32-bit DDR2 or LPDDR1 memory controller, a 3-D graphics engine, video decode and video encode engines, a display controller, a cDMI interface link to the Intel® Platform Controller Hub MP30, an LVDS or embedded MIPI interface to support a primary display interface link, and a cDVO interface link to the Intel® Platform Controller Hub MP30 to support an external display.

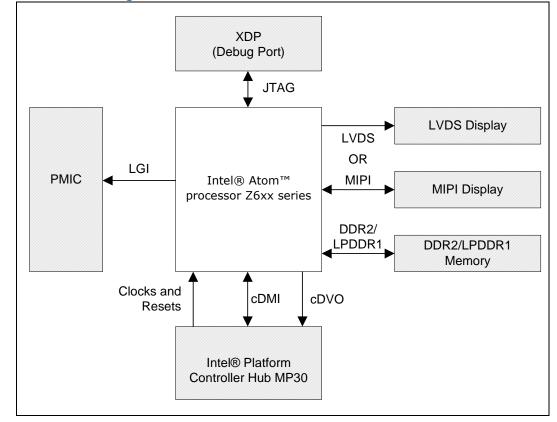

Figure 2-1. shows a block diagram of the main external interfaces for the Intel® Atom<sup>™</sup> processor Z6xx series.

#### Figure 2-1. Block Diagram of Intel® Atom<sup>TM</sup> Processor Z6xx Series Interfaces

# 2.4 Intel® Atom<sup>TM</sup> Processor Z6xx Series Feature Set

## 2.4.1 Intel® Atom<sup>TM</sup> Processor Z6xx Series Processor Core

- Supports macro-operation execution

- Supports Intel® Hyper-Threading Technology (Intel® HT Technology)

- Supports Enhanced Intel SpeedStep® Technology

- Supports Intel® Burst Performance Technology (Intel® BPT)

- Supports Intel® Smart Idle Technology (Intel® SIT)

- 2-wide instruction decode and in-order execution

- 32KB, 4-way L1 instruction cache

- 24KB, 6-way L1 data cache

- 512KB, 8 way L2 cache

- 32b physical address, 48b linear address size support

## 2.4.2 Memory Controller

The Intel® Atom<sup>™</sup> processor Z6xx series contains an integrated memory controller that supports DDR2 and LPDDR1 memory. The memory controller interface is fully configurable through a set of control registers. The following sections discuss the features of the integrated memory controller.

## 2.4.3 LPDDR1

- 32-bit data bus

- Supports 400 MT/s only

- Supports total memory size of up to 1GB

- Provides aggressive power management to reduce power consumption when idle

- Provides proactive page closing policies to close unused pages

### 2.4.4 DDR2

- 32-bit data bus

- Supports 800 MT/s only

- Supports total memory size of up to 2GB

- Provides aggressive power management to reduce power consumption when idle

- Provides proactive page closing policies to close unused pages

### 2.4.5 Intel® Graphics Media Accelerator 600 (Intel® GMA 600) Graphics

#### 2.4.5.1 3-D Graphics/Video Decode/Video Encode

- Up to 400 MHz graphics core frequency

- Supports OpenGL\* ES1.1

- Supports OpenGL\* ES2.0

- Supports OpenGL\* 2.1

- Supports OpenVG\* 1.1

- Supports hardware-accelerated HD video decode (MPEG4 part 2, H.264, WMV, and VC1)

- Supports hardware-accelerated HD video encode (MPEG4 part 2 and H.264)

### 2.4.5.2 Display Controller

- Seven display planes: Display Plane A, Display Plane B, Display C/sprite, Overlay, Cursor A, Cursor B, and VGA

- Display Pipe A: Supports LVDS or MIPI display interface

- Display Pipe B: cDVO pixel data link to the Intel  $\ensuremath{\mathbb{R}}$  Platform Controller Hub MP30 to support HDMI

- Supports 18 bpp and 24 bpp

- Supports Non-Power of 2 Tiling

- Output pixel width: 24-bit RGB

- Supports NV12 video data format

- Supports 3 x 3 panel fitter

- Dynamic Power Saving Technology (DPST) 3.0

- Support 16 x 256 byte tile size

- Supports overlay

- Supports global constant alpha blending

#### 2.4.5.3 MIPI-DSI

- Maximum resolution (internal display) of up to 1024 x 600

- Supports 1 or 2 lane operation

- Supports lane double data rates up to 400 Mbps in high speed (HS) mode

- Supports 24 bpp, 18 bpp packed and 18 bpp loosely packed pixel formats

- Display Pixel Interface (DPI) for video-mode displays

- Supports bi-directional low power (LP) mode on Lane 0 for display-to-host communications

- Supports ECC in both directions

#### 2.4.5.4 LVDS

- Maximum resolution (internal display) of up to 1366 x 768

- Dot clock range from 20–83 MHz

- Five differential signal pairs—Four data pairs (up to 581 Mbps on each data link) and one clock pair

- Supports 24 bpp, 18 bpp packed, and 18 bpp loosely packed pixel formats

### 2.4.6 cDMI

- The data interface between the Intel® Atom<sup>™</sup> processor Z6xx series and the Intel® Platform Controller Hub MP30

- Peak raw BW of cDMI link per direction is 400 MT/s using a quad-pumped, 8-bit transmit and an 8-bit receive data bus

- Supports low power management schemes

- Supports CMOS signaling technology

## 2.4.7 cDVO

- The unidirectional display data link interface from the Intel® Atom<sup>™</sup> processor Z6xx series to the Intel® Platform Controller Hub MP30

- Peak raw BW of cDVO is 400 MT/s for Intel® Atom<sup>™</sup> Processors Z600, Z610, Z612, and Z620 and 800 MT/s for Intel® Atom<sup>™</sup> Processors Z605, Z615, and Z625 using a quad-pumped, 6-bit transmit data bus

- Supports low power management schemes

- Supports CMOS signaling technology for Intel® Atom<sup>™</sup> Processors Z600, Z610, Z612, and Z620 and AGTL+ signaling technology for Intel® Atom<sup>™</sup> processors Z605, Z615, and Z625

## 2.4.8 LGI/LGIE/Debug

- Thermal sensing

- Legacy control signals

- JTAG debug port

# 2.5 Intel® Atom<sup>TM</sup> Processor Z6xx Series Power Management

The Intel® Atom<sup>™</sup> processor Z6xx series supports fine grain power management by having several partitions of voltage islands created through on-die power switches. The Intel® Smart Power Technology (Intel® SPT) software determines the most power efficient state for the platform at any given point in time and then provides guidance to turn ON or OFF different voltage islands on the processor. For the scenario where Intel® SPT has directed the processor to go into an Intel® SIT idle mode, the processor waits for all partitions with shared voltage to reach a safe point and then turns them off.

## 2.5.1 Intel<sup>®</sup> Burst Performance Technology (Intel<sup>®</sup> BPT)

The Intel® Atom<sup>™</sup> processor Z6xx series processor core supports ACPI Performance States (P-states). The P-state referred to as P0 will be a request for Intel® Burst Performance Technology (Intel® BPT). Intel® BPT opportunistically and automatically, allows the processor to run faster than the marked frequency if the part is operating within the thermal design limits of the platform. Intel® BPT can be enabled or disabled by IA-32 firmware.

## 2.5.2 Intel<sup>®</sup> Smart Idle Technology (Intel<sup>®</sup> SIT)

The Intel® Atom<sup>™</sup> processor Z6xx series is targeted to deliver always on, always connected, standby power with the use of Intel® Smart Idle Technology (Intel® SIT). Intel® SIT enables the processor to enter its lowest supported idle power states, S0i1 and S0i3, which greatly increases system standby time. The OS manages entry and exit of S0i1 and S0i3 power states through the Intel® SPT.

# 2.6 External/Industry Standard Interfaces and Specifications

The Intel® Atom  $\ensuremath{^{\text{M}}}$  processor Z6xx series adheres to the following external specifications:

- JEDEC JESD79-2E (DDR2)

- JEDEC JESD209 (LPDDR1)

- TIA/EIA-644A (LVDS)

- MIPI DPHY, Revision 0.9

- MIPI DSI, Revision 1.01.00, Release 09

- MIPI DCS, Revision 1.01.00, June 2006

§

# 3 Signal Descriptions

# 3.1 Chapter Contents

This chapter contains information about:

- "Acronyms"

- "Buffer Types"

- "Signal Description"

# 3.2 Acronyms

Table 3-1 below contains a list of acronyms used in this chapter.

#### Table 3-1. Signal Descriptions—Acronyms

| Acronym | Description                             |  |

|---------|-----------------------------------------|--|

| ACPI    | Advanced Control Programmable Interface |  |

| AGTL+   | Assisted Gunning Transceiver Logic Plus |  |

| CKE     | Clock Enable                            |  |

| DQ      | Memory data                             |  |

| DQS     | Memory data strobe                      |  |

| GPIO    | General Purpose Input/Output            |  |

| HPLL    | Host Phase Lock Loop                    |  |

| IERR    | Internal Error                          |  |

| РСН     | Intel® Platform Controller Hub MP30     |  |

| LP Mode | Low Power Mode                          |  |

| NMI     | Non-Maskable Interrupt                  |  |

| PMIC    | Power Management Integrated Circuit     |  |

| SCK     | System Clock                            |  |

| ТАР     | Test Access Point                       |  |

# **3.3 Buffer Types**

### Table 3-2.Buffer Types

| Buffer Type   | Interface             | Description                                                                                                                            |

|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| AGTL+         | cDVO                  | Assisted Gunning Transceiver Logic Plus:<br>CMOS open drain interface signals that require<br>termination.                             |

| CMOS, CMOS_OD | cDMI, cDVO, LGI, LGIE | 1.05V CMOS buffer or CMOS open drain                                                                                                   |

| Analog        | All                   | <b>Analog reference or output</b> : This may be used as a threshold voltage or for buffer compensation.                                |

| MIPI          | MIPI                  | <b>MIPI buffers</b> : Support HSTX, LPTX, and LPRX modes.                                                                              |

| LVDS          | LVDS                  | <b>Low-Voltage Differential Signal output</b><br><b>buffers:</b> These should drive across a $100-\Omega$<br>resistor at the receiver. |

| CMOS1.8       | DDR2/LPDDR1           | <b>1.8V CMOS buffer</b> : These buffers can be configured as Stub Series Termination Logic.                                            |

| F             | Power Signals         | <b>Fixed</b> : The voltage level is fixed to be a certain value based on the I/O family.                                               |

| AON           | Power Signals         | <b>Always ON:</b> The voltage level must always be on for the component to operate safely, reliably, and deterministically.            |

| S             | Power Signals         | Selectable: The voltage can be selected at the platform level.                                                                         |

| V             | Power Signals         | Variable: Variable supplies are negotiable supply levels.                                                                              |

# 3.4 Signal Description

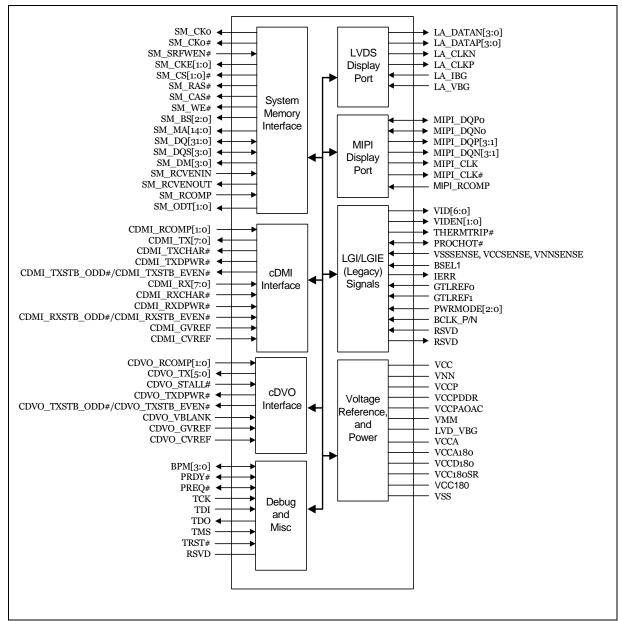

This section provides a detailed description of the Intel® Atom<sup>™</sup> processor Z6xx series signals. The signals are arranged in functional groups according to their associated interface (see Figure 3-1).

#### Figure 3-1. Interface Signal Diagram

# 3.4.1 System Memory Interface

## Table 3-3. System Memory Interface Signals (Sheet 1 of 2)

| Signal      | Direction<br>Type | Power<br>Rail            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|-------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SM_ODT[1:0] | O<br>CMOS1.8      | V <sub>CC180</sub>       | <b>On-Die termination enable</b> : Enables the use of<br>on-die termination on the DDRIO and memory devices<br>for data and strobes when asserted. When the ODT<br>feature is enabled, ODT is dynamically enabled for the<br>receiver of the data. The processor does this internally<br>for read data returning from the DRAM devices. For<br>write data to the DRAM devices, the SM_ODT[1:0] pins<br>are asserted to enable ODT within the DRAM devices<br>themselves. For dual rank memory configurations<br>using x8 devices, ODT must be enabled. |

| SM_CK0      | O<br>CMOS1.8      | V <sub>CC180</sub>       | <b>Differential DDR clock</b> : The crossing of the positive edge of SM_CK0 and the negative edge of SM_CK0# is used to sample the address and control signals on memory.                                                                                                                                                                                                                                                                                                                                                                              |

| SM_CK0#     | O<br>CMOS1.8      | V <sub>CC180</sub>       | Complementary differential DDR clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SM_SREN#    | I<br>CMOS1.8      | V <sub>CC180S</sub><br>R | <b>SOi3 self-refresh enable</b> : Signal from the Intel® Platform Controller Hub MP30 asserted after the processor places DDR in self-refresh and sends an acknowledgement of SOi3 to the Intel® Platform Controller Hub MP30.                                                                                                                                                                                                                                                                                                                         |

| SM_CKE[1:0] | O<br>CMOS1.8      | V <sub>CC180S</sub><br>R | <b>Clock enable</b> : SM_CKE is used for power control of the DRAM devices. There is one SM_CKE per rank.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SM_CS[1:0]# | O<br>CMOS1.8      | V <sub>CC180</sub>       | <b>Chip select:</b> These signals determine whether a command is valid in a given cycle for the devices connected to it. There is one chip select signal for each rank.                                                                                                                                                                                                                                                                                                                                                                                |

| SM_RAS#     | O<br>CMOS1.8      | V <sub>CC180</sub>       | <b>Row address strobe</b> : This signal is used with SM_CAS# and SM_WE# (along with SM_CS#) to define commands.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SM_CAS#     | O<br>CMOS1.8      | V <sub>CC180</sub>       | <b>Column address strobe</b> : This signal is used with SM_WE#, SM_RAS#, and SM_CS# to define commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SM_WE#      | O<br>CMOS1.8      | V <sub>CC180</sub>       | Write enable: This signal is used with SM_CAS#, SM_RAS#, and SM_CS# to define commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SM_BS[2:0]  | O<br>CMOS1.8      | V <sub>CC180</sub>       | <b>Bank select</b> : These signals define which banks are being addressed within each Rank.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SM_MA[14:0] | O<br>CMOS1.8      | V <sub>CC180</sub>       | Multiplexed address: SM_MA signals provide multiplexed row and column address to memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SM_DQ[31:0] | I/O<br>CMOS1.8    | V <sub>CC180</sub>       | <b>Data lines:</b> SM_DQ signals interface to the DRAM data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## Table 3-3. System Memory Interface Signals (Sheet 2 of 2)

| Signal      | Direction<br>Type | Power<br>Rail      | Description                                                                                                                                                                                                                                                                                                                                                            |

|-------------|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SM_DQS[3:0] | I/O<br>CMOS1.8    | V <sub>CC180</sub> | Data strobes: These signals are used during writes<br>and are centered with respect to data. During read,<br>these signals are driven by memory devices and are<br>edge aligned with data. The following list matches the<br>data strobe with the data bytes.<br>SM_DQS3 -> SM_DQ[31:24]<br>SM_DQS2 -> SM_DQ[23:16]<br>SM_DQS1 -> SM_DQ[15:8]<br>SM_DQS0 -> SM_DQ[7:0] |

| SM_DM[3:0]  | O<br>CMOS1.8      | V <sub>CC180</sub> | <b>Data mask:</b> One bit per byte indicating which bytes should be written.                                                                                                                                                                                                                                                                                           |

| SM_RCVENIN  | I<br>CMOS1.8      | V <sub>CC180</sub> | <b>Receive enable in</b> : This signal connects to SM_RCVENOUT on the motherboard. This input enables the SM_DQS input buffers during reads.                                                                                                                                                                                                                           |

| SM_RCVENOUT | O<br>CMOS1.8      | V <sub>CC180</sub> | <b>Receive enable out:</b> This signal connects to SM_RCVENIN on the motherboard. Part of the feedback used to enable the DQS input buffers during reads.                                                                                                                                                                                                              |

| SM_RCOMP    | I<br>Analog       | V <sub>CC180</sub> | <b>RCOMP</b> : This signal connects externally to a high-<br>precision reference resistor on the board to<br>dynamically calibrate the driver strengths.                                                                                                                                                                                                               |

## 3.4.2 cDMI Interface

#### Table 3-4. cDMI Interface Signals

| Signal                               | Direction<br>Type | Power<br>Rail    | Description                                                                                                                                                            |

|--------------------------------------|-------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDMI_RCOMP[1:0]                      | I<br>Analog       | V <sub>CCP</sub> | <b>CDMI_RCOMP</b> : Connected to high-precision resistors on the motherboard. Used for compensating DMI pull-up/pull-down impedances.                                  |

| CDMI_TX[7:0]                         | O<br>CMOS         | V <sub>CCP</sub> | <b>Data output</b> : Quad-pumped (strobed) data bus from the processor to the Intel® Platform Controller Hub MP30.                                                     |

| CDMI_TXCHAR#                         | O<br>CMOS         | V <sub>CCP</sub> | Data control character data control<br>character output: Quad-pumped (strobed)<br>indication that CDMI_TX[7:0] contains a control<br>character instead of data.        |

| CDMI_TXDPWR#                         | O<br>CMOS         | V <sub>CCP</sub> | Line wakeup for output: When asserted, the<br>Intel® Platform Controller Hub MP30 will power-<br>up its receivers on CDMI_TX[7:0],<br>CDMI_TXCHAR#, and CDMI_TXSTB[0]. |

| CDMI_TXSTB_ODD#,<br>CDMI_TXSTB_EVEN# | 0<br>CMOS         | V <sub>CCP</sub> | <b>Data strobe output</b> : Strobes for CDMI_TX[7:0] and CDMI_TXCHAR#.                                                                                                 |

| CDMI_RX[7:0]                         | I<br>CMOS         | V <sub>CCP</sub> | <b>Data input</b> : Quad-pumped (strobed) data bus from the Intel® Platform Controller Hub MP30 to the processor.                                                      |

| CDMI_RXCHAR#                         | I<br>CMOS         | V <sub>CCP</sub> | <b>Data control character input</b> : Quad-pumped (strobed) indication that CDMI_RX[7:0] contains a control character instead of data.                                 |

| CDMI_RXDPWR#                         | I<br>CMOS         | V <sub>CCP</sub> | Line wakeup for input: Power enable from the Intel® Platform Controller Hub MP30. Used to enable Receivers on CDMI_RX[7:0], CDMI_RXCHAR#, and CDMI_RXSTB_ODD#.         |

| CDMI_RXSTB_ODD#,<br>CDMI_RXSTB_EVEN# | I<br>CMOS         | V <sub>CCP</sub> | Data strobe input: Strobes for CDMI_RX[7:0] and CDMI_RXCHAR#.                                                                                                          |

| CDMI_GVREF                           | I<br>Analog       | V <sub>CCP</sub> | Strobe signals reference voltage for CDMI: Externally set by means of a passive voltage divider. Voltage should be $1/2 V_{CCP}$ when configured for CMOS.             |

| CDMI_CVREF                           | I<br>Analog       | V <sub>CCP</sub> | Non-strobe signals reference voltage for CDMI: Externally set by means of a passive voltage divider. Voltage should be $1/2 V_{CCP}$ when configured for CMOS.         |

## 3.4.3 cDVO Interface

#### Table 3-5. cDVO Interface Signals

| Signal                               | Direction<br>Type  | Power<br>Rail    | Description                                                                                                                                                                                                        |

|--------------------------------------|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDVO_RCOMP[1:0]                      | I<br>Analog        | V <sub>CCP</sub> | <b>CDVO_RCOMP</b> : Connected to high-precision resistors on the motherboard. Used for compensating pull-up/pull-down impedances.                                                                                  |

| CDVO_TX[5:0]                         | O<br>AGTL+<br>CMOS | V <sub>CCP</sub> | Data output: Quad-pumped (strobed) data bus from the processor to the Intel® Platform Controller Hub MP30.                                                                                                         |

| CDVO_STALL#                          | I<br>AGTL+<br>CMOS | V <sub>CCP</sub> | <b>Stall</b> : Allows the Intel® Platform Controller Hub MP30 to throttle the sending of display data.                                                                                                             |

| CDVO_TXDPWR#                         | O<br>AGTL+<br>CMOS | V <sub>CCP</sub> | Line wakeup for output: When asserted, the Intel® Platform Controller Hub MP30 will power-<br>up its receivers on CDVO_TX[5:0] and CDVO_TXSTB_ODD#.                                                                |

| CDVO_TXSTB_ODD#,<br>CDVO_TXSTB_EVEN# | O<br>AGTL+<br>CMOS | V <sub>CCP</sub> | Data strobe output: Strobes for CDVO_TX[5:0].                                                                                                                                                                      |

| CDVO_VBLANK#                         | I<br>AGTL+<br>CMOS | V <sub>CCP</sub> | <b>Vertical blank</b> : Indication from the Intel®<br>Platform Controller Hub MP30 indicating the start<br>of the vertical blank period.                                                                           |

| CDVO_GVREF                           | I<br>Analog        | V <sub>CCP</sub> | Strobe signals reference voltage for CDVO:<br>Externally set by means of a passive voltage<br>divider. Voltage should be 2/3 $V_{CCP}$ when<br>configured for AGTL+ and 1/2 $V_{CCP}$ when<br>configured for CMOS. |

| CDVO_CVREF                           | I<br>Analog        | V <sub>CCP</sub> | Non-strobe signals reference voltage for CDVO: Externally set by means of a passive voltage divider. Voltage should be $2/3 V_{CCP}$ when configured for AGTL+ and $1/2 V_{CCP}$ when configured for CMOS.         |

NOTE: The cDVO interface is configured to support CMOS signaling technology for Intel® Atom<sup>™</sup> Processors Z600, Z610, Z612, Z620, and AGTL+ signaling technology for Intel® Atom<sup>™</sup> Processors Z605, Z615, and Z625.

## 3.4.4 LVDS Display Port Interface

#### Table 3-6. LVDS Display Port Interface Signals

| Signal        | Direction<br>Type | Power<br>Rail                                             | Description                                                                                                                      |

|---------------|-------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| LA_DATAN[3:0] | 0<br>LVDS         | V <sub>CCD180</sub> ,<br>V <sub>CCA180</sub>              | Differential data output (Negative)                                                                                              |

| LA_DATAP[3:0] | 0<br>LVDS         | V <sub>CCD180</sub> ,<br>V <sub>CCA180</sub>              | Differential data output (Positive)                                                                                              |

| LA_CLKN       | 0<br>LVDS         | V <sub>CCD180</sub> ,<br>V <sub>CCA180</sub>              | Differential clock output (Negative)                                                                                             |

| LA_CLKP       | 0<br>LVDS         | V <sub>CCD180</sub> ,<br>V <sub>CCA180</sub>              | Differential clock output (Positive)                                                                                             |

| LA_IBG        | I<br>Analog       | V <sub>CCD180</sub> ,<br>V <sub>CCA180</sub>              | <b>External voltage reference BG</b> : Connected to high-precision ( $\pm 1\%$ ) 2.43 K $\Omega$ resistor on motherboard to VSS. |

| LA_VBG        | I<br>Analog       | V <sub>CCD180</sub> ,<br>V <sub>CCA180</sub> ,<br>LVD_VBG | External voltage reference BG: Requires external 1.25V ±2% supply.                                                               |

# 3.4.5 MIPI Display Port Interface

Table 3-7.

MIPI Display Port Interface Signals

| Signal        | Direction   | Power<br>Rail   | Description                                                                                                     |  |

|---------------|-------------|-----------------|-----------------------------------------------------------------------------------------------------------------|--|

| MIPI_DQP0     | I/O<br>MIPI | V <sub>MM</sub> | Data (positive): Differential, bi-directional in LP mode                                                        |  |

| MIPI_DQN0     | I/O<br>MIPI | V <sub>MM</sub> | Data (negative): Differential, bi-directional in LP mode                                                        |  |

| MIPI_DQP[3:1] | O<br>MIPI   | V <sub>MM</sub> | Data (positive): Differential output only                                                                       |  |

| MIPI_DQN[3:1] | O<br>MIPI   | V <sub>MM</sub> | Data (negative): Differential output only                                                                       |  |

| MIPI_CLK      | O<br>MIPI   | V <sub>MM</sub> | Clock (positive): Differential                                                                                  |  |

| MIPI_CLK#     | O<br>MIPI   | V <sub>MM</sub> | Clock (negative): Differential                                                                                  |  |

| MIPI_RCOMP    | I<br>Analog | V <sub>MM</sub> | <b>RCOMP:</b> Connected to a high-precision resistor<br>on the motherboard. Used for impedance<br>compensation. |  |

# 3.4.6 LGI/LGIE (Legacy) Interface

## Table 3-8. LGI/LGIE Interface Signals (Sheet 1 of 2)

| Signal                             | Direction<br>Type               | Power<br>Rail                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------|---------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VID[6:0]                           | O<br>CMOS                       | V <sub>CCP</sub>                                       | <b>Voltage ID</b> : Connects to PMIC. Indicates a desired voltage for either $V_{CC}$ or $V_{NN}$ depending on the VIDEN[1:0] pins. Resolution of 12.5 mV.                                                                                                                                                                                                                                                                                                                                      |

| VIDEN[1:0]                         | O<br>CMOS                       | Vccpaoac                                               | Voltage ID enable: Connects to PMIC.<br>Indicates which voltage is being specified on<br>the VID pins:<br>00 = VID is invalid<br>$01 = VID = V_{CC}$<br>$10 = VID = V_{NN}$<br>11 = RSVD                                                                                                                                                                                                                                                                                                        |

| THERMTRIP#                         | O<br>CMOS_OD                    | V <sub>CCPAOAC</sub>                                   | <b>Catastrophic thermal trip:</b> The processor<br>protects itself from catastrophic overheating by<br>use of an internal thermal sensor. This sensor is<br>set well above the normal operating<br>temperature to ensure that there are no false<br>trips. The processor will stop all execution<br>when the junction temperature exceeds the trip<br>point. This condition is signaled to the system<br>by the THERMTRIP# (Thermal Trip) pin.                                                  |

| PROCHOT#                           | I/O<br>O:<br>CMOS_OD<br>I: CMOS | Vccpaoac                                               | <b>Processor hot:</b> As an output, PROCHOT#<br>(processor hot) will go active when the<br>processor temperature monitoring sensor<br>detects that the processor has reached its<br>maximum safe operating temperature. This<br>indicates that the processor Thermal Control<br>Circuit (TCC) has been activated, if enabled.<br>As an input, assertion of PROCHOT# by the<br>system will activate the TCC, if enabled. The<br>TCC will remain active until the system de-<br>asserts PROCHOT#. |

| VSSSENSE,<br>VCCSENSE,<br>VNNSENSE | I<br>Analog                     | V <sub>SS</sub> , V <sub>CC</sub> ,<br>V <sub>NN</sub> | Voltage sense: Connects to PMIC. Voltage Regulator must connect feedback lines for V <sub>CC</sub> , V <sub>SS</sub> , and V <sub>NN</sub> to these pins on the package.                                                                                                                                                                                                                                                                                                                        |

| BSEL1                              | O<br>CMOS                       | V <sub>CCP</sub>                                       | <b>BSEL1</b> : Selects external reference clock for<br>DDR, cDMI, and cDVO frequencies.<br>1 = Reserved<br>0 = 100 MHz, for cDMI/cDVO/LPDDR1 at<br>400 MT/s or cDVO/DDR2 at 800 MT/s.                                                                                                                                                                                                                                                                                                           |

| Table 3-8. | LGI/LGIE | Interface Signals | (Sheet 2 of 2) |

|------------|----------|-------------------|----------------|

|------------|----------|-------------------|----------------|

| Signal       | Direction<br>Type | Power<br>Rail        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|-------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IERR         | O<br>CMOS         | V <sub>CCP</sub>     | IERR: Internal error indication (debug).<br>Positively asserted. Asserted when the<br>processor has had an internal error and may<br>have unexpectedly stopped executing.<br>Assertion of IERR is usually accompanied by a<br>SHUTDOWN transaction internal to the<br>processor which may result in assertion of Non-<br>Maskable Interrupt (NMI) to the processor. The<br>processor will keep IERR asserted until the<br>PWRMODE[2:0] pins take the processor to<br>reset or the processor receives a reset<br>message over cDMI.<br>PWRMODE[2:0]<br>M0, M1, M2, M3<br>M5, M7, M6, M4 |

| GTLREF0      | I<br>Analog       | V <sub>CCP</sub>     | Voltage reference for BPM[3:0]#: 2/3 V <sub>CCP</sub> by means of an external voltage divider: 1 K $\Omega$ to V <sub>CCP</sub> , 2 K $\Omega$ to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GTLREF1      | I<br>Analog       | V <sub>CCP</sub>     | Voltage reference: 2/3 V <sub>CCP</sub> by means of external voltage divider: 1 K $\Omega$ to V <sub>CCP</sub> , 2 K $\Omega$ to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PWRMODE[2:0] | I<br>CMOS         | V <sub>CCPAOAC</sub> | <b>Power mode</b> : The Intel® Platform Controller<br>Hub MP30 is expected to sequence the<br>processor through various states using the<br>PWRMODE[2:0] pins to facilitate cold reset,<br>warm reset, and S0i3 entry and exit.                                                                                                                                                                                                                                                                                                                                                        |

| BCLK_P/N     | I<br>CMOS         | V <sub>CCP</sub>     | Reference clock: Differential 100 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# 3.4.7 Debug and Miscellaneous

## Table 3-9. Debug and Miscellaneous Signals

| Signal    | Direction<br>Type | Power<br>Rail    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|-------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BPM[3:0]# | I/O<br>AGTL+      | V <sub>CCP</sub> | Break/perf monitor: Various debug input and output functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PRDY#     | I/O<br>AGTL+      | V <sub>CCP</sub> | <b>Probe mode ready</b> : The processor's response to<br>a PRDY# assertion. This signal indicates that the<br>processor is in probe mode. Input is unused.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PREQ#     | I/O<br>AGTL+      | V <sub>CCP</sub> | <b>Probe mode request</b> : Assertion is a request for the processor to enter probe mode. Processor will respond with PRDY# assertion once it has entered. PREQ# can be enabled to cause the processor to break from C4 and C6. Internal 56 $\Omega$ pull up.                                                                                                                                                                                                                                                                                                                |

| ТСК       | I<br>CMOS         | V <sub>CCP</sub> | <b>Processor JTAG test clock</b> : This signal provides the clock input for the processor Test Bus (also known as the Test Access Port).                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TDI       | I<br>CMOS         | V <sub>CCP</sub> | <b>Processor JTAG test data input</b> : This signal transfers serial test data into the processor. TDI provides the serial input needed for JTAG specification support.                                                                                                                                                                                                                                                                                                                                                                                                      |

| TDO       | O<br>OD           | V <sub>CCP</sub> | <b>Processor JTAG test data output</b> : This signal transfers serial test data out of the processor. TDO provides the serial output needed for JTAG specification support.                                                                                                                                                                                                                                                                                                                                                                                                  |

| TMS       | I<br>CMOS         | V <sub>CCP</sub> | <b>Processor JTAG test mode select</b> : A JTAG specification support signal used by debug tools.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TRST#     | I<br>CMOS         | V <sub>CCP</sub> | <b>Processor JTAG test reset:</b> Asynchronously<br>resets the Test Access Port (TAP) logic. TRST#<br>must be driven asserted (low) during processor<br>power on reset.<br>The Intel® Atom <sup>TM</sup> processor Z6xx series has an<br>internal 56 $\Omega$ pull-up to V <sub>CCP</sub> , unlike the Intel®<br>Pentium® M Processor, the Intel® Core <sup>TM</sup> 2 Duo<br>Processor, and the Intel® Atom <sup>TM</sup> Z5xx<br>Processor. The Intel® Atom <sup>TM</sup> Processor Z6xx<br>pull-up matches the Intel® Pentium® 4<br>Processor and the IEEE specification. |

| RSVD      |                   |                  | These pins should be treated as no connection (NC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

§

(This page intentionally left blank.)

# 4 Power Management

# 4.1 Chapter Contents

This chapter contains information about:

- "Acronyms"

- "Processor Voltage Rails"

- "Processor Voltage Rail States"

- "VCC/VNN VID Control"

- "Valid Power States"

- "Processor Core Low Power Features"

# 4.2 Acronyms

Table 4-1 contains a list of acronyms used in this chapter.

Table 4-1.

Power Management—Acronyms

| Acronym       | Description                                                                                                                                    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| North Complex | The Intel® Atom <sup>™</sup> processor Z6xx series unicore which includes the memory controller, Power Management Unit, and internal FSB Logic |

| PMU           | Power Management Unit                                                                                                                          |

| RCOMP         | Resistor Compensation                                                                                                                          |

| S0i1          | Intel® Smart Idle Technology (Intel® SIT) State 1                                                                                              |

| S0i3          | Intel® Smart Idle Technology (Intel® SIT) State 3                                                                                              |

| SIT           | Intel® Smart Idle Technology (Intel® SIT)                                                                                                      |

| SPT           | Intel® Smart Power Technology (Intel® SPT)                                                                                                     |

| SR            | Self-Refresh                                                                                                                                   |

# 4.3 Processor Voltage Rails

#### Table 4-2. Voltage Rail Types

| Buffer Type | Description                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------|

| F           | Fixed: Voltage level is fixed to be a certain value based on the I/O family.                                               |

| AON         | <b>Always ON:</b> The voltage level must always be on for the component to operate safely, reliably and deterministically. |

| S           | Selectable: Voltage can be selected at the platform level                                                                  |

| V           | Variable: Variable supplies are negotiable supply levels                                                                   |

#### Table 4-3. Voltage Rail Descriptions

| Voltage Rail<br>Name             | Rail<br>Type | Description                            | Active Power<br>States |

|----------------------------------|--------------|----------------------------------------|------------------------|

| V <sub>CC</sub>                  | V            | Core CPU                               | S0                     |