# Intel<sup>®</sup> Core<sup>™</sup>2 Duo Processor, Intel<sup>®</sup> Pentium<sup>®</sup> Dual Core Processor, and Intel<sup>®</sup> Celeron<sup>®</sup> Dual-Core Processor

**Thermal and Mechanical Design Guidelines**

#### Supporting the:

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo Processor E6000<sup>△</sup> and E4000<sup>△</sup> Series

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual Core Processor E2000<sup>A</sup> Series

- Intel<sup>®</sup> Celeron<sup>®</sup> Dual-Core Processor E1000<sup>△</sup> Series

June 2009

Document Number: 317804-011

THIS DOCUMENT AND RELATED MATERIALS AND INFORMATION ARE PROVIDED "AS IS" WITH NO WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE. INTEL ASSUMES NO RESPONSIBILITY FOR ANY ERRORS CONTAINED IN THIS DOCUMENT AND HAS NO LIABILITIES OR OBLIGATIONS FOR ANY DAMAGES ARISING FROM OR IN CONNECTION WITH THE USE OF THIS DOCUMENT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel may make changes to specifications and product descriptions at any time, without notice. Intel accepts no duty to update specifications or product descriptions with information. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The hardware vendor remains solely responsible for the design, sale and functionality of its product, including any liability arising from product infringement or product warranty. Intel provides this information for customer's convenience only. Use at your own risk. Intel accepts no liability for results if customer chooses at its discretion to implement these methods within its business operations. Intel makes no representations or warranties regarding the accuracy or completeness of the information provided.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting <a href="http://www.intel.com">http://www.intel.com</a>.

The Intel® Core™2 Duo processor, Intel® Pentium® Dual Core processor and Intel® Pentium® 4 processor may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

<sup>a</sup>Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. Over time processor numbers will increment based on changes in clock, speed, cache, FSB, or other features, and increments are not intended to represent proportional or quantitative increases in any particular feature. Current roadmap processor number progression is not necessarily representative of future roadmaps. See www.intel.com/products/processor\_number for details.

Intel, Pentium, Core, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2007–2009 Intel Corporation

# **Contents**

| 1 | Introd | duction                                                                         | 11 |

|---|--------|---------------------------------------------------------------------------------|----|

|   | 1.1    | Document Goals and Scope                                                        |    |

|   |        | 1.1.2 Document Goals                                                            |    |

|   |        | 1.1.3 Document Scope                                                            |    |

|   | 1.2    | References                                                                      |    |

|   | 1.3    | Definition of Terms                                                             |    |

| 2 | Proce  | ssor Thermal/Mechanical Information                                             | 15 |

|   | 2.1    | Mechanical Requirements                                                         | 15 |

|   |        | 2.1.1 Processor Package                                                         | 15 |

|   |        | 2.1.2 Heatsink Attach                                                           |    |

|   | 2.2    | Thermal Requirements                                                            | 18 |

|   |        | 2.2.1 Processor Case Temperature                                                | 18 |

|   |        | 2.2.2 Thermal Profile                                                           |    |

|   |        | 2.2.3 T <sub>CONTROL</sub>                                                      | 20 |

|   | 2.3    | Heatsink Design Considerations                                                  | 21 |

|   |        | 2.3.1 Heatsink Size                                                             | 22 |

|   |        | 2.3.2 Heatsink Mass                                                             | 22 |

|   |        | 2.3.3 Package IHS Flatness                                                      |    |

|   |        | 2.3.4 Thermal Interface Material                                                |    |

|   | 2.4    | System Thermal Solution Considerations                                          | 24 |

|   |        | 2.4.1 Chassis Thermal Design Capabilities                                       | 24 |

|   |        | 2.4.2 Improving Chassis Thermal Performance                                     | 24 |

|   |        | 2.4.3 Summary                                                                   |    |

|   | 2.5    | System Integration Considerations                                               | 25 |

| 3 | Thern  | nal Metrology                                                                   | 27 |

|   | 3.1    | Characterizing Cooling Performance Requirements                                 | 27 |

|   |        | 3.1.1 Example                                                                   | 28 |

|   | 3.2    | Processor Thermal Solution Performance Assessment                               | 29 |

|   | 3.3    | Local Ambient Temperature Measurement Guidelines                                | 29 |

|   | 3.4    | Processor Case Temperature Measurement Guidelines                               |    |

| 4 |        |                                                                                 |    |

| 4 | 4.1    | nal Management Logic and Thermal Monitor Feature<br>Processor Power Dissipation |    |

|   |        | ·                                                                               |    |

|   | 4.2    | Thermal Monitor Implementation                                                  |    |

|   |        | 4.2.1 PROCHOT# Signal                                                           |    |

|   |        | 4.2.2 Thermal Control Circuit                                                   |    |

|   |        | 4.2.3 Thermal Monitor 2                                                         | 35 |

|   |        | 4.2.5 On-Demand Mode                                                            |    |

|   |        | 4.2.6 System Considerations                                                     |    |

|   |        | 4.2.7 Operating System and Application Software Considerations                  |    |

|   |        | 4.2.8 THERMTRIP# Signal                                                         |    |

|   |        | 4.2.9 Cooling System Failure Warning                                            | 38 |

|   |        | 5 3                                                                             |    |

|            |        | 4.2.10<br>4.2.11                             | Digital Thermal SensorPlatform Environmental Control Interface (PECI)                    |                            |

|------------|--------|----------------------------------------------|------------------------------------------------------------------------------------------|----------------------------|

| 5          | Balanc | ed Techn                                     | ology Extended (BTX) Thermal/Mechanical Design Information                               | 41                         |

|            | 5.1    | Overview 5.1.1 5.1.2 5.1.3 5.1.4 5.1.5 5.1.6 | w of the Balanced Technology Extended (BTX) Reference Design Target Heatsink Performance | 41<br>42<br>44<br>45<br>46 |

|            | 5.2    | Environr<br>5.2.1<br>5.2.2<br>5.2.3          | mental Reliability Testing                                                               | 46<br>49                   |

|            | 5.3    | Material                                     | and Recycling Requirements                                                               | 49                         |

|            | 5.4    | -                                            | Requirements                                                                             |                            |

|            | 5.5    | Geometi                                      | ric Envelope for Intel Reference BTX Thermal Module Assembly                             | 50                         |

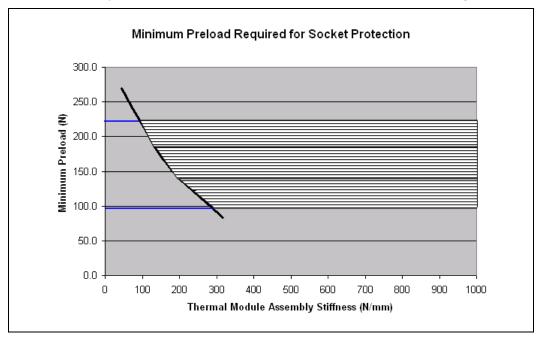

|            | 5.6    | Preload                                      | and TMA Stiffness                                                                        |                            |

|            |        | 5.6.1                                        | Structural Design Strategy                                                               |                            |

|            |        | 5.6.2                                        | TMA Preload versus Stiffness                                                             |                            |

| 6          | ATX TI |                                              | echanical Design Information                                                             |                            |

|            | 6.1    | ATX Ref                                      | erence Design Requirements                                                               | 55                         |

|            | 6.2    |                                              | on Results for Reference Design                                                          |                            |

|            |        | 6.2.1                                        | Heatsink Performance                                                                     |                            |

|            |        | 6.2.2<br>6.2.3                               | Acoustics                                                                                |                            |

|            |        | 6.2.4                                        | Heatsink Thermal Validation                                                              |                            |

|            | 6.3    | Environr                                     | mental Reliability Testing                                                               |                            |

|            |        | 6.3.1<br>6.3.2<br>6.3.3                      | Structural Reliability Testing                                                           | 63                         |

|            | 6.4    |                                              | and Recycling Requirements                                                               |                            |

|            | 6.5    |                                              | Requirements                                                                             |                            |

|            | 6.6    |                                              | ric Envelope for Intel Reference ATX Thermal Mechanical Design                           |                            |

|            | 6.7    |                                              | ce Attach Mechanism                                                                      |                            |

|            |        | 6.7.1<br>6.7.2                               | Structural Design Strategy  Mechanical Interface to the Reference Attach Mechanism       |                            |

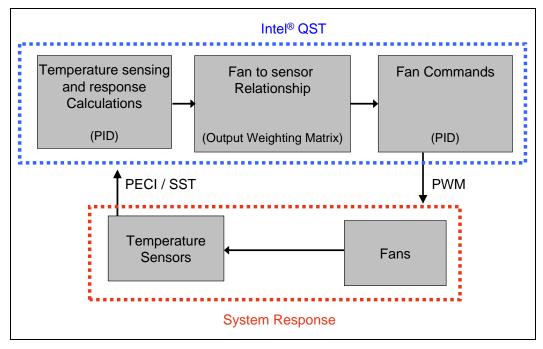

| 7          | Intel® | Quiet Sys                                    | stem Technology (Intel® QST)                                                             | 69                         |

|            | 7.1    | Intel® Q                                     | ST Algorithm                                                                             | 69                         |

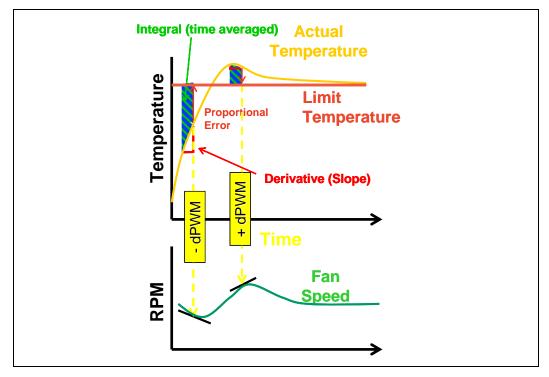

|            |        | 7.1.1<br>7.1.2                               | Output Weighting Matrix Proportional-Integral-Derivative (PID)                           | 70<br>70                   |

|            | 7.2    |                                              | nd System Implementation of Intel® QST                                                   |                            |

|            | 7.3    |                                              | ST Configuration and Tuning                                                              |                            |

|            | 7.4    | Fan Hub                                      | Thermistor and Intel® QST                                                                | 74                         |

| Appendix A | LGA77  | 5 Socket                                     | Heatsink Loading                                                                         | 75                         |

|            | A.1    |                                              | Socket Heatsink Considerations                                                           | 75                         |

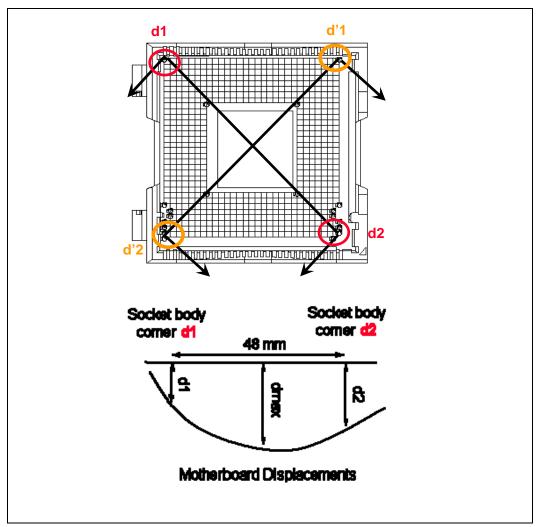

|            | A.2    | Metric fo<br>Intel <sup>®</sup> R            | or Heatsink Preload for ATX/uATX Designs Non-Compliant with eference Design              | 75                         |

|               | A.3                                       | A.2.1 Heatsink Preload Requirement Limitations. A.2.2 Motherboard Deflection Metric Definition                                                                                                                                                                                                                                 | 76<br>77<br>78                  |

|---------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Appendix B    |                                           | nk Clip Load Metrology                                                                                                                                                                                                                                                                                                         |                                 |

| , pposition 2 | B.1<br>B.2                                | Overview Test Preparation B.2.1 Heatsink Preparation B.2.2 Typical Test Equipment Test Procedure Examples                                                                                                                                                                                                                      | 81<br>81<br>81<br>84            |

|               |                                           | B.3.1 Time-Zero, Room Temperature Preload Measurement B.3.2 Preload Degradation under Bake Conditions                                                                                                                                                                                                                          |                                 |

| Appendix C    | Therm<br>C.1<br>C.2<br>C.3                | nal Interface Management                                                                                                                                                                                                                                                                                                       | 87<br>87                        |

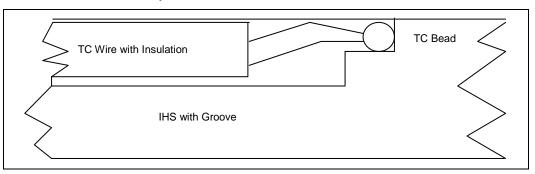

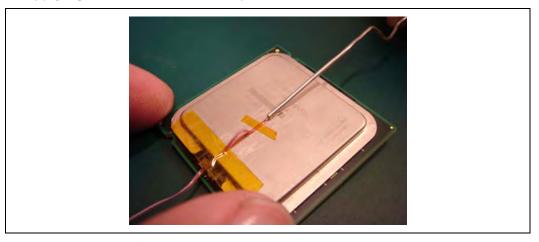

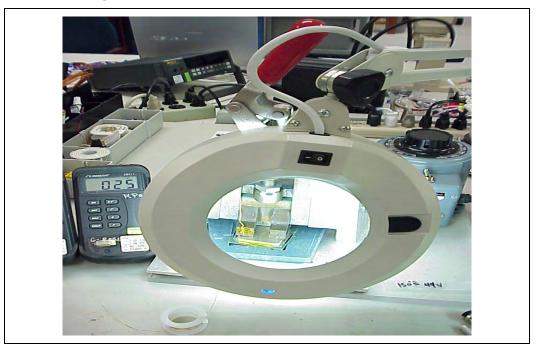

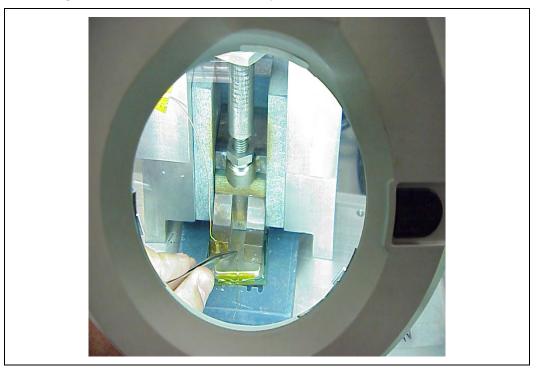

| Appendix D    | Case T<br>D.1<br>D.2<br>D.3<br>D.4<br>D.5 | Objective and Scope Supporting Test Equipment Thermal Calibration and Controls IHS Groove Thermocouple Attach Procedure D.5.1 Thermocouple Conditioning and Preparation D.5.2 Thermocouple Attachment to the IHS D.5.3 Solder Process D.5.4 Cleaning and Completion of Thermocouple Installation. Thermocouple Wire Management | 8991959595                      |

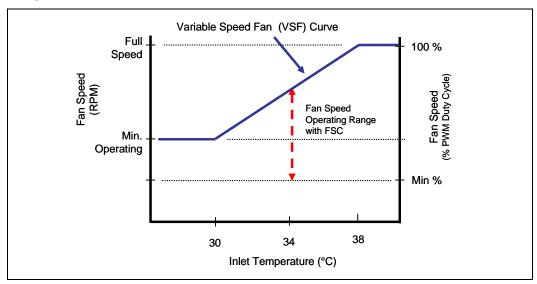

| Appendix E    | E.2<br>E.3<br>E.4                         | Thermal Solution Design  E.1.1 Determine Thermistor Set Points  E.1.2 Minimum Fan Speed Set Point  Board and System Implementation  E.2.1 Choosing Fan Speed Control Settings  Combining Thermistor and On-Die Thermal Sensor Control  Interaction of Thermal Profile and T <sub>CONTROL</sub>                                 | 109<br>109<br>110<br>111<br>111 |

| Appendix F    | Balanc                                    | ced Technology Extended (BTX) System Thermal Considerations                                                                                                                                                                                                                                                                    | 121                             |

| Appendix G    | Fan Pe                                    | erformance for Reference Design                                                                                                                                                                                                                                                                                                | 125                             |

| Appendix H    | Mecha                                     | nical Drawings                                                                                                                                                                                                                                                                                                                 | 128                             |

| Appendix I    | Intel E                                   | Enabled Reference Solution Information                                                                                                                                                                                                                                                                                         | 146                             |

## **Figures**

| Figure 2-1. Package IHS Load Areas                                                | 15 |

|-----------------------------------------------------------------------------------|----|

| Figure 2-2. Processor Case Temperature Measurement Location                       |    |

| Figure 2-3. Example Thermal Profile                                               |    |

| Figure 3-1. Processor Thermal Characterization Parameter Relationships            |    |

| Figure 3-2. Locations for Measuring Local Ambient Temperature, Active ATX         |    |

| Heatsink                                                                          | 31 |

| Figure 3-3. Locations for Measuring Local Ambient Temperature, Passive Heatsink.  | 31 |

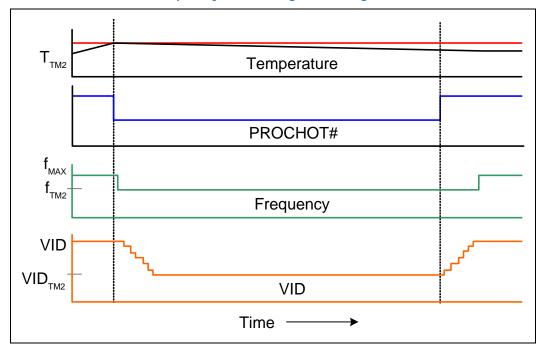

| Figure 4-1. Thermal Monitor Control                                               |    |

| Figure 4-2. Thermal Monitor 2 Frequency and Voltage Ordering                      |    |

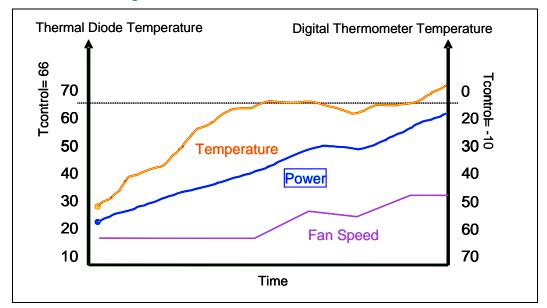

| Figure 4-3. TCONTROL for Digital Thermal Sensor                                   |    |

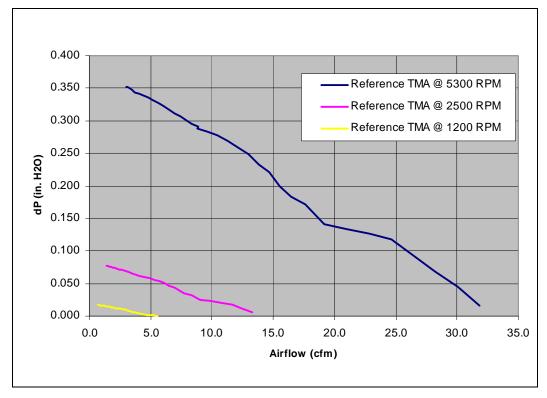

| Figure 5-1. Effective TMA Fan Curves with Reference Extrusion                     |    |

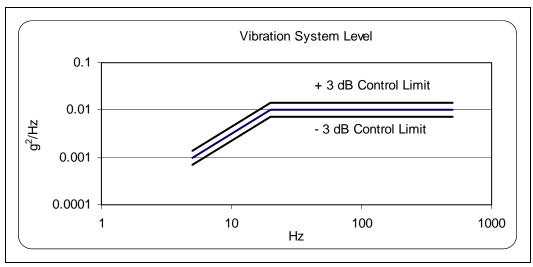

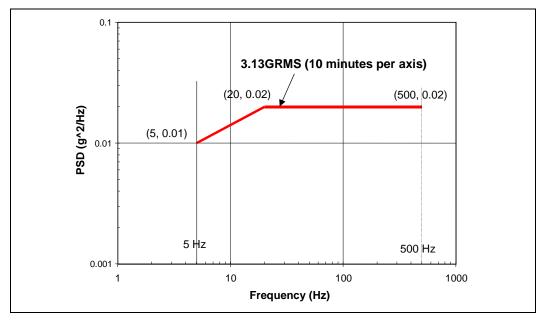

| Figure 5-2. Random Vibration PSD                                                  | 47 |

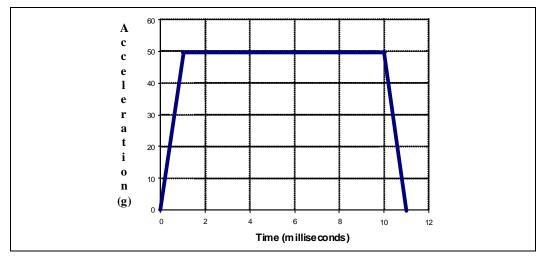

| Figure 5-3. Shock Acceleration Curve                                              |    |

| Figure 5-4. Intel Type II TMA 65 W Reference Design                               |    |

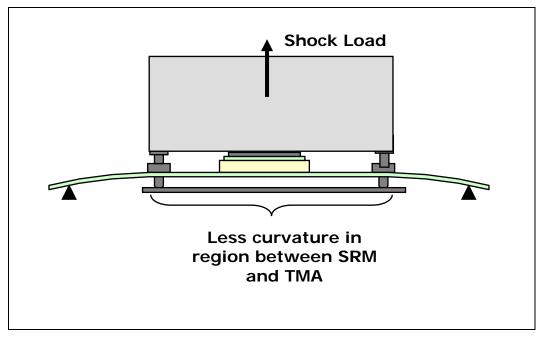

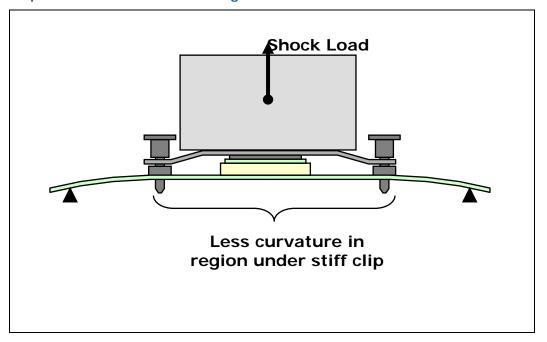

| Figure 5-5. Upward Board Deflection During Shock                                  |    |

| Figure 5-6. Minimum Required Processor Preload to Thermal Module Assembly         |    |

| Stiffness                                                                         | 52 |

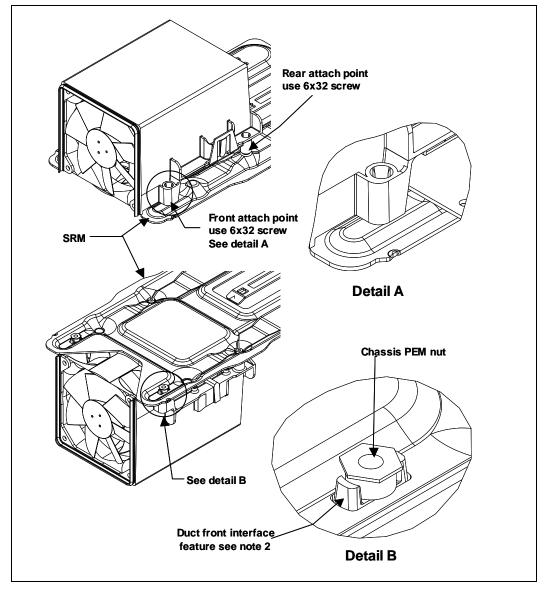

| Figure 5-7. Thermal Module Attach Pointes and Duct-to-SRM Interface Features      | 53 |

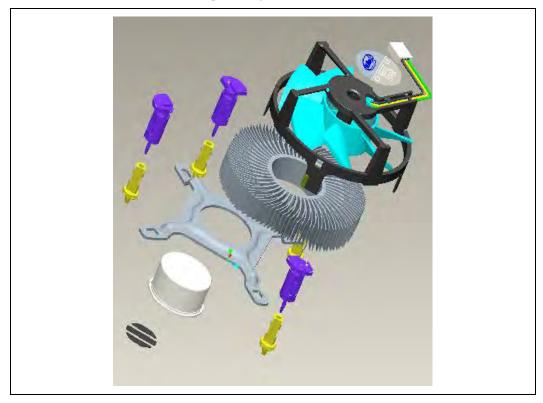

| Figure 6-1. D60188-001Reference Design – Exploded View                            | 56 |

| Figure 6-2. E18764-001 Reference Design – Exploded View                           | 57 |

| Figure 6-3. Bottom View of Copper Core Applied by TC-1996 Grease                  |    |

| Figure 6-4. Random Vibration PSD                                                  |    |

| Figure 6-5. Shock Acceleration Curve                                              | 62 |

| Figure 6-6. Upward Board Deflection During Shock                                  | 65 |

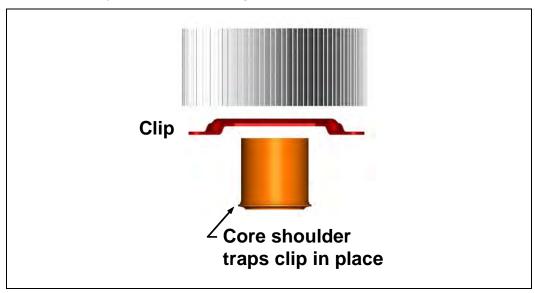

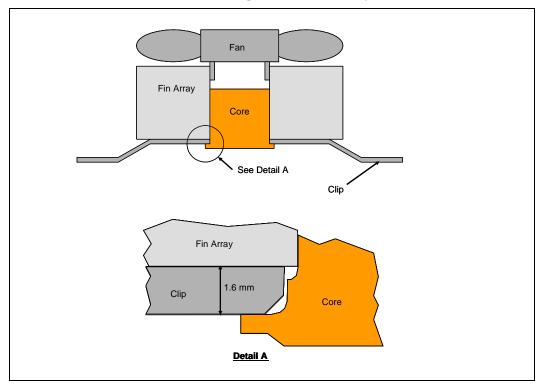

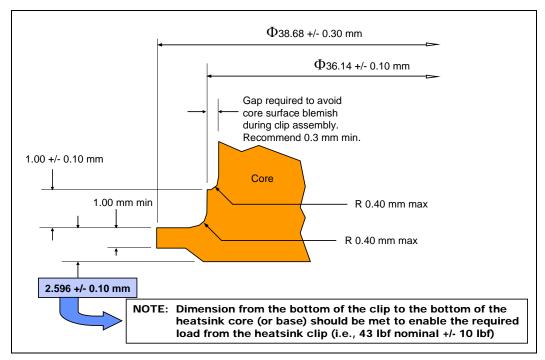

| Figure 6-7. Reference Clip/Heatsink Assembly                                      | 66 |

| Figure 6-8. Critical Parameters for Interfacing to Reference Clip                 | 67 |

| Figure 6-9. Critical Core Dimension                                               | 67 |

| Figure 7-1. Intel <sup>®</sup> QST Overview                                       | 70 |

| Figure 7-2. PID Controller Fundamentals                                           |    |

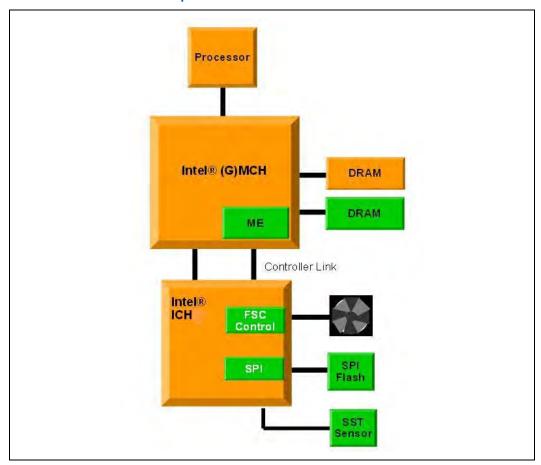

| Figure 7-3. Intel <sup>®</sup> QST Platform Requirements                          | 72 |

| Figure 7-4. Example Acoustic Fan Speed Control Implementation                     |    |

| Figure 7-5. Digital Thermal Sensor and Thermistor                                 | 74 |

| Figure 7-6. Board Deflection Definition                                           | 77 |

| Figure 7-7. Example: Defining Heatsink Preload Meeting Board Deflection Limit     | 79 |

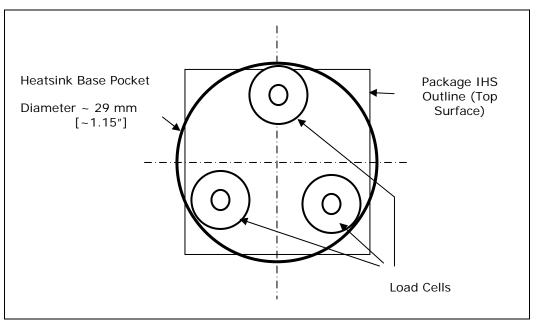

| Figure 7-8. Load Cell Installation in Machined Heatsink Base Pocket – Bottom View | 82 |

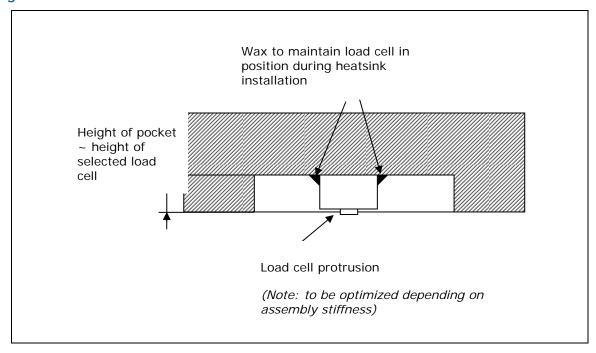

| Figure 7-9. Load Cell Installation in Machined Heatsink Base Pocket – Side View   | 83 |

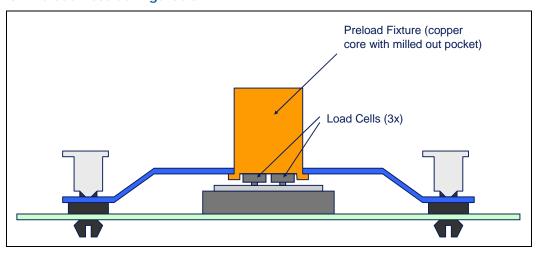

| Figure 7-10. Preload Test Configuration                                           | 83 |

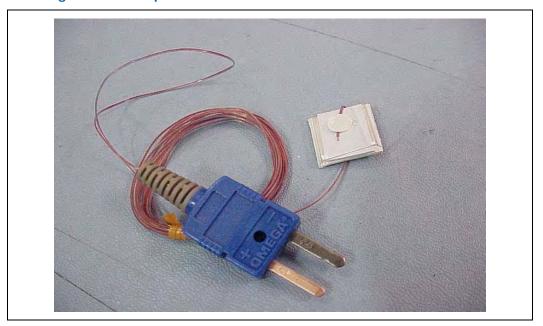

| Figure 7-11. Omega Thermocouple                                                   | 90 |

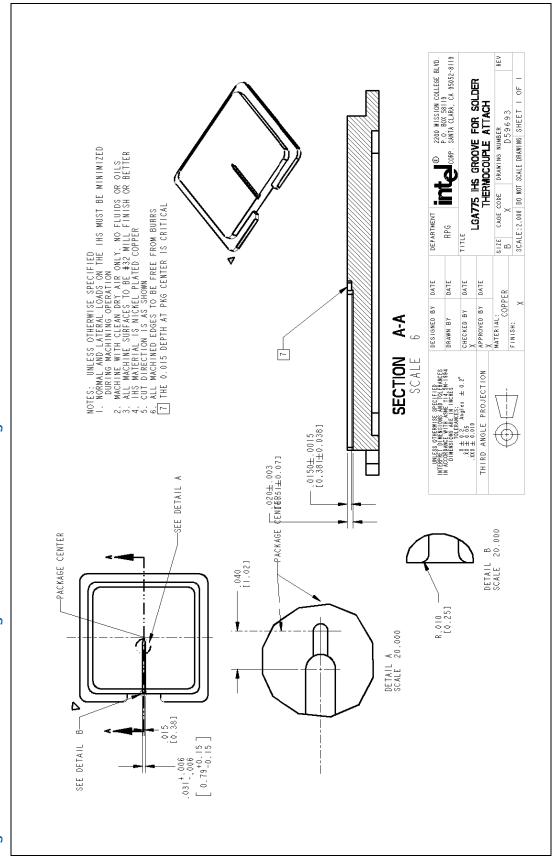

| Figure 7-12. 775-LAND LGA Package Reference Groove Drawing at 6 o'clock Exit      | 92 |

| Figure 7-13. 775-LAND LGA Package Reference Groove Drawing at 3 o'clock Exit      |    |

| (Old Drawing)                                                                     |    |

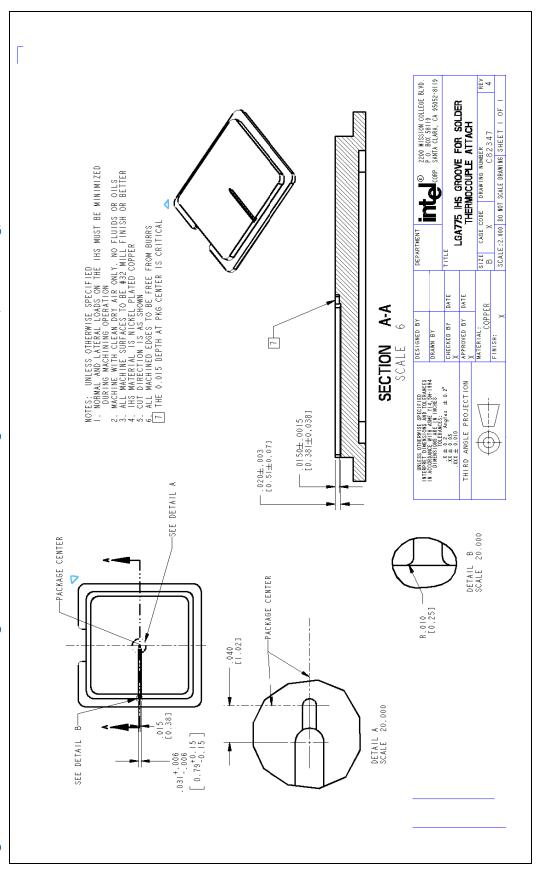

| Figure 7-14. IHS Groove at 6 o'clock Exit on the 775-LAND LGA Package             | 94 |

| Figure 7-15. IHS Groove at 6 o'clock Exit Orientation Relative to the LGA775      |    |

| Socket                                                                            |    |

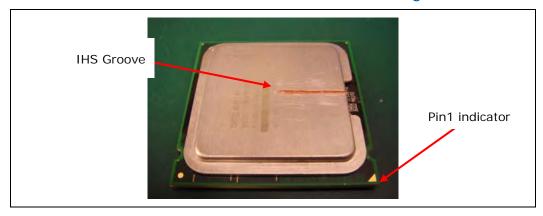

| Figure 7-16. Inspection of Insulation on Thermocouple                             |    |

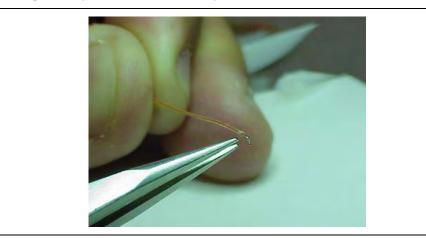

| Figure 7-17. Bending the Tip of the Thermocouple                                  |    |

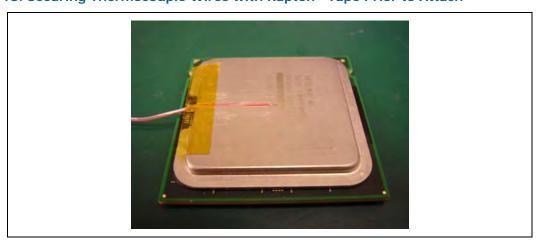

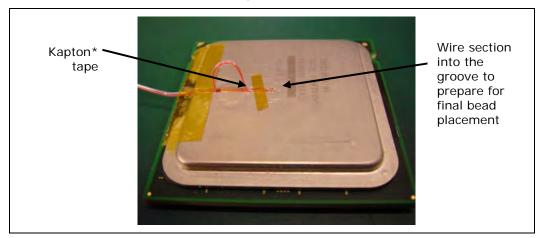

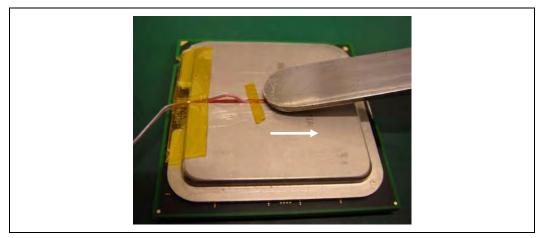

| Figure 7-18. Securing Thermocouple Wires with Kapton* Tape Prior to Attach        |    |

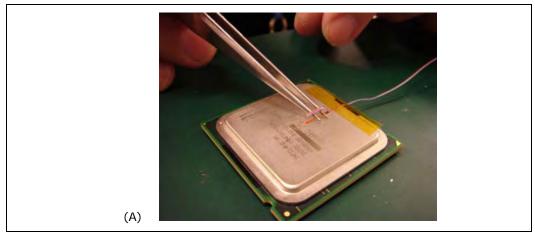

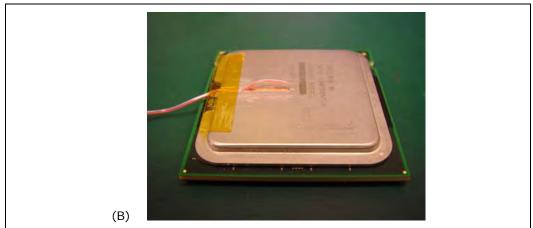

| Figure 7-19. Thermocouple Bead Placement                                          |    |

| Figure 7-20 Position Read on the Groove Step                                      | 98 |

| Figure 7-21. | Detailed Thermocouple Bead Placement                                    | 98  |

|--------------|-------------------------------------------------------------------------|-----|

|              | Third Tape Installation                                                 |     |

| Figure 7-23. | Measuring Resistance Between Thermocouple and IHS                       | 99  |

| Figure 7-24. | Applying Flux to the Thermocouple Bead                                  | 100 |

| Figure 7-25. | Cutting Solder                                                          | 100 |

| Figure 7-26. | Positioning Solder on IHS                                               | 101 |

| Figure 7-27. | Solder Station Setup                                                    | 102 |

| Figure 7-28. | View Through Lens at Solder Station                                     | 103 |

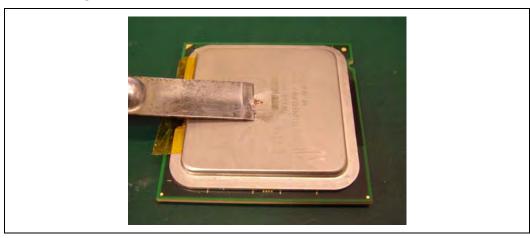

| Figure 7-29. | Moving Solder back onto Thermocouple Bead                               | 103 |

|              | Removing Excess Solder                                                  |     |

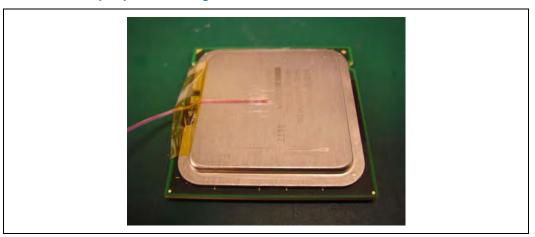

| Figure 7-31. | Thermocouple placed into groove                                         | 105 |

| Figure 7-32. | Removing Excess Solder                                                  | 105 |

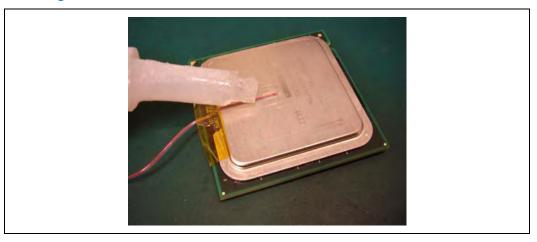

| Figure 7-33. | Filling Groove with Adhesive                                            | 106 |

| Figure 7-34. | Application of Accelerant                                               | 106 |

| Figure 7-35. | Removing Excess Adhesive from IHS                                       | 107 |

| Figure 7-36. | Finished Thermocouple Installation                                      | 107 |

| Figure 7-37. | Thermocouple Wire Management                                            | 108 |

| Figure 7-38. | Thermistor Set Points                                                   | 110 |

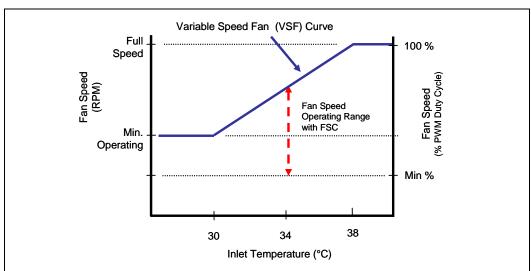

| Figure 7-39. | Example Fan Speed Control Implementation                                | 111 |

| Figure 7-40. | Fan Speed Control                                                       | 112 |

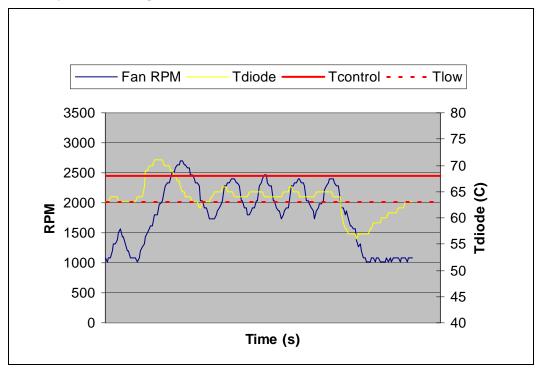

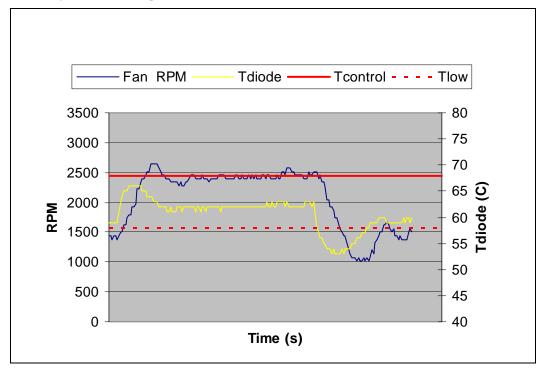

| Figure 7-41. | Temperature Range = 5 °C                                                | 113 |

| Figure 7-42. | Temperature Range = 10 °C                                               | 114 |

| Figure 7-43. | On-Die Thermal Sensor and Thermistor                                    | 115 |

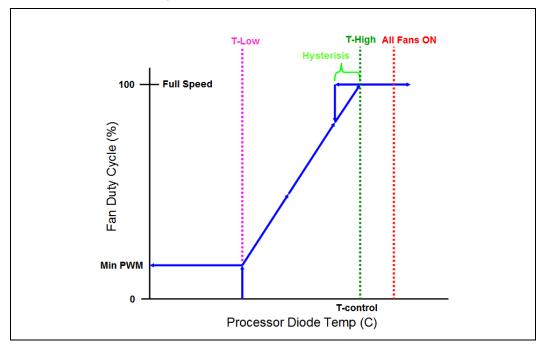

| Figure 7-44. | FSC Definition Example                                                  | 117 |

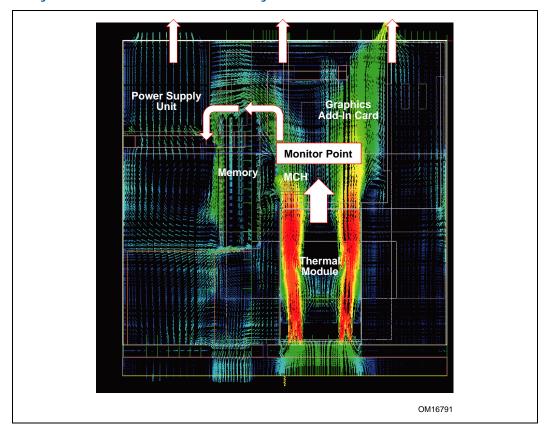

| Figure 7-45. | System Airflow Illustration with System Monitor Point Area Identified . | 122 |

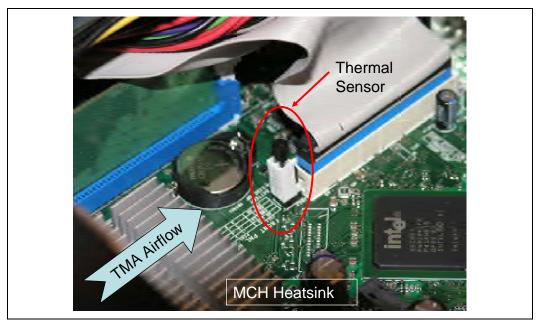

| Figure 7-46. | Thermal sensor Location Illustration                                    | 123 |

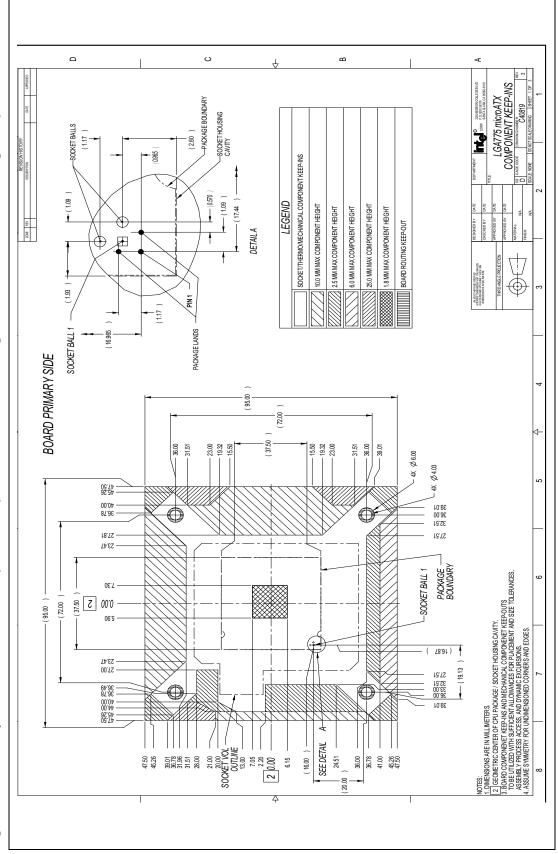

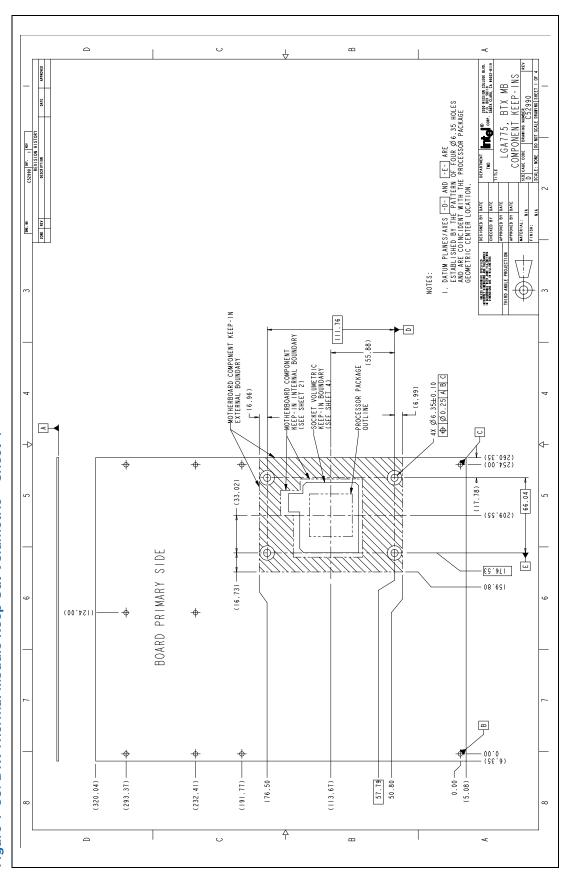

| Figure 7-47. | ATX/µATX Motherboard Keep-out Footprint Definition and Height           |     |

|              | Restrictions for Enabling Components - Sheet 1                          | 129 |

| Figure 7-48. | ATX/µATX Motherboard Keep-out Footprint Definition and Height           |     |

|              | Restrictions for Enabling Components - Sheet 2                          | 130 |

| Figure 7-49. | ATX/µATX Motherboard Keep-out Footprint Definition and Height           |     |

|              | Restrictions for Enabling Components - Sheet 3                          |     |

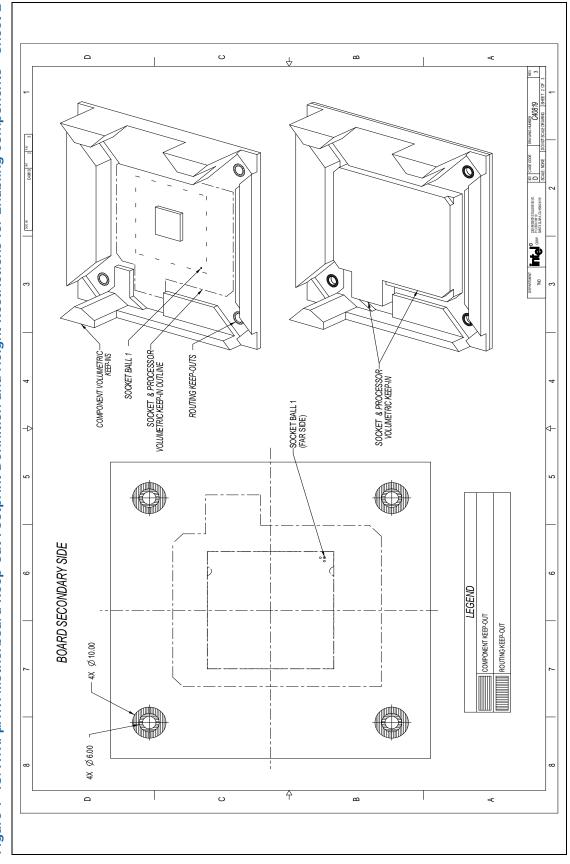

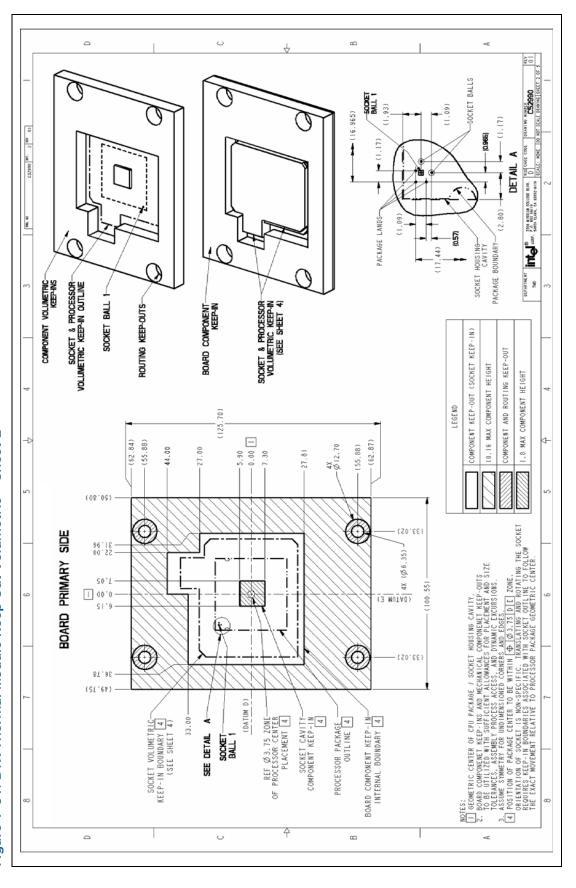

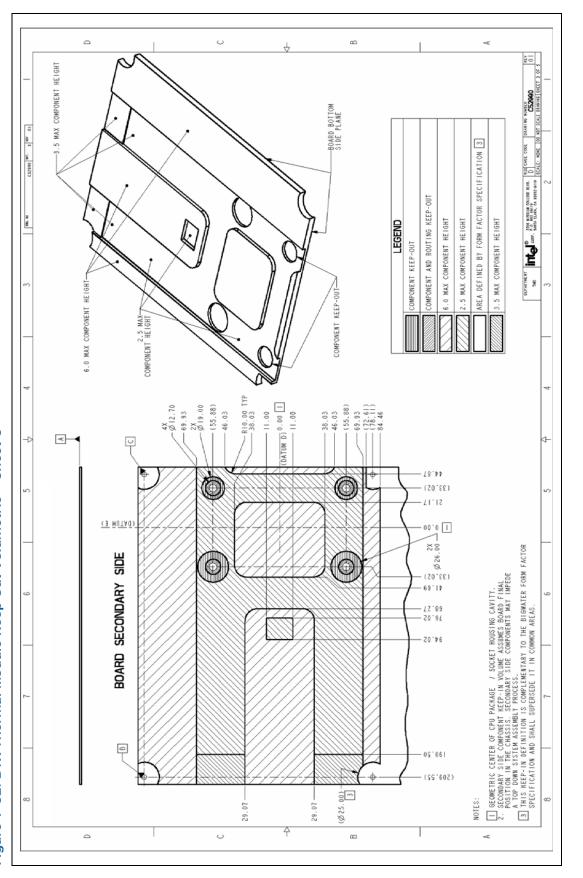

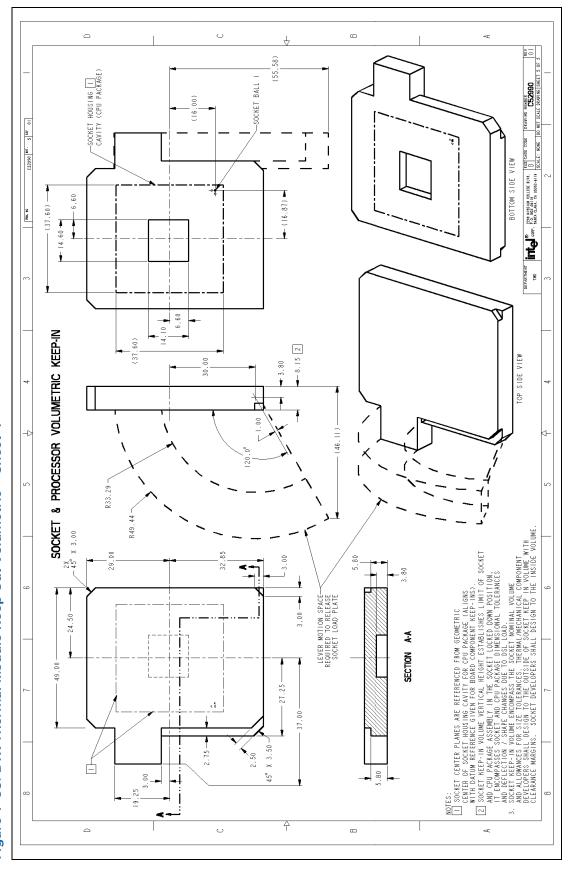

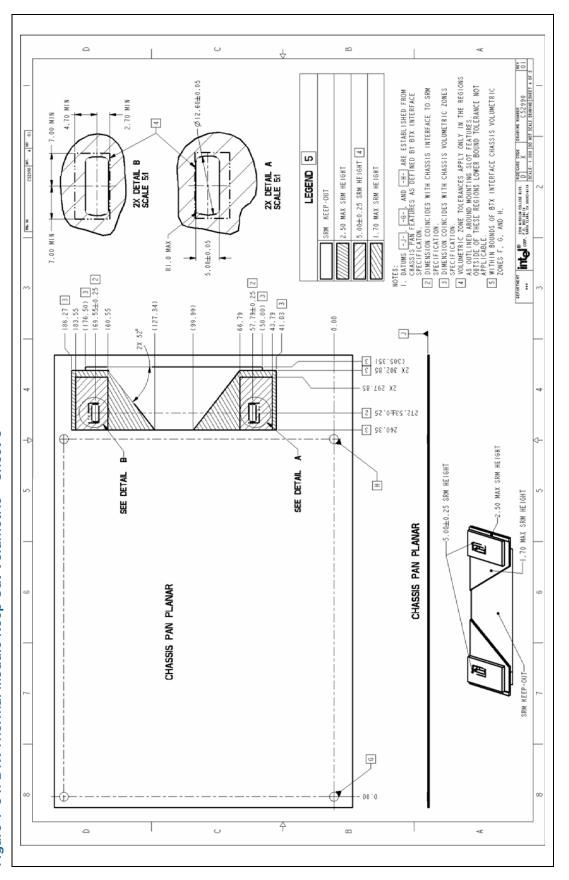

|              | BTX Thermal Module Keep Out Volumetric – Sheet 1                        |     |

|              | BTX Thermal Module Keep Out Volumetric – Sheet 2                        |     |

| •            | BTX Thermal Module Keep Out Volumetric – Sheet 3                        |     |

|              | BTX Thermal Module Keep Out Volumetric – Sheet 4                        |     |

|              | BTX Thermal Module Keep Out Volumetric – Sheet 5                        |     |

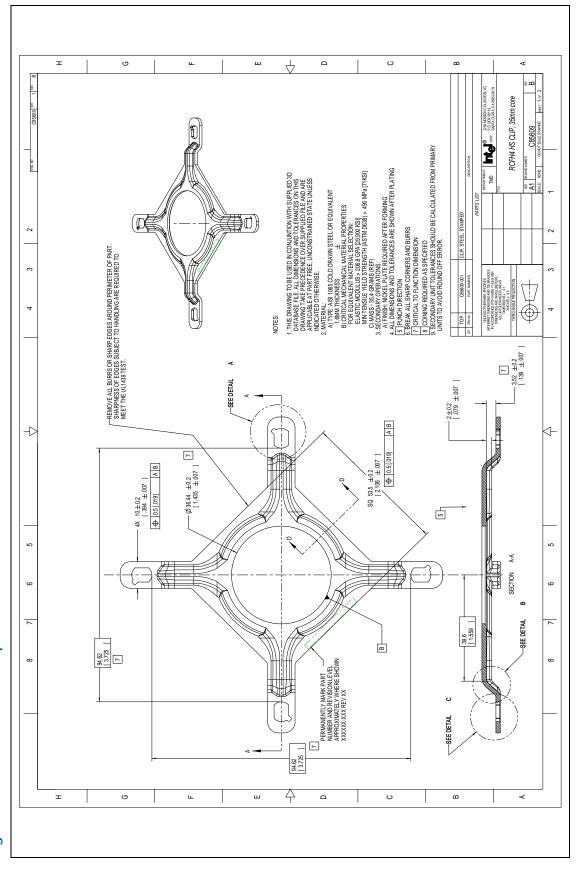

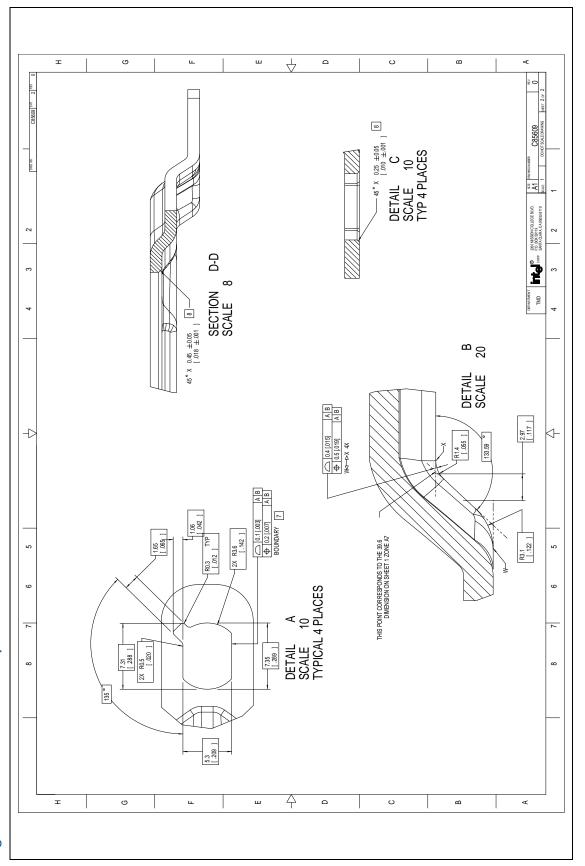

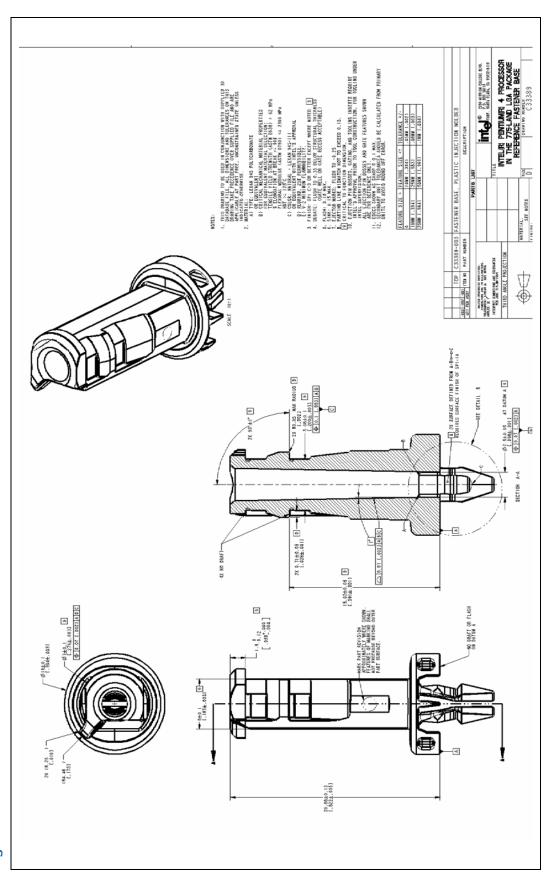

|              | ATX Reference Clip – Sheet 1                                            |     |

|              | ATX Reference Clip - Sheet 2                                            |     |

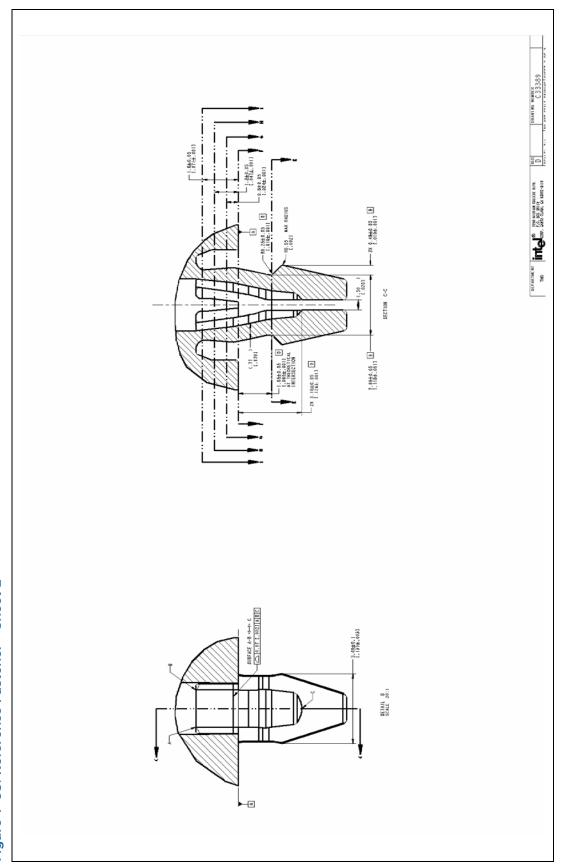

|              | Reference Fastener - Sheet 1                                            |     |

| Figure 7-58. | Reference Fastener - Sheet 2                                            | 140 |

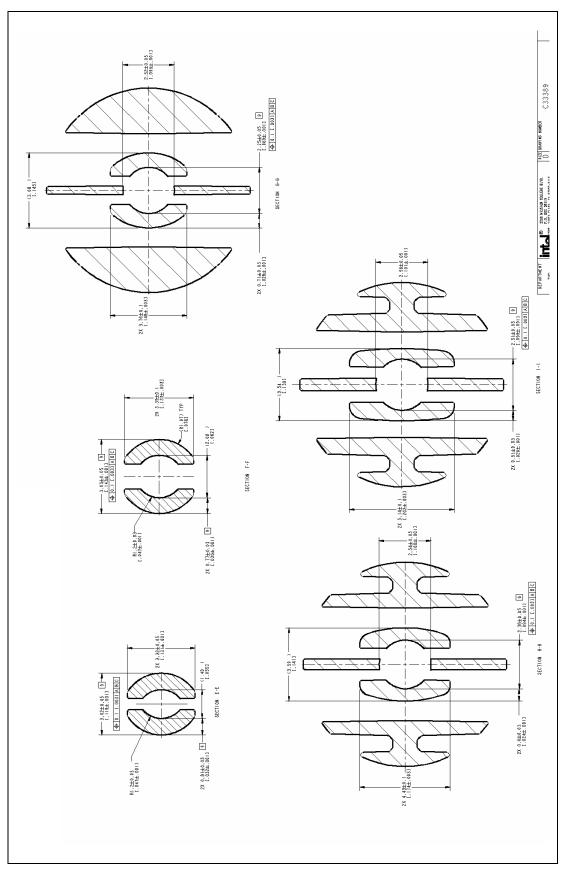

|              | Reference Fastener - Sheet 3                                            |     |

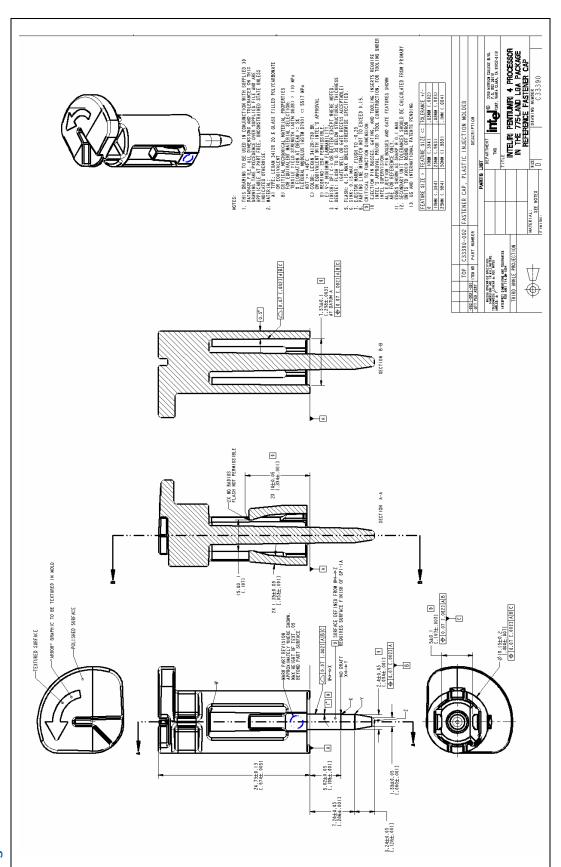

|              | Reference Fastener - Sheet 4                                            |     |

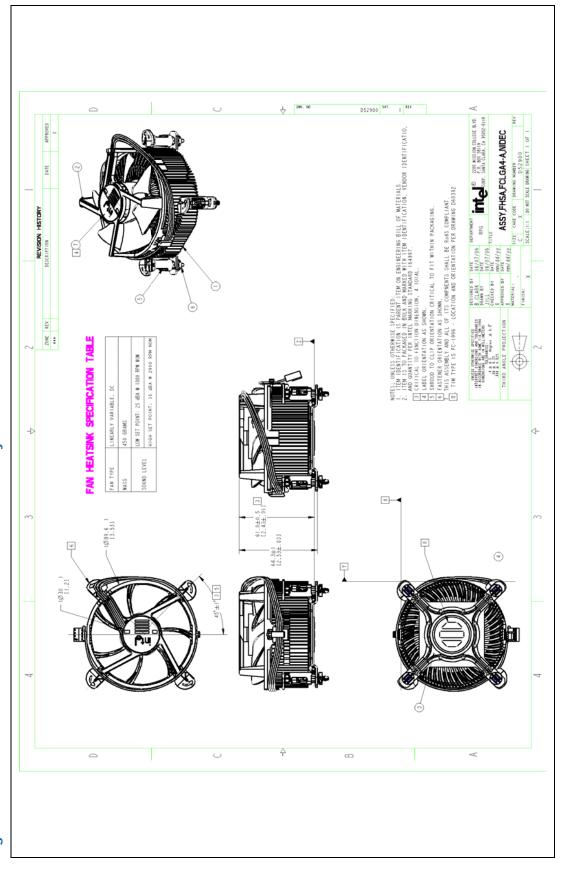

|              | Intel® D60188-001 Reference Solution Assembly                           |     |

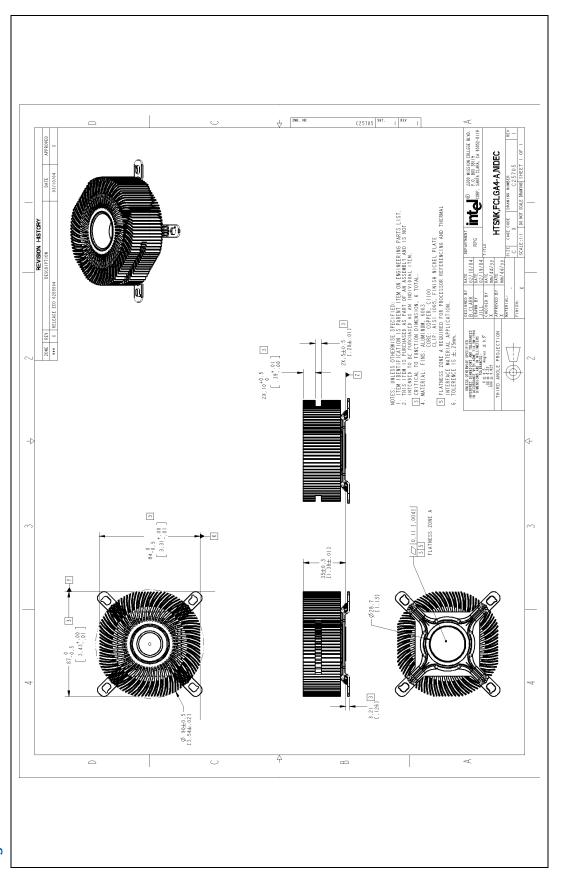

|              | Intel® D60188-001 Reference Solution Heatsink                           |     |

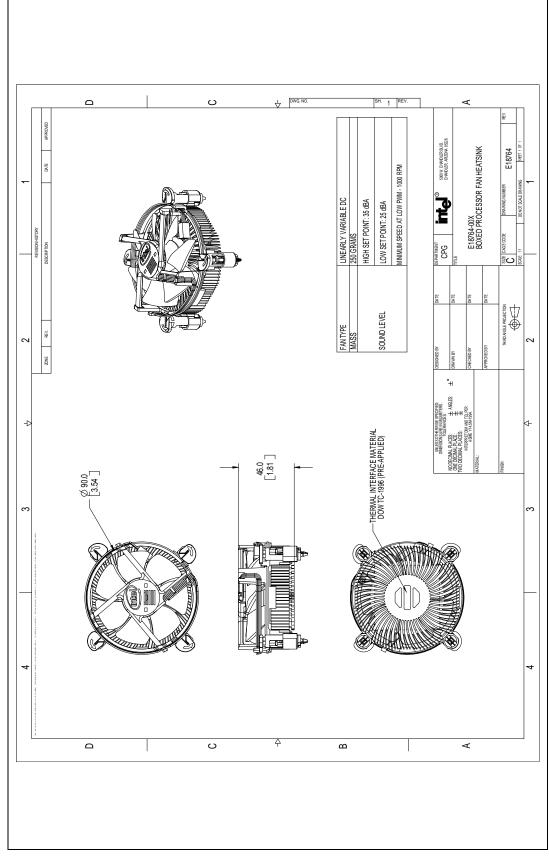

| Figure 7-63. | Intel® E18764-001 Reference Solution Assembly                           | 145 |

## **Tables**

| Table 2-1. Heatsink Inlet Temperature of Intel Reference Thermal Solutions            | 24  |

|---------------------------------------------------------------------------------------|-----|

| Table 2-2. Heatsink Inlet Temperature of Intel Boxed Processor Thermal Solution       | s24 |

| Table 5-1. Balanced Technology Extended (BTX) Type II Reference TMA                   |     |

| Performance                                                                           | 42  |

| Table 5-2. Acoustic Targets                                                           | 43  |

| Table 5-3. VR Airflow Requirements                                                    | 46  |

| Table 5-4. Processor Preload Limits                                                   | 52  |

| Table 6-1. D60188-001 Reference Heatsink Performance                                  | 58  |

| Table 6-2. E18764-001 Reference Heatsink Performance                                  | 58  |

| Table 6-3. Acoustic Results for ATX Reference Heatsink (D60188-001)                   | 59  |

| Table 6-4. Acoustic Results for ATX Reference Heatsink (E18764-001)                   | 59  |

| Table 7-1. Board Deflection Configuration Definitions                                 | 76  |

| Table 7-2. Typical Test Equipment                                                     | 84  |

| Table 7-3. FSC Definitions                                                            | 116 |

| Table 7-4. ATX FSC Settings                                                           | 118 |

| Table 7-5. Balanced Technology Extended (BTX) Fan Speed Control Settings              | 119 |

| Table 7-6. Fan Electrical Performance Requirements                                    | 125 |

| Table 7-7. Intel <sup>®</sup> Representative Contact for Licensing Information of BTX |     |

| Reference Design                                                                      | 146 |

| Table 7-8. D60188-001 Reference Thermal Solution Providers                            | 146 |

| Table 7-9. E18764-001 Reference Thermal Solution Providers                            | 147 |

| Table 7-10. Balanced Technology Extended (BTX) Reference Thermal Solution             |     |

| Providers                                                                             | 148 |

# **Revision History**

| Revision<br>Number | Description                                                                                                  | Revision Date     |

|--------------------|--------------------------------------------------------------------------------------------------------------|-------------------|

| -001               | Initial release.                                                                                             | July 2007         |

| -002               | • Added Intel <sup>®</sup> Core <sup>™</sup> 2 Duo Desktop processor E4400 at Tc-max of 73.3 °C.             | August 2007       |

| -003               | Added Intel® Pentium® Dual Core processor E2180 specifications                                               | August 2007       |

| -004               | Added Intel® Pentium® Dual Core processor E2160 and E2140 at Tc-max of 73.3 °C                               | September<br>2007 |

| -005               | Added Intel <sup>®</sup> Core <sup>™</sup> 2 Duo Desktop processor E4600                                     | October 2007      |

| -006               | Added Intel® Pentium® Dual Core processor E2200 specifications                                               | December 2007     |

| -007               | <ul> <li>Added Intel<sup>®</sup> Celeron<sup>®</sup> Dual-Core processor E1000<sup>△</sup> series</li> </ul> | January 2008      |

|                    | Updated reference design Intel P/N, supplier P/N and heatsink drawing                                        |                   |

|                    | Updated Intel® Boxed Processor Thermal Solutions inlet ambient temperature assumption                        |                   |

| -008               | Added Intel® Pentium® Dual Core processor E2220 specifications                                               | March 2008        |

|                    | <ul> <li>Added Intel<sup>®</sup> Core<sup>™</sup>2 Duo Desktop processor E4700 specifications</li> </ul>     |                   |

| -009               | Added Intel® Celeron® Dual-Core processor E1400                                                              | April 2008        |

| -010               | Added Intel® Celeron® Dual-Core processor E1500                                                              | December 2008     |

| -011               | Added Intel® Celeron® Dual-Core processor E1600                                                              | June 2009         |

## 1 Introduction

## 1.1 Document Goals and Scope

### 1.1.1 Importance of Thermal Management

The objective of thermal management is to ensure that the temperatures of all components in a system are maintained within their functional temperature range. Within this temperature range, a component is expected to meet its specified performance. Operation outside the functional temperature range can degrade system performance, cause logic errors or cause component and/or system damage. Temperatures exceeding the maximum operating limit of a component may result in irreversible changes in the operating characteristics of this component.

In a system environment, the processor temperature is a function of both system and component thermal characteristics. The system level thermal constraints consist of the local ambient air temperature and airflow over the processor as well as the physical constraints at and above the processor. The processor temperature depends in particular on the component power dissipation, the processor package thermal characteristics, and the processor thermal solution.

All of these parameters are affected by the continued push of technology to increase processor performance levels and packaging density (more transistors). As operating frequencies increase and packaging size decreases, the power density increases while the thermal solution space and airflow typically become more constrained or remains the same within the system. The result is an increased importance on system design to ensure that thermal design requirements are met for each component, including the processor, in the system.

#### 1.1.2 Document Goals

Depending on the type of system and the chassis characteristics, new system and component designs may be required to provide adequate cooling for the processor. The goal of this document is to provide an understanding of these thermal characteristics and discuss guidelines for meeting the thermal requirements imposed on single processor systems using the Intel<sup>®</sup> Core  $^{\text{M}}2$  Duo processor E6000 and E4000 series, Intel<sup>®</sup> Pentium<sup>®</sup> Dual Core processor E2000 series, and Intel<sup>®</sup> Celeron<sup>®</sup> Dual-Core processor E1000 $^{\text{A}}$  series.

The concepts given in this document are applicable to any system form factor. Specific examples used will be the Intel enabled reference solution for ATX/uATX systems. See the applicable BTX form factor reference documents to design a thermal solution for that form factor.

#### 1.1.3 Document Scope

This design guide supports the following processors:

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor with 4 MB cache at Tc-max of 60.1 °C applies to Intel<sup>®</sup> Core<sup>™</sup>2 Duo processors E6700, E6600, E6420 and E6320

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor with 4 MB cache at Tc-max of 72.0 °C applies to Intel<sup>®</sup> Core<sup>™</sup>2 Duo processors E6850, E6750, E6550 and E6540

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor with 2 MB cache of Tc-max of 72.0 °C applies to Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor E4700

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor with 2 MB cache at Tc-max of 61.4 °C applies to Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor E6000 series of processors E6400 and E6300 and Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor E4000 series of the processors E4400 and E4300

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual Core processor E2000 series at Tc-max of 61.4 °C applies to the Intel<sup>®</sup> Pentium<sup>®</sup> Dual Core processors E2160 and E2140

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor with 2 MB cache at Tc-max of 73.3 °C applies to Intel<sup>®</sup> Core<sup>™</sup>2 Duo processors E6400, E4600, E4500, E4400, and E4300

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual Core processor E2000 series at Tc-max of 73.3 °C applies to the Intel<sup>®</sup> Pentium<sup>®</sup> Dual Core processors E2220, E2200, E2180, E2160, and E2140

- Intel<sup>®</sup> Celeron<sup>®</sup> dual-core processor E1000 Series of Tc-max of 73.3 °C applies to the Intel<sup>®</sup> Celeron <sup>®</sup> dual-core processor E1200, E1400, E1500, and E1600

In this document when a reference is made to "the processor" it is intended that this includes all the processors supported by this document. If needed for clarity, the specific processor will be listed.

In this document, when a reference is made to the "the reference design" it is intended that this includes all ATX reference designs (D60188-001 and E18764-001) supported by this document. If needed for clarify, the specific reference design will be listed.

In this document, when a reference is made to "the Datasheet", the reader should refer to the  $Intel^{@}$   $Core^{TM}2$  Extreme Processor X6800 and  $Intel^{@}$   $Core^{TM}2$  Duo Desktop Processor E6000 Equal E4000 E4000

Chapter 2 of this document discusses package thermal mechanical requirements to design a thermal solution for the processor in the context of personal computer applications. Chapter 3 discusses the thermal solution considerations and metrology recommendations to validate a processor thermal solution. Chapter 4 addresses the benefits of the processor's integrated thermal management logic for thermal design. Chapter 5 gives information on the Intel reference thermal solution for the processor in BTX platform. Chapter 6 gives information on the Intel reference thermal solution for the processor in ATX platform. Chapter 7 discusses the implementation of acoustic fan speed control.

The physical dimensions and thermal specifications of the processor that are used in this document are for illustration only. Refer to the datasheet for the product dimensions, thermal power dissipation and maximum case temperature. In case of conflict, the data in the datasheet supersedes any data in this document.

## 1.2 References

Material and concepts available in the following documents may be beneficial when reading this document.

| Document                                                                                                                                                            | Location                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Intel <sup>®</sup> Core <sup>™</sup> 2 Extreme Processor X6800 and Intel <sup>®</sup> Core <sup>™</sup> 2 Duo<br>Desktop Processor E6000 and E4000 Series Datasheet | http://intel.com<br>/design/processor/datashts/3132<br>78.htm |

| Intel® Pentium® Dual-Core Desktop Processor E2000 Series<br>Datasheet                                                                                               | www.intel.com//design/processor<br>/datashts/316981.htm       |

| Intel <sup>®</sup> Celeron <sup>®</sup> Dual-Core Processor E1000 Series Datasheet                                                                                  | http://www.intel.com/design/pro<br>cessor/datashts/318924.htm |

| LGA775 Socket Mechanical Design Guide                                                                                                                               | http://intel.com/design/<br>Pentium4/guides/ 302666.htm       |

| uATX SFF Design Guidance                                                                                                                                            | http://www.formfactors.org/                                   |

| Fan Specification for 4-wire PWM Controlled Fans                                                                                                                    | http://www.formfactors.org/                                   |

| ATX Thermal Design Suggestions                                                                                                                                      | http://www.formfactors.org/                                   |

| microATX Thermal Design Suggestions                                                                                                                                 | http://www.formfactors.org/                                   |

| Balanced Technology Extended (BTX) System Design Guide                                                                                                              | http://www.formfactors.org/                                   |

| Thermally Advantaged Chassis version 1.1                                                                                                                            | http://www.intel.com/go/chassis/                              |

## 1.3 Definition of Terms

| Term               | Description                                                                                                                                                                                                                                  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

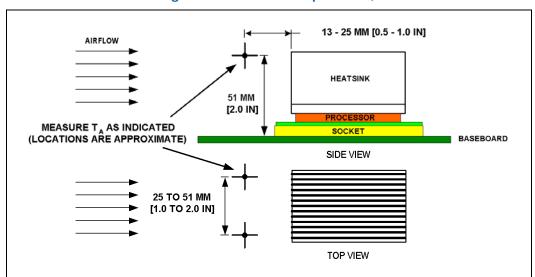

| T <sub>A</sub>     | The measured ambient temperature locally surrounding the processor. The ambient temperature should be measured just upstream of a passive heatsink or at the fan inlet for an active heatsink.                                               |

| T <sub>c</sub>     | The case temperature of the processor, measured at the geometric center of the topside of the IHS.                                                                                                                                           |

| T <sub>E</sub>     | The ambient air temperature external to a system chassis. This temperature is usually measured at the chassis air inlets.                                                                                                                    |

| T <sub>s</sub>     | Heatsink temperature measured on the underside of the heatsink base, at a location corresponding to ${\rm T_{\rm C}}$ .                                                                                                                      |

| T <sub>C-MAX</sub> | The maximum case temperature as specified in a component specification.                                                                                                                                                                      |

| $\Psi_{\sf CA}$    | Case-to-ambient thermal characterization parameter (psi). A measure of thermal solution performance using total package power. Defined as $(T_C - T_A)$ / Total Package Power.  Note: Heat source must be specified for $\Psi$ measurements. |

|                    | Case-to-sink thermal characterization parameter. A measure of thermal interface                                                                                                                                                              |

| $\Psi_{\sf cs}$    | material performance using total package power. Defined as $(T_c - T_s)$ / Total Package Power.                                                                                                                                              |

|                    | Note: Heat source must be specified for $\Psi$ measurements.                                                                                                                                                                                 |

| Term                           | Description                                                                                                                                                                                                                           |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $\Psi_{\sf SA}$                | Sink-to-ambient thermal characterization parameter. A measure of heatsink thermal performance using total package power. Defined as $(T_S-T_A)$ / Total Package Power.                                                                |  |

|                                | Note: Heat source must be specified for $\Psi$ measurements.                                                                                                                                                                          |  |

| TIM                            | Thermal Interface Material: The thermally conductive compound between the heatsink and the processor case. This material fills the air gaps and voids, and enhances the transfer of the heat from the processor case to the heatsink. |  |

| P <sub>MAX</sub>               | The maximum power dissipated by a semiconductor component.                                                                                                                                                                            |  |

| TDP                            | Thermal Design Power: a power dissipation target based on worst-case applications.  Thermal solutions should be designed to dissipate the thermal design power.                                                                       |  |

| IHS                            | Integrated Heat Spreader: a thermally conductive lid integrated into a processor package to improve heat transfer to a thermal solution through heat spreading.                                                                       |  |

| LGA775<br>Socket               | The surface mount socket designed to accept the processors in the 775-Land LGA package.                                                                                                                                               |  |

| ACPI                           | Advanced Configuration and Power Interface.                                                                                                                                                                                           |  |

| Bypass                         | Bypass is the area between a passive heatsink and any object that can act to form a duct. For this example, it can be expressed as a dimension away from the outside dimension of the fins to the nearest surface.                    |  |

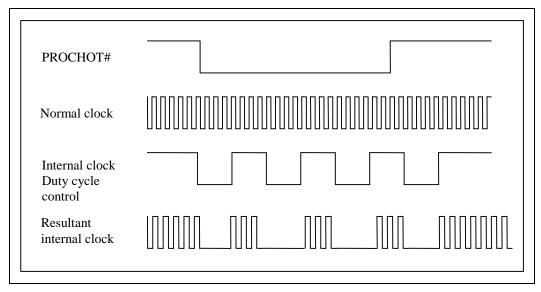

| Thermal<br>Monitor             | A feature on the processor that attempts to keep the processor die temperature within factory specifications.                                                                                                                         |  |

| TCC                            | Thermal Control Circuit: Thermal Monitor uses the TCC to reduce die temperature by lowering effective processor frequency when the die temperature has exceeded its operating limits.                                                 |  |

| T <sub>DIODE</sub>             | Temperature reported from the on-die thermal diode.                                                                                                                                                                                   |  |

| FSC                            | Fan Speed Control: Thermal solution that includes a variable fan speed which is driven by a PWM signal and uses the on-die thermal diode as a reference to change the duty cycle of the PWM signal.                                   |  |

| T <sub>CONTROL</sub>           | T <sub>CONTROL</sub> is the specification limit for use with the on-die thermal diode.                                                                                                                                                |  |

| PWM                            | Pulse width modulation is a method of controlling a variable speed fan. The enabled 4 wire fans use the PWM duty cycle % from the fan speed controller to modulate the fan speed.                                                     |  |

| Health<br>Monitor<br>Component | Any standalone or integrated component that is capable of reading the processor temperature and providing the PWM signal to the 4 pin fan header.                                                                                     |  |

| BTX                            | Balanced Technology Extended.                                                                                                                                                                                                         |  |

| TMA                            | Thermal Module Assembly. The heatsink, fan and duct assembly for the BTX thermal solution                                                                                                                                             |  |

§

## 2 Processor Thermal/Mechanical Information

## 2.1 Mechanical Requirements

#### 2.1.1 Processor Package

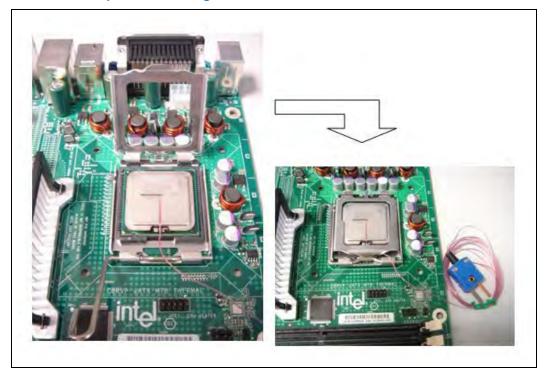

The processors covered in the document are packaged in a 775-Land LGA package that interfaces with the motherboard using a LGA775 socket. Refer to the datasheet for detailed mechanical specifications.

The processor connects to the motherboard through a land grid array (LGA) surface mount socket. The socket contains 775 contacts arrayed about a cavity in the center of the socket with solder balls for surface mounting to the motherboard. The socket is named LGA775 socket. A description of the socket is in the *LGA775 Socket Mechanical Design Guide*.

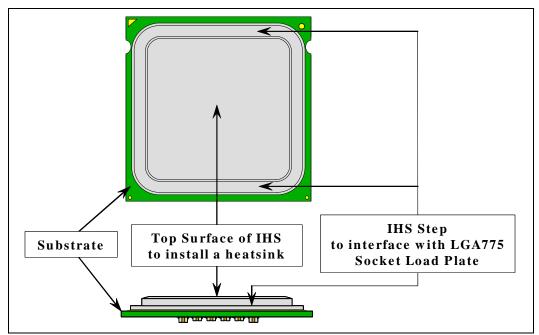

The package includes an integrated heat spreader (IHS) that is shown in Figure 2-1 for illustration only. Refer to the processor datasheet for further information. In case of conflict, the package dimensions in the processor datasheet supersedes dimensions provided in this document.

Figure 2-1. Package IHS Load Areas

#### Processor Thermal/Mechanical Information

The primary function of the IHS is to transfer the non-uniform heat distribution from the die to the top of the IHS, out of which the heat flux is more uniform and spread over a larger surface area (not the entire IHS area). This allows more efficient heat transfer out of the package to an attached cooling device. The top surface of the IHS is designed to be the interface for contacting a heatsink.

The IHS also features a step that interfaces with the LGA775 socket load plate, as described in *LGA775 Socket Mechanical Design Guide*. The load from the load plate is distributed across two sides of the package onto a step on each side of the IHS. It is then distributed by the package across all of the contacts. When correctly actuated, the top surface of the IHS is above the load plate allowing proper installation of a heatsink on the top surface of the IHS. After actuation of the socket load plate, the seating plane of the package is flush with the seating plane of the socket. Package movement during socket actuation is along the Z direction (perpendicular to substrate) only. Refer to the *LGA775 Socket Mechanical Design Guide* for further information about the LGA775 socket.

The processor package has mechanical load limits that are specified in the processor datasheet. The specified maximum static and dynamic load limits should not be exceeded during their respective stress conditions. These include heatsink installation, removal, mechanical stress testing, and standard shipping conditions.

- When a compressive static load is necessary to ensure thermal performance of the thermal interface material between the heatsink base and the IHS, it should not exceed the corresponding specification given in the processor datasheet.

- When a compressive static load is necessary to ensure mechanical performance, it should remain in the minimum/maximum range specified in the processor datasheet

- The heatsink mass can also generate additional dynamic compressive load to the package during a mechanical shock event. Amplification factors due to the impact force during shock must be taken into account in dynamic load calculations. The total combination of dynamic and static compressive load should not exceed the processor datasheet compressive dynamic load specification during a vertical shock. For example, with a 0.550 kg [1.2 lb] heatsink, an acceleration of 50G during an 11 ms trapezoidal shock with an amplification factor of 2 results in approximately a 539 N [117 lbf] dynamic load on the processor package. If a 178 N [40 lbf] static load is also applied on the heatsink for thermal performance of the thermal interface material the processor package could see up to a 717 N [156 lbf]. The calculation for the thermal solution of interest should be compared to the processor datasheet specification.

No portion of the substrate should be used as a load-bearing surface.

Finally, the processor datasheet provides package handling guidelines in terms of maximum recommended shear, tensile and torque loads for the processor IHS relative to a fixed substrate. These recommendations should be followed in particular for heatsink removal operations.

#### 2.1.2 Heatsink Attach

#### 2.1.2.1 General Guidelines

There are no features on the LGA775 socket to directly attach a heatsink: a mechanism must be designed to attach the heatsink directly to the motherboard. In addition to holding the heatsink in place on top of the IHS, this mechanism plays a significant role in the robustness of the system in which it is implemented, in particular:

- Ensuring thermal performance of the thermal interface material (TIM) applied between the IHS and the heatsink. TIMs based on phase change materials are very sensitive to applied pressure: the higher the pressure, the better the initial performance. TIMs such as thermal greases are not as sensitive to applied pressure. Designs should consider a possible decrease in applied pressure over time due to potential structural relaxation in retention components.

- Ensuring system electrical, thermal, and structural integrity under shock and vibration events. The mechanical requirements of the heatsink attach mechanism depend on the mass of the heatsink and the level of shock and vibration that the system must support. The overall structural design of the motherboard and the system have to be considered when designing the heatsink attach mechanism. Their design should provide a means for protecting LGA775 socket solder joints. One of the strategies for mechanical protection of the socket is to use a preload and high stiffness clip. This strategy is implemented by the reference design and described in Section 6.7.

**Note:** Package pull-out during mechanical shock and vibration is constrained by the LGA775 socket load plate (refer to the *LGA775 Socket Mechanical Design Guide* for further information).

#### 2.1.2.2 Heatsink Clip Load Requirement

The attach mechanism for the heatsink developed to support the processor should create a static preload on the package between **18 lbf** and **70 lbf** throughout the life of the product for designs compliant with the reference design assumptions:

- 72 mm x 72 mm mounting hole span for ATX (refer to Figure 7-47).

- TMA preload vs. stiffness for BTX within the limits shown on Figure 5-6.

- And no board stiffening device (backing plate, chassis attach, etc.).

The minimum load is required to protect against fatigue failure of socket solder joint in temperature cycling.

It is important to take into account potential load degradation from creep over time when designing the clip and fastener to the required minimum load. This means that, depending on clip stiffness, the initial preload at beginning of life of the product may be significantly higher than the minimum preload that must be met throughout the life of the product. For additional guidelines on mechanical design, in particular on designs departing from the reference design assumptions refer to Appendix A.

For clip load metrology guidelines, refer to Appendix B.

#### 2.1.2.3 Additional Guidelines

In addition to the general guidelines given above, the heatsink attach mechanism for the processor should be designed to the following guidelines:

- Holds the heatsink in place under mechanical shock and vibration events and applies force to the heatsink base to maintain desired pressure on the thermal interface material. Note that the load applied by the heatsink attach mechanism must comply with the package specifications described in the processor datasheet. One of the key design parameters is the height of the top surface of the processor IHS above the motherboard. The IHS height from the top of board is expected to vary from 7.517 mm to 8.167 mm. This data is provided for information only, and should be derived from:

- The height of the socket seating plane above the motherboard after reflow, given in the *LGA775 Socket Mechanical Design Guide* with its tolerances.

- The height of the package, from the package seating plane to the top of the IHS, and accounting for its nominal variation and tolerances that are given in the corresponding processor datasheet.

- Engages easily, and if possible, without the use of special tools. In general, the heatsink is assumed to be installed after the motherboard has been installed into the chassis.

- *Minimizes contact with the motherboard surface during installation* and actuation to avoid scratching the motherboard.

## 2.2 Thermal Requirements

Refer to the datasheet for the processor thermal specifications. The majority of processor power is dissipated through the IHS. There are no additional components, e.g., BSRAMs, which generate heat on this package. The amount of power that can be dissipated as heat through the processor package substrate and into the socket is usually minimal.

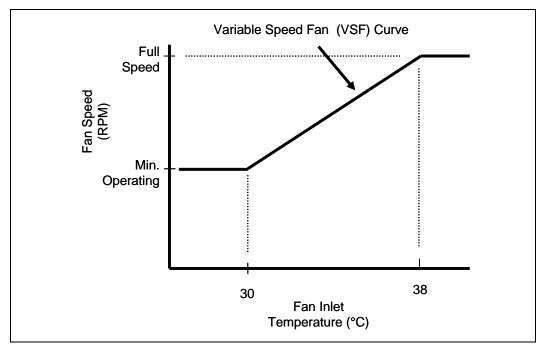

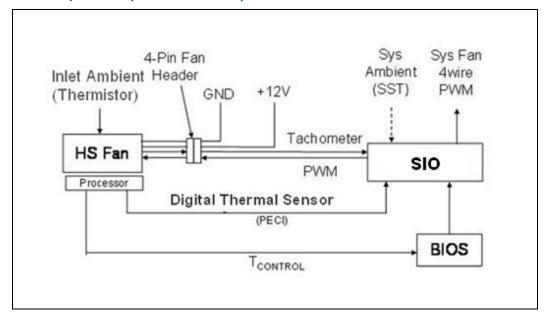

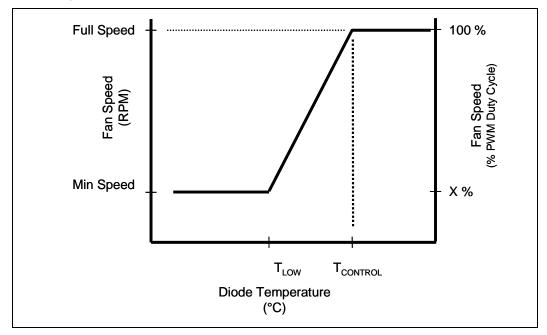

The thermal limits for the processor are the Thermal Profile and  $T_{CONTROL}$ . The Thermal Profile defines the maximum case temperature as a function of power being dissipated.  $T_{CONTROL}$  is a specification used in conjunction with the temperature reported by the digital thermal sensor and a fan speed control method. Designing to these specifications allows optimization of thermal designs for processor performance and acoustic noise reduction.

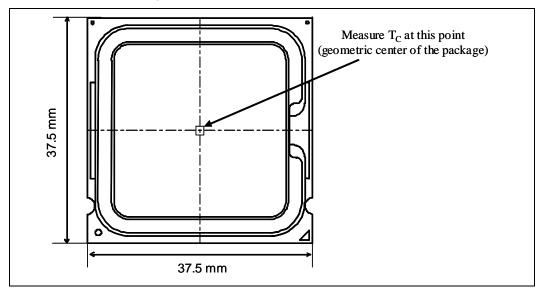

### 2.2.1 Processor Case Temperature

For the processor, the case temperature is defined as the temperature measured at the geometric center of the package on the surface of the IHS. For illustration, Figure 2-2 shows the measurement location for a 37.5 mm x 37.5 mm [1.474 in x 1.474 in] 775-Land LGA processor package with a 28.7 mm x 28.7 mm [1.13 in x 1.13 in] IHS top surface. Techniques for measuring the case temperature are detailed in Section 3.4.

**Note:** In case of conflict, the package dimensions in the processor datasheet supersedes dimensions provided in this document.

Figure 2-2. Processor Case Temperature Measurement Location

#### 2.2.2 Thermal Profile

The Thermal Profile defines the maximum case temperature as a function of processor power dissipation. The TDP and Maximum Case Temperature are defined as the maximum values of the thermal profile. By design the thermal solutions must meet the thermal profile for all system operating conditions and processor power levels. Refer to the processor datasheet for further information.

While the thermal profile provides flexibility for ATX /BTX thermal design based on its intended target thermal environment, thermal solutions that are intended to function in a multitude of systems and environments need to be designed for the worst-case thermal environment. The majority of ATX /BTX platforms are targeted to function in an environment that will have up to a 35 °C ambient temperature external to the system.

**Note:** For ATX platforms, an active air-cooled design, assumed be used in ATX Chassis, with a fan installed at the top of the heatsink equivalent to the reference design (see Chapter 6) should be designed to manage the processor TDP at an inlet temperature of  $35 \, ^{\circ}\text{C} + 5 \, ^{\circ}\text{C} = 40 \, ^{\circ}\text{C}$ .

For BTX platforms, a front-to-back cooling design equivalent to Intel BTX TMA Type II reference design (see the Chapter 5) should be designed to manage the processor TDP at an inlet temperature of 35 °C + 0.5 °C = 35.5 °C.

The slope of the thermal profile was established assuming a generational improvement in thermal solution performance of the reference design. For an example of Intel  $^{\mathbb{W}}$  Core  $^{\mathbb{W}}$ 2 Duo processor with 4 MB cache at Tc-max of 60.1 °C in ATX platform, its improvement is about 16% over the Intel reference design (D60188-001). This performance is expressed as the slope on the thermal profile and can be thought of as the thermal resistance of the heatsink attached to the processor,  $\Psi_{\text{CA}}$  (Refer to

Section 3.1). The intercept on the thermal profile assumes a maximum ambient operating condition that is consistent with the available chassis solutions.

To determine compliance to the thermal profile, a measurement of the actual processor power dissipation is required. The measured power is plotted on the Thermal Profile to determine the maximum case temperature. Using the example in Figure 2-3 for the Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor with 4 MB cache at Tc-max of 60.1 °C dissipating 50 W, the maximum case temperature is 56.2 °C. See the datasheet for the thermal profile.

70.0

(C) 60.0

Thermal Profile

TDP

40.0

0 10 20 30 40 50 60 70

Power (W)

Figure 2-3. Example Thermal Profile

#### $\mathbf{2.2.3} \quad \mathbf{T}_{\text{CONTROL}}$

$T_{CONTROL}$  defines the maximum operating temperature for the digital thermal sensor when the thermal solution fan speed is being controlled by the digital thermal sensor. The  $T_{CONTROL}$  parameter defines a very specific processor operating region where fan speed can be reduced. This allows the system integrator a method to reduce the acoustic noise of the processor cooling solution, while maintaining compliance to the processor thermal specification.

**Note:** The T<sub>CONTROL</sub> value for the processor is relative to the Thermal Control Circuit (TCC) activation set point which will be seen as 0 using the digital thermal sensor. As a result the T<sub>CONTROL</sub> value will always be a negative number. See Chapter 4 for the discussion the thermal management logic and features and Chapter 7 on *Intel® Quiet System Technology (Intel® QST)*.

The value of  $T_{CONTROL}$  is driven by a number of factors. One of the most significant of these is the processor idle power. As a result a processor with a high (closer to 0)

$T_{CONTROL}$  will dissipate more power than a part with lower value (farther from 0, e.g., more negative number) of  $T_{CONTROL}$  when running the same application.

This is achieved in part by using the  $\Psi_{\text{CA}}$  vs. RPM and RPM vs. Acoustics (dBA) performance curves from the Intel enabled thermal solution. A thermal solution designed to meet the thermal profile would be expected to provide similar acoustic performance of different parts with potentially different  $T_{\text{CONTROL}}$  values.

The value for  $T_{CONTROL}$  is calculated by the system BIOS based on values read from a factory configured processor register. The result can be used to program a fan speed control component. See the appropriate processor datasheet for further details on reading the register and calculating  $T_{CONTROL}$ .

See Chapter 7, *Intel<sup>®</sup> Quiet System Technology (Intel<sup>®</sup> QST)*, for details on implementing a design using T<sub>CONTROL</sub> and the Thermal Profile.

## 2.3 Heatsink Design Considerations

To remove the heat from the processor, three basic parameters should be considered:

- The area of the surface on which the heat transfer takes place. Without any enhancements, this is the surface of the processor package IHS. One method used to improve thermal performance is by attaching a heatsink to the IHS. A heatsink can increase the effective heat transfer surface area by conducting heat out of the IHS and into the surrounding air through fins attached to the heatsink base.

- The conduction path from the heat source to the heatsink fins. Providing a direct conduction path from the heat source to the heatsink fins and selecting materials with higher thermal conductivity typically improves heatsink performance. The length, thickness, and conductivity of the conduction path from the heat source to the fins directly impact the thermal performance of the heatsink. In particular, the quality of the contact between the package IHS and the heatsink base has a higher impact on the overall thermal solution performance as processor cooling requirements become stricter. Thermal interface material (TIM) is used to fill in the gap between the IHS and the bottom surface of the heatsink, and thereby improve the overall performance of the stack-up (IHS-TIM-Heatsink). With extremely poor heatsink interface flatness or roughness, TIM may not adequately fill the gap. The TIM thermal performance depends on its thermal conductivity as well as the pressure applied to it. Refer to Section 2.3.4 and Appendix C for further information on TIM and on bond line management between the IHS and the heatsink base.

- The heat transfer conditions on the surface on which heat transfer takes place. Convective heat transfer occurs between the airflow and the surface exposed to the flow. It is characterized by the local ambient temperature of the air, T<sub>A</sub>, and the local air velocity over the surface. The higher the air velocity over the surface, and the cooler the air, the more efficient is the resulting cooling. The nature of the airflow can also enhance heat transfer using convection. Turbulent flow can provide improvement over laminar flow. In the case of a heatsink, the surface exposed to the flow includes in particular the fin faces and the heatsink base.

**Active heatsinks** typically incorporate a fan that helps manage the airflow through the heatsink.

Passive heatsink solutions require in-depth knowledge of the airflow in the chassis. Typically, passive heatsinks see lower air speed. These heatsinks are therefore typically larger (and heavier) than active heatsinks due to the increase in fin surface required to meet a required performance. As the heatsink fin density (the number of fins in a given cross-section) increases, the resistance to the airflow increases: it is more likely that the air travels around the heatsink instead of through it, unless air bypass is carefully managed. Using air-ducting techniques to manage bypass area can be an effective method for controlling airflow through the heatsink.

#### 2.3.1 Heatsink Size

The size of the heatsink is dictated by height restrictions for installation in a system and by the real estate available on the motherboard and other considerations for component height and placement in the area potentially impacted by the processor heatsink. The height of the heatsink must comply with the requirements and recommendations published for the motherboard form factor of interest. Designing a heatsink to the recommendations may preclude using it in system adhering strictly to the form factor requirements, while still in compliance with the form factor documentation.

For the ATX/microATX form factor, it is recommended to use:

- The ATX motherboard keep-out footprint definition and height restrictions for enabling components, defined for the platforms designed with the LGA775 socket in Appendix H of this design guide.

- The motherboard primary side height constraints defined in the *ATX Specification V2.1* and the *microATX Motherboard Interface Specification V1.1* found at <a href="http://www.formfactors.org/">http://www.formfactors.org/</a>.

The resulting space available above the motherboard is generally not entirely available for the heatsink. The target height of the heatsink must take into account airflow considerations (for fan performance for example) as well as other design considerations (air duct, etc.).

For BTX form factor, it is recommended to use:

- The BTX motherboard keep-out footprint definitions and height restrictions for enabling components for platforms designed with the LGA77 socket in Appendix H of this design guide.

- An overview of other BTX system considerations for thermal solutions can be obtained in the latest version of the *Balanced Technology Extended (BTX) System Design Guide* found at <a href="http://www.formfactors.org/">http://www.formfactors.org/</a>.

#### 2.3.2 Heatsink Mass

With the need to push air cooling to better performance, heatsink solutions tend to grow larger (increase in fin surface) resulting in increased mass. The insertion of highly thermally conductive materials like copper to increase heatsink thermal conduction performance results in even heavier solutions. As mentioned in Section 2.1, the heatsink mass must take into consideration the package and socket load limits, the heatsink attach mechanical capabilities, and the mechanical shock and vibration profile targets. Beyond a certain heatsink mass, the cost of developing and implementing a heatsink attach mechanism that can ensure the system integrity under the mechanical shock and vibration profile targets may become prohibitive.

The recommended maximum heatsink mass for the ATX thermal solution is 550g. This mass includes the fan and the heatsink only. The attach mechanism (clip, fasteners, etc.) are not included.

The mass limit for BTX heatsinks that use Intel reference design structural ingredients is 900 grams. The BTX structural reference component strategy and design is reviewed in depth in the latest version of the *Balanced Technology Extended (BTX) System Design Guide*.

**Note:** The 550g mass limit for ATX solutions is based on the capabilities of the reference design components that retain the heatsink to the board and apply the necessary preload. Any reuse of the clip and fastener in derivative designs should not exceed 550g. ATX Designs that have a mass of greater than 550g should analyze the preload as discussed in Appendix A and retention limits of the fastener.

**Note:** The chipset components on the board are affected by processor heatsink mass. Exceeding these limits may require the evaluation of the chipset for shock and vibration.

### 2.3.3 Package IHS Flatness

The package IHS flatness for the product is specified in the datasheet and can be used as a baseline to predict heatsink performance during the design phase.

Intel recommends testing and validating heatsink performance in full mechanical enabling configuration to capture any impact of IHS flatness change due to combined socket and heatsink loading. While socket loading alone may increase the IHS warpage, the heatsink preload redistributes the load on the package and improves the resulting IHS flatness in the enabled state.

#### 2.3.4 Thermal Interface Material

Thermal interface material application between the processor IHS and the heatsink base is generally required to improve thermal conduction from the IHS to the heatsink. Many thermal interface materials can be pre-applied to the heatsink base prior to shipment from the heatsink supplier and allow direct heatsink attach, without the need for a separate thermal interface material dispense or attach process in the final assembly factory.

All thermal interface materials should be sized and positioned on the heatsink base in a way that ensures the entire processor IHS area is covered. It is important to compensate for heatsink-to-processor attach positional alignment when selecting the proper thermal interface material size.

When pre-applied material is used, it is recommended to have a protective application tape over it. This tape must be removed prior to heatsink installation.

## 2.4 System Thermal Solution Considerations

#### 2.4.1 Chassis Thermal Design Capabilities

The Intel reference thermal solutions and Intel Boxed Processor thermal solutions assume that the chassis delivers a maximum  $T_A$  at the inlet of the processor fan heatsink. The following tables show the  $T_A$  requirements for the reference solutions and Intel Boxed Processor thermal solutions.

Table 2-1. Heatsink Inlet Temperature of Intel Reference Thermal Solutions

|                               | ATX D60188-<br>001 | ATX E18764-001 | BTX Type II |

|-------------------------------|--------------------|----------------|-------------|

| Heatsink Inlet<br>Temperature | 40 °C              | 40 °C          | 35.5 °C     |

#### NOTE:

1. Intel reference designs (D60188-001 and E18764-001) are assumed be used in the chassis where expected the temperature rise is 5  $^{\circ}$ C.

Table 2-2. Heatsink Inlet Temperature of Intel Boxed Processor Thermal Solutions

|                               | Boxed Processor for Intel® Core™2 Duo Processor<br>E6000 and E4000 Series, Intel® Pentium® Dual Core<br>Processor E2000 Series, and Intel® Celeron® Dual-<br>Core Processor E1000 Series |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Heatsink Inlet<br>Temperature | 40 °C                                                                                                                                                                                    |

#### NOTE:

1. Boxed Processor thermal solutions for ATX assume the use of the thermally advantaged chassis (refer to *Thermally Advantaged Chassis version 1.1* for Thermally Advantaged Chassis thermal and mechanical requirements).

## 2.4.2 Improving Chassis Thermal Performance

The heat generated by components within the chassis must be removed to provide an adequate operating environment for both the processor and other system components. Moving air through the chassis brings in air from the external ambient environment and transports the heat generated by the processor and other system components out of the system. The number, size and relative position of fans and vents determine the chassis thermal performance, and the resulting ambient temperature around the processor. The size and type (passive or active) of the thermal solution and the amount of system airflow can be traded off against each other to meet specific system design constraints. Additional constraints are board layout, spacing, component placement, acoustic requirements and structural considerations that limit the thermal solution size. For more information, refer to the *Performance ATX Desktop System Thermal Design Suggestions* or *Performance microATX Desktop System Thermal Design Suggestions* or *Balanced Technology Extended (BTX) System Design Guide* documents available on the <a href="http://www.formfactors.org/">http://www.formfactors.org/</a> web site.

In addition to passive heatsinks, fan heatsinks and system fans are other solutions that exist for cooling integrated circuit devices. For example, ducted blowers, heat pipes and liquid cooling are all capable of dissipating additional heat. Due to their varying attributes, each of these solutions may be appropriate for a particular system implementation.

To develop a reliable, cost-effective thermal solution, thermal characterization and simulation should be carried out at the entire system level, accounting for the thermal requirements of each component. In addition, acoustic noise constraints may limit the size, number, placement, and types of fans that can be used in a particular design.