## Dr. Jerry L. Hudgins Department of Electrical Engineering University of South Carolina

**Transistor Review**

8/12/03

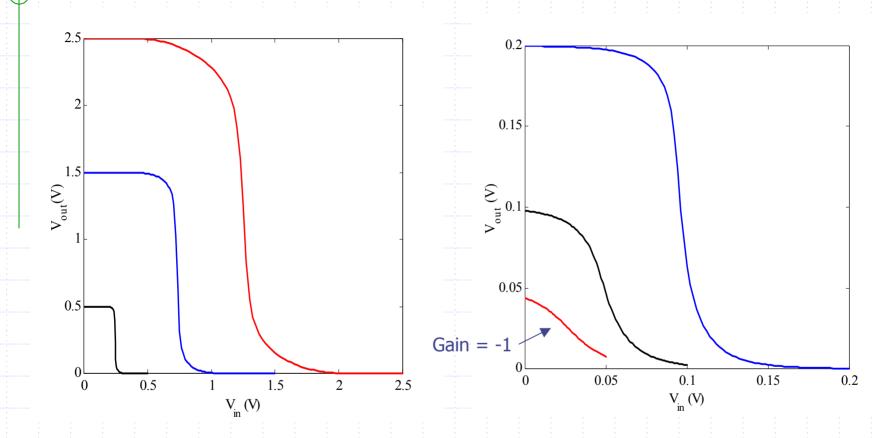

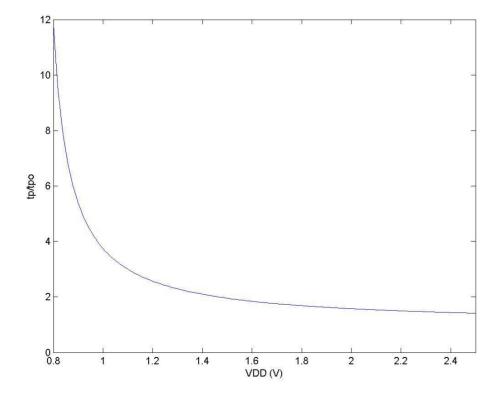

## Supply Voltage Effects

## Gain as a Function of $V_{DD}$

The gain can be improved by lowering the supply voltage, however, below a few tenths of a volt, the gain deteriorates.

**Transistor Review**

Effects of Reducing the Supply Voltage Gain improves Energy dissipation is lowered Reduces internal noise (crosstalk) dc characteristics become sensitive to variations in device parameters Increases sensitivity to external noise Increases the propagation delay times!

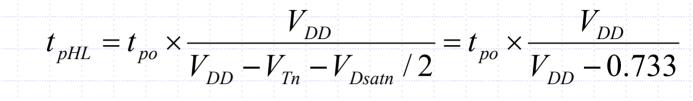

## Supply Voltage Effect on Propagation Delay

Average equivalent resistance during the load capacitance discharge.

$$R_{eq} = \frac{1}{V_{DD}/2} \int_{V_{DD}/2}^{V_{DD}} \frac{V}{I_{Dsat}(1+\lambda V)} dV \approx \frac{3V_{DD}}{4I_{Dsat}} \left(1 - \frac{7\lambda V_{DD}}{9}\right)$$

$$I_{Dsat} = k \left| \frac{W}{L} \right| (V_{DD} - V_t) V_{DSsat} - \frac{V_{DSsat}^2}{2}$$

#### Ignoring channel-length modulation factor:

$$t_{pHL} = 0.69R_{eqn}C_{L-HL} = 0.69\frac{3C_L V_{DD}}{4I_{Dsatn}} = 0.52\frac{C_L V_{DD}}{(W_n / L_n)k'_n V_{Dsatn}(V_{DD} - V_{Tn} - V_{Dsatn} / 2)}$$

$$t_{pHL} = t_{po} \times \frac{V_{DD}}{V_{DD} - V_{Tn} - V_{Dsatn} / 2}$$

**Transistor Review**

## Supply Voltage Effect on Propagation Delay

Note that supply voltages below 1.1 V cause an enormous increase in the propagation delay.

**Transistor Review**

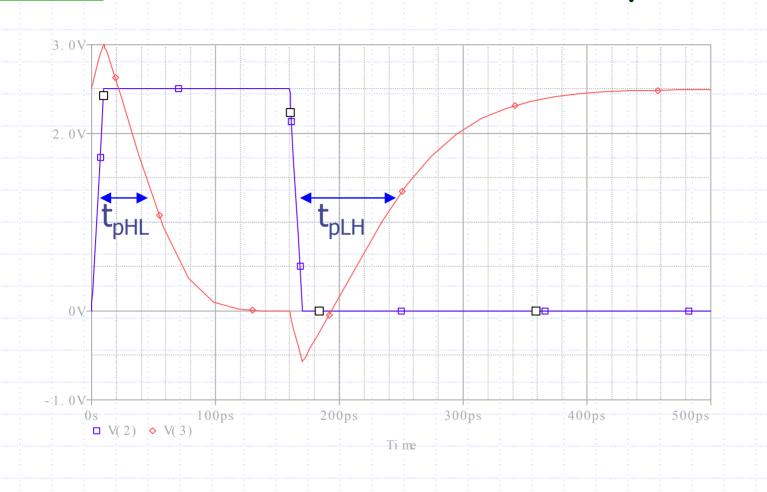

# Propagation Delay Effects from Sizing

## **Transient Response**

**Transistor Review**

8/12/03

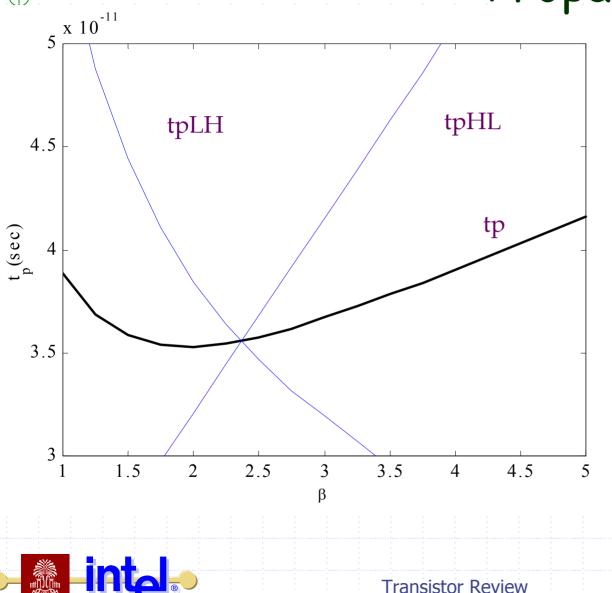

#### NMOS/PMOS Ratios

For equal resistance values, the width ratio,  $\beta = W_p/W_n$ , should be 3 to 3.5. If symmetry and reduced noise margins are not primary, then reducing the PMOS channel width can reduce the propagation delay.

Consider two identical cascaded inverters where the drain diffusion capacitances of the first inverter and the gate capacitances of the second inverter plus the interconnect capacitance between them are included :

$$C_{L} = (C_{dp1} + C_{dn1}) + (C_{gp2} + C_{gn2}) + C_{W}$$

#### NMOS/PMOS Ratios

$\frac{\partial t_p}{dm} = 0$

When the PMOS are made  $\beta$  times larger than the NMOS, then all capacitances scale the same way.

$$C_{L} = (1 + \beta)(C_{dn1} + C_{gn2}) + C_{W}$$

Propagation delay then becomes: (where  $R_{eqn}$  and  $R_{eqp}$  are resistances of identically sized transistors):

$$t_{p} = \frac{0.69}{2} \left[ (1+\beta)(C_{dn1} + C_{gn2}) + C_{W} \right] \left( R_{eqn} + \frac{R_{eqp}}{\beta} \right)$$

Optimal  $\beta$  then becomes :

$$\beta_{opt} = \sqrt{\frac{R_{eqp}}{R_{eqn}}} \left(1 + \frac{C_W}{C_{dn1} + C_{gn2}}\right)$$

## NMOS/PMOS Ratio Effects on Propagation Delay

The smallest delay is for  $\beta$ =1.9. Equal propagation delays require  $\beta$ =2.4.

8/12/03

#### Inverter Sizing

- •Assume a symmetrical inverter (PMOS and NMOS are sized to give identical rise and fall times).

- •Load capacitance can be divided into intrinsic and extrinsic components:  $C_{I} = C_{int} + C_{ext}$

- Intrinsic capacitance represents the intrinsic output capacitance of the inverter or the self-loading.

It is composed of the diffusion capacitances of transistors and gate-drain overlap (Miller) capacitances.

- •Extrinsic capacitance is the extrinsic load capacitance made up of the input gate capacitances (fan-out) and wiring capacitance.

#### Inverter Sizing

# Let $R_{eq}$ be the equivalent resistance of the gate. Then the propagation delay is:

$t_{p} = 0.69R_{eq}(C_{int} + C_{ext}) = 0.69R_{eq}C_{int}(1 + C_{ext}/C_{int}) = t_{po}(1 + C_{ext}/C_{int})$

$t_{po}$  is the intrinsic or unloaded delay.

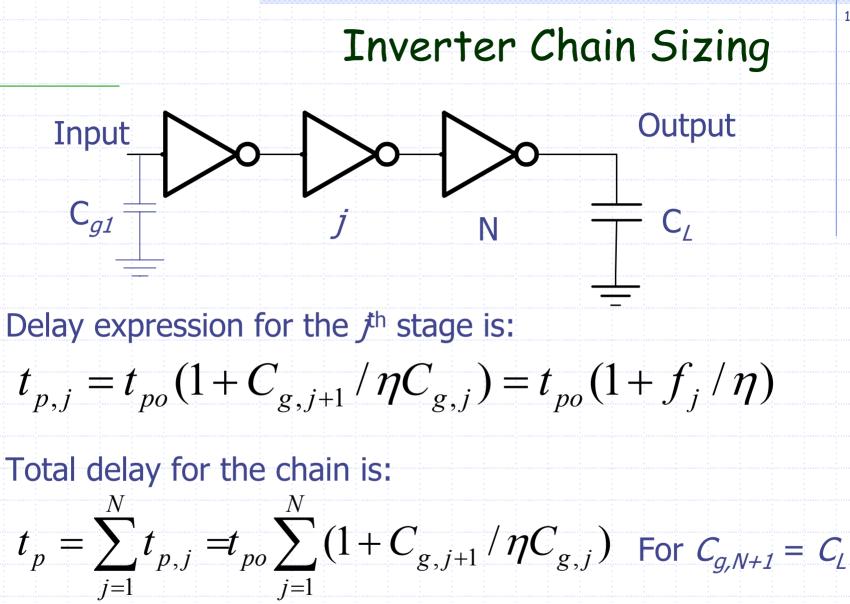

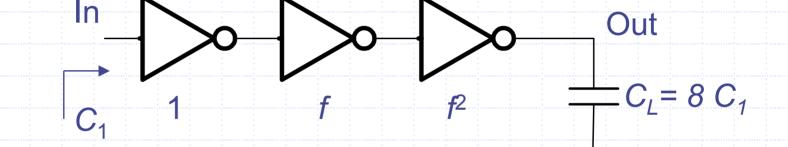

### Sizing a Chain of Inverters

Increasing an inverter's size decreases the delay, but it increases the input capacitance. The intrinsic output capacitance is proportional to the gate capacitance and both are proportional the transistor/inverter sizing.

$$C_{\rm int} = \eta C_g$$

$\eta$  is the proportionality factor and is near to unity in value.

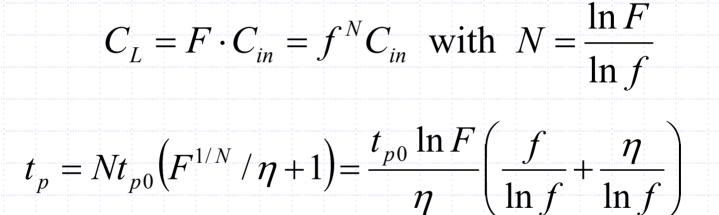

## Sizing of Inverter Chain

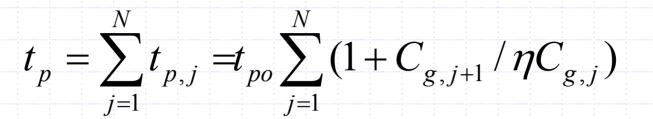

Therefore, the delay of an inverter is only a function of the ratio, *f*, between its external load capacitance and its input capacitance!!

$$t_{p} = t_{po} (1 + C_{ext} / \eta C_{g}) = t_{po} (1 + f / \eta)$$

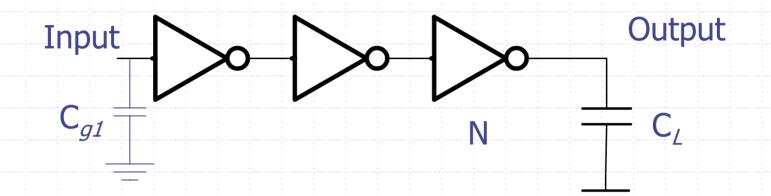

#### $C_{g1}$ is the input capacitance of the 1<sup>st</sup> inverter. $C_{L}$ is the load capacitance at the end of the fixed chain.

**Transistor Review**

There are N-1 unknowns, given  $C_{g1}$  and  $C_L$ . The minimum delay is found by taking N-1 partial derivatives and setting them each to 0:

$$\partial t_p / \partial C_{g,j} = 0$$

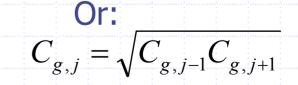

Result is:

$$C_{g,j+1} / C_{g,j} = C_{g,j} / C_{g,j-1}$$

**Transistor Review**

$$C_{g,j} = \sqrt{C_{g,j-1}C_{g,j+1}}$$

This expression means that each inverter in the chain is sized up by the same factor, *f*, with respect to the preceding gate, has the same effective fan-out  $(f_j=f)$ , and therefore the same delay.

Thus, given  $C_{g,1}$  and  $C_L$ , the sizing factor for each stage to give the same delay through each stage, and the minimal total delay is:

$$f = \sqrt[N]{C_L / C_{g,1}} \equiv \sqrt[N]{F}$$

The minimal delay through the inverter chain is then:

$$t_p = N t_{po} (1 + \sqrt[N]{F} / \eta)$$

F represents the overall effective fan-out of the circuit and is equal to:  $F = C_L / C_{g,1}$

## Inverter Chain Sizing: The Problem Posed One way

Usually  $C_{q,1}$  is associated with a minimally-sized gate.

$$f_p = Nt_{po}(1 + \sqrt[N]{F} / \eta)$$

For a given F(e.g. given a load capacitance to drive from a minimally-sized gate), what is the number of stages that obeys the minimal propagation delay expression derived above?

If *N* is too large then the first term dominates (intrinsic delay of the stages dominates). If *N* is too small then the effective fan-out of each stage becomes too large and the second term dominates.

#### Inverter Chain Sizing: The Solution

Differentiate the delay expression with respect to N and set to 0. (1)

$$\partial t_p / \partial N = t_{po} \left(1 + \sqrt[N]{F} / \eta\right) + N t_{po} \left(\ln F\right) \left(\frac{\sqrt[N]{F}}{\eta}\right) \left(\frac{-1}{N^2}\right) = 0$$

$$F = f^N = e^{N(1+\eta/f)}$$

$$\sqrt[N]{F} = f = e^{(1+\eta/f)}$$

#### Inverter Chain Sizing: The Solution

Given the first gate (usually minimally-sized), then we know its input capacitance,  $C_{g,1}$  and its intrinsic output capacitance,  $C_{int}$ .

$$\eta = C_{\text{int}} / C_{g,1}$$

Knowing  $\eta$ , iteratively solve for *f* using the derived expression:  $f = e^{(1+\eta/f)}$

We know the load capacitance we are trying to drive,  $C_L$ , so we also know  $F = C_L / C_{g,1}$ .

#### Inverter Chain Sizing: The Solution

Finally, having values for *f* and *F*, we can find N; the number of stages needed to drive the load capacitance that gives a minimal propagation delay of the signal through the stages.

$$f = \sqrt[N]{F}$$

Also, we can compute the delay time using the expression previously derived:

$$t_p = Nt_{po}(1 + \sqrt[N]{F} / \eta)$$

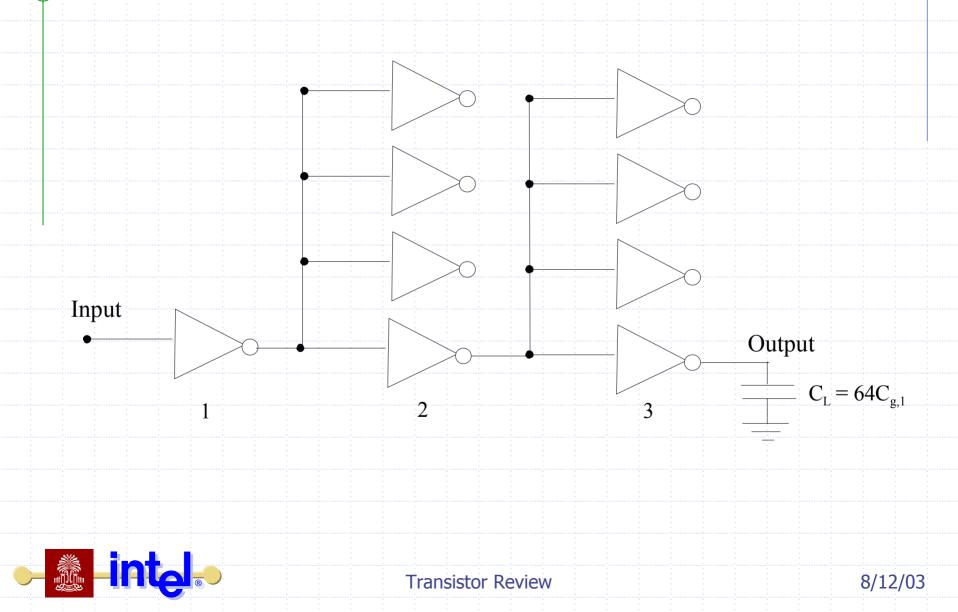

#### $C_L/C_1$ has to be evenly distributed across N = 3 stages:

$$f = \sqrt[3]{C_L / C_1} = \sqrt[3]{8} = 2$$

**Transistor Review**

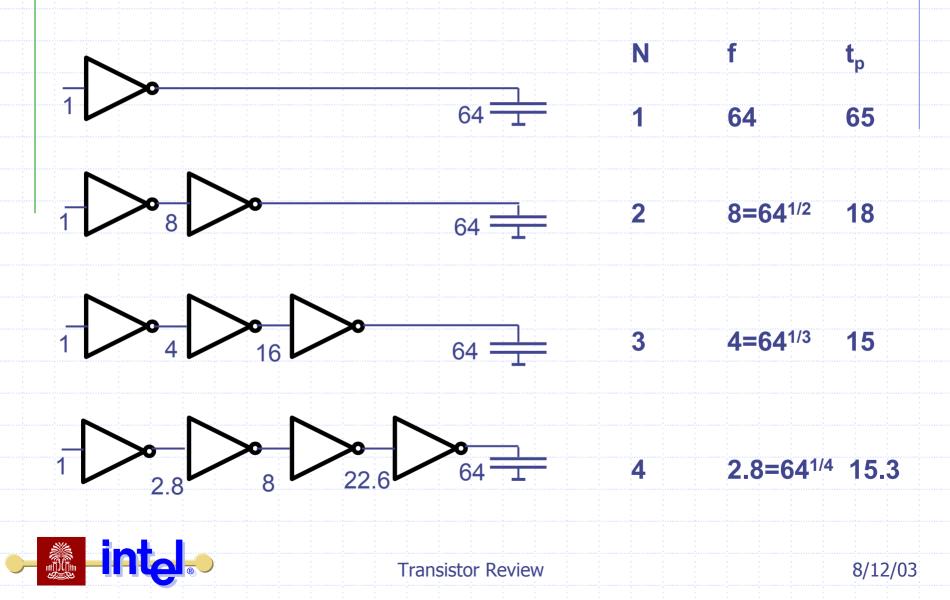

# Example 2: Optimum Number of Stages

For a given load,  $C_L$  and given input capacitance  $C_{in}$ Find optimal sizing *f* and minimal delay.

## Number of Stages to Minimize $t_p$

#### Homework #1

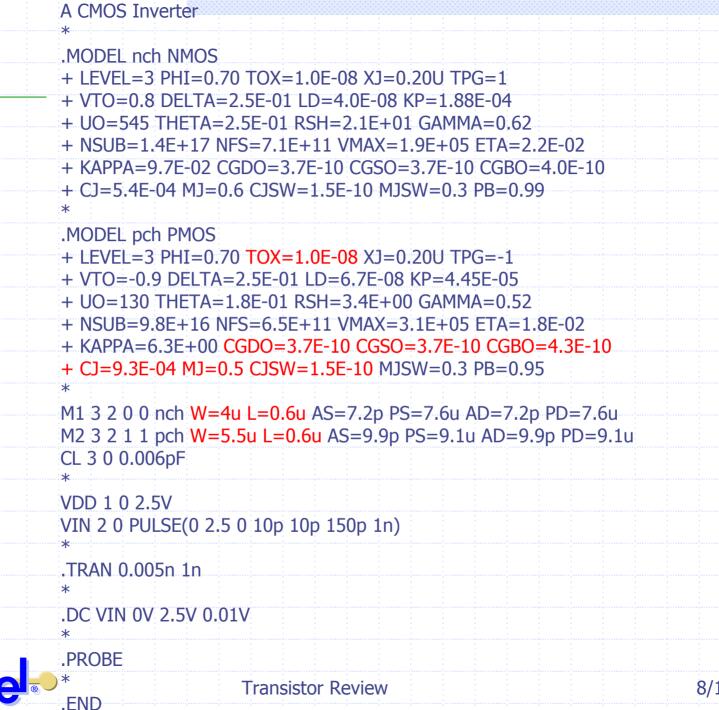

Using the Level-3 CMOS inverter model given above, determine the t<sub>pHL</sub> and t<sub>pLH</sub> for 6 to 10 different supply voltage values from 2.5 to 1.1 V.

Do the simulations again using  $L_n = L_p = 0.25 \ \mu m$ ,  $W_n = 2 \ \mu m$ , and  $W_p = 4 \ \mu m$ .

You will need to modify the VIN values for the pulse and dc analysis as VDD is changed.

Transistor Review

#### Homework #2

Determine the sizes (f) of the inverters in the circuit below such that the delay time between input and output is minimized. (Hint: First find the ratios between the devices that minimize the delay. You should find that:  $\frac{4C_{g,2}}{4C_{g,3}} = \frac{4C_{g,3}}{C_L}$

Determine the sizes of the inverters if the extra fan-out at each stage is not taken into account.

$C_{g,1}$   $C_{g,2}$   $C_{g,3}$