# Enabling Breakthroughs In Technology

#### Mike Mayberry

Director of Components Research VP, Technology and Manufacturing Group Intel Corporation

June 2011

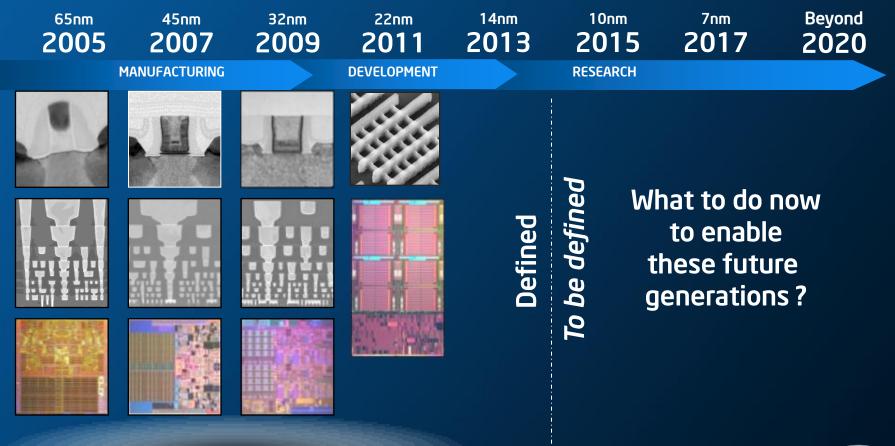

# Enabling a Steady Technology Cadence

#### **TECHNOLOGY GENERATION**

Not to scale

# But first some old technology ...

#### Transistor Innovations Enable Technology Cadence

### Exploration – late 90's

- Talk of 0.1um as the end due to leakage power

- 248nm lithography limited device exploration

# Then enabled Creation of sub-resolution features Study of dense patterns (later)

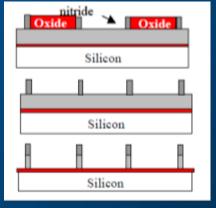

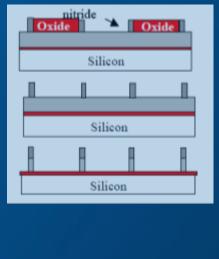

#### 1997 Intel Invention Spacer based pattern

| Resist Resist |

|---------------|

| poly          |

| Silicon       |

| Oxide Oxide   |

| Silicon       |

| Oxide Oxide   |

| Silicon       |

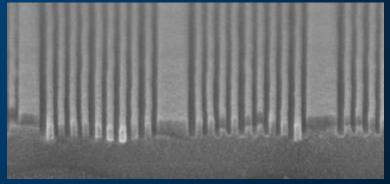

Intel: 10nm planar transistor

# Exploration was not limited by lithography

#### Exploration – late 90's

- Talk of 0.1um as the end due to leakage power

- 248nm lithography limited device exploration

#### 1997 Intel Invention Spacer based pattern

| Resist Resist    |     |

|------------------|-----|

| poly             |     |

| Silicon          | L.  |

| Oxide Oxide poly |     |

| Silicon          | - H |

| Oxide Dxide      | Ľ   |

| Silicon          |     |

#### Exploration today 193 immersion lithography + Spacer based pattern twice

Pitch Quartering with 193i, 16nm features

#### Scalable to Sub 10nm features

Exploration (still) not limited by lithography (intel.

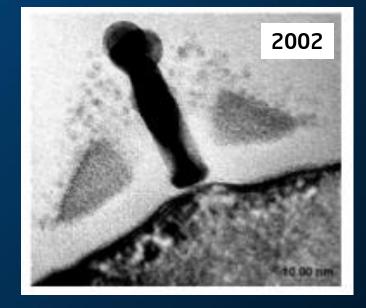

#### Evaluation – early 00's

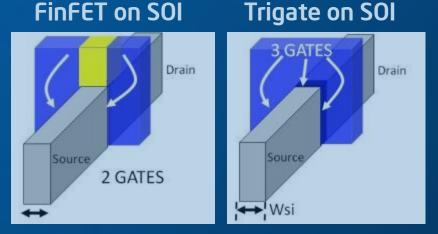

- 15 yrs discussion of possible non-planar device concepts

- No systematic scaling studies

#### Then enabled

- Assessment of scaling challenges and critical parameters

Focus for optimization

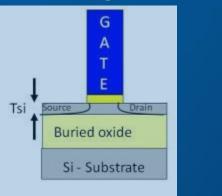

- Planar Thin body SOI **FinFET on SOI** Trigate on SOI G G GATES Drain A Drain т Е Drain Tsi Source Orain **Buried** oxide Source Source 2 GATES Si - Substrate Si - Substrate ↔ Wsi 5-0

Build all variations and compare

Evaluation – early 00's

15 yrs discussion of possible non-planar device concepts

No systematic scaling studies

#### Thin body SOI

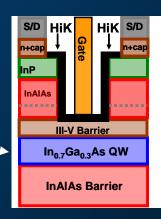

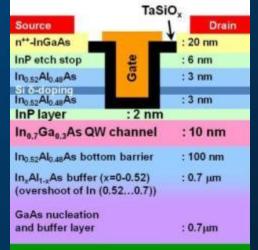

# Evaluation today Assessment of scaling challenges and critical parameters for III-V

Quantum Well equivalent to Thin body SOI

3D devices

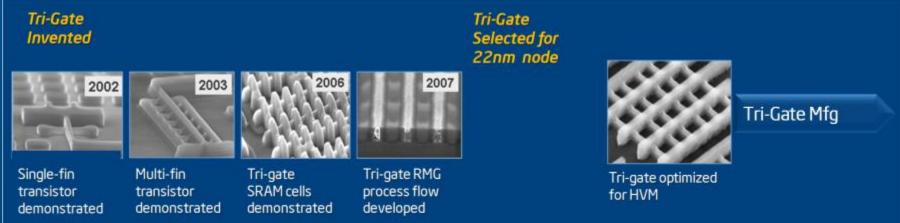

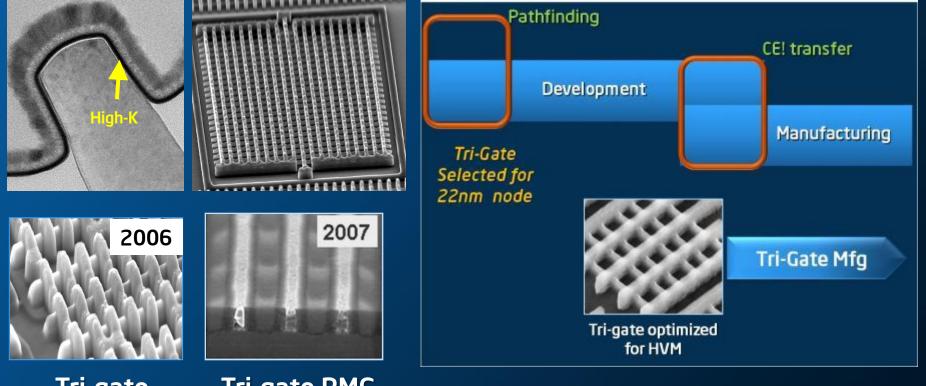

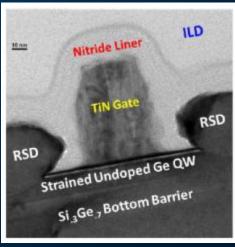

#### Integration – mid 00's

- Move to bulk silicon (cost)

- Catch up to planar for high k/metal gate + strain

- Create working CMOS

#### Then enabled

- Quality decision to adopt

- Development roadmap

- Lots more work !!!!

Tri-gate SRAM cells demonstrated

Tri-gate RMG process flow developed

#### Integration – mid 00's

- Move to bulk silicon (cost)

- Catch up to planar for high k/metal gate + strain

- Create working CMOS

Tri-gate SRAM cells demonstrated Tri-gate RMG process flow developed

#### Integration Today

- III-V grown on bulk silicon

- High k integration done

- Strain engineering not needed

- 3D devices partially done

- N and P on same wafer NOT DONE

4º(100) Offcut Si substrate

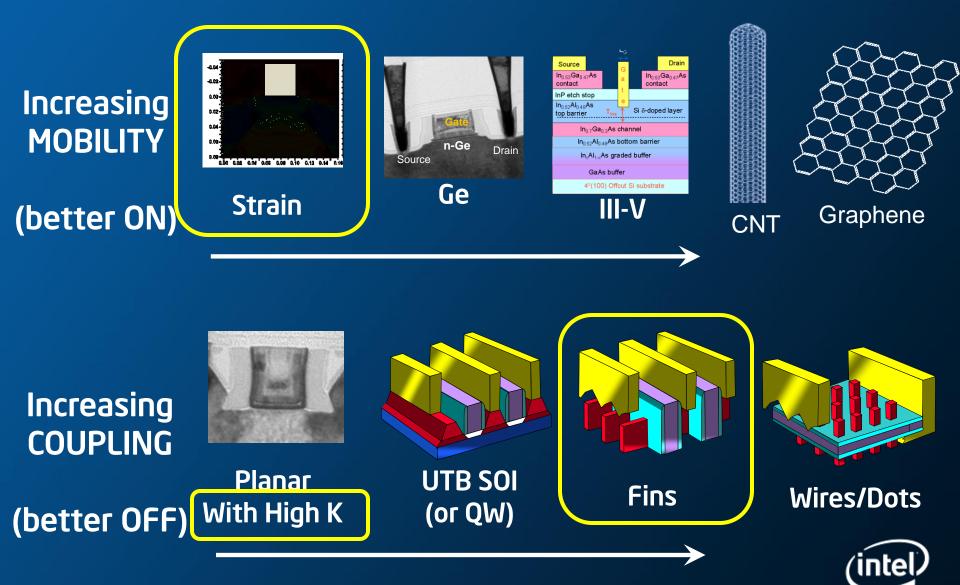

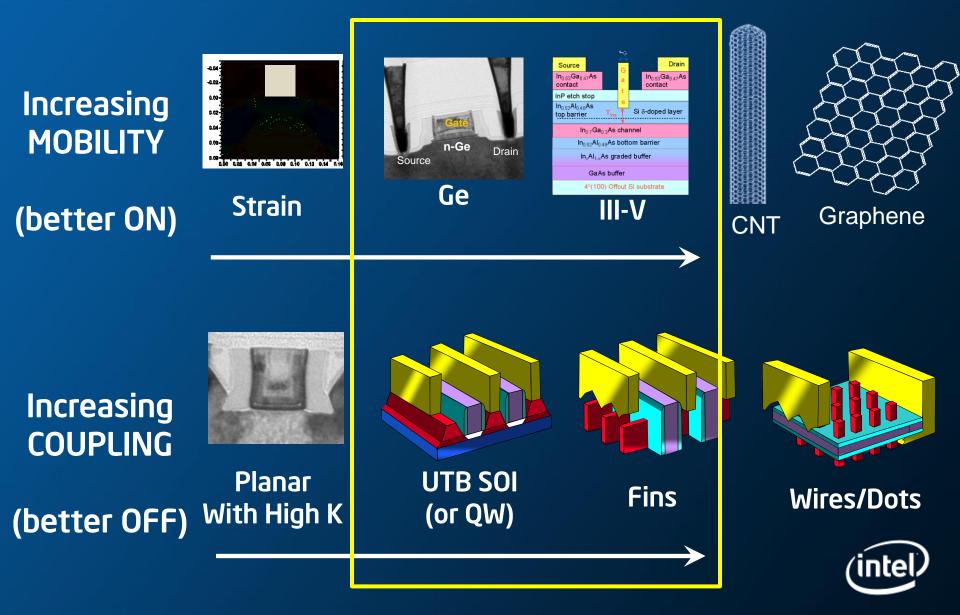

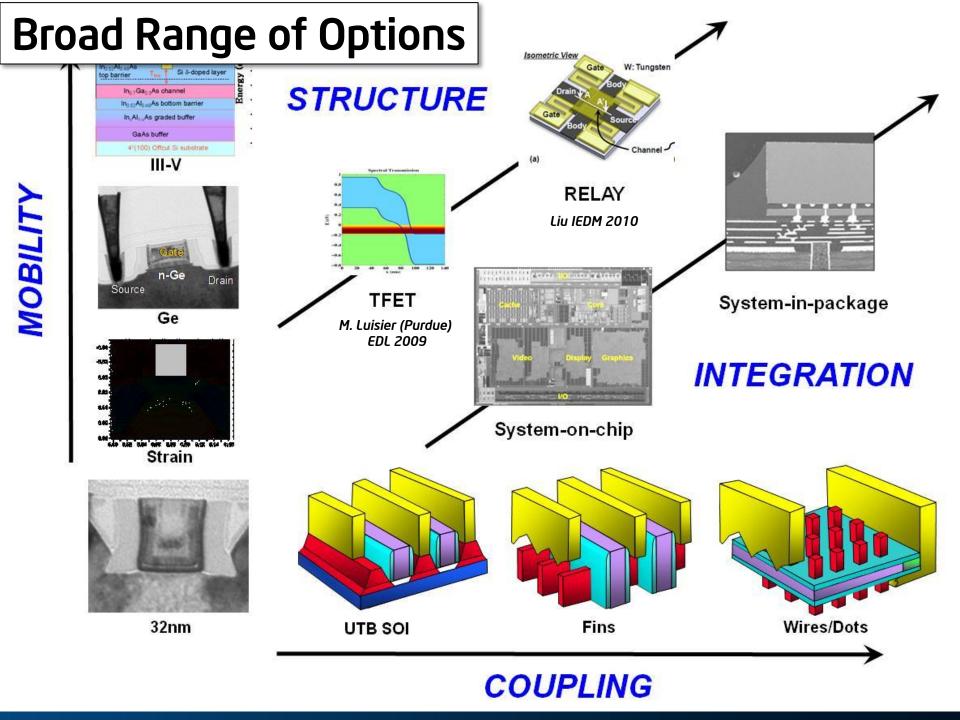

# **Optimizing Choices for Transistors on Multiple Fronts**

NOW

# **Optimizing Choices for Transistors on Multiple Fronts**

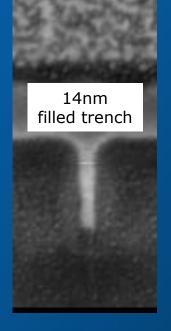

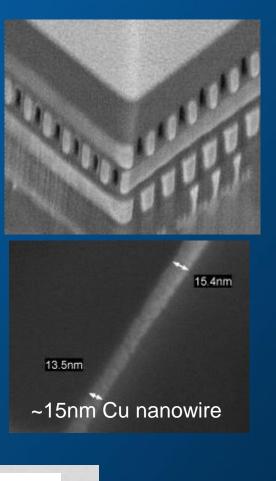

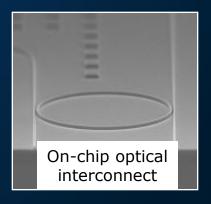

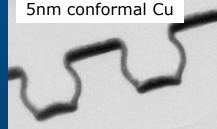

## **Interconnects Need to Scale**

**Needed Focus**

- Thin conformal plateable barrier ... or self forming barrier

- Tall vias might use non-Cu

- Non-SiO2 dielectrics

- Exotic long interconnects: CNT (10's um), optical (>mm)

- 3D stacking

<u>)</u>

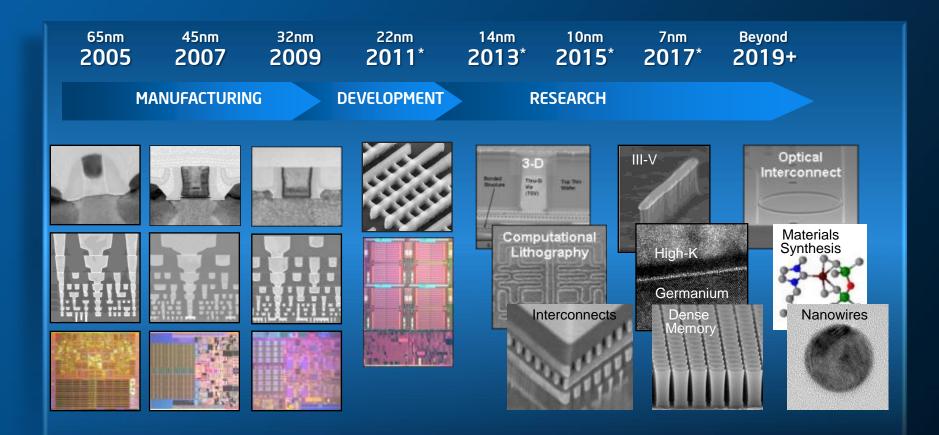

# We Expect Technology Innovation to Continue

\*projected

# Conclusions

Moore's Law is not a law of nature, it is an expectation of continued innovation

We expect to continue through focused research, rapid development, investment in production

Scaling research is increasingly about materials research, solving problems brings opportunities

New product opportunities will arise from continued advances in integration, connectivity

# Discussion