## Innovating and Integrating for Communications and Storage

Stephen Price

Director of Marketing

Performance Platform Division

Embedded and Communications Group

September 2009

# WHAT IS THE NEWS? New details on Jasper Forest for Embedded, Communications and Storage

Innovate

Integrate

Robust Performance Lower System Power

27 WATT SAVINGS\*

Integration for Savings

Workload Consolidation

4 TO 1

Coming in early 2010

<sup>\*</sup> Configurations of the systems used in the benchmark: two Jasper Forest processors, 2.13GHz GHz, 60W TDP, with Intel® 3420 chipset versus two Intel Xeon processors L5528, 2.13 GHz, 60 W TDP, with Intel® 5520 chipset

## Lower Power, Higher Integration and Reduced Foot Print

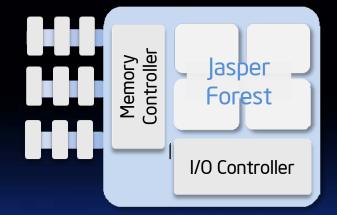

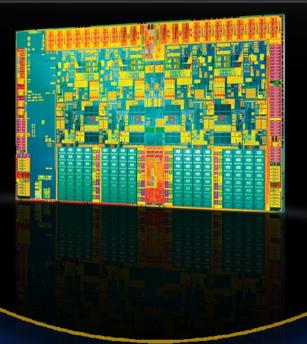

#### Jasper Forest

#### **Feature Overview**

#### Innovate and Integrate

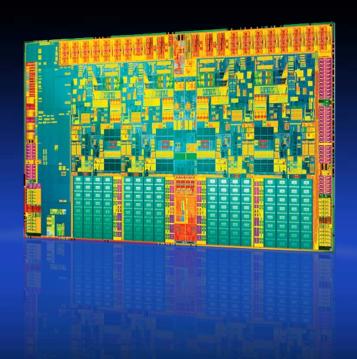

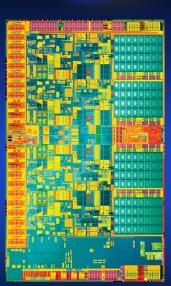

- Based on Intel® Xeon® Microarchitecture, formally code named Nehalem

- Integrated PCIe\* Gen 2.0 I/O in processor

- Less power consumption

- Crystal Beach Direct Memory Access (DMA)

- Non-Transparent PCI-E\* Bridging (NTB)

- Hardware RAID acceleration

- High TCase for NEBs and other thermal certifications

- 7 Year Lifecycle, 10 Year Reliability

### Integration

Intel® Xeon® 5500 Processor **Jasper Forest** Intel® Memory Controller Intel® Xeon Memory Controller asper lasper Xeon<sup>°</sup> 5500 5500 **Forest** Prodessor Forest Processor I/O NTB RAID NTB RAID Intel® ICH10R 5520 Intel® 3420 Chipset Chipset Provides a 27 watt system

power savings

## **Scalability**

Same Architecture

1 - 4 Cores 23W - 85W

One Common Socket

23 to 30 watts

### **Summary**

Jasper Forest Delivers Lower Power with Higher Integration

- Robust performance with a 27 watt system power savings

- I/O Hub Integration for real estate and power savings

- Workload consolidation

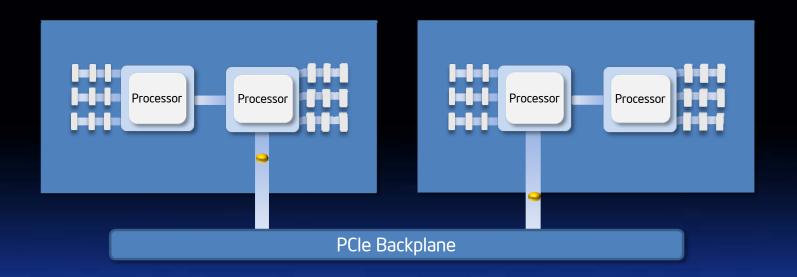

## Non-Transparent Bridge (NTB) Benefits

- Enables failover for redundant systems (as shown above)

- Can connect two uni-processor systems and function as dualprocessor

- Ability to connect to a non-IA system without a PCle switch

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

Intel architecture, Intel Xeon, Intel, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2009, Intel Corporation.