## Enabling IA SoCs with Intel's Technology and Manufacturing Innovation

Sunit Rikhi Vice President, Technology & Manufacturing Group

#### Shared SoC Design & Manufacturing Technology Layers

SoC DESIGN TECHNOLOGY LAYER

**PROCESS TECHNOLOGY & MANUFACTURING LAYER**

#### Shared Process & Manufacturing Technology Layer

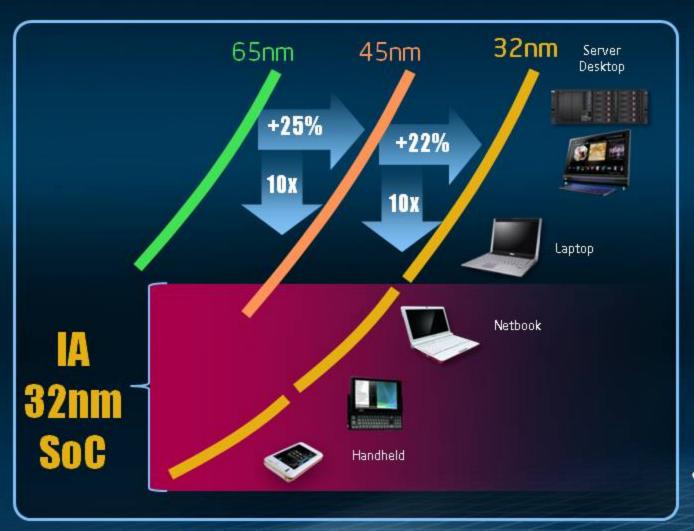

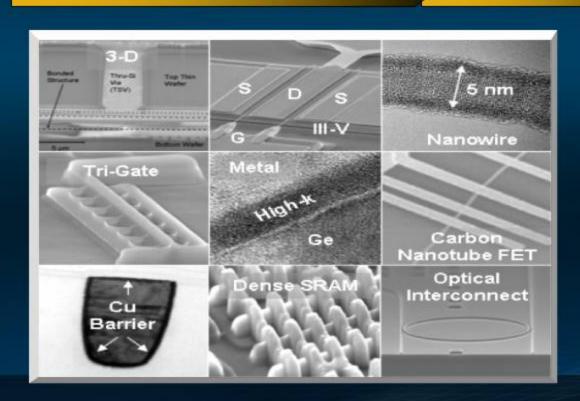

#### Silicon Process Technology Advantage

Faster Transistors and Improved Power at 32nm

LEAKAGE REDUCTION

3 ORDERS OF MAGNITUDE

INTEL 32nm SoC TECHNOLOGY EXTENDS THE REACH OF IA

TRANSISTOR PERFORMANCE

#### The Enabler

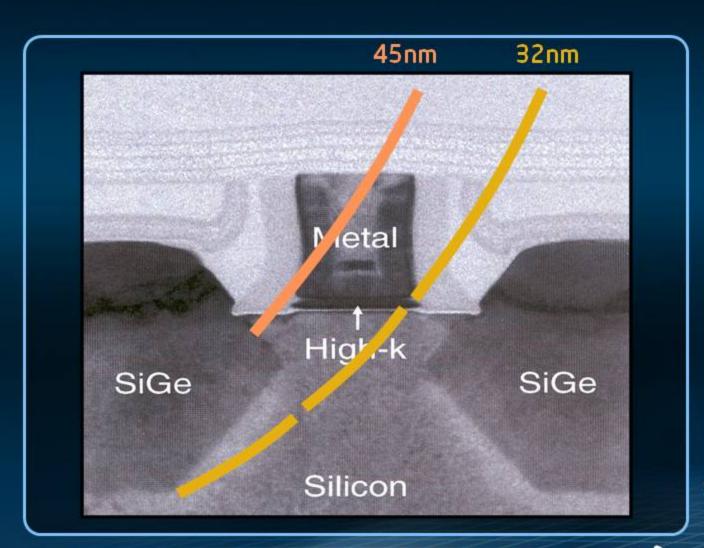

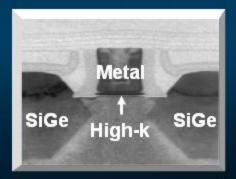

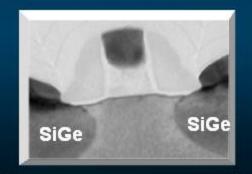

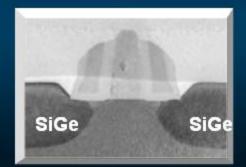

#### Intel's Hi-K/Metal Gate Transistor Technology

LEAKAGE REDUCTION

3 ORDERS OF MAGNITUDE

45nm: IN PRODUCTION SINCE 2H'07

32nm: ON TRACK FOR 2nd GEN RAMP IN 2H'09. HIGHEST DRIVE CURRENT AND SMALLEST GATE PITCH OF ANY REPORTED 32nm/28nm TECHNOLOGY

TRANSISTOR PERFORMANCE

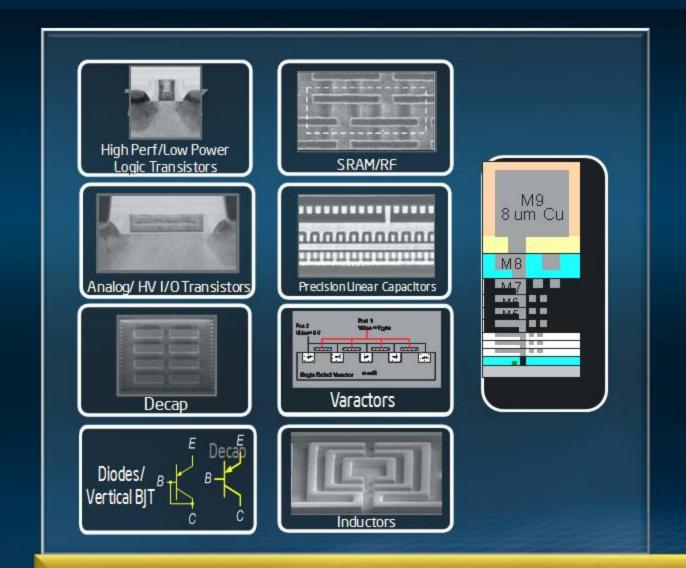

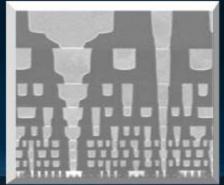

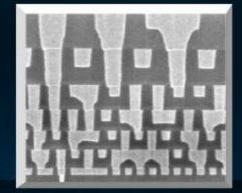

#### **32nm SOC Full-Featured Process Menu**

| LOGIC<br>TRANSISTOR | HIGH PERF          | - Y      |  |  |  |

|---------------------|--------------------|----------|--|--|--|

|                     | STD PERF-PWR       | 4        |  |  |  |

|                     | LOW PWR            | ✓.       |  |  |  |

|                     | HIGH PERF/LOW PWR  | ×        |  |  |  |

| I/O<br>TRANSISTOR   | 18V                | 4        |  |  |  |

|                     | 2.5V               | ×        |  |  |  |

|                     | 3.3V               | ~        |  |  |  |

| METALS              | HIGH PERF (CPU)    | 1        |  |  |  |

|                     | HIGH DENSITY       | 4        |  |  |  |

|                     | LOW COST           | ~        |  |  |  |

|                     | ULTRA HIGH DENSITY | <b>V</b> |  |  |  |

| EMBEDDED<br>MEMORY  | e-SRAM             | 1        |  |  |  |

|                     | E-OTP/FUSE         | ~        |  |  |  |

| BASIC               | MOM, MOS CAP       | ~        |  |  |  |

| ANALOG              | INDUCTOR (L)       | ✓.       |  |  |  |

| ADV MIXED           | PRECISION R        | 4        |  |  |  |

| SIGNAL/RF           | PRECISION C        | 4        |  |  |  |

|                     | HIGH Q L           | ~        |  |  |  |

|                     | DEEPNW             | <b>V</b> |  |  |  |

|                     | HIGH RESISUB       | 1        |  |  |  |

VARIETY OF OPTIONS TO ENABLE OPTIMIZED SILICON INTEGRATION OF DIVERSE SYSTEM COMPONENTS

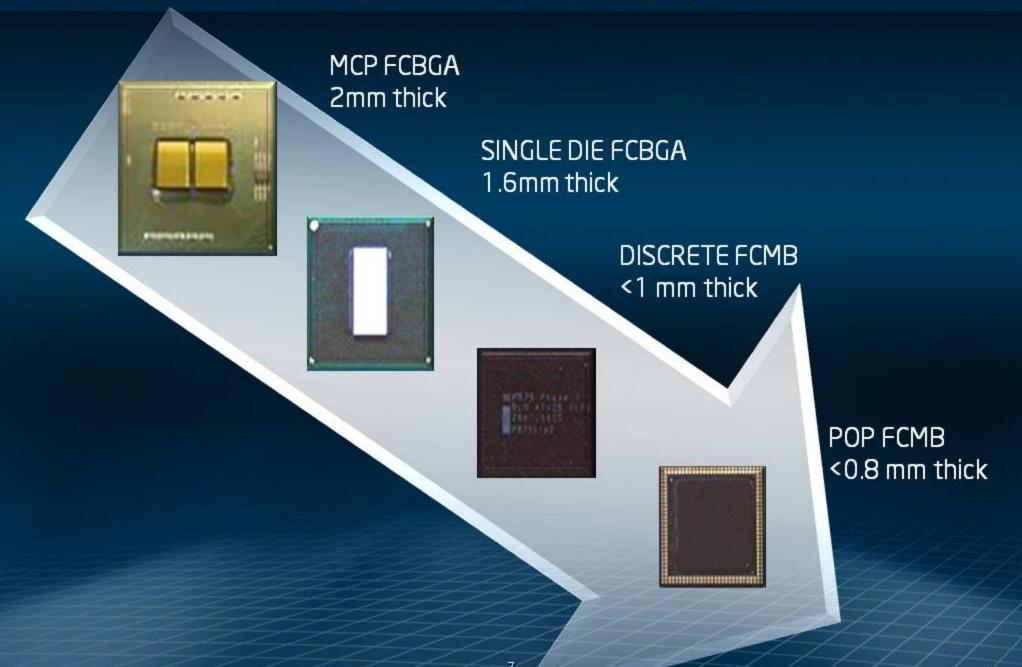

#### Intel 32nm Package Options

Enabling SOC Optimization in Integration, Form Factor and Cost

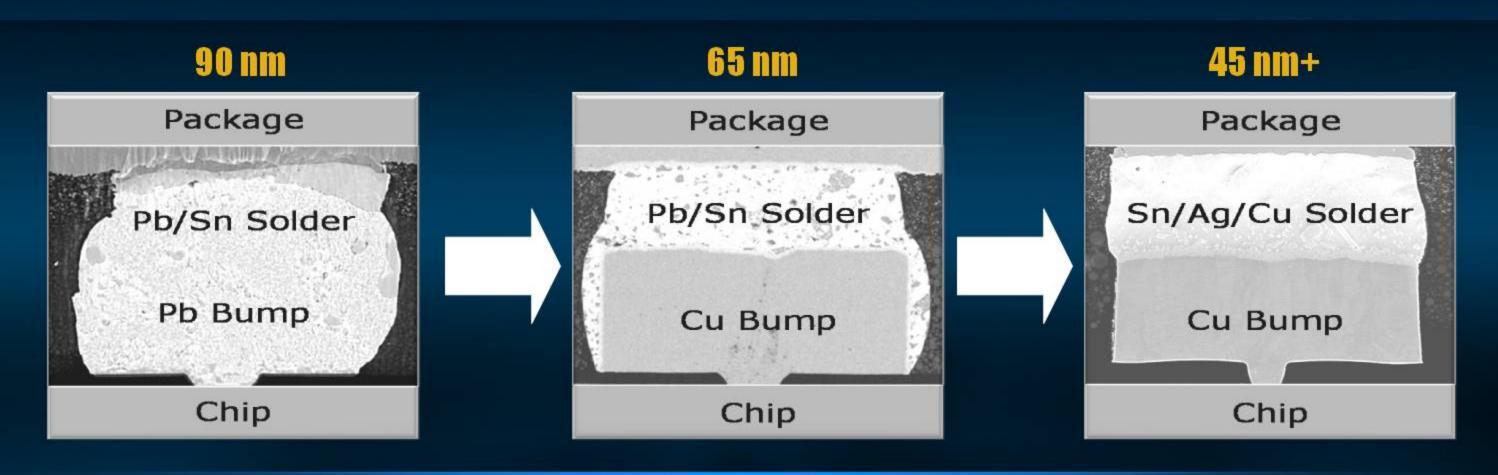

#### Intel's Lead Free Package Technology

ALL OPTIONS ARE LEAD FREE FOR TECHNOLOGY NODES 45nm AND BELOW

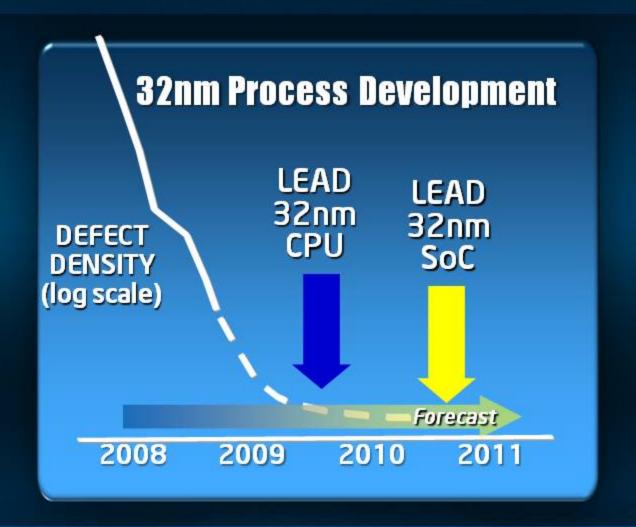

#### **Common Process Platform**

Low Power SoC Process...

INTEL's 32nm SOC PROCESS DEVELOPMENT SHARES INVESTMENT AND LEARNING ON A COMMON PLATFORM WITH CPU PROCESS

## 32nm Silicon Shuttles

| SHUTTLE:      | 1                     | 2                                    | 3                     | 4                                    | 5                                |

|---------------|-----------------------|--------------------------------------|-----------------------|--------------------------------------|----------------------------------|

| SILICON DATE: | Q307                  | Q208                                 | Q308                  | Q109                                 | Q309                             |

| TECH FOCUS:   | CPU TD                | CPU Tech Cert                        | SOC TD                | SOC Tech Cert                        | SOC Feature Refinements          |

| PROD FOCUS:   | Lead CPU<br>Memory IP | Lead CPU Memory +<br>Mixed-Signal IP | Lead SOC<br>Memory IP | Lead SOC Memory +<br>Mixed-Signal IP | Multi-Product<br>Mixed Signal IP |

UNFOLDING THE MAGIC OF 2nd GEN 32nm TECHNOLOGY

#### Extending Decades of IDM Co-optimization to SOCs

Co-optimized decisions from definition to ramp

Synchronized execution

Rapid yield learning & ramp

#### **32nm Manufacturing Investment**

D1D, Oregon (now)

F32, Arizona (2010)\*

D1C, Oregon (Q409)\*

F11x, New Mexico

Intel News Release

Intel to Invest \$7 Billion in U.S. Manufacturing Facilities

2-Year Plan to Focus on Leading-Edge Technologies

WASHINGTON, DC, Feb. 10, 2009 - Intel President and

#### A full, flowing, innovation pipeline

<22nm 2013+ 22nm 2011 32nm 2009 45nm 2007 65nm 2005 90nm 2003

RESEARCH

DEVELOPMENT

MANUFACTURING

AND AS FAR AS WE CAN SEE... THE MAGIC CONTINUES

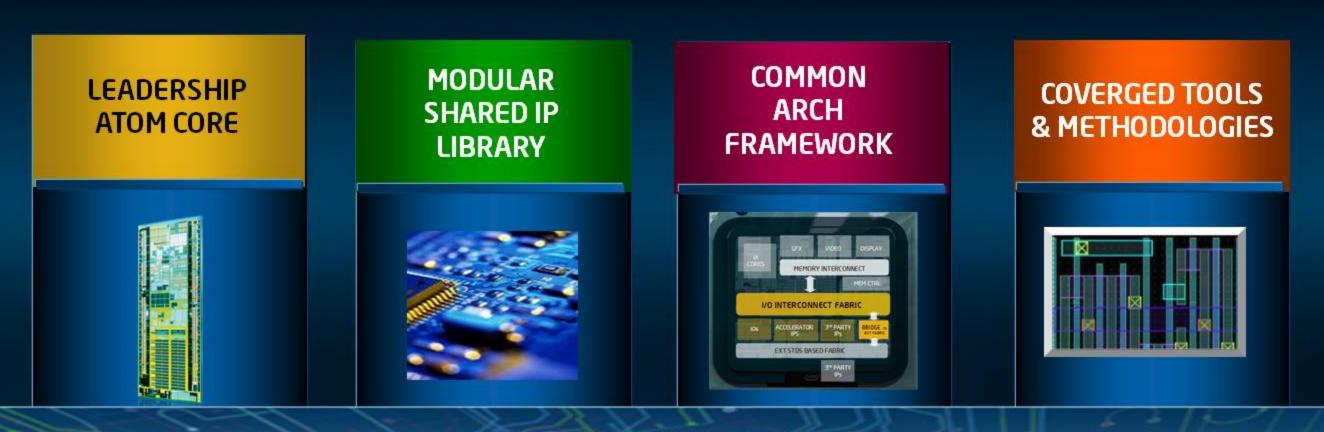

### **Shared SoC Technology Layer**

PROCESS TECHNOLOGY & MANUFACTURING LAYER

#### **shared Soc Technology Layer**

Soc Design Technology Layer

BENEFITS: TTM; MODULARITY/FLEXIBILITY/CUSTOMIZATION; COST/POWER/PERF/SIZE

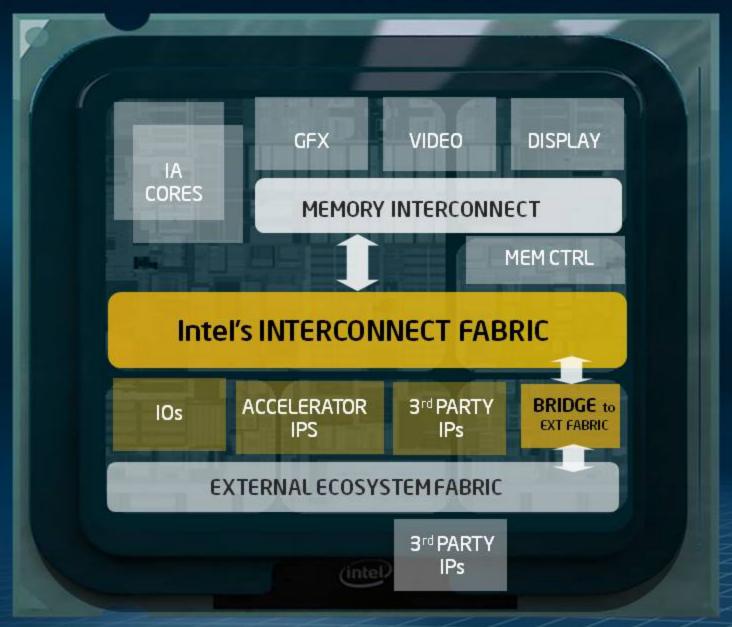

#### IA-based Common Architecture Framework

IA SOFTWARE COMPATIBILITY

MODULAR INTEGRATION

BRIDGE TO EXTERNAL ECOSYSTEM FABRIC

## **Intel Soc Products**

## Intel Smart Soc Products

EMBEDDED

#### EP80579

FULL FEATURE SoC **ACCELERATORS** QUICK ASSIST TECH

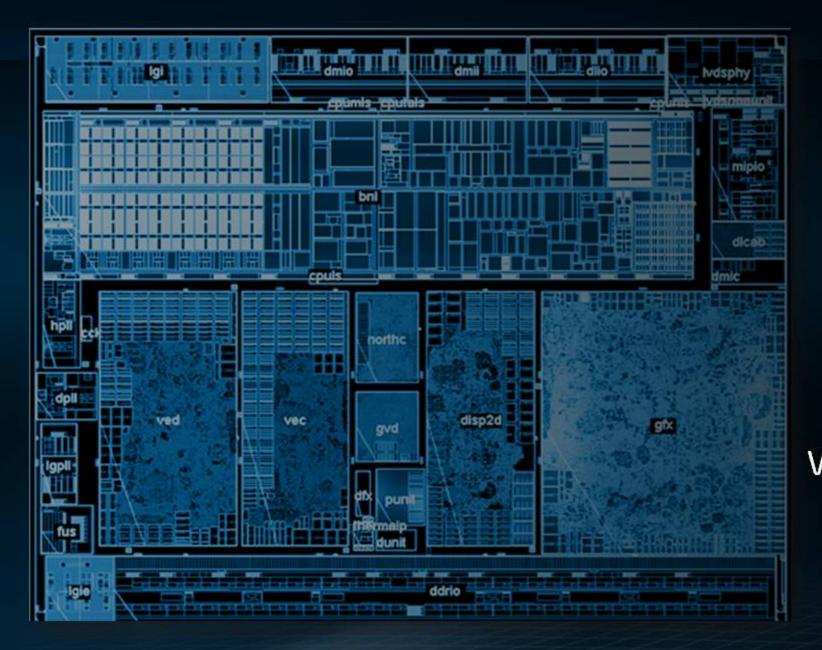

#### LINCROFT

45nm; ATOM CORE CPU/GFX/MEM/DISPLAY ADV. PWR MGMT

#### **CE 3100**

15 UNIQUE IP PIECES AUDIO-VIDEO DECODE **GRAPHICS** DISPLAYPROCESSING

#### SODAVILLE

45nm; ATOM CORE SEGMENT OPTIMIZED

#### **FOURTEEN** + 32nm SoCs **IN PROGRESS\***

#### **Legal Notices**

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting Intel's Web Site.

This document contains information on products in the design phase of development.

45nm product is manufactured on a lead-free process. Lead is below 1000 PPM per EU RoHS directive (2002/95/EC, Annex A). Some EU RoHS exemptions for lead may apply to other components used in the product package.

Any code names featured are used internally within Intel to identify products that are in development and not yet publicly announced for release. Customers, licensees and other third parties are not authorized by Intel to use code names in advertising, promotion or marketing of any product or services and any such use of Intel's internal code names is at the sole risk of the user.

All products, computer systems, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice.

Intel and the Intel logo are trademarks of Intel Corporation in the United States and other countries.

\*Other names and brands may be claimed as the property of others

Copyright © 2009, Intel Corporation. All rights reserved.

# Thank you QEA

## Intel Mid-Summer Technology Summit

July 29, 2009