## 2009 International Solid-State Circuits Conference Intel Paper Highlights

Mark Bohr Intel Senior Fellow

Soumyanath Krishnamurthy Intel Fellow

1

## 2009 ISSCC Intel Paper Summary Under embargo until February, 4, 9 p.m. PST 2009

- The New Era of Scaling for SoC: Fundamental shifts required in both transistor development and circuit design to continue innovation in microprocessors and SoC products

- **Microprocessor:** Intel will lead half of the microprocessor session with four papers discussing future industry leading 45nm enterprise processors

- Wireless Technology: Three research papers on new wireless developments which will enable more capabilities in the future SOC

- **Graphics for Mobile Technology**: A new technique for small mobile devices like laptops, MIDs and nettops for rich multi-media, bringing additional graphics capabilities onto the processor using SIMD

- 15 total papers presented

## Industry-Leading Enterprise Processors

#### Unquestioned enterprise performance leadership

#### Paper 3.1: A 45nm 8-Core Enterprise Intel<sup>®</sup> Xeon<sup>®</sup> Processor

- Codename: Nehalem-EX

- 8-core 16-thread enterprise Xeon<sup>®</sup> processor

- 2.3B transistors

#### Paper 3.2: A Family of 45nm IA Processors

- Codename: Nehalem

- Enhanced Intel<sup>®</sup> Core<sup>TM</sup> microarchitecture

- Mobile, desktop and server applications

#### Paper 3.4: Dynamic Frequency-Switching Clock System on a Quad-Core Itanium<sup>®</sup> Processor

- Codename: Tukwila, 2B+ transistors

- Clock design allows frequency-power optimization without stopping the clock

#### Paper 3.8: Over One Million TPCC with a 45nm 6-Core Xeon<sup>®</sup> CPU

- Codename: Dunnington

- 1.9B transistors, 16MB L3 cache

- 1M transactions/minute TPCC in 8-socket configuration

Nehalem-EX

Nehalem

Tukwila

Dunnington

Chip photos not to scale

Copyright © Intel Corporation, 2009. All rights reserved. Third-party marks and brands are the property of their respective owners. All products, dates, and figures are preliminary and subject to change without notice.

## Mark Bohr, Intel Senior Fellow ISSCC Plenary Talk, Feb 9th THE NEW ERA OF SCALING IN AN SOC WORLD

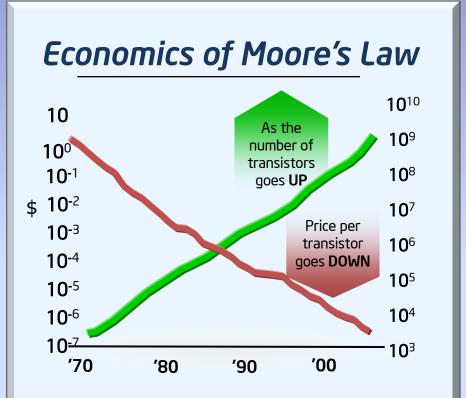

## Moore's Law Enabling ... More

Continue the pace of dimension reduction and feature improvement

- Supporting unprecedented complexity

- 45nm -> 32nm -> 22nm

- 100s of millions of transistor SoCs

(intel)

## Intel Advantage

High performance computing leadership Process technology & high volume manufacturing High HW & SW complexity handling expertise

#### **Extensive R&D investment**

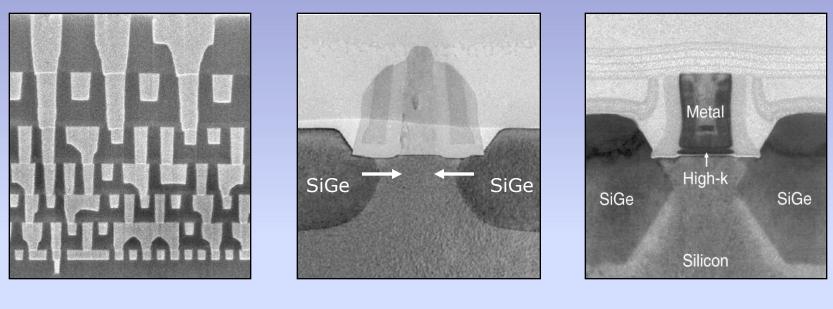

## The New Era of Device Scaling

Copper + Low-k

Strained Silicon

High-k + Metal Gate

Modern CMOS scaling is as much about material and structure innovation as dimensional scaling

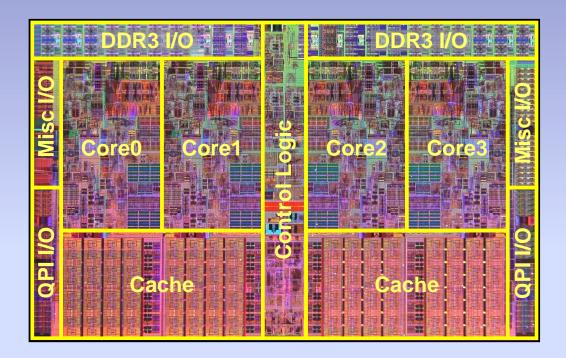

## 45 nm Nehalem CPU

Modern microprocessors are a complex system on a chip with multiple functional units and multiple interfaces

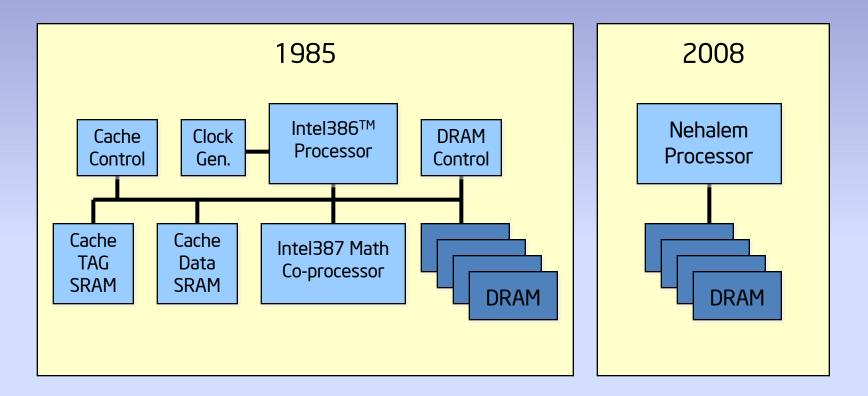

## PC Platform Comparison

Modern microprocessors integrate many of the separate system components from past platforms

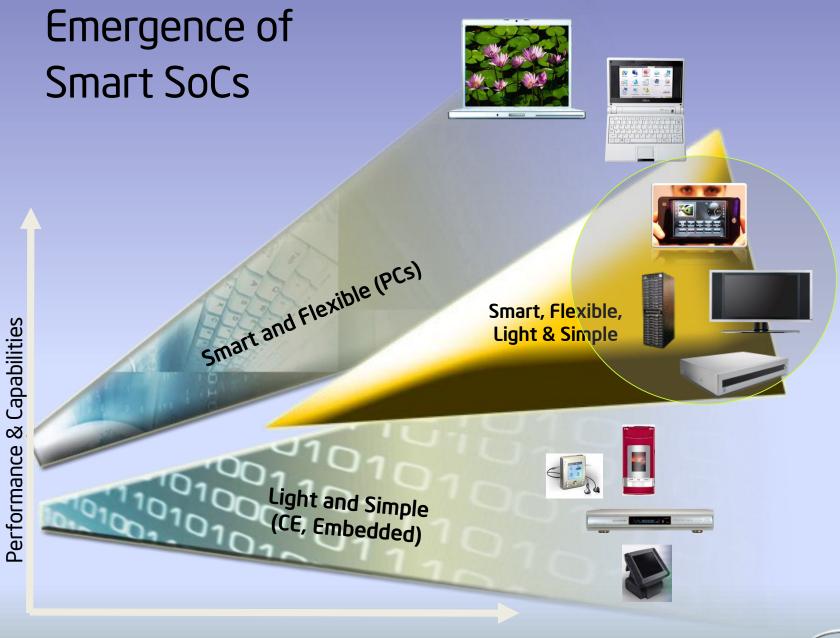

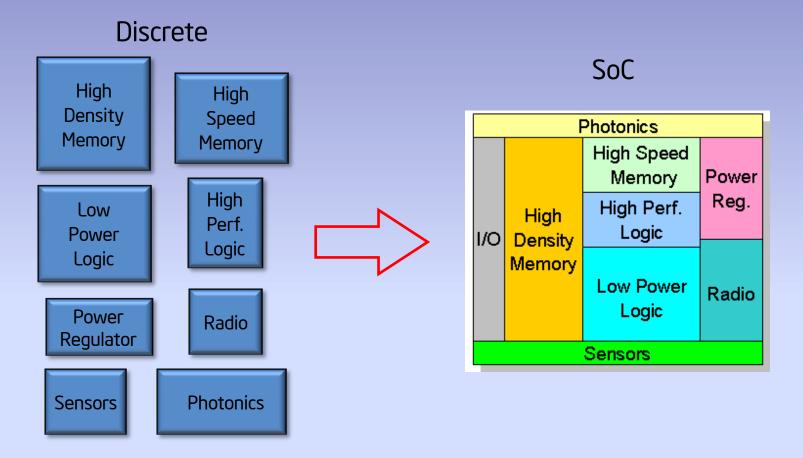

## System Integration

System integration will continue, using key elements such as the Atom<sup>™</sup> core, to realize improved performance and power in a smaller form factor

Krishnamurthy Soumyanath (Soumya) Intel Fellow, Corporate Technology Group

Director, Communications Circuits Research

## **FUTURE SOC TECHNOLOGIES:** DIGITAL MULTI-RADIO, GRAPHICS FOR MOBILE & SENSORS

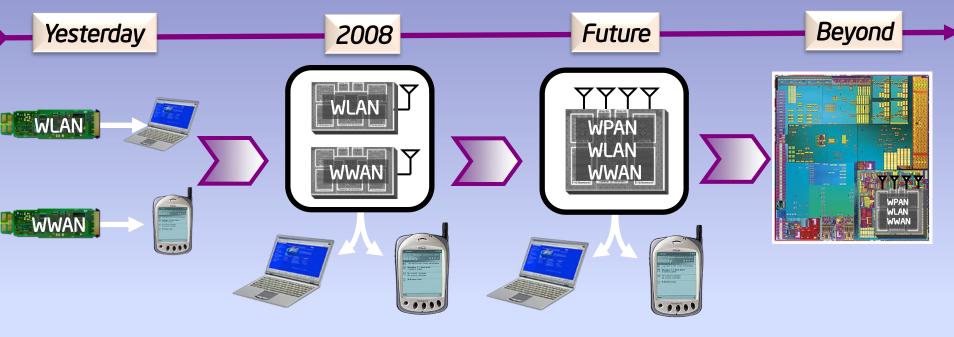

## The Wireless "Radio" Evolution

#### **Discrete Radios**

One standard Bulky, costly Inflexible

#### **Integrated Radios**

Full CMOS Integration Dual-standard +Performance, -Cost, -TTM

#### <u>Digital Multi-Radios</u>

Reconfigurable CMOS Radios Multi-standard Tunable antenna **SOC** Full DMR on SOC New Embedded Apps --Cost, --TTM, ++Perf.

#### Vision: Connectivity Anytime, Anywhere for Everyone

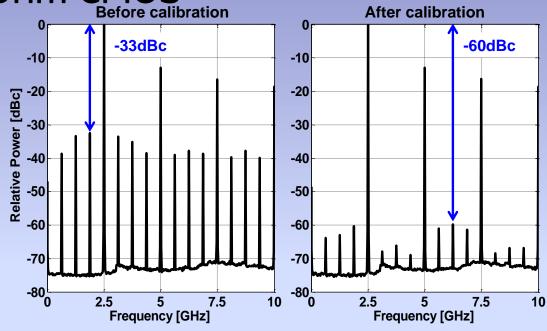

### Digital Techniques for radio data transfer in 45nm CMOS

- Pulling-free LO generation by means of fractional division

- Reduced amount of components required, saving silicon area, power and cost

- Takes advantage of inherent statistical variations in the 45nm CMOS process to measure and calibrate mismatches

14

WiFi/WiMax 2.5/3.5GHz LO generation with digital calibration with no filtering

Session 12.6: "A 4.75GHz fractional frequency divider with digital spur calibration in 45nm CMOS"

Sync-n-Go

Wireless Display

Wireless Computing

# Gigabit wireless enables better user experience and new applications

Airpor Movies

# Low power, high data for 60Ghz communication

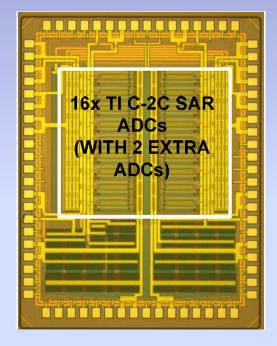

Convert analog signals to digital by using multiple SAR ADCs and spreading task across all of them.

Data rates in excess of 3Gb/s to allow a DVD quality movie to transfer wirelessly in less than 15 seconds

First ADC that can resolve 7 bits at 2.5Gb/s in pure CMOS, Key step toward digital radios with high performance and low power

Power comparable to the state of the art ADCs available today, but with better accuracy

#### First 7 bit 2.5GS/s ADC in 45nm CMOS process.

Session 4.2: "A 1.1V 50mW 2.5GS/s 7b Time-Interleaved C-2C SAR ADC in 45nm LP Digital CMOS" (joint work with Carnegie Mellon University)

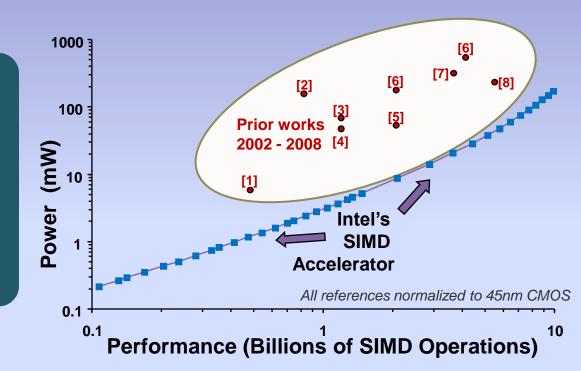

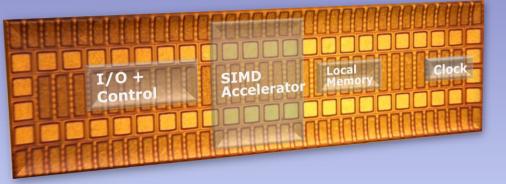

## SIMD Accelerator

"A 300mV 494GOPS/W Reconfigurable Dual Supply 4-Way SIMD Vector Processing Accelerator in 45nm CMOS"

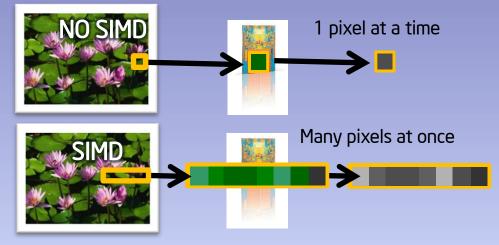

Great multimedia experiences require high-performance **SIMD** processing in the CPU or GPU *SIMD* = <u>Single Instruction Multiple Data</u> SIMD Example: Make an image black & white

## A Low-power, Scalable SIMD Accelerator

SIMD Accelerator Prototype

#### SIMD Challenges

• High leakage currents and — poor power management

18

#### **Our Solutions**

- Fine-grain power gating and active power management

- Do not scale down to ultra low voltages ------ New ultra low voltage circuit techniques

Operation from 1.3V down to ultra-low **0.23V**. Energy-efficiency up to **10X better** at normal voltages and up to **80x better** at ultra-low voltages

#### Potential: Much better graphics on small devices

14.6 A 300mV 494GOPS/W Reconfigurable Dual-Supply 4-Way SIMD Vector Processing Accelerator in 45nm CMOS

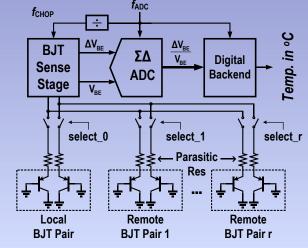

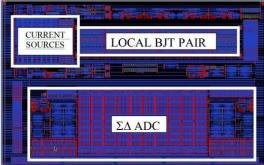

# First 32nm thermal sensor for multi-core microprocessor applications

#### Achievement:

Numerous remote sensors used to accurately measure temperature over the entire multi-core die in 32nm CMOS

#### **Results:**

- Improves processor power management

- Ability to maximize microprocessor performance, reliably.

- Limit leakage through load-balancing with multiple location hot spot temperature measurements

- Extend life of processor components by maintaining lower operational stress

- Multiple sensors allow more precise identification and intervention

## CPU Thermal/power management is crucial to platform performance and energy efficiency

Session 20.1: "A 1.05V 1.6mW, 0.45°C  $3\sigma$  Resolution  $\Sigma\Delta$  based Temperature Sensor with Parasitic Resistance Compensation in 32nm Digital CMOS Process"

## Thank You

- Attend Mark Bohr's plenary session:

- Feb 9<sup>th</sup>: 10:30am

- Press Q&A: 1:30pm

#### Contact Intel for more info:

- <u>www.intel.com/pressroom</u>

- Megan Langer: <u>megan.e.langer@intel.com</u>, 503-333-1121

## BACKUP

# List of Papers (15)

Microprocessor:

A 45nm 8-Core Enterprise Xeon® Processor

A Family of 45nm IA Processors

Dynamic Frequency-Switching Clock System on A Quad-Core Itanium® Processor

Over One Million TPCC with a 45nm 6-Core Xeon® CPU

Wireless:

A 1.1V 50mW 2.5GS/s 7b Time-Interleaved C-2C SAR ADC in 45nm LP Digital CMOS

A 4.75GHz Fractional Frequency Divider with Digital Spur Calibration in 45nm CMOS

A 1MHz-Bandwidth Type-I  $\Delta\Sigma$  Fractional-N Synthesizer for WiMAX Applications

Mobile:

A Scalable 3.6-to-5.2mW 5-to-10Gb/s 4-Tap DFE in 32nm CMOS

A 1.1V 5-to-6GHz Reduced-Component Direct-Conversion Transmit Signal Path in 45nm CMOS

13.1 A 172mm2 32Gb MLC NAND Flash Memory in 34nm CMOS

Graphics on Mobile:

14.6 A 300mV 494GOPS/W Reconfigurable Dual-Supply 4-Way SIMD Vector Processing Accelerator in 45nm CMOS Process Technology:

22.3 A Single-Chip Highly Linear 2.4GHz 30dBm Power Amplifier in 90nm CMOS

27.1 A 4.0GHz 291Mb Voltage-Scalable SRAM in 32nm High-κ Metal-Gate CMOS with Integrated Power Management

Optical I/O Technology in Tera-Scale Computing

A 1.05V 1.6mW 0.45°C  $3\sigma$ -Resolution  $\Delta\Sigma$ -Based Temperature Sensor with Parasitic-Resistance Compensation in 32nm CMOS Forum:

RF Transceivers from 3.x Toward 4G/OFDM-Based Systems

## SIMD Accelerator Results

#### Prototype Results:

- 41% lower power overall

- 6.5x lower active leakage

- 10x lower standby leakage

- 494GOPS/W peak efficiency

- Operates from 0.23V-1.3V

- 161mW @ 2.3GHz, 1.1V