# Technology Research to Drive Innovation

### Mike Mayberry

Components Research VP, Technology and Manufacturing Group Intel Corporation

June, 2009

## Optimize Collaboration and Investing in R&D Pipeline

External Consortia Universities Investment Suppliers Nat'l Labs Internal

Components ResearchHow can we build it ?How can we integrate it ?

Intel LabsWhat should we build ?How will people use it ?

Identify Ideas/Options

RESEARCH

Select Features/ Make it Work for HVM High Volume Manufacturing

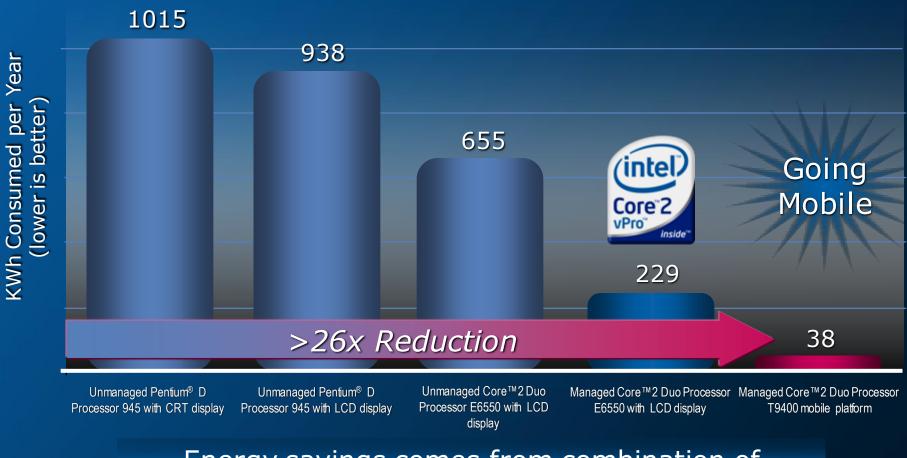

### Potential Energy Savings Enabled by Moore's Law

Estimated Annual Energy Consumption

# Energy savings comes from combination of transistor scaling and architectural innovations

Performance tests/ratings are provided assuming specific computer systems and/or components and reflect the approximate performance of Intel products as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance. This data may vary from other material generated for specific marketing requests.

3

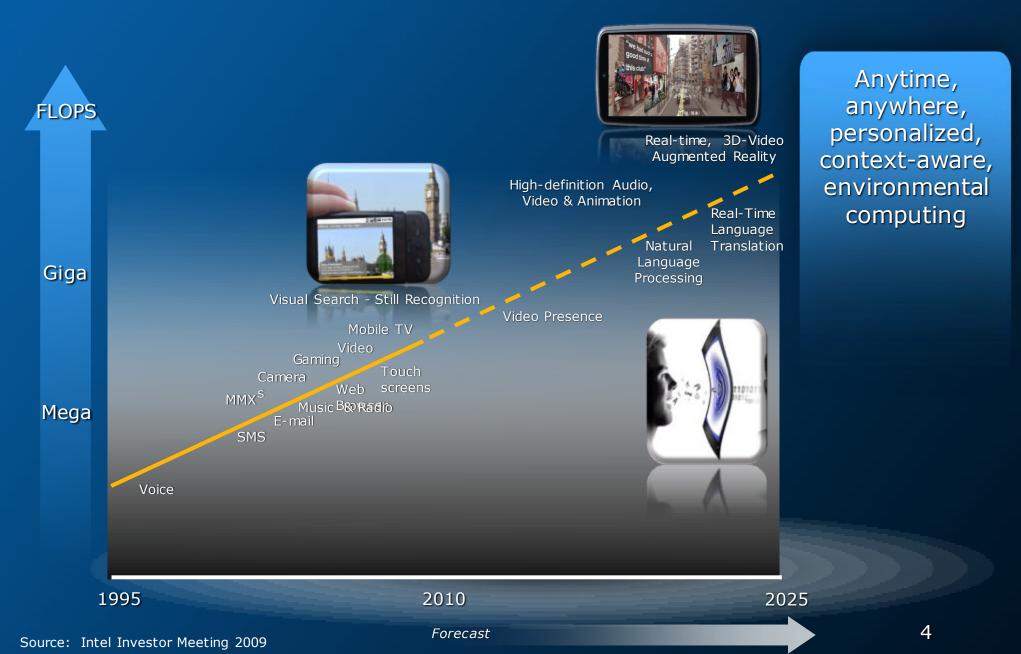

### Small Computing Segment Needs More and More Performance At Low Power

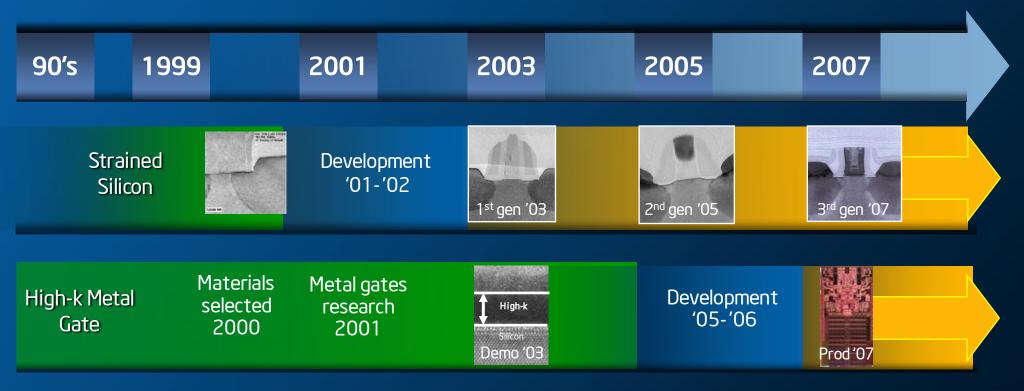

## The Timing of Research Is Not Always Predictable

## But a Commitment to Research is Required

Source: Intel

# Lithography Options for Beyond 32 nm

#### Pitch Doubling

#### 2-D Features

- Pitch doubling

- Improved 2-D features

#### **Pixilated Mask**

#### Printed Image

### Computational Lithography

- Pixilated mask

- Existing 193 nm litho tools

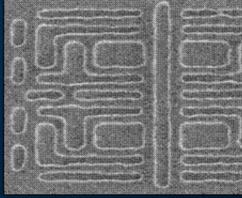

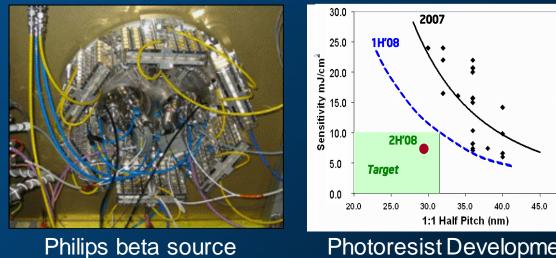

## Extreme Ultraviolet Lithography

Cymer beta source

Intel EUV Mask

ASMLADT printed wafer

50.0

Photoresist Development

### Continued progress towards EUV implementation

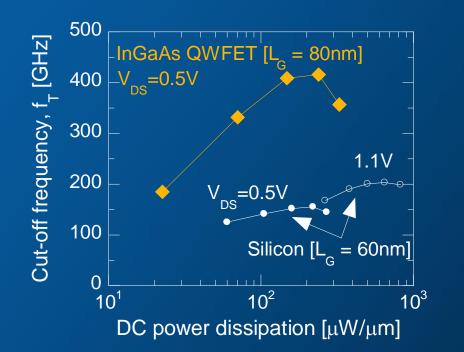

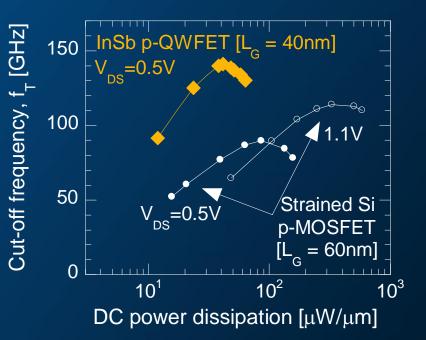

## **III-V Transistor Options**

### InGaAs NMOS QWFET Peak $f_T > 400$ GHz at Vcc = 0.5V

InSb PMOS QWFET Peak  $f_T > 140$  GHz at Vcc = -0.5V

III-V materials for improved performance at low voltage

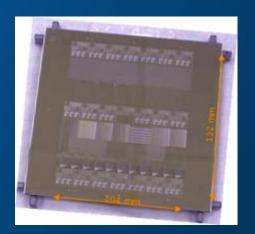

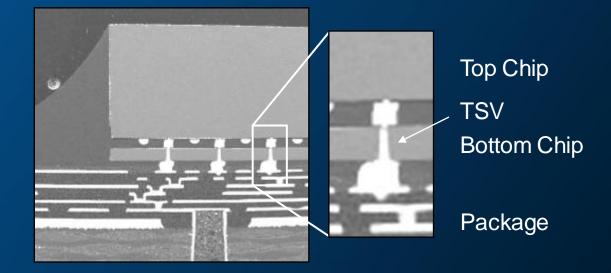

# **3-D Chip Stacking**

- + High density chip-chip connections

- + Small form factor

- + Combine dissimilar technologies

- ? Added cost

- ? Degraded power delivery, heat sinking

- ? Area impact on lower chip

### 3-D chip stacking using through-silicon vias

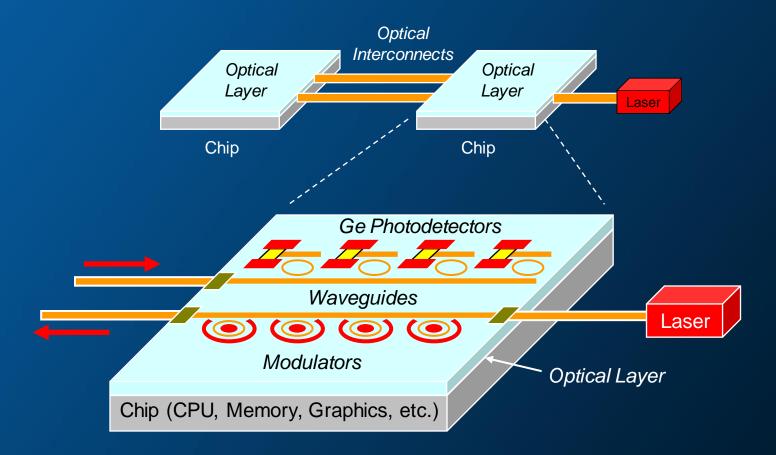

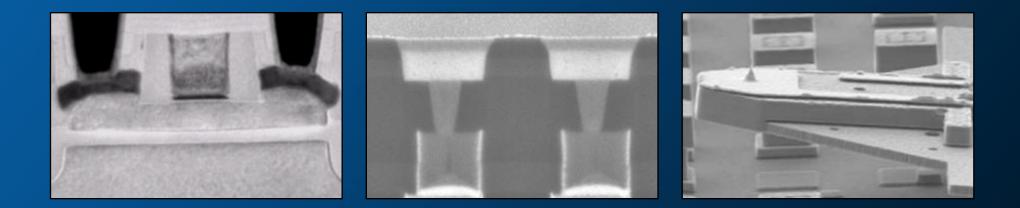

## **Optical Interconnects**

Nearer term: High bandwidth chip-chip interconnects Longer term: On-chip interconnects

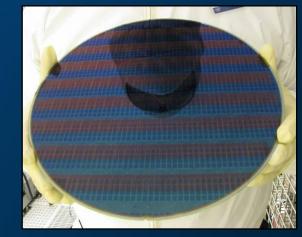

## High Density Memory

Floating Body Cell

Phase Change Memory

Seek and Scan Probe

Dense memory increasingly important Several novel directions being explored

# Discussion