# Intel® Server System SC5650HCBRP

## Technical Product Specification

Intel order number E81443-002

**Revision 1.2**

**April, 2010**

**Enterprise Platforms and Services Division**

## Revision History

| Date           | Revision<br>Number | Modifications                                                                                                                  |

|----------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------|

| September 2009 | 1.0                | Initial Release                                                                                                                |

| March 2010     | 1.1                | <ul> <li>Updated Section 3.3</li> <li>Updated Section 2.1 and 3.2 to add Intel® Xeon® Processor 5600 series support</li> </ul> |

| April 2010     | 1.2                | - Removed CCC related notice                                                                                                   |

### Disclaimers

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® Server System SC5650HCBRP may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Refer to the *Intel® Server System SC5650HCBRP Specification Update* for published errata.

Intel Corporation server baseboards contain a number of high-density VLSI and power delivery components that need adequate airflow to cool. Intel's own chassis are designed and tested to meet the intended thermal requirements of these components when the fully integrated system is used together. It is the responsibility of the system integrator that chooses not to use Intel developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of air flow required for their specific application and environmental conditions. Intel Corporation can not be held responsible if components fail or the server board does not operate correctly when used outside any of their published operating or non-operating limits.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2009-2010.

## Table of Contents

| 1. | Introdu | iction                                                                | 1  |

|----|---------|-----------------------------------------------------------------------|----|

|    | 1.1     | Chapter Outline                                                       | 1  |

| •  | 1.2     | Server System Use Disclaimer                                          | 1  |

| 2. | Overvie | ew                                                                    | 3  |

| 2  | 2.1     | Intel® Server System SC5650HCBRP Feature Set                          | 3  |

|    | 2.1.1   | Intel® Server System SC5650HCBRP Layout                               | 5  |

|    | 2.1.2   | Mechanical Locks                                                      | 9  |

|    | 2.1.3   | System Color                                                          | 9  |

|    | 2.1.4   | Rack and Cabinet Mouting Option                                       | 9  |

|    | 2.1.5   | Server Board Connector and Component Layout                           | 9  |

|    | 2.1.6   | Server Board Mechanical Drawings                                      | 11 |

|    | 2.1.7   | Rear I/O Layout                                                       | 20 |

| 3. | Functio | onal Architecture                                                     | 21 |

| ;  | 3.1     | Intel® 5520 I/O Hub (IOH)                                             | 23 |

|    | 3.1.1   | Intel® QuickPath Interconnect                                         | 23 |

|    | 3.1.2   | PCI Express* Ports                                                    | 23 |

|    | 3.1.3   | Enterprise South Bridge Interface (ESI)                               | 24 |

|    | 3.1.4   | Manageability Engine (ME)                                             | 24 |

|    | 3.1.5   | Controller Link (CL)                                                  | 24 |

| ;  | 3.2     | Processor Support                                                     | 25 |

|    | 3.2.1   | Processor Population Rules                                            | 25 |

|    | 3.2.2   | Mixed Processor Configurations                                        | 25 |

|    | 3.2.3   | Intel <sup>®</sup> Hyper-Threading Technology (Intel <sup>®</sup> HT) | 27 |

|    | 3.2.4   | Enhanced Intel SpeedStep® Technology (EIST)                           | 27 |

|    | 3.2.5   | Intel® Turbo Boost Technology                                         | 27 |

|    | 3.2.6   | Execute Disable Bit Feature                                           | 27 |

|    | 3.2.7   | Core Multi-Processing                                                 | 28 |

|    | 3.2.8   | Direct Cache Access (DCA)                                             | 28 |

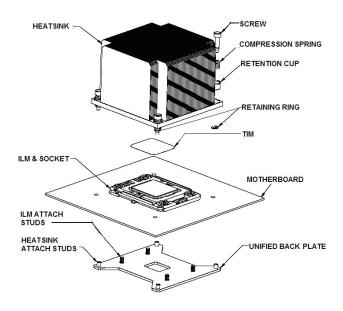

|    | 3.2.9   | Unified Retention System Support                                      | 28 |

| ;  | 3.3     | Memory Subsystem                                                      | 30 |

|    | 3.3.1   | Memory Subsystem Nomenclature                                         | 30 |

|    | 3.3.2   | Supported Memory                                                      | 31 |

| 3.3.3    | Processor Cores, QPI Links and DDR3 Channels Frequency Configuration | 32 |

|----------|----------------------------------------------------------------------|----|

| 3.3.4    | Publishing System Memory                                             | 35 |

| 3.3.5    | Memory Interleaving                                                  | 36 |

| 3.3.6    | Memory Test                                                          | 36 |

| 3.3.7    | Memory Scrub Engine                                                  | 36 |

| 3.3.8    | Memory RAS                                                           | 36 |

| 3.3.9    | Memory Population and Upgrade Rules                                  | 37 |

| 3.3.10   | Supported Memory Configuration                                       | 39 |

| 3.3.11   | Memory Error Handling                                                | 41 |

| 3.4      | ICH10R                                                               | 42 |

| 3.4.1    | Serial ATA Support                                                   | 42 |

| 3.4.2    | USB 2.0 Support                                                      | 44 |

| 3.5      | PCI Subsystem                                                        | 45 |

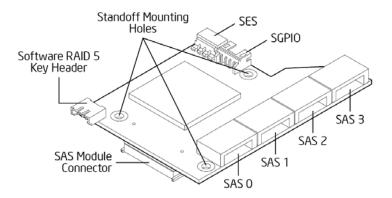

| 3.6      | Intel® SAS Entry RAID Module AXX4SASMOD (Optional Accessory)         | 46 |

| 3.6.1    | SAS RAID Support                                                     | 47 |

| 3.7      | Baseboard Management Controller                                      | 49 |

| 3.7.1    | BMC Embedded LAN Channel                                             | 50 |

| 3.8      | Serial Ports                                                         | 51 |

| 3.9      | Floppy Disk Controller                                               | 51 |

| 3.10     | Keyboard and Mouse Support                                           | 51 |

| 3.11     | Video Support                                                        | 51 |

| 3.11.1   | Video Modes                                                          | 52 |

| 3.11.2   | Dual Video                                                           | 52 |

| 3.12     | Network Interface Controller (NIC)                                   | 53 |

| 3.12.1   | MAC Address Definition                                               | 53 |

| 3.13     | ACPI Support                                                         | 54 |

| 3.14     | Intel® Virtualization Technology                                     | 54 |

| 3.14.1   | Intel® Virtualization Technology for Directed IO (VT-d)              | 54 |

| 3.15     | Intel® I/O Acceleration Technology                                   | 54 |

| 4. Power | Sub-system                                                           | 55 |

| 4.1      | 600-W 1+1 Power Supply Module                                        | 55 |

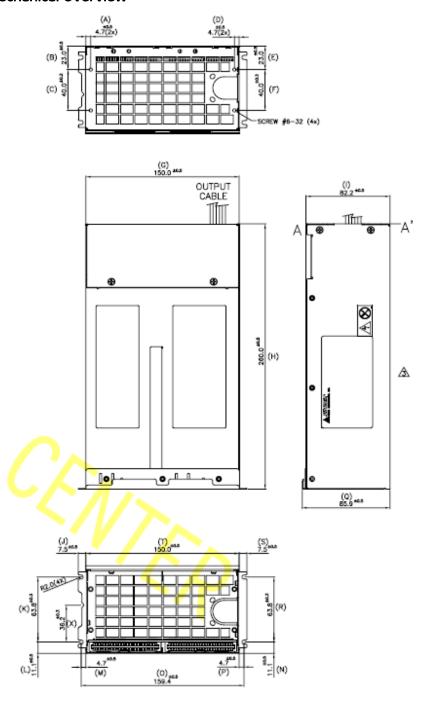

| 4.1.1    | Mechanical Overview                                                  | 55 |

| 4.1.2    | AC Input Requirements                                                | 57 |

| 4.1.3    | DC Output Specification                                              | 62 |

| 4.1.4    | Protection Circuits                                                  | 70 |

|    | 4.1.5    | Control and Indicator Functions                   | 71  |

|----|----------|---------------------------------------------------|-----|

|    | 4.1.6    | PMBus Monitoring Interface                        | 74  |

| 4  | 1.2      | 600-W Power Distribution Board (PDB)              | 76  |

|    | 4.2.1    | Mechanical Overview                               | 77  |

|    | 4.2.2    | DC Output Specification                           | 82  |

|    | 4.2.3    | Protection Circuits                               | 88  |

|    | 4.2.4    | Control and Indicator Functions (Hard-wired)      | 89  |

|    | 4.2.5    | PMBus                                             | 91  |

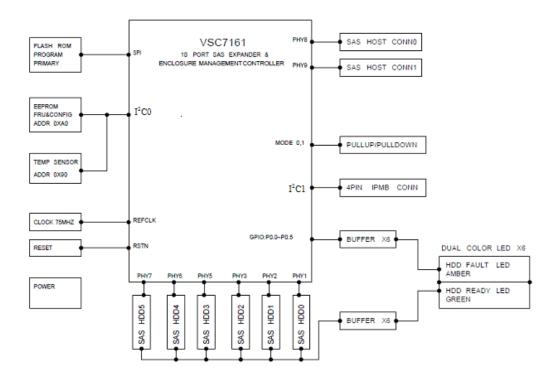

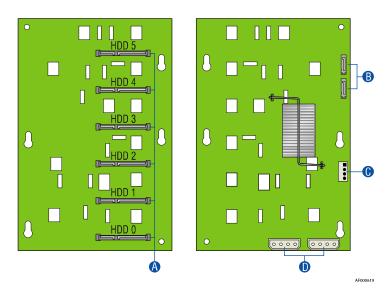

| 5. | 6-HDD I  | Expander SAS Hot Swap Backplane                   | 92  |

| 5  | 5.1      | 6-HDD Expander SAS Hot Swap Backplane Overview    | 92  |

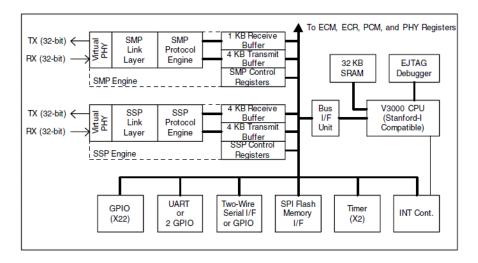

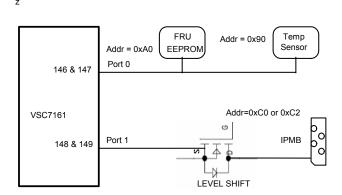

|    | 5.1.1    | SAS Expander Vitesse VSC7161*                     | 93  |

|    | 5.1.2    | General Purpose Input/Output (GPIO)               | 96  |

|    | 5.1.3    | External Memory Device                            | 97  |

|    | 5.1.4    | LEDs                                              | 97  |

|    | 5.1.5    | SAS/SATA Drive Connectors                         | 98  |

|    | 5.1.6    | Power Connectors                                  | 98  |

|    | 5.1.7    | Clock Generation and Distribution                 | 99  |

|    | 5.1.8    | IPMB Header - IPMB                                | 99  |

|    | 5.1.9    | Active Hot-swap Backplane (HSBP) Cables Explained | 99  |

|    | 5.1.10   | Board Layouts                                     | 100 |

|    | 5.1.11   | Connector Specifications                          | 100 |

| 6. | Platforn | n Management                                      | 101 |

| 6  | 6.1      | Feature Support                                   | 101 |

|    | 6.1.1    | IPMI 2.0 Features                                 | 101 |

|    | 6.1.2    | Non-IPMI Features                                 | 101 |

| 6  | 6.2      | Optional Advanced Management Feature Support      | 103 |

|    | 6.2.1    | Enabling Advanced Management Features             | 103 |

|    | 6.2.2    | Keyboard, Video, and Mouse (KVM) Redirection      | 104 |

|    | 6.2.3    | Media Redirection                                 | 104 |

|    | 6.2.4    | Web Services for Management (WS-MAN)              | 105 |

|    | 6.2.5    | Embedded Web server                               | 106 |

|    | 6.2.6    | Local Directory Authentication Protocol (LDAP)    | 106 |

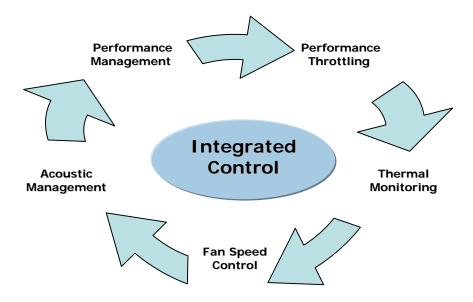

| 6  | 3.3      | Platform Control                                  | 107 |

|    | 6.3.1    | Memory Open and Closed Loop Thermal Throttling    | 108 |

|    | 6.3.2    | Fan Speed Control                                 | 108 |

| 6  | 6.4                    | Intel <sup>®</sup> Intelligent Power Node Manager | 110 |

|----|------------------------|---------------------------------------------------|-----|

|    | 6.4.1                  | Manageability Engine (ME)                         | 110 |

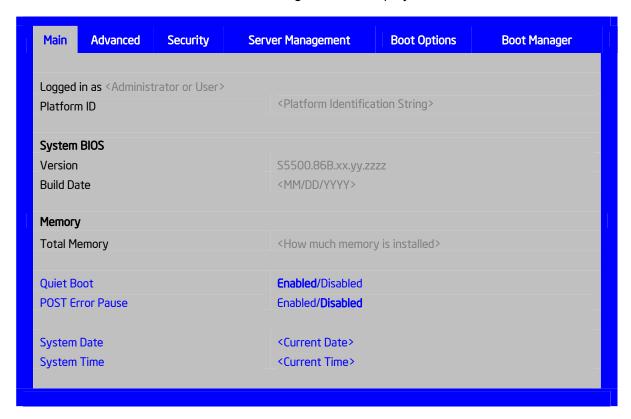

| 7. | BIOS S                 | Setup Utility                                     | 112 |

| 7  | 7.1                    | Logo / Diagnostic Screen                          | 112 |

| 7  | 7.2                    | BIOS Boot Popup Menu                              | 112 |

| 7  | 7.3                    | BIOS Setup Utility                                | 112 |

|    | 7.3.1                  | Operation                                         | 113 |

|    | 7.3.2                  | Server Platform Setup Utility Screens             | 115 |

| 8. | Conne                  | ctor/Header Locations and Pin-outs                | 151 |

| 8  | 3.1                    | Server Board Connector Information                | 151 |

| 8  | 3.2                    | Power Connectors                                  | 152 |

| 8  | 3.3                    | System Management Headers                         | 153 |

|    | 8.3.1                  | Intel® Remote Management Module 3 Connector       | 153 |

|    | 8.3.2                  | LCP / IPMB Header                                 | 154 |

|    | 8.3.3                  | HSBP Header                                       | 154 |

|    | 8.3.4                  | SGPIO Header                                      | 155 |

| 8  | 3.4                    | Front Panel Connector                             | 155 |

| 8  | 3.5                    | I/O Connectors                                    | 155 |

|    | 8.5.1                  | VGA Connector                                     | 155 |

|    | 8.5.2                  | NIC Connectors                                    | 156 |

|    | 8.5.3                  | SATA Connectors                                   | 157 |

|    | 8.5.4                  | SAS Module Slot                                   | 157 |

|    | 8.5.5                  | Serial Port Connectors                            | 158 |

|    | 8.5.6                  | USB Connector                                     | 159 |

| 8  | 3.6                    | Fan Headers                                       | 160 |

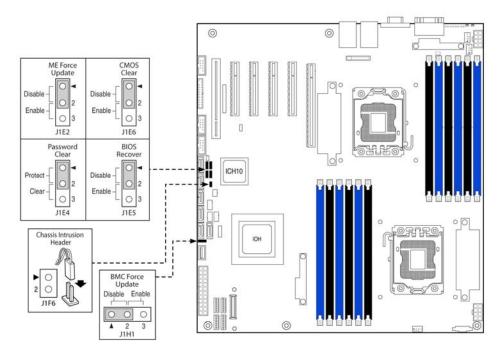

| 9. | Jumpe                  | er Blocks                                         | 162 |

| Ç  | 9.1                    | CMOS Clear and Password Reset Usage Procedure     | 163 |

|    | 9.1.1                  | Clearing the CMOS                                 | 163 |

|    | 9.1.2                  | Clearing the Password                             | 163 |

| Ç  | 9.2                    | Force BMC Update Procedure                        | 163 |

| Ç  | 9.3                    | BIOS Recovery Jumper                              | 164 |

| 10 | . Intel <sup>®</sup> L | Light Guided Diagnostics                          | 166 |

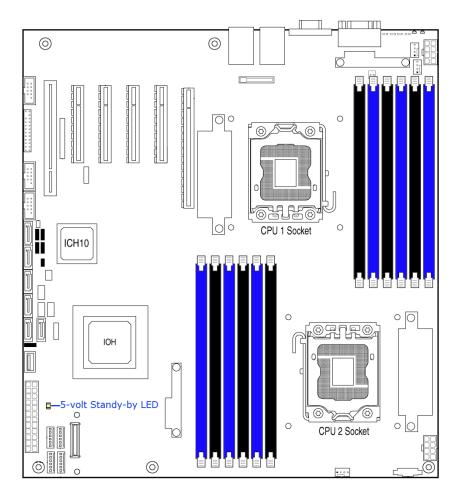

| •  | 10.1                   | 5-volt Stand-by LED                               | 166 |

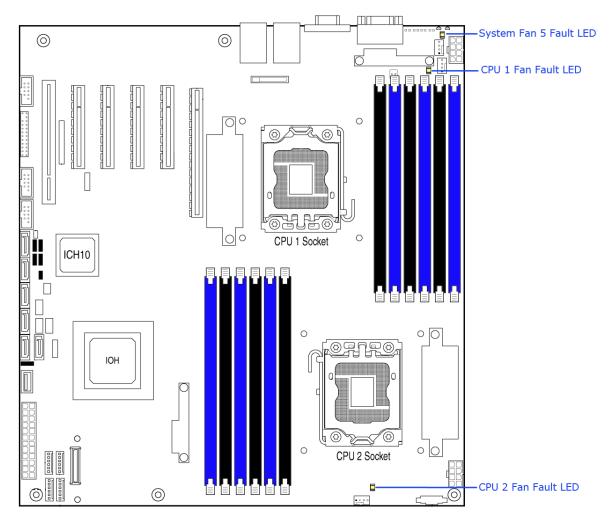

| •  | 10.2                   | Fan Fault LED's                                   | 167 |

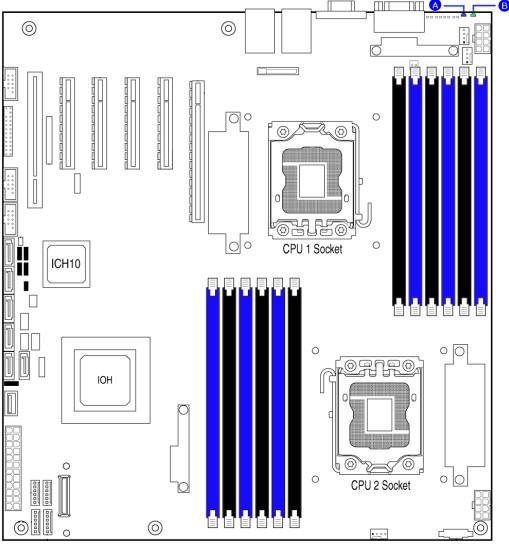

| •  | 10.3                   | System ID LED and System Status LED               | 169 |

#### **Table of Contents**

| 10.4        | DIMM Fault LEDs                                        | 171 |

|-------------|--------------------------------------------------------|-----|

| 10.5        | Post Code Diagnostic LEDs                              | 172 |

| 11. Design  | and Environmental Specifications                       | 173 |

| 11.1        | Intel® Server System SC5650HCBRP Design Specifications | 173 |

| 11.2        | MTBF                                                   | 173 |

| 11.3        | Processor Power Support                                | 175 |

| 12. Regula  | tory and Certification Information                     | 176 |

| 12.1        | Product Regulatory Compliance                          | 176 |

| 12.1.1      | Product Safety Compliance                              | 176 |

| 12.1.2      | Product EMC Compliance – Class A Compliance            | 176 |

| 12.1.3      | Certifications / Registrations / Declarations          | 177 |

| 12.2        | Product Regulatory Compliance Markings                 | 178 |

| 12.3        | Electromagnetic Compatibility Notices                  | 178 |

| FCC (U      | JSA)                                                   | 178 |

| ICES-0      | 03 (Canada)                                            | 180 |

| Europe      | (CE Declaration of Conformity)                         | 180 |

| VCCI (      | Japan)                                                 | 180 |

| BSMI (      | Taiwan)                                                | 180 |

| RRL K       | CC (Korea)                                             | 181 |

| 12.4        | Product Ecology Change (EU RoHS)                       | 181 |

| 12.5        | Product Ecology Change (CRoHS)                         | 181 |

| 12.6        | China Packaging Recycle Marks (or GB18455-2001)        | 184 |

| 12.7        | CA Perchlorate Warning                                 | 184 |

| 12.8        | End-of-Life / Product Recycling                        | 184 |

| Appendix A  | a: Integration and Usage Tips                          | 185 |

| Appendix B  | B: Processor Active Heat Sink Installation             | 187 |

| Appendix C  | : BMC Sensor Tables                                    | 188 |

|             | ): Platform Specific BMC Appendix                      |     |

| Appendix E  | : POST Code Diagnostic LED Decoder                     | 200 |

| Appendix F  | : POST Error Messages and Handling                     | 205 |

|             | : Installation Guidelines                              |     |

|             |                                                        |     |

| Reference l | Documents                                              | 216 |

## List of Figures

| Figure 1. Front View Components (with Front Bezel Assembly)                                | 5      |

|--------------------------------------------------------------------------------------------|--------|

| Figure 2. Front View Components (with Drive Access Door Open)                              | 6      |

| Figure 3. Internal Components                                                              | 7      |

| Figure 4. Back Panel Components                                                            | 7      |

| Figure 5. Front Panel Components                                                           | 8      |

| Figure 6. Mechanical Locks                                                                 | 9      |

| Figure 7. Major Board Components                                                           | 11     |

| Figure 8. Mounting Hole Locations                                                          | 12     |

| Figure 9. Major Connector Pin-1 Locations (1 of 2)                                         | 13     |

| Figure 10. Major Connector Pin-1 Locations (2 of 2)                                        | 14     |

| Figure 11. Primary Side Keep-out Zone (1 of 2)                                             | 15     |

| Figure 12. Primary Side Keep-out Zone (2 of 2)                                             | 16     |

| Figure 13. Primary Side Air Duct Keep-out Zone                                             | 17     |

| Figure 14. Primary Side Card-Side Keep-out Zone                                            | 18     |

| Figure 15. Second Side Keep-out Zone                                                       | 19     |

| Figure 16. Rear I/O Layout                                                                 | 20     |

| Figure 17. Intel <sup>®</sup> Server System SC5650HCBRP Functional Block Diagram           | 22     |

| Figure 18. Unified Retention System and Unified Back Plate Assembly                        | 29     |

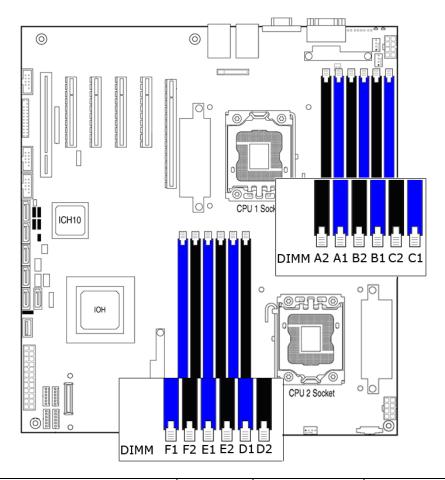

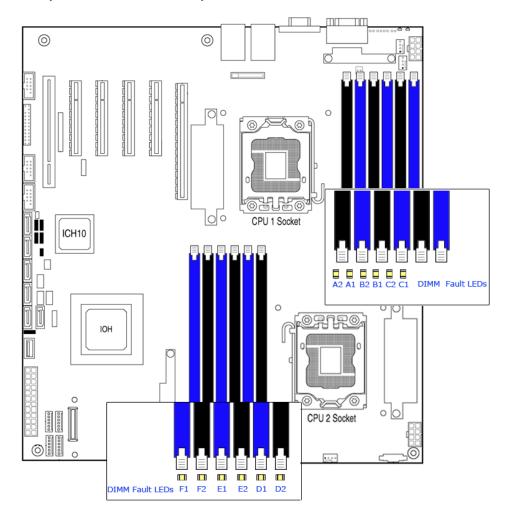

| Figure 19. Intel <sup>®</sup> Server System SC5650HCBRP DIMM Slots Arrangement             | 31     |

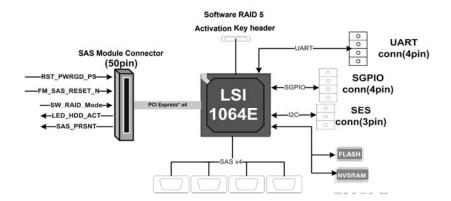

| Figure 20. Intel <sup>®</sup> SAS Entry RAID Module AXX4SASMOD Component and Connector Lay | out.46 |

| Figure 21. Intel <sup>®</sup> SAS Entry RAID Module AXX4SASMOD Functional Block Diagram    | 47     |

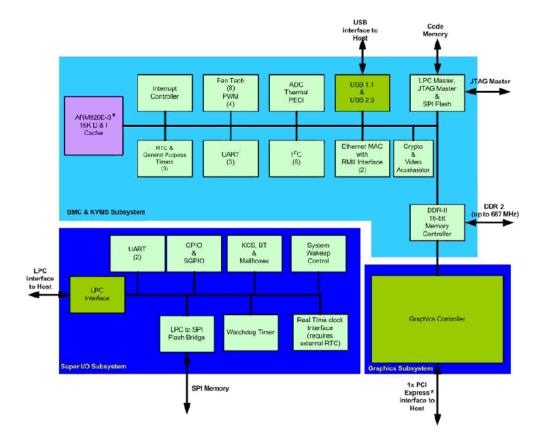

| Figure 22. Integrated BMC Hardware                                                         | 50     |

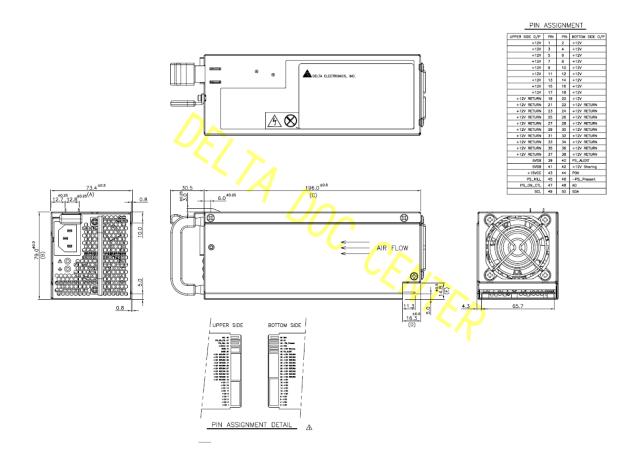

| Figure 23. Power Supply Enclosure - Dimensional Drawing                                    | 55     |

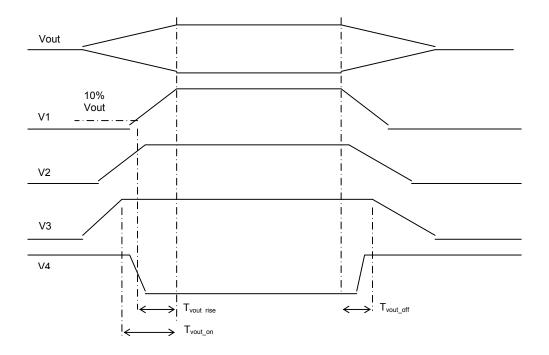

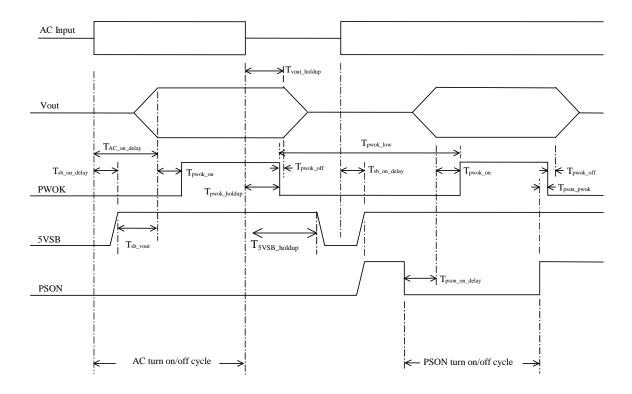

| Figure 24. Output Voltage Timing                                                           | 67     |

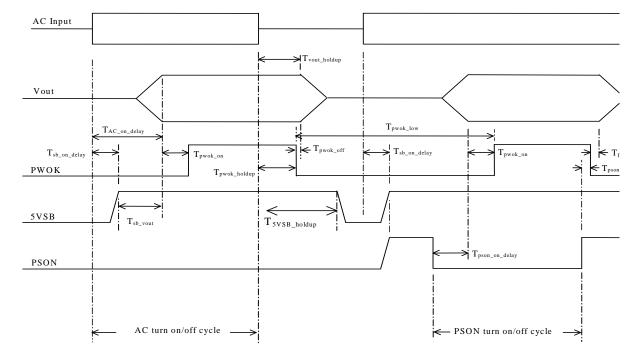

| Figure 25. Turn On/Off Timing (Power Supply Signals)                                       | 69     |

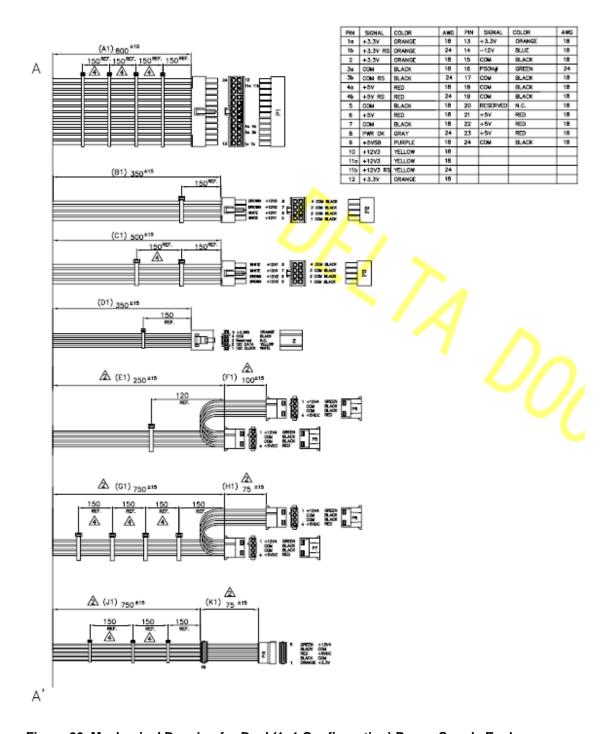

| Figure 26. Mechanical Drawing for Dual (1+1 Configuration) Power Supply Enclosure          | 78     |

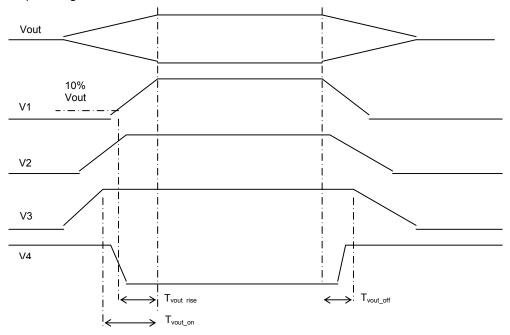

| Figure 27. Output Voltage Timing                                                           | 86     |

| Figure 28. Turn On/Off Timing (Power Supply Signals)                                       | 87     |

| Figure 29. 6HDD Active SAS/SATA HSBP Block Diagram                                         | 93     |

| Figure 30. Expander Management (EM) subsystem                                              | 94     |

| Figure 31, Active SAS/SATA HSBP I <sup>2</sup> C Bus Connection Diagram                    | 95     |

| Figure 32. 6-HDD Expander SAS HSBP Board Layout                                        | 100     |

|----------------------------------------------------------------------------------------|---------|

| Figure 33. SMBUS Block Diagram                                                         | 111     |

| Figure 34. Setup Utility — Main Screen Display                                         | 116     |

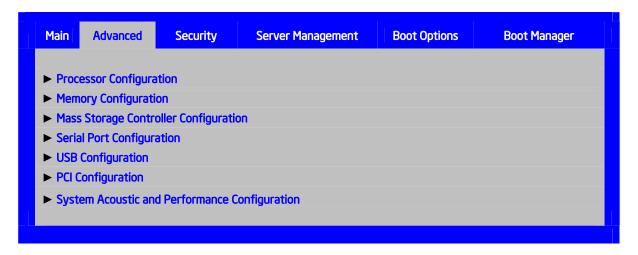

| Figure 35. Setup Utility — Advanced Screen Display                                     | 118     |

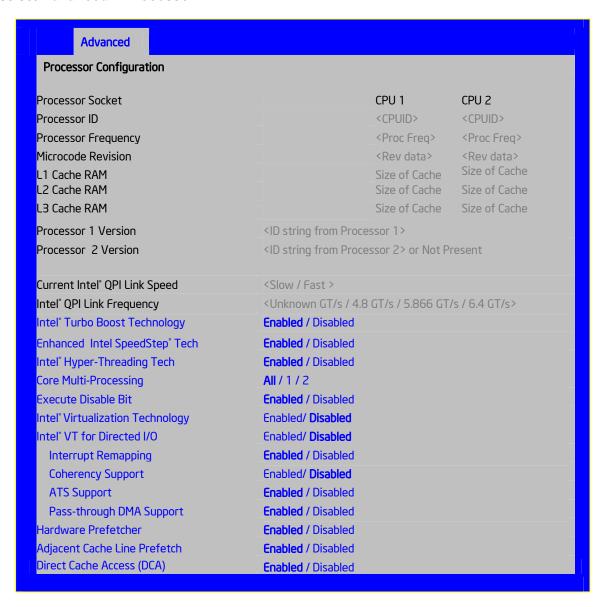

| Figure 36. Setup Utility — Processor Configuration Screen Display                      | 119     |

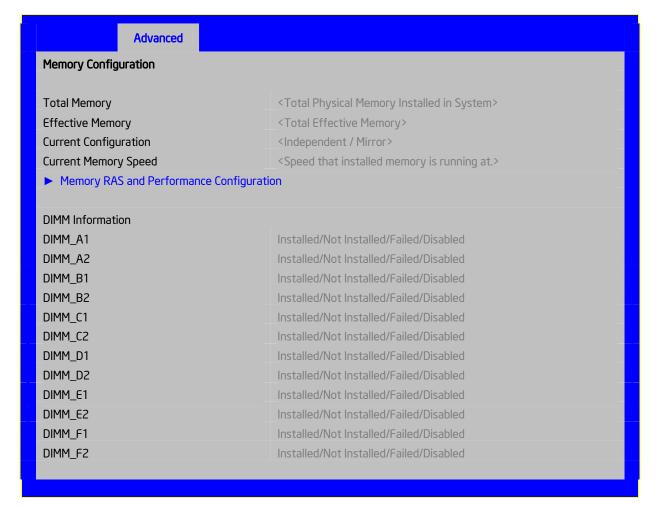

| Figure 37. Setup Utility — Memory Configuration Screen Display                         | 122     |

| Figure 38. Setup Utility — Configure RAS and Performance Screen Display                | 124     |

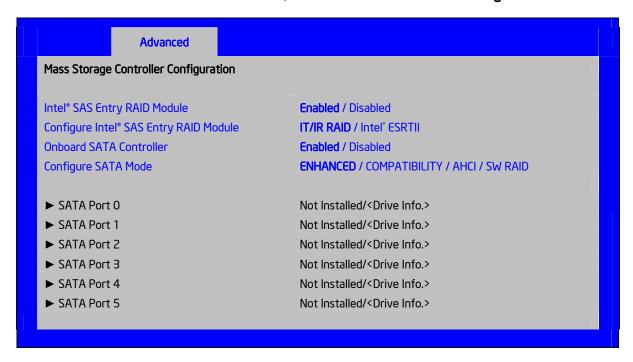

| Figure 39. Setup Utility — Mass Storage Controller Configuration Screen Display        | 125     |

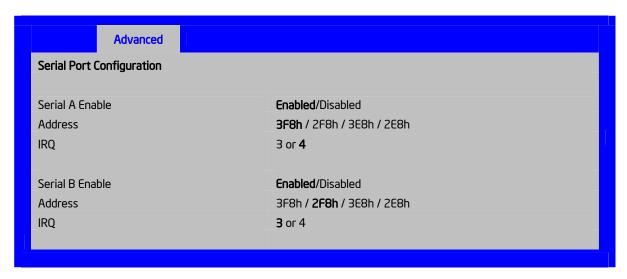

| Figure 40. Setup Utility — Serial Port Configuration Screen Display                    | 127     |

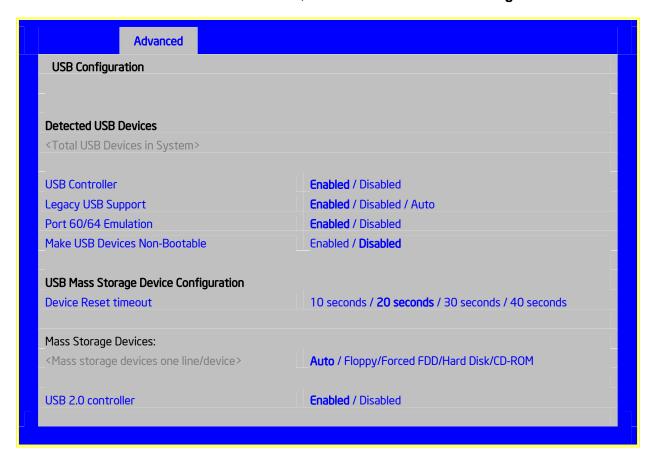

| Figure 41. Setup Utility — USB Controller Configuration Screen Display                 | 128     |

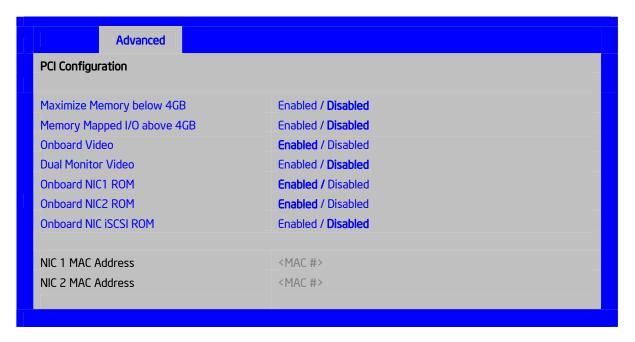

| Figure 42. Setup Utility — PCI Configuration Screen Display                            | 130     |

| Figure 43. Setup Utility — System Acoustic and Performance Configuration Screen Displa | y . 131 |

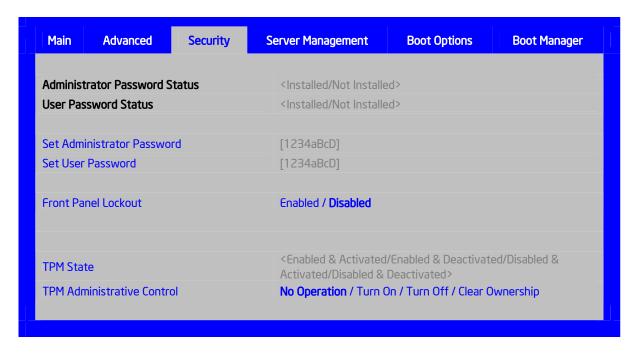

| Figure 44. Setup Utility — Security Configuration Screen Display                       | 133     |

| Figure 45. Setup Utility — Server Management Configuration Screen Display              | 135     |

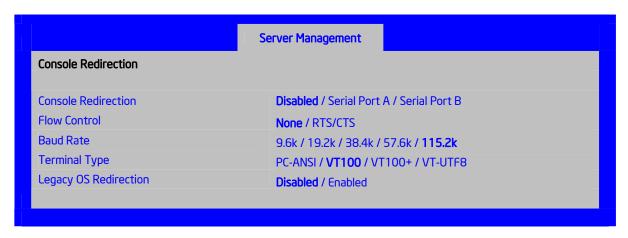

| Figure 46. Setup Utility — Console Redirection Screen Display                          | 137     |

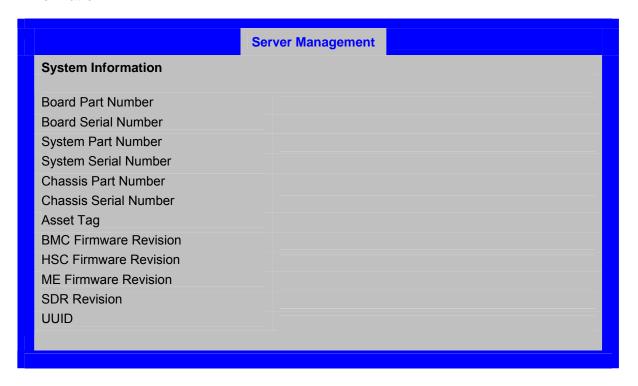

| Figure 47. Setup Utility — Server Management System Information Screen Display         | 139     |

| Figure 48. Setup Utility — Boot Options Screen Display                                 | 140     |

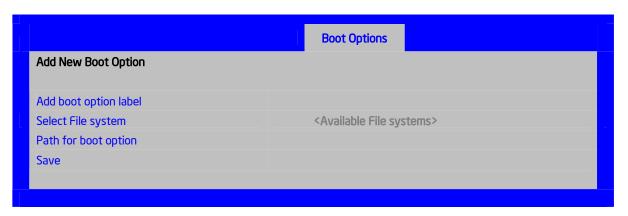

| Figure 49. Setup Utility — Add New Boot Option Screen Display                          | 142     |

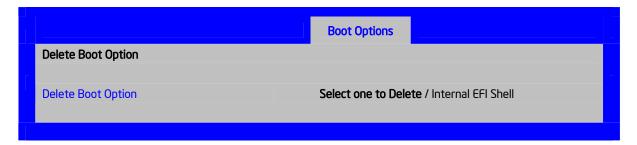

| Figure 50. Setup Utility — Delete Boot Option Screen Display                           | 143     |

| Figure 51. Setup Utility — Hard Disk Order Screen Display                              | 144     |

| Figure 52. Setup Utility — CDROM Order Screen Display                                  | 144     |

| Figure 53. Setup Utility — Floppy Order Screen Display                                 | 145     |

| Figure 54. Setup Utility — Network Device Order Screen Display                         | 146     |

| Figure 55. Setup Utility — BEV Device Order Screen Display                             | 146     |

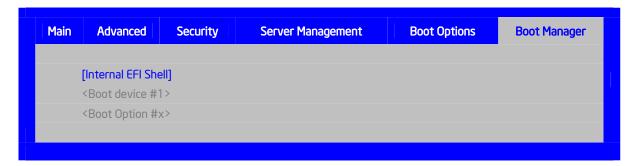

| Figure 56. Setup Utility — Boot Manager Screen Display                                 | 147     |

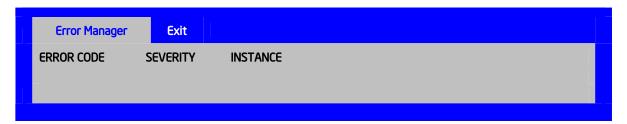

| Figure 57. Setup Utility — Error Manager Screen Display                                | 148     |

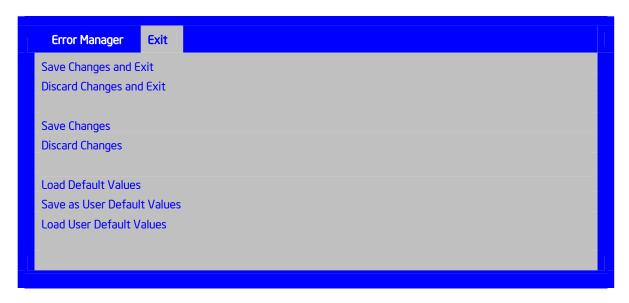

| Figure 58. Setup Utility — Exit Screen Display                                         | 149     |

| Figure 59. Jumper Blocks (J1E2, J1E4, J1E5, J1E6, J1H1)                                | 162     |

| Figure 60. 5-volt Stand-by Status LED Location                                         | 167     |

| Figure 61. Fan Fault LED's Location                                                    | 168     |

| Figure 62. System Status LED Location                                                  | 169     |

| Figure 63. DIMM Fault LED's Location                                                   | 171     |

| Figure 64. POST Code Diagnostic LED Locations                                          | 172     |

| Figure 65. Active Processor Heatsink Installation Requirement                          | 187     |

| Figure 66. Diagnostic LED Placement Diagram                                            | 200     |

## List of Tables

| Table 1. IOH High-Level Summary                                             | 23 |

|-----------------------------------------------------------------------------|----|

| Table 2. Mixed Processor Configurations                                     | 26 |

| Table 3. Memory Running Frequency vs. Processor SKU                         | 33 |

| Table 4. Memory Running Frequency vs. Memory Population                     | 33 |

| Table 5. Supported DIMM Population under the Dual Processors Configuration  | 40 |

| Table 6. Supported DIMM Population under the Single Processor Configuration | 40 |

| Table 7. Onboard SATA Storage Mode Matrix                                   | 43 |

| Table 8. Intel® Server System SC5650HCBRP PCI Bus Segment Characteristics   | 45 |

| Table 9. Intel® SAS Entry RAID Module AXX4SASMOD Storage Mode               | 48 |

| Table 10. Serial B Header Pin-out                                           | 51 |

| Table 11. Video Modes                                                       | 52 |

| Table 12. Onboard NIC Status LED                                            | 53 |

| Table 13. Acoustic Requirements                                             | 57 |

| Table 14. Thermal Requirements                                              | 57 |

| Table 15. Efficiency                                                        | 58 |

| Table 16. AC Input Rating                                                   | 58 |

| Table 17. AC Line Sag Transient Performance                                 | 59 |

| Table 18. AC Line Surge Transient Performance                               | 59 |

| Table 19. Performance Criteria                                              | 60 |

| Table 20. Holdup Requirements                                               | 61 |

| Table 21. Edge Finger Power Supply Connector Pin-out                        | 63 |

| Table 22. Power Supply Module Load Ratings                                  | 64 |

| Table 23. Voltage Regulation Limits                                         | 65 |

| Table 24. Transient Load Requirements                                       | 65 |

| Table 25. Capacitive Loading Conditions                                     | 65 |

| Table 26. Ripple and Noise                                                  | 66 |

| Table 27. Output Voltage Timing                                             | 66 |

| Table 28. Turn On / Off Timing                                              | 68 |

| Table 29. Over-current Protection (OCP)                                     | 70 |

| Table 30. Over-voltage Protection Limits                                    | 71 |

| Table 31. PSON# Signal Characteristic                                       | 72 |

| Table 32. PSKILL Signal Characteristics                                     | 72 |

| Table 33. PWOK Signal Characteristics                                    | 73  |

|--------------------------------------------------------------------------|-----|

| Table 34. LED Indicators                                                 | 74  |

| Table 35. Environmental Requirements                                     | 79  |

| Table 36. Cable Lengths                                                  | 79  |

| Table 37. P1 Baseboard Power Connector                                   | 79  |

| Table 38. P2 Processor 0 Power Connector                                 | 81  |

| Table 39. P3 Processor 1 Power Connector                                 | 81  |

| Table 40. P5, P6, P7, and P8 Peripheral Power Connectors                 | 82  |

| Table 41. P9 Right-angle SATA Power Connector                            | 82  |

| Table 42. P10 SATA Power Connector                                       | 82  |

| Table 43. +12V Outputs Load Ratings                                      | 83  |

| Table 44. DC/DC Converters Load Ratings                                  | 83  |

| Table 45. Voltage Regulation Limits                                      | 84  |

| Table 46. Transient Load Requirements                                    | 84  |

| Table 47. Capacitive Loading Conditions                                  | 84  |

| Table 48. Ripple and Noise                                               | 85  |

| Table 49. Output Voltage Timing                                          | 86  |

| Table 50. Turn On / Off Timing                                           | 86  |

| Table 51. Over-current Protection Limits / 240VA Protection              | 88  |

| Table 52. Over-voltage Protection (OVP) Limits                           | 89  |

| Table 53. PSON# Signal Characteristics                                   | 89  |

| Table 54. PWOK Signal Characteristics                                    | 90  |

| Table 55. SMBAlert# Signal Characteristics                               | 90  |

| Table 56. 7-pin SAS Connector Pin-out                                    | 95  |

| Table 57. I <sup>2</sup> C Bus Addressing                                | 95  |

| Table 58. 6HDD I <sup>2</sup> C Bus Loading                              | 96  |

| Table 59. VSC7161* SAS Expander GPIO Assignment                          | 96  |

| Table 60. LED Function                                                   | 97  |

| Table 61. 22-pin SAS/SATA Connector Pin-out                              | 98  |

| Table 62. Power Connector Pin-out                                        | 98  |

| Table 63. IPMB Header Pin-out                                            | 99  |

| Table 64. 6-HDD Expander SAS Hot-swap Backplane Connector Specifications | 100 |

| Table 65. Basic and Advanced Management Features                         | 103 |

| Table 66. Intel® Server System SC5650HCBRP Fan Domain Table              | 109 |

| Table 67. BIOS Setup Page Layout                                         | 113 |

| Table 68. BIOS Setup: Keyboard Command Bar                                            | 114 |

|---------------------------------------------------------------------------------------|-----|

| Table 69. Setup Utility — Main Screen Fields                                          | 116 |

| Table 70. Setup Utility — Advanced Screen Display Fields                              | 118 |

| Table 71. Setup Utility — Processor Configuration Screen Fields                       | 120 |

| Table 72. Setup Utility — Memory Configuration Screen Fields                          | 123 |

| Table 73. Setup Utility — Configure RAS and Performance Screen Fields                 | 124 |

| Table 74. Setup Utility — Mass Storage Controller Configuration Screen Fields         | 125 |

| Table 75. Setup Utility — Serial Ports Configuration Screen Fields                    | 127 |

| Table 76. Setup Utility — USB Controller Configuration Screen Fields                  | 129 |

| Table 77. Setup Utility — PCI Configuration Screen Fields                             | 130 |

| Table 78. Setup Utility — System Acoustic and Performance Configuration Screen Fields | 132 |

| Table 79. Setup Utility — Security Configuration Screen Fields                        | 133 |

| Table 80. Setup Utility — Server Management Configuration Screen Fields               | 136 |

| Table 81. Setup Utility — Console Redirection Configuration Fields                    | 138 |

| Table 82. Setup Utility — Server Management System Information Fields                 | 139 |

| Table 83. Setup Utility — Boot Options Screen Fields                                  | 141 |

| Table 84. Setup Utility — Add New Boot Option Fields                                  | 142 |

| Table 85. Setup Utility — Delete Boot Option Fields                                   | 143 |

| Table 86. Setup Utility — Hard Disk Order Fields                                      | 144 |

| Table 87. Setup Utility — CDROM Order Fields                                          | 145 |

| Table 88. Setup Utility — Floppy Order Fields                                         | 145 |

| Table 89. Setup Utility — Network Device Order Fields                                 | 146 |

| Table 90. Setup Utility — BEV Device Order Fields                                     | 147 |

| Table 91. Setup Utility — Boot Manager Screen Fields                                  | 147 |

| Table 92. Setup Utility — Error Manager Screen Fields                                 | 148 |

| Table 93. Setup Utility — Exit Screen Fields                                          | 149 |

| Table 94. Board Connector Matrix                                                      | 151 |

| Table 95. Main Power Connector Pin-out (J1K3)                                         | 152 |

| Table 96. CPU 1 Power Connector Pin-out (J9A1)                                        | 153 |

| Table 97. CPU 2 Power Connector Pin-out (J9K1)                                        | 153 |

| Table 98. Power Supply Auxiliary Signal Connector Pin-out (J9K2)                      | 153 |

| Table 99. Intel <sup>®</sup> RMM3 Connector Pin-out (J1C1)                            | 154 |

| Table 100. LCP / IPMB Header Pin-out (J1G6)                                           | 154 |

| Table 101. HSBP Header Pin-out (J1F5, J1G3)                                           | 154 |

| Table 102. SGPIO Header Pin-out (J1G2)                                                | 155 |

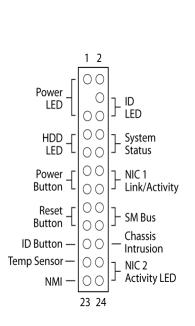

| Table 103. Front Panel SSI Standard 24-pin Connector Pin-out (J1B3)                     | 155 |

|-----------------------------------------------------------------------------------------|-----|

| Table 104. VGA Connector Pin-out (J7A1)                                                 | 156 |

| Table 105. RJ-45 10/100/1000 NIC Connector Pin-out (J5A1, J6A1)                         | 156 |

| Table 106. SATA / SAS Connector Pin-out (J1E3, J1G1, J1G4, J1G5, J1F1, J1F4)            | 157 |

| Table 107. SAS Module Slot Pin-out (J2J1)                                               | 157 |

| Table 108. External DB9 Serial A Port Pin-out (J8A1)                                    | 158 |

| Table 109. Internal 9-pin Serial B Header Pin-out (J1B1)                                | 158 |

| Table 110. External USB Connector Pin-out (J5A1, J6A1)                                  | 159 |

| Table 111. Internal USB Connector Pin-out (J1D1)                                        | 159 |

| Table 112. Internal USB Connector Pin-out (J1D2)                                        | 159 |

| Table 113. Pin-out of Internal Low-Profile USB Connector for Solid State Drive (J2D2)   | 160 |

| Table 114. Internal Type A USB Port Pin-out (J1H2)                                      | 160 |

| Table 115. SSI 4-pin Fan Header Pin-out (J7K1, J9A2, J9A3)                              | 161 |

| Table 116. SSI 6-pin Fan Header Pin-out (J1K1, J1K2, J1K4, J1K5)                        | 161 |

| Table 117. Server Board Jumpers (J1E6, J1E2, J1E4, J1E5, J1H1)                          | 162 |

| Table 118. System Status LED                                                            | 170 |

| Table 119. Server Board Design Specifications                                           | 173 |

| Table 120. MTBF Estimate                                                                | 174 |

| Table 121. Intel <sup>®</sup> Xeon <sup>®</sup> Processor Dual Processor TDP Guidelines | 175 |

| Table 122. Compatible Heatsink Matrix                                                   | 187 |

| Table 123. Integrated BMC Core Sensors                                                  | 190 |

| Table 124. Platform Specific BMC Features                                               | 199 |

| Table 125. POST Progress Code LED Example                                               | 200 |

| Table 126. POST Codes and Messages                                                      | 201 |

| Table 127. POST Error Messages and Handling                                             | 206 |

| Table 128. POST Error Beep Codes                                                        | 209 |

| Table 129. BMC Beep Codes                                                               | 209 |

<This page intentionally left blank.>

### 1. Introduction

This Technical Product Specification (TPS) provides board-specific information detailing the features, functionality, and high-level architecture of the Intel® Server System SC5650HCBRP.

In addition, you can obtain design-level information for a given subsystem by ordering the External Product Specifications (EPS) for the specific subsystem. EPS documents are not publicly available and you must order them through your local Intel representative.

#### 1.1 Chapter Outline

This document is divided into the following chapters:

- Chapter 1 Introduction

- Chapter 2 Overview

- Chapter 3 Functional Architecture

- Chapter 4 Power Sub-system

- Chapter 5 6-HDD Expander SAS Hot Swap Backplane

- Chapter 6 Platform Management

- Chapter 7 BIOS Setup Utility

- Chapter 8 Connector / Header Locations and Pin-outs

- Chapter 9 Jumper Blocks

- Chapter 10 Intel<sup>®</sup> Light Guided Diagnostics

- Chapter 11 Design and Environmental Specifications

- Chapter 12 Regulatory and Certification Information

- Appendix A Integration and Usage Tips

- Appendix B Processor Active Heat Sink Installation

- Appendix C BMC Sensor Tables

- Appendix D Platform Specific BMC Appendix

- Appendix E POST Code Diagnostic LED Decoder

- Appendix F POST Error Messages and Handling

- Appendix G Installation Guidelines

- Glossary

- Reference Documents

### 1.2 Server System Use Disclaimer

Intel<sup>®</sup> Server Systems contain a number of high-density VLSI (Very-large-scale integration) and power delivery components that require adequate airflow for cooling. Intel ensures through its own chassis development and testing that when Intel<sup>®</sup> server building blocks are used together, the fully integrated system meets the intended thermal requirements of these components. It is the responsibility of the system integrator who chooses not to use Intel developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of airflow required for their specific application and environmental conditions. Intel Corporation

cannot be held responsible if components fail or the server board does not operate correctly when used outside any of the published operating or non-operating limits.

## 2. Overview

The Intel $^{\circ}$  Server System SC5650HCBRP has monolithic printed circuit board (PCB) with features designed to support the pedestal server markets.

## 2.1 Intel® Server System SC5650HCBRP Feature Set

| Feature                                                                             | Description                                                                                                                                                                                                                                                                                              |  |  |  |  |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Processors                                                                          | Support for one or two Intel® Xeon® Processor(s) 5500 series up to 95W Thermal Design Power                                                                                                                                                                                                              |  |  |  |  |

|                                                                                     | Support for one or two Intel® Xeon® Processor(s) 5600 series up to 130W Thermal Design Power                                                                                                                                                                                                             |  |  |  |  |

|                                                                                     | 4.8 GT/s, 5.86 GT/s, and 6.4 GT/s Intel® QuickPath Interconnect (Intel® QPI)                                                                                                                                                                                                                             |  |  |  |  |

|                                                                                     | FC-LGA 1366 Socket B                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                     | Enterprise Voltage Regulator-Down (EVRD) 11.1                                                                                                                                                                                                                                                            |  |  |  |  |

| Memory                                                                              | Six memory channels (three channels for each processor socket)                                                                                                                                                                                                                                           |  |  |  |  |

|                                                                                     | ■ Channels A, B, C, D, E, and F                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                                                                     | 12 DIMM slots, two DIMM slots per channel                                                                                                                                                                                                                                                                |  |  |  |  |

|                                                                                     | Support for 800/166/1333 MT/s ECC Registered DDR3 Memory (RDIMM), ECC Unbuffered DDR3 memory (UDIMM)                                                                                                                                                                                                     |  |  |  |  |

|                                                                                     | No support for mixing of RDIMMs and UDIMMs                                                                                                                                                                                                                                                               |  |  |  |  |

| Chipset                                                                             | Intel® 5520 Chipset                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                                                     | Intel® 82801JIR I/O Controller Hub (ICH10R)                                                                                                                                                                                                                                                              |  |  |  |  |

| Add-in Card Slots                                                                   | Six expansion slots                                                                                                                                                                                                                                                                                      |  |  |  |  |

| <ul> <li>One PCI Express* Gen 2 slot (x16 Mechanically, x8 Electrically)</li> </ul> |                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                                                                     | ■ Three PCI Express* Gen 2 x8 slots                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                                                     | <ul> <li>One PCI Express* Gen 1 slot (x8 Mechanically, x4 Electrically) shared with SAS Module<br/>slot.</li> </ul>                                                                                                                                                                                      |  |  |  |  |

|                                                                                     | <ul> <li>One 32-bit/33 MHz PCI slot, keying for 5 V and Universal PCI add-in card</li> </ul>                                                                                                                                                                                                             |  |  |  |  |

| Hard Drive and<br>Optical Drive Support                                             | One expander backplane drive bay for up to six hot-swap SAS/SATA drives at 3GB/s, requires SAS add-in adapter or SAS module card accessory                                                                                                                                                               |  |  |  |  |

|                                                                                     | Optional 2.5" drive carrier (AXX25DRVADPTR) to install 2.5" hard disk drive into 3.5" hotswap hard disk drive bay                                                                                                                                                                                        |  |  |  |  |

| RAID Support                                                                        | Optional Intel® SAS Entry RAID Module AXX4SASMOD provides Intel® Embedded<br>Server RAID Technology II with SAS RAID 0, 1, 10, and optional RAID 5 support provided<br>by the Intel® RAID Activation Key AXXRAKSW5, or IT/IR RAID with entry hardware RAID 0, 1, 10/1E, and native SAS pass through mode |  |  |  |  |

|                                                                                     | Optional Intel® Integrated RAID Module SROMBSASMR (AXXROMBSASMR), provides RAID 0, 1, 5, 6 and striping capability for spans 10, 50, and 60                                                                                                                                                              |  |  |  |  |

| USB Drive Support                                                                   | One internal type A USB port with USB 2.0 support that supports a peripheral, such as a floppy drive                                                                                                                                                                                                     |  |  |  |  |

|                                                                                     | One internal low-profile USB port for USB Solid State Drive                                                                                                                                                                                                                                              |  |  |  |  |

| Feature                        | Description                                                                                                                                         |  |  |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| I/O control support            | External connections:                                                                                                                               |  |  |  |  |

|                                | DB9 serial port A connection                                                                                                                        |  |  |  |  |

|                                | One DH 10 serial port connector (optional)                                                                                                          |  |  |  |  |

|                                | <ul> <li>Two RJ-45 NIC connectors for 10/100/1000 Mb connections: Dual GbE through the<br/>Intel<sup>®</sup> 82575EB Network Connection.</li> </ul> |  |  |  |  |

|                                | <ul> <li>Four USB 2.0 ports at the back of the board</li> </ul>                                                                                     |  |  |  |  |

|                                | Internal connections:                                                                                                                               |  |  |  |  |

|                                | <ul> <li>Two 9-pin USB headers, each supports two USB 2.0 ports</li> </ul>                                                                          |  |  |  |  |

|                                | One DH10 serial port B header                                                                                                                       |  |  |  |  |

|                                | <ul> <li>Six SATA connectors at 1.5 Gbps and 3 Gbps</li> </ul>                                                                                      |  |  |  |  |

|                                | • Four SAS connectors at 3 Gbps (optional)                                                                                                          |  |  |  |  |

|                                | One SSI-compliant 24-pin front control panel header                                                                                                 |  |  |  |  |

| Video Support                  | ServerEngines* LLC Pilot II* with 64 MB DDR2 memory, 8 MB allocated to graphics                                                                     |  |  |  |  |

|                                | Integrated 2D video controller                                                                                                                      |  |  |  |  |

|                                | Dual monitor video mode is supported                                                                                                                |  |  |  |  |

| LAN                            | Two Gigabit through Intel® 82575EB PHYs with Intel® I/O Acceleration Technology 2 support                                                           |  |  |  |  |

| Server Management              | Onboard ServerEngines* LLC Pilot II* Controller                                                                                                     |  |  |  |  |

|                                | <ul> <li>Integrated Baseboard Management Controller (Integrated BMC), IPMI 2.0 compliant</li> </ul>                                                 |  |  |  |  |

|                                | Integrated Super I/O on LPC interface                                                                                                               |  |  |  |  |

|                                | Support for Intel <sup>®</sup> Remote Management Module 3                                                                                           |  |  |  |  |

|                                | Intel <sup>®</sup> Light-Guided Diagnostics on field replaceable units                                                                              |  |  |  |  |

|                                | Support for Intel® System Management Software 3.1 and beyond                                                                                        |  |  |  |  |

|                                | Support for Intel® Intelligent Power Node Manager (Need PMBus-compliant power supply)                                                               |  |  |  |  |

| BIOS Flash                     | Winbond* W25X64                                                                                                                                     |  |  |  |  |

| Server Board Form Factor       | • SSI EEB (12"x13")                                                                                                                                 |  |  |  |  |

| Chassis Dimensions             | Pedestal Configuration: 17.8 inches high, 9.256 inches wide, 19 inches deep                                                                         |  |  |  |  |

|                                | Rack Configuration: 9.256 inches high, 17.6 inches wide, 19 inches deep                                                                             |  |  |  |  |

| Peripherals                    | Two multi-mount 5.25-inch peripheral bays                                                                                                           |  |  |  |  |

|                                | One 3.5-inch peripheral bay                                                                                                                         |  |  |  |  |

| Control Panel                  | Front Control Panel                                                                                                                                 |  |  |  |  |

| (dependent on option selected) | Intel® Local Control Panel (optional)                                                                                                               |  |  |  |  |

| LEDs and displays              | With Front Control Panel                                                                                                                            |  |  |  |  |

| (dependent on option selected) | NIC1 Activity                                                                                                                                       |  |  |  |  |

|                                | NIC2 Activity                                                                                                                                       |  |  |  |  |

|                                | • Power/Sleep                                                                                                                                       |  |  |  |  |

| D 0 :                          | System Status LED                                                                                                                                   |  |  |  |  |

| Power Supply                   | One 600-W PFC power supply is standard                                                                                                              |  |  |  |  |

|                                | Upgradable to full, hot-swap redundancy by adding a second power supply module.                                                                     |  |  |  |  |

| Cooling                        | Two 120-mm system fans (rear fan and PCI zone)                                                                                                      |  |  |  |  |

|                                | One 92-mm system fans (Hard Disk Cage fan)                                                                                                          |  |  |  |  |

|                                | Active processor heat sink(s) is required                                                                                                           |  |  |  |  |

<sup>\*</sup> The PCI Express\* Gen 1 slot (x8 Mechanically, x4 Electrically) is not available when the SAS module slot is in use and vice versa.

## 2.1.1 Intel® Server System SC5650HCBRP Layout

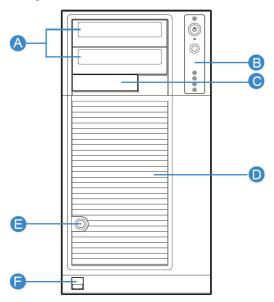

#### 2.1.1.1 Front View Components

| Α                       | 5.25-inch Device Drive Bays      |  |

|-------------------------|----------------------------------|--|

| B Front Control Panel   |                                  |  |

| С                       | C 3.5-inch Drive Bay Access Door |  |

| D Drive Bay Access Door |                                  |  |

| E Door Lock             |                                  |  |

| F Front Panel USB Ports |                                  |  |

Figure 1. Front View Components (with Front Bezel Assembly)

Figure 2. Front View Components (with Drive Access Door Open)

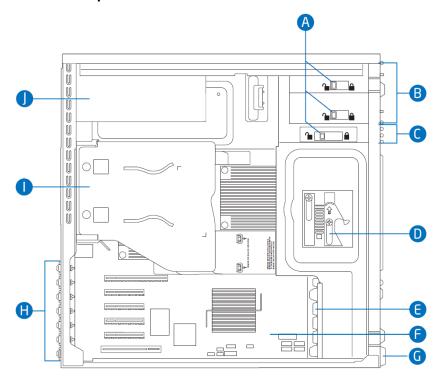

#### 2.1.1.2 Internal Components

| Α | Tool-less Device Bay Locks     |  |  |  |

|---|--------------------------------|--|--|--|

| В | 5.25-inch Device Bays          |  |  |  |

| С | 3.5-inch Device Bay            |  |  |  |

| D | Drive Cage Retention Mechanism |  |  |  |

| Е | PCI Add-in Card Guide / System |  |  |  |

|   | Fan Assembly                   |  |  |  |

| F | Server Board                   |  |  |  |

| G | Front Panel USB Ports          |  |  |  |

| Н | Rear Tool-less PCI Retention   |  |  |  |

|   | Mechanisms                     |  |  |  |

|   | Fan Duct / System Fan Assembly |  |  |  |

| J | Power Supply                   |  |  |  |

Figure 3. Internal Components

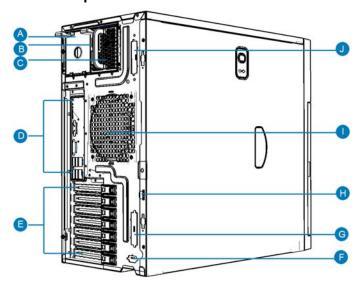

### 2.1.1.3 Back Panel Components

| Α                                 | Power Supply Blank Filler Panel  |  |  |

|-----------------------------------|----------------------------------|--|--|

| В                                 | A/C Power In                     |  |  |

| С                                 | Power Supply Unit                |  |  |

| D                                 | Rear I/O Shield                  |  |  |

| Е                                 | PCI Add-in Card Slots            |  |  |

| F Alternate Serial B Port Knockou |                                  |  |  |

| G                                 | External SCSI Port Knockout      |  |  |

| Н                                 | Location to Install Padlock Loop |  |  |

| I                                 | Rear Chassis Fan Assembly        |  |  |

| J                                 | External SCSI Port Knockout      |  |  |

**Figure 4. Back Panel Components**

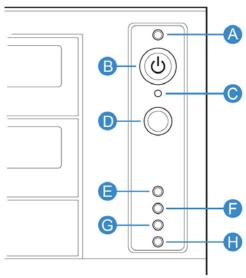

#### 2.1.1.4 Front Control Panel

| Callout        | Button / LED Name             | Color        | Condition                                                                | Description                                                                                                                       |  |

|----------------|-------------------------------|--------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| А              | Power LED                     | Green        | On                                                                       | Power on                                                                                                                          |  |

|                | LOWEL LED                     |              | Off                                                                      | Power off                                                                                                                         |  |

| В              | Power Button                  | N/A          | N/A Powers the system on or off                                          |                                                                                                                                   |  |

| С              | NMI Button                    | N/A          | N/A Used to force system halt and dump memory contents to screen or file |                                                                                                                                   |  |

| D              | Reset Button                  | N/A          | N/A                                                                      | Reboots and initializes the system                                                                                                |  |

|                | NIC1 Activity                 | Green        | On                                                                       | Linked                                                                                                                            |  |

| Е              |                               |              | Blink                                                                    | LAN activity                                                                                                                      |  |

|                |                               |              | Off                                                                      | Idle                                                                                                                              |  |

| F              | NIC2 Activity                 | Green        | On                                                                       | Linked                                                                                                                            |  |

|                |                               |              | Blink                                                                    | LAN activity                                                                                                                      |  |

|                |                               |              | Off                                                                      | Idle                                                                                                                              |  |

| G              | Hard Drive Activity           | Green        | Blink                                                                    | Hard drive activity                                                                                                               |  |

|                | System Status LED             | Green        | On                                                                       | System booted and ready                                                                                                           |  |

| Н              |                               |              | Blink                                                                    | System ready, but degraded: some CPU fault, DIMM killed, and so forth                                                             |  |

|                |                               | Amber        | On                                                                       | Critical alarm: Critical power module failure, critical fan failure, voltage (power supply), voltage, thermal fault, and so forth |  |

|                |                               |              | Blink                                                                    | Non-critical failure: Redundant fan failure, redundant power failure, non-critical power and voltage, and so forth                |  |

|                |                               | Off          | Off                                                                      | AC Power off;                                                                                                                     |  |

|                |                               |              | Off                                                                      | Powered Down (DC-off state or S5), and no degraded, non-critical, critical conditions exist*                                      |  |

| t \A/ban tha c | orior is policered doller (to | onoitiono to | the DC off oto                                                           | oto or CE) the DMC is still an atandhy navyor and                                                                                 |  |

<sup>\*</sup> When the server is powered down (transitions to the DC-off state or S5), the BMC is still on standby power and retains the sensor and front panel status LED state established before the power-down event. If the system status is normal when the system is powered down (the LED is in a solid green state), the system status LED will be off.

**Figure 5. Front Panel Components**

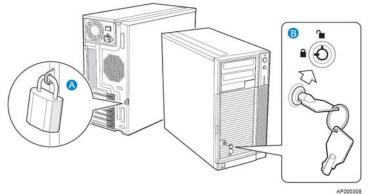

#### 2.1.2 Mechanical Locks

The Intel® Server System SC5650HCBRP chassis support the installation of a padlock loop (see letter "A" in the following figure) at the rear of the chassis. Additionally, the system ships with a two-position mechanical lock (see letter "B") on the front bezel assembly to prevent access to the hard drives and the interior of the system.

Figure 6. Mechanical Locks

#### 2.1.3 System Color

The Intel® Server System SC5650HCBRP chassis is offered in one color - Black (GE701).

#### 2.1.4 Rack and Cabinet Mouting Option

The Intel® Server System SC5650HCBRP supports a rack mount configuration. The rack mount kit includes the chassis slide rails, rack handle, rack orientation label, screws, and manual. This rack mount kit is designed to meet the EIA-310-D enclosure specification. General rack compatibility is further described in the *Server Rack Cabinet Compatibility Guide* found at <a href="http://support.intel.com">http://support.intel.com</a>.

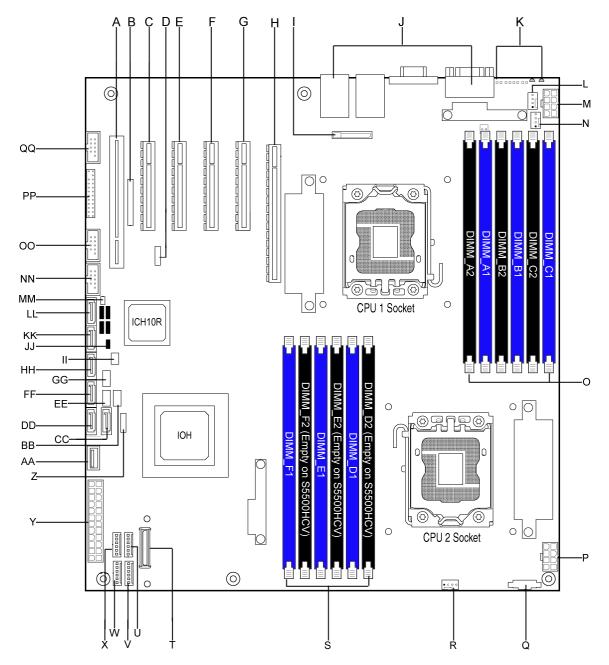

#### 2.1.5 Server Board Connector and Component Layout

The following figure shows the layout of the server board. Each connector and major component is identified by a number or letter, and a description is given below the figure.

| Callout | Description                                            | Callout | Description                 |

|---------|--------------------------------------------------------|---------|-----------------------------|

| Α       | Slot 1, 32-bit/33 MHz PCI, Keying for 5V and Universal | W       | System Fan 2 Header (6-pin) |

| В       | Intel® RMM3 Slot                                       | Х       | System Fan 1 Header (6-pin) |

| С       | Slot 2, PCI Express* x4 (x8 Mechanically)              | Υ       | Main Power Connector        |

| D       | Low-profile USB Solid State Drive Header               | Z       | LCP/IPMB Header             |

| Е       | Slot 3, PCI Express* Gen2 x8                           | AA      | Type A USB Port             |

| F       | Slot 4, PCI Express* Gen2 x8                           | BB      | SATA SGPIO Header           |

| G       | Slot 5, PCI Express* Gen2 x8                           | CC      | SATA Port 0                 |

| Н       | Slot 6, PCI Express* Gen2 x8 (x16 Mechanically)        | DD      | SATA Port 1                 |

| I       | Battery                                                | EE      | HSBP_B                      |

| Callout | Description                                                        | Callout | Description                                                              |

|---------|--------------------------------------------------------------------|---------|--------------------------------------------------------------------------|

| J       | Back Panel I/O Ports                                               | FF      | SATA Port 2                                                              |

| K       | Diagnostic and Identify LED's                                      | GG      | HSBP_A                                                                   |

| L       | System Fan 5 Header (4-pin)                                        | HH      | SATA Port 3                                                              |

| М       | Power Connector for Processor 1 and Memory attached to Processor 1 | II      | SATA Software RAID 5 Key Header                                          |

| N       | Processor 1 Fan Header (4-pin)                                     | JJ      | Chassis Intrusion Header                                                 |

| 0       | DIMM Sockets of Memory Channel A, B, and C                         | KK      | SATA Port 4                                                              |

| Р       | Power Connector for Processor 2 and Memory attached to Processor 2 | LL      | SATA Port 5                                                              |

| Q       | Auxiliary Power Signal Connector                                   | ММ      | HDD Activity LED Header (Connect to Add-in Card HDD Activity LED Header) |

| R       | Processor 2 Fan Header (4-pin)                                     | NN      | USB Connector (9-pin, for front panel USB ports)                         |

| S       | DIMM Sockets of Memory Channel D, E, and F                         | 00      | USB Connector (9-pin)                                                    |

| Т       | SAS Module Slot                                                    | PP      | Front Control Panel header                                               |

| U       | System Fan 3 Header (6-pin)                                        | QQ      | DH-10 Serial B header                                                    |

| V       | System Fan 4 Header (6-pin)                                        |         |                                                                          |

Figure 7. Major Board Components

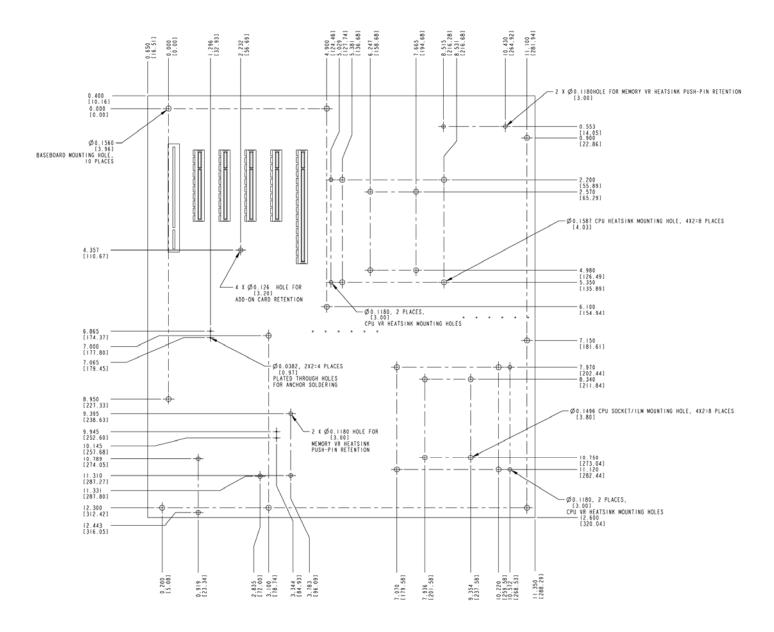

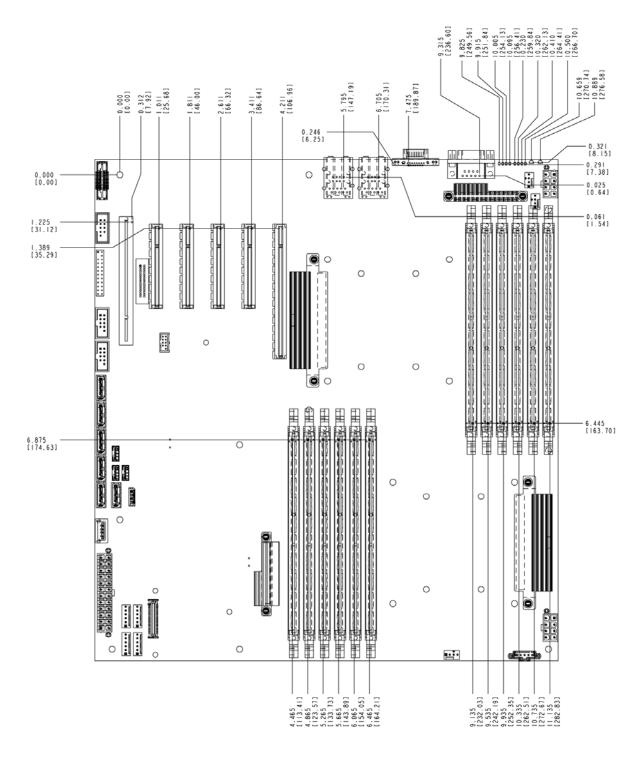

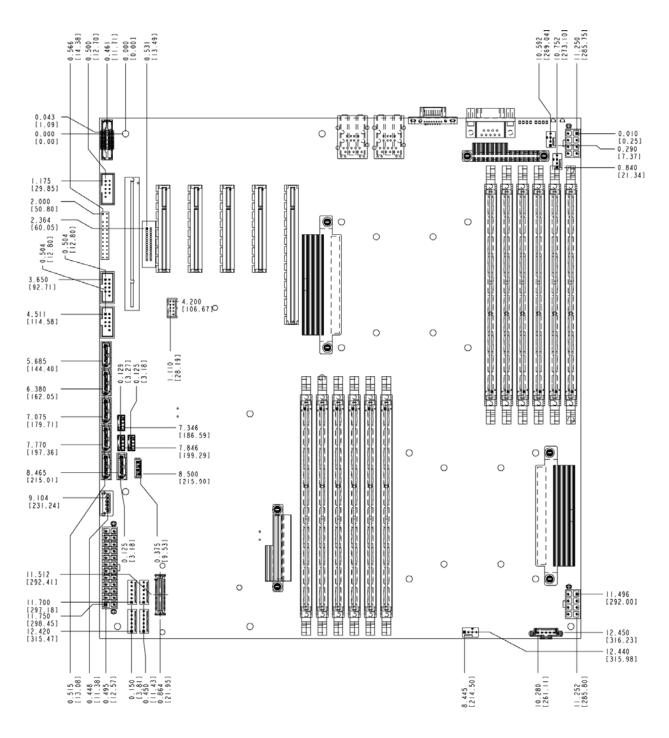

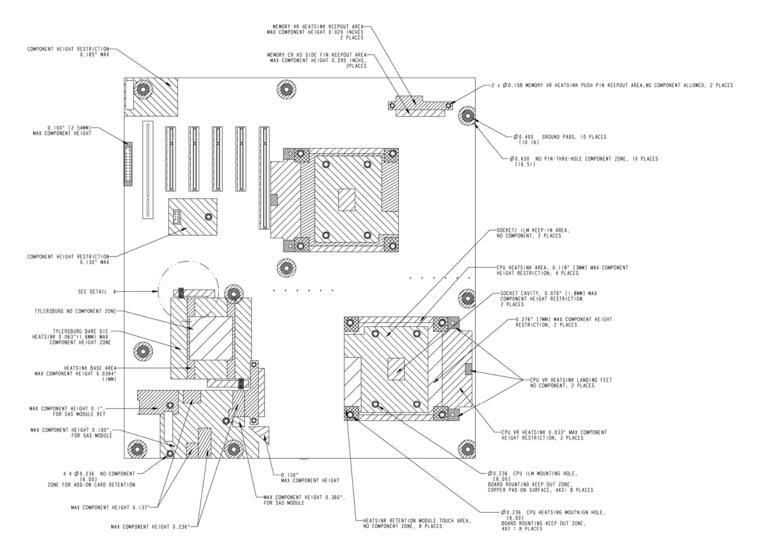

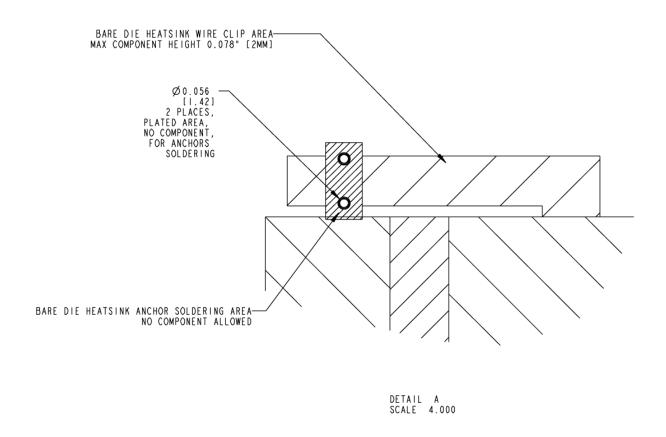

## 2.1.6 Server Board Mechanical Drawings

Figure 8. Mounting Hole Locations

Figure 9. Major Connector Pin-1 Locations (1 of 2)

Figure 10. Major Connector Pin-1 Locations (2 of 2)

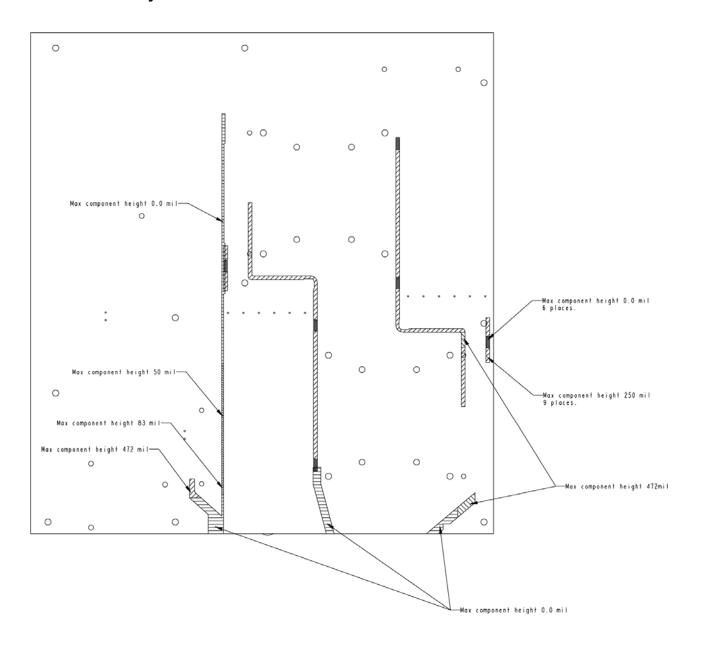

Figure 11. Primary Side Keep-out Zone (1 of 2)

Figure 12. Primary Side Keep-out Zone (2 of 2)

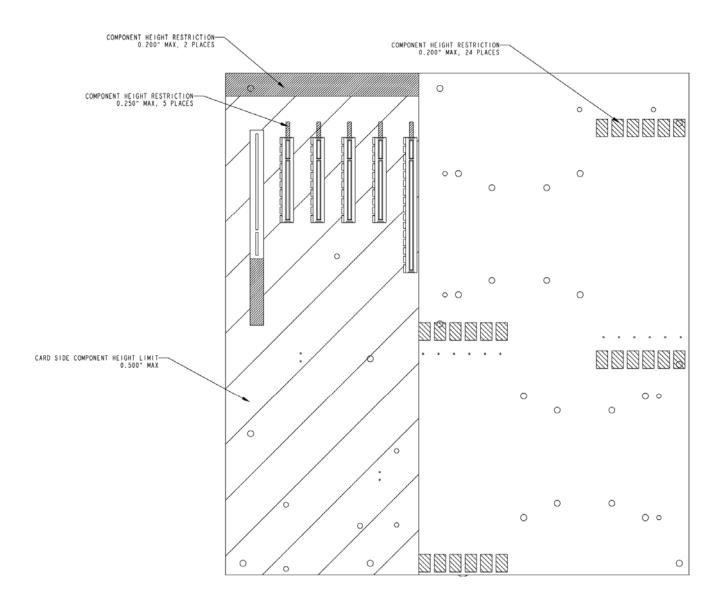

Figure 13. Primary Side Air Duct Keep-out Zone

Figure 14. Primary Side Card-Side Keep-out Zone

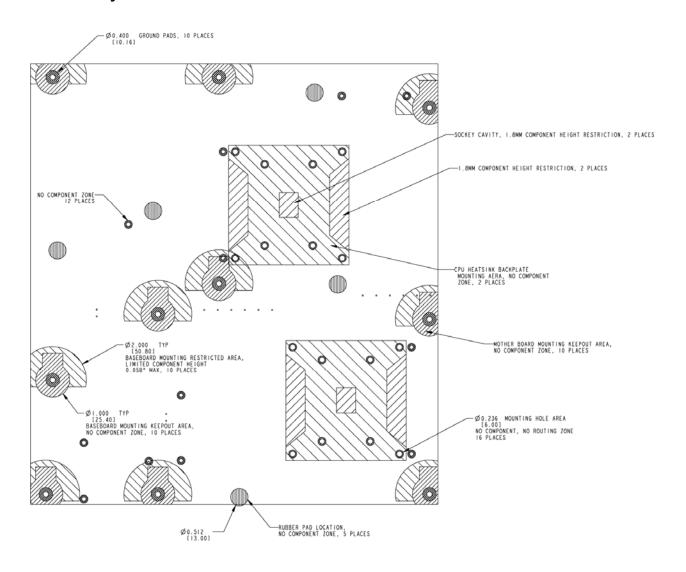

Figure 15. Second Side Keep-out Zone

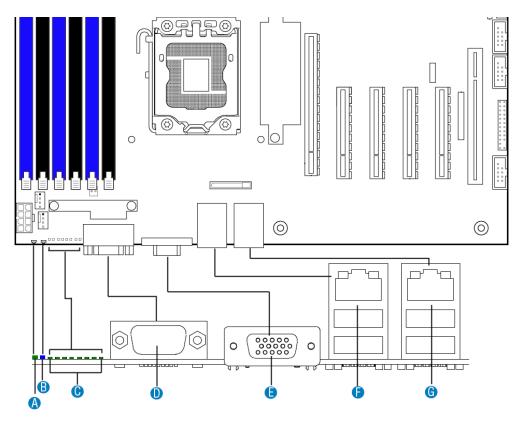

### 2.1.7 Rear I/O Layout

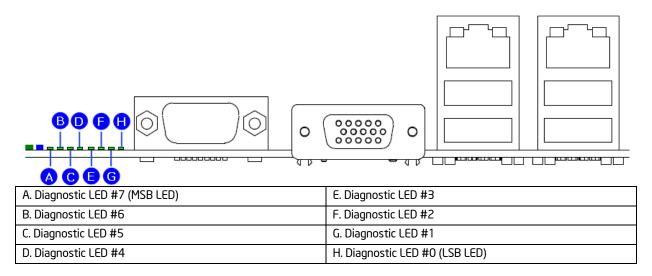

The following drawing shows the layout of the rear I/O components for the Intel $^{\$}$  Server System SC5650HCBRP.

| Callout | Description       | Callout | Description                                                             |

|---------|-------------------|---------|-------------------------------------------------------------------------|

| Α       | System Status LED | Е       | Video                                                                   |

| В       | ID LED            | F       | NIC Port 1 (1 Gb, Default Management Port) USB Port 2 (top), 3 (bottom) |

| С       | Diagnostics LED's | G       | NIC Port 2 (1 Gb) USB Port 0 (top), 1 (bottom)                          |

| D       | Serial Port A     |         |                                                                         |

Figure 16. Rear I/O Layout

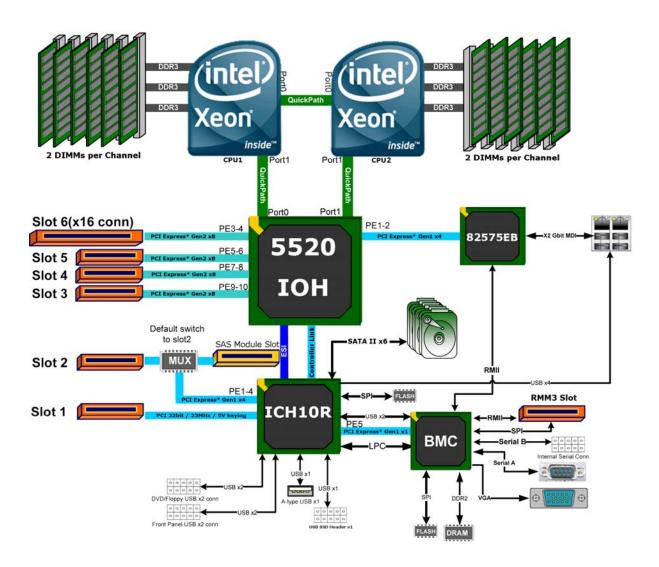

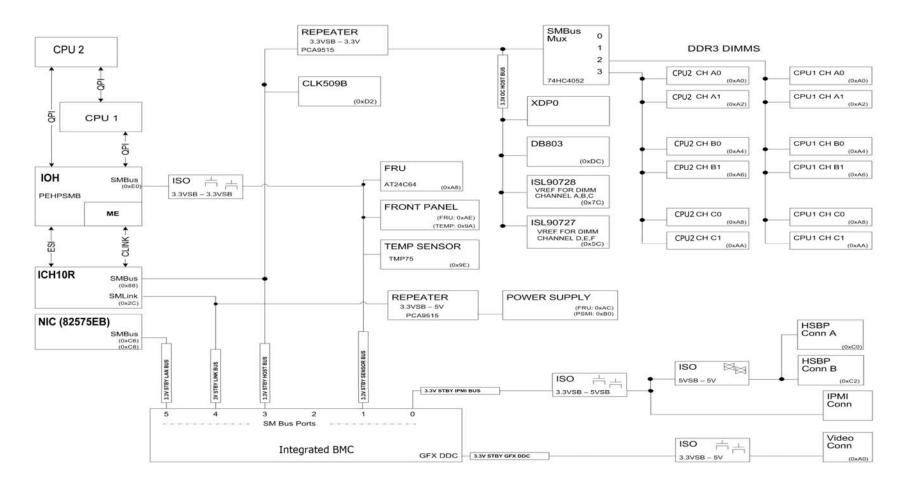

# 3. Functional Architecture

The architecture and design of the Intel® Server System SC5650HCBRP is based on the Intel® 5520 and ICH10R chipset. The chipset is designed for systems based on the Intel® Xeon® Processor 5500 Series and Intel® Xeon® Processor 5600 Series in an FC-LGA 1366 Socket B package with Intel® QuickPath Interconnect (Intel® QPI) speed at 6.40 GT/s, 5.86 GT/s, and 4.80 GT/s.

The chipset contains two main components:

- Intel<sup>®</sup> 5520 I/O Hub, which provides a connection point between various I/O components and the Intel<sup>®</sup> QuickPath Interconnect (Intel<sup>®</sup> QPI) based processors.

- Intel® ICH10 RAID (ICH10R) I/O controller hub for the I/O subsystem.

This chapter provides a high-level description of the functionality associated with each chipset component and the architectural blocks that make up the server boards.

Figure 17. Intel® Server System SC5650HCBRP Functional Block Diagram

# 3.1 Intel\* 5520 I/O Hub (IOH)

The Intel® 5520 I/O Hub (IOH) in the Intel® Server System SC5650HCBRP provides a connection point between various I/O components and Intel® QPI-based processors, which includes the following core platform functions:

- Intel<sup>®</sup> QPI link interface for the processor subsystem

- PCI Express\* Ports

- Enterprise South Bridge Interface (ESI) for connecting Intel<sup>®</sup> ICH10R

- Manageability Engine (ME)

- Controller Link (CL)

- SMBus Interface

- Intel<sup>®</sup> Virtualization Technology for Directed I/O (Intel<sup>®</sup> VT-d)

The following table shows the high-level features of the Intel® 5520 IOH:

Table 1. IOH High-Level Summary

| IOH SKU | Intel® QPI Ports | Supported Processor                | PCI Express*<br>Lanes | Manageability                                        |

|---------|------------------|------------------------------------|-----------------------|------------------------------------------------------|

| 5520    | 2                | Intel® Xeon® Processor 5500 Series | 36                    | Intel <sup>®</sup> Intelligent Power Node<br>Manager |

#### 3.1.1 Intel® QuickPath Interconnect

The Intel® Server System SC5650HCBRP provides two full-width, cache-coherent, link-based Intel® QuickPath Interconnect interfaces from Intel® 5520 IOH for connecting Intel® QPI based processors. The two Intel® QPI link interfaces support full-width communication only and have the following main features:

- Packetized protocol with 18 data/protocol bits and 2 CRC bits per link per direction

- Supporting 4.8 GT/s, 5.86 GT/s, and 6.4 GT/s

- Fully-coherent write cache with inbound write combining

- Read Current command support

- Support for 64-byte cache line size

#### 3.1.2 PCI Express\* Ports

The Intel® 5520 IOH is capable of interfacing with up to 36 PCI Express\* Gen2 lanes, which support devices with the following link width: x16, x8, x4, x2, and x1.

All ports support PCI Express\* Gen1 and Gen2 transfer rates.

For a detailed PCI Express\* Slots definition in the Intel® Server System SC5650HCBRP, see "3.5 PCI Subsystem."

### 3.1.3 Enterprise South Bridge Interface (ESI)