# Intel<sup>®</sup> Server System SR2625UR

Technical Product Specification

Intel order number E46130-010

Revision 1.8

May, 2011

(intel) Xeon<sup>\*</sup>

**Enterprise Platforms and Services Division - Marketing**

# Revision History

| Date          | Revision<br>Number | Modifications                                                               |

|---------------|--------------------|-----------------------------------------------------------------------------|

| March 2009    | 1.0                | Initial release.                                                            |

| October 2009  | 1.1                | Updated section - 7.3 Control Panel Connectors.                             |

| January 2010  | 1.2                | <ul> <li>Added security feature for SR2625URLXT.</li> </ul>                 |

|               |                    | <ul> <li>Update section 2.6 - NIC Connectors.</li> </ul>                    |

|               |                    | <ul> <li>Added section 2.9 - Trusted Platform Module.</li> </ul>            |

|               |                    | <ul> <li>Updated section 6.4.2 - Intel<sup>®</sup> IT/IR RAID.</li> </ul>   |

| March 2010    | 1.3                | Updated section 2.1.1 - Processor Support.                                  |

| April 2010    | 1.4                | <ul> <li>Updated section 2.6 - System Board Overview.</li> </ul>            |

|               |                    | <ul> <li>Removed CCC Certification.</li> </ul>                              |

| July 2010     | 1.5                | Updated section 2 - Product Overview.                                       |

| December 2010 | 1.6                | <ul> <li>Updated section 5.1 - Midplane.</li> </ul>                         |

|               |                    | <ul> <li>Removed section 4.5 - Memory Slot Population.</li> </ul>           |

|               | 1.7                | Updated section 2 - Product Overview.                                       |

| May 2011      | 1.8                | Updated section 2- Product Overview.                                        |

|               |                    | <ul> <li>Added section 3.11- Cold Redundant Power Supply Module.</li> </ul> |

## Disclaimers

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel<sup>®</sup>'s Terms and Conditions of Sale for such products, Intel<sup>®</sup> assumes no liability whatsoever, and Intel<sup>®</sup> disclaims any express or implied warranty, relating to sale and/or use of Intel<sup>®</sup> products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel<sup>®</sup> products are not intended for use in medical, life saving, or life sustaining applications. Intel<sup>®</sup> may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel<sup>®</sup> reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> Server System SR2625UR may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the license. The information in this manual is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2008-2011.

# **Table of Contents**

| 1. | Introduc | ction                                                         | 1  |

|----|----------|---------------------------------------------------------------|----|

|    | 1.1      | Chapter Outline                                               | 1  |

|    | 1.2      | Server Board Use Disclaimer                                   | 2  |

| 2. | Product  | : Overview                                                    | 3  |

|    | 2.1.1    | Processor Support                                             | 5  |

|    | 2.2      | System Overview                                               | 7  |

|    | 2.3      | System Dimensions                                             | 7  |

|    | 2.4      | System Components                                             | 8  |

|    | 2.5      | Hard Drive and Peripheral Bays                                | 9  |

|    | 2.6      | System Board Overview                                         | 10 |

|    | 2.7      | Front Bezel Features                                          | 14 |

|    | 2.8      | Rack and Cabinet Mounting Options                             | 15 |

|    | 2.9      | Trusted Platform Module (TPM) – Supported only on SR2625URLXT | 15 |

|    | 2.9.1    | Overview                                                      | 15 |

|    | 2.9.2    | TPM security BIOS                                             | 16 |

| 3. | Power S  | Subsystem                                                     | 19 |

|    | 3.1      | Mechanical Overview                                           | 19 |

|    | 3.2      | Single Power Supply Module Population                         | 21 |

|    | 3.3      | Handle and Retention Mechanism                                | 21 |

|    | 3.4      | Hot-swap Support                                              | 21 |

|    | 3.5      | Airflow                                                       | 22 |

|    | 3.6      | AC Power Cord Specification Requirements                      | 22 |

|    | 3.7      | Output Cable Harness                                          | 22 |

|    | 3.7.1    | P1 – Server Board Power Connector                             | 23 |

|    | 3.7.2    | P2 – Processor Power Connector                                | 23 |

|    | 3.7.3    | P3 – Power Signal Connector                                   | 24 |

|    | 3.7.4    | P4 – Backplane Power Connector                                | 24 |

|    | 3.7.5    | P5 – Midplane Power Connector                                 | 24 |

|    | 3.8      | AC Input Requirements                                         | 25 |

|    | 3.8.1    | Efficiency                                                    | 25 |

|    | 3.8.2    | AC Input Voltage Specification                                | 25 |

|    | 3.8.3   | AC Line Dropout/Holdup                    | 26 |

|----|---------|-------------------------------------------|----|

|    | 3.8.4   | AC Line 5 VSB Holdup                      | 26 |

|    | 3.8.5   | AC Inrush                                 | 26 |

| 3  | .9      | Protection Circuits                       | 26 |

|    | 3.9.1   | Over-current Protection (OCP)             | 26 |

|    | 3.9.2   | Over-voltage Protection (OVP)             | 27 |

|    | 3.9.3   | Over-temperature Protection (OTP)         | 27 |

| 3  | .10     | DC Output Specification                   | 28 |

|    | 3.10.1  | Output Power/Currents                     | 28 |

|    | 3.10.2  | Standby Output/Standby Mode               | 28 |

| 3  | .11     | Cold Redundant Power Supply Module        | 28 |

|    | 3.11.1  | Overview                                  | 28 |

|    | 3.11.2  | Signals                                   | 29 |

|    | 3.11.3  | Cold Redundancy Enabling / Disabling      | 30 |

|    | 3.11.4  | System Power on timing                    | 30 |

|    | 3.11.5  | Power supply fan(s)                       | 30 |

|    | 3.11.6  | Failure Detection and Protection          | 30 |

|    | 3.11.7  | Power Supply Control based on output load | 31 |

|    | 3.11.8  | Backward Compatibility                    | 31 |

| 3  | .12     | Power Supply Status LED                   | 32 |

| 4. | Cooling | Subsystem                                 | 33 |

| 4  | .1      | Non-redundant Fan Module                  | 34 |

| 4  | .2      | Redundant System Fan Module               | 38 |

| 4  | .3      | Airflow Support                           | 40 |

|    | 4.3.1   | Power Supply Zone                         | 40 |

|    | 4.3.2   | Full-height Riser Zone                    | 40 |

|    | 4.3.3   | CPU/Memory/Low-profile PCI Zone           | 41 |

| 4  | .4      | Drive Bay Population                      | 41 |

| 4  | .5      | Sata HDD Support                          | 42 |

| 5. | System  | Board Interconnects                       | 43 |

| 5  | .1      | Midplane                                  | 43 |

| 5  | .2      | Bridge Board                              | 50 |

| 5  | .3      | Hot-swap SAS/SATA Backplane               | 50 |

| 6. | Periphe | ral and Hard Drive Subsystem              | 57 |

| 6.1                     | Slimline Drive Bay                                     | 57 |

|-------------------------|--------------------------------------------------------|----|

| 6.2                     | Hard Drive Bays                                        | 58 |

| 6.2.1                   | Hot-swap Drive Carriers                                |    |

| 6.3                     | Optional Tape Drive or Additional Hard Drives Flex Bay | 60 |

| 6.4                     | Midplane Options                                       | 61 |

| 6.4.1                   | Passive Midplane                                       | 61 |

| 6.4.2                   | Active Midplane with SAS/SAS RAID Support              | 62 |

| 6.5                     | Hot-swap SAS/SATA Backplane                            | 64 |

| 6.5.1                   | SAS/SATA Backplane Layout                              | 65 |

| 6.5.2                   | SAS/SATA Backplane Functional Architecture             | 67 |

| 6.6                     | Enclosure Management Cabling for Passive Midplane      | 68 |

| 7. Standa               | ard Control Panel                                      | 69 |

| 7.1                     | Control Panel Buttons                                  | 69 |

| 7.2                     | Control Panel LED Indicators                           | 70 |

| 7.2.1                   | Power/Sleep LED                                        | 72 |

| 7.2.2                   | System Status LED                                      | 72 |

| 7.2.3                   | Drive Activity LED                                     | 73 |

| 7.2.4                   | System Identification LED                              | 73 |

| 7.3                     | Control Panel Connectors                               | 74 |

| 7.4                     | Internal Control Panel Interconnect                    | 75 |

| 8. Intel <sup>®</sup> I | Local Control Panel                                    | 77 |

| 8.1                     | LED Functionality                                      |    |

| 8.1.1                   | Power/Sleep LED                                        | 79 |

| 8.1.2                   | System Status LED                                      | 79 |

| 8.1.3                   | Drive Activity LED                                     |    |

| 8.1.4                   | System Identification LED                              | 80 |

| 8.2                     | Intel <sup>®</sup> Local Control Panel Interconnects   |    |

| 9. PCI Ri               | ser Cards and Assembly                                 | 82 |

| 9.1                     | Riser Card Options                                     | 83 |

| 9.2                     | PCI Riser Card Mechanical Drawings                     | 84 |

| 10. Enviro              | onmental Specifications                                | 88 |

| 10.1                    | System Level Environmental Limits                      |    |

| 10.2                    | Serviceability and Availability                        |    |

| 10.3                    | Replacing the Backup Battery                           |    |

| 11. Regulat | ory and Certification Information           | 90  |

|-------------|---------------------------------------------|-----|

| 11.1        | Product Regulatory Compliance               | 90  |

| 11.1.1      | Product Safety Compliance                   | 90  |

| 11.1.2      | Product EMC Compliance – Class A Compliance | 91  |

| 11.1.3      | Product Ecology Compliance                  | 91  |

| 11.1.4      | Certifications/Registrations/Declarations   | 92  |

| 11.2        | Product Regulatory Compliance Markings      | 92  |

| 11.3        | Rack Mount Installation Guidelines          | 94  |

| 11.4        | Power Cord Usage Guidelines                 | 96  |

| 11.5        | Electromagnetic Compatibility Notices       | 96  |

| 11.5.1      | FCC Verification Statement (USA)            | 96  |

| 11.5.2      | ICES-003 (Canada)                           | 97  |

| 11.5.3      | Europe (CE Declaration of Conformity)       | 97  |

| 11.5.4      | VCCI (Japan)                                | 97  |

| 11.5.5      | BSMI (Taiwan)                               | 98  |

| 11.5.6      | KCC (Korea)                                 | 98  |

| 11.6        | Regulated Specified Components              | 99  |

| Appendix A  | : Integration and Usage Tips                | 100 |

| Appendix B  | : POST Code Diagnostic LED Decoder          | 101 |

| Appendix C  | : POST Code Errors                          | 106 |

| Glossary    |                                             | 111 |

| Reference D | Documents                                   | 113 |

# List of Figures

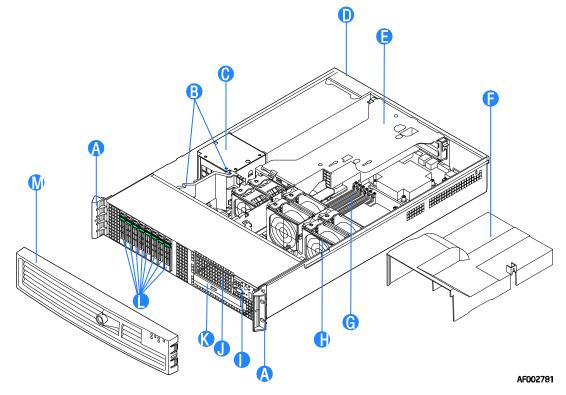

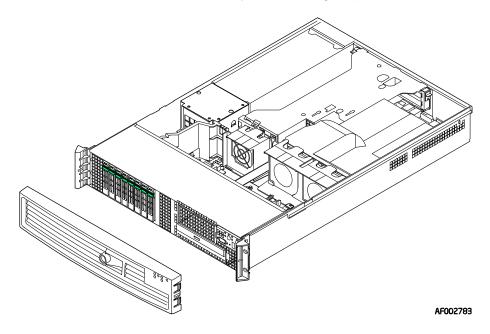

| Figure 1. Top Down View – Passive System SKU (SR2625URBRP) Shown              | 7  |

|-------------------------------------------------------------------------------|----|

| Figure 2. Major System Components                                             | 8  |

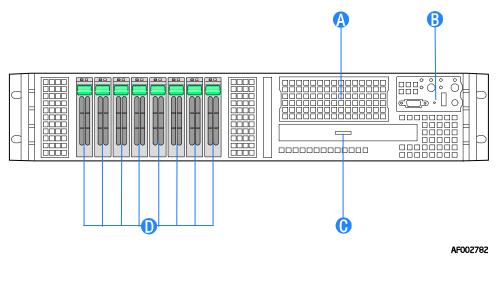

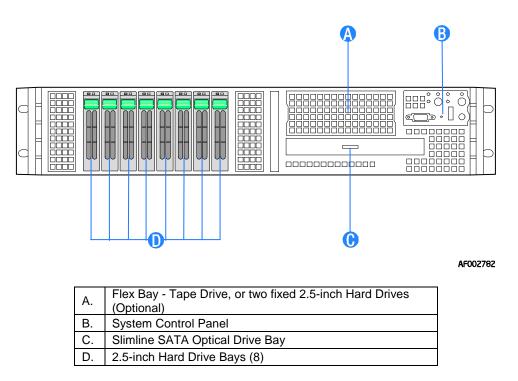

| Figure 3. Front Panel Feature Overview                                        | 9  |

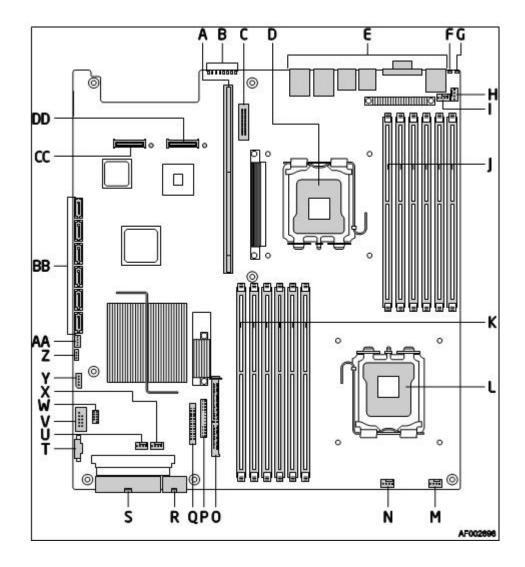

| Figure 4. Intel <sup>®</sup> Server Board S5520UR                             | 10 |

| Figure 5. Intel <sup>®</sup> Server Board S5520UR Components                  | 11 |

| Figure 6. Back Panel Feature Overview                                         | 12 |

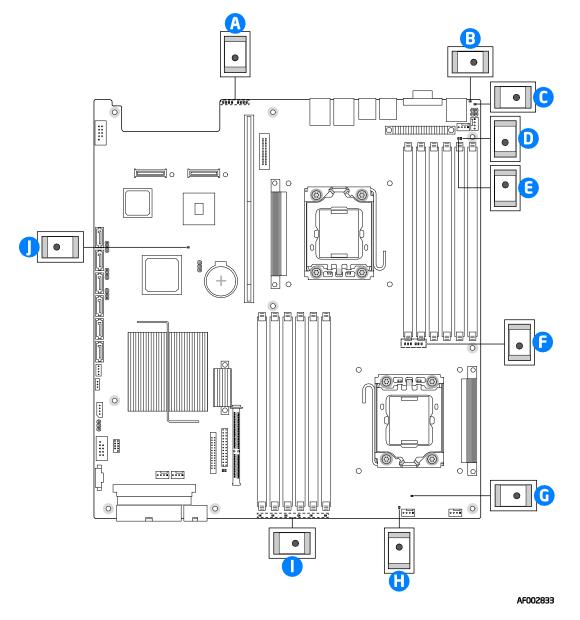

| Figure 7. Intel <sup>®</sup> Light-Guided Diagnostic LEDs - Server Board      | 13 |

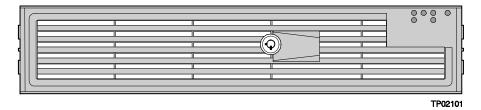

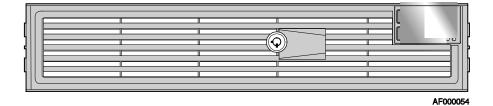

| Figure 8. Optional Front Bezel                                                | 14 |

| Figure 9. Front Bezel Supporting Standard Control Panel                       | 14 |

| Figure 10. Front Bezel Supporting Intel <sup>®</sup> Local Control Panel      | 15 |

| Figure 11. Setup Utility – TPM Configuration Screen                           | 17 |

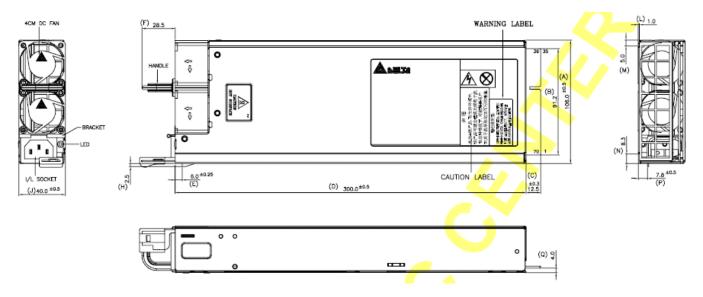

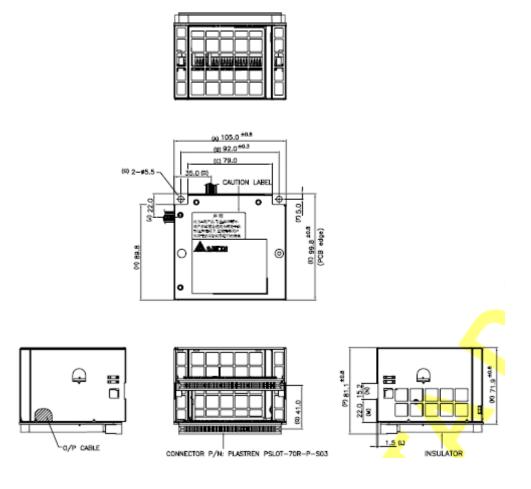

| Figure 12. Mechanical Drawing for Power Supply Module                         | 19 |

| Figure 13. Mechanical Drawing for Power Distribution Module                   | 20 |

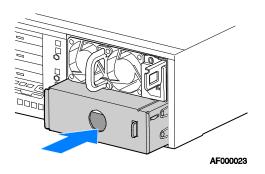

| Figure 14. Power Supply Blank                                                 | 21 |

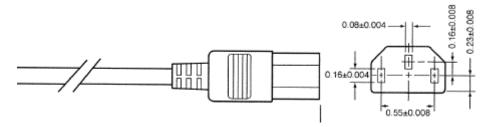

| Figure 15. AC Power Cord                                                      | 22 |

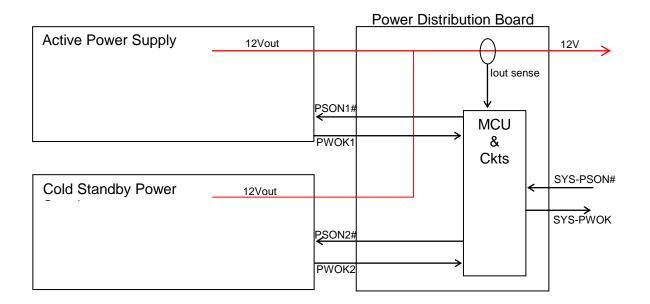

| Figure 16. Cold Redundant Power Supply Module                                 | 29 |

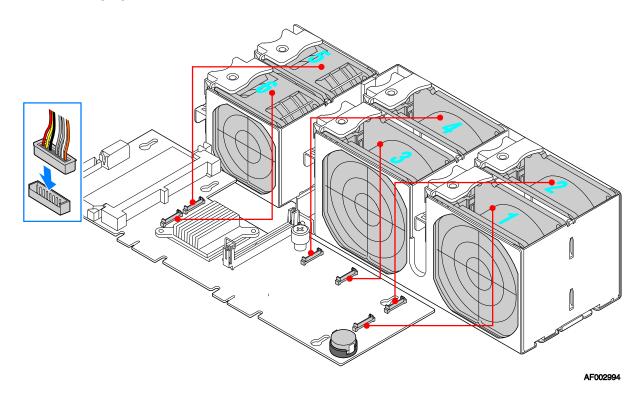

| Figure 17. Non-redundant Fan Module                                           | 34 |

| Figure 18. Non-redundant Fan Header Assignments on Midplane                   | 37 |

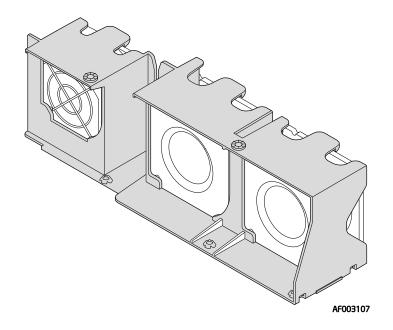

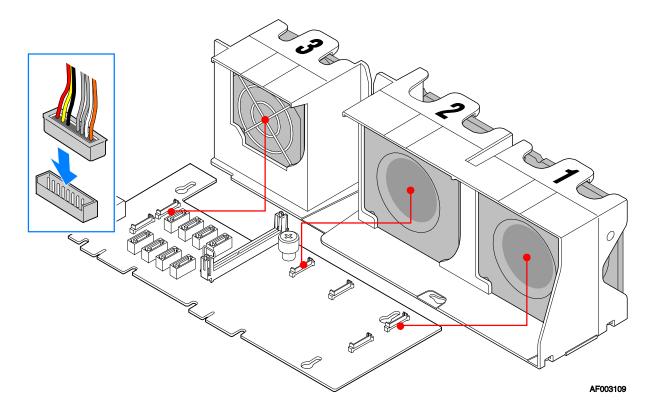

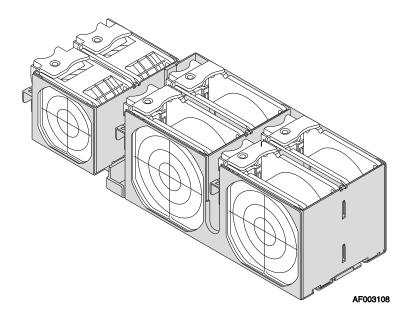

| Figure 19. Fan Module Assembly                                                | 38 |

| Figure 20. Redundant Fan Header Assignments on Midplane                       | 39 |

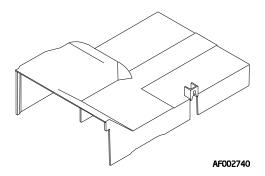

| Figure 21. CPU Air Duct with Air Baffle                                       | 41 |

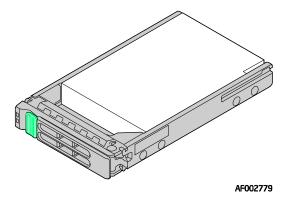

| Figure 22. 2.5-inch Drive Carrier with a Blank                                | 41 |

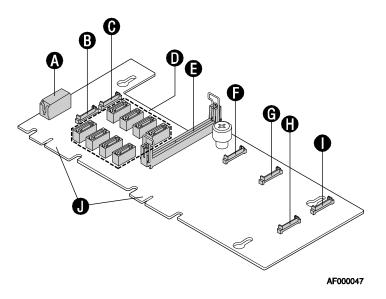

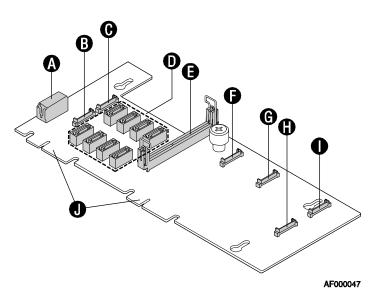

| Figure 23. Passive Midplane Board                                             | 43 |

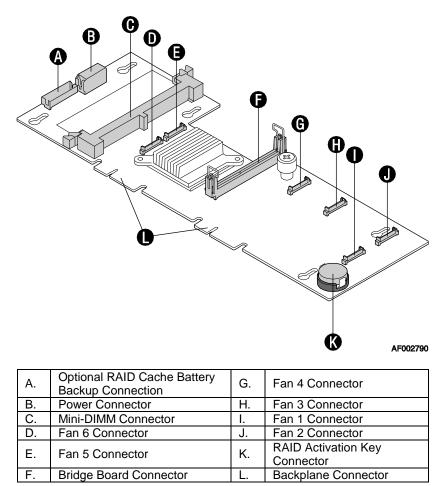

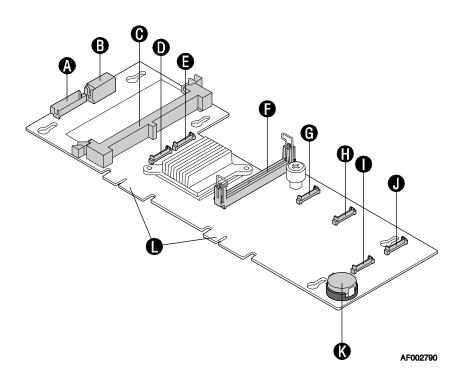

| Figure 24. Active SAS/SAS RAID Midplane Board                                 | 44 |

| Figure 25. Bridge Board                                                       | 50 |

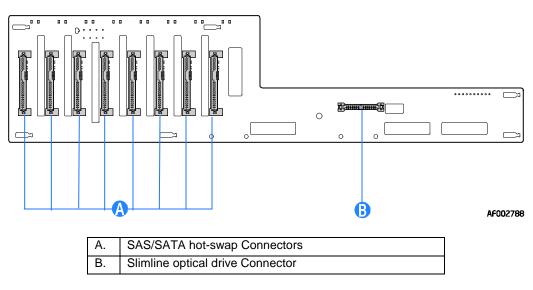

| Figure 26. 2.5-inch Hot-swap SAS/SATA Backplane (Front Side View)             | 50 |

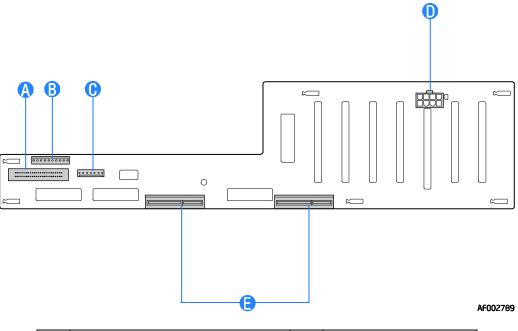

| Figure 27. 2.5-inch Hot-swap SAS/SATA Backplane (Back Side View)              | 51 |

| Figure 28. Flex bay for 3.5-inch Tape Drive or Two 2.5-inch HDDs (Front View) | 57 |

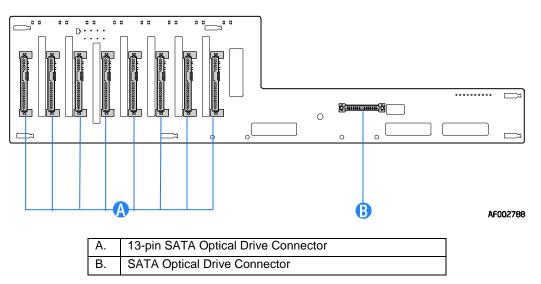

| Figure 29. Slimline Optical Drive Assembly for 2.5-inch drive System          | 58 |

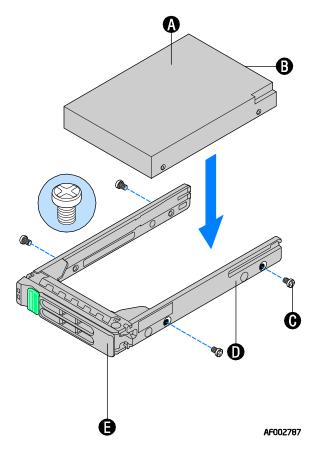

| Figure 30. 2.5-inch Hard Drive Tray Assembly                                  | 59 |

| Figure 31. Flex Bay                                                           | 60 |

| Figure 32. Optional Tape Drive (Front View)                              | 60  |

|--------------------------------------------------------------------------|-----|

| Figure 33. Passive Midplane Board                                        | 61  |

| Figure 34. Active Midplane with SAS/SAS RAID Support                     | 62  |

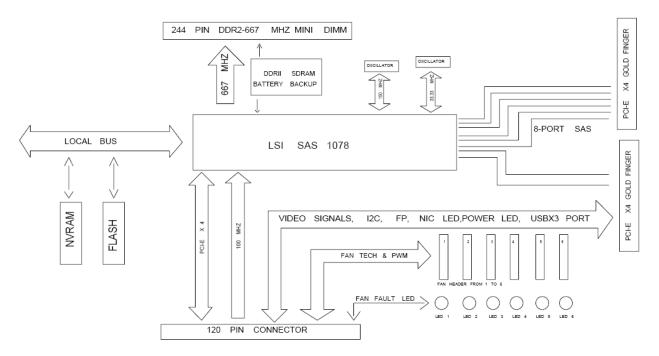

| Figure 35. Architecture Overview                                         | 63  |

| Figure 36. Hot-swap SAS/SATA Backplane (Front Side View)                 | 65  |

| Figure 37. Hot-swap SAS/SATA Backplane (Back Side View)                  | 66  |

| Figure 38. SAS/SATA Backplane Functional Block Diagram                   | 67  |

| Figure 39. Standard Control Panel Assembly Module                        | 69  |

| Figure 40. Control Panel Buttons                                         | 70  |

| Figure 41. Control Panel LEDs                                            | 71  |

| Figure 42. Standard Control Panel PCB                                    | 75  |

| Figure 43. Intel <sup>®</sup> Local Control Panel Assembly Module        | 77  |

| Figure 44. Intel <sup>®</sup> Local Control Panel Overview               | 77  |

| Figure 45. 2U Riser Assembly                                             | 82  |

| Figure 46. 2U PCI Express* Passive Riser                                 | 83  |

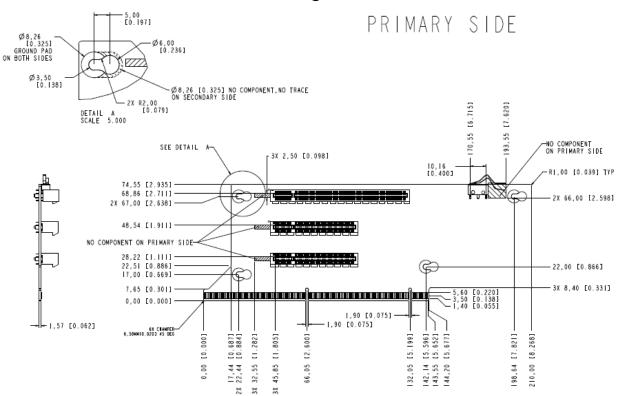

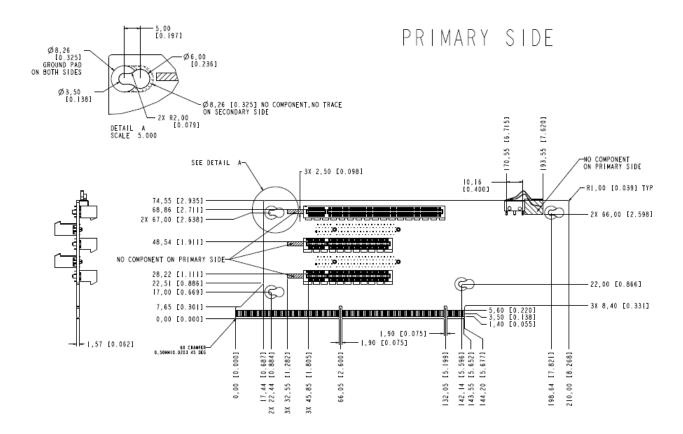

| Figure 47. 2U PCI Express* Passive Riser – Primary Side                  | 84  |

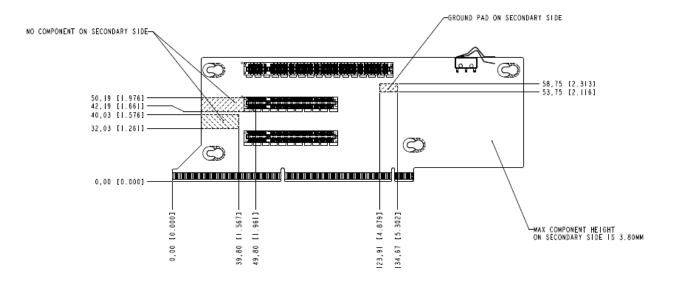

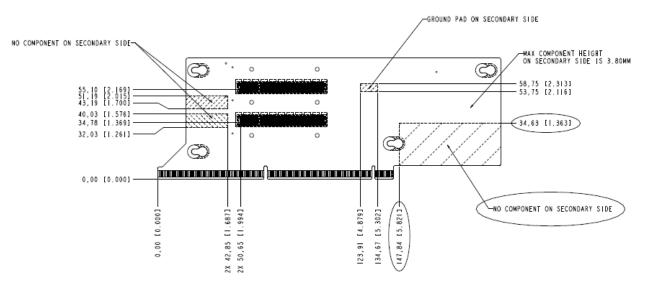

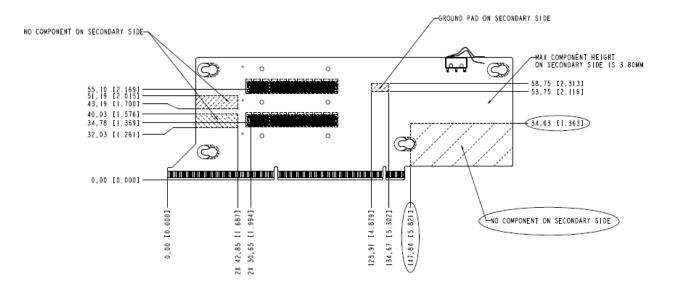

| Figure 48. 2U PCI Express* Passive Riser – Secondary Side                | 85  |

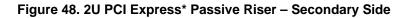

| Figure 49. 2U Butterfly PCI-X/PCI Express* Active Riser – Primary Side   | 85  |

| Figure 50. 2U Butterfly PCI-X/PCI Express* Active Riser – Secondary Side | 86  |

| Figure 51. 2U Butterfly PCI Express* Active Riser – Primary Side         | 86  |

| Figure 52. 2U Butterfly PCI Express* Active Riser – Secondary Side       | 87  |

| Figure 53. Diagnostic LED Placement Diagram                              | 101 |

|                                                                          |     |

# List of Tables

| Table 1. System Feature Set                                               | 3  |

|---------------------------------------------------------------------------|----|

| Table 2. Mixed Processor Configurations                                   | 6  |

| Table 3. System Dimensions                                                | 7  |

| Table 4. Drive Overview                                                   |    |

| Table 5. Major Board Components                                           | 12 |

| Table 6. TSetup Utility – Security Configuration Screen Fields            | 18 |

| Table 7. AC Power Cord Specifications                                     | 22 |

| Table 8. Power Harness Cable Definitions                                  | 22 |

| Table 9. P1 Main Power Connector                                          | 23 |

| Table 10. P2 Processor Power Connector                                    | 23 |

| Table 11. P3 Power Signal Connector                                       | 24 |

| Table 12. P4 Backplane Power Connector                                    | 24 |

| Table 13. P5 Midplane Power Connector                                     | 24 |

| Table 14. Efficiency                                                      | 25 |

| Table 15. AC Input Rating                                                 | 25 |

| Table 16. Over-current Protection Limits/240 VA Protection                | 27 |

| Table 17. Over-voltage Protection (OVP) Limits                            | 27 |

| Table 18. Output Power and Current Ratings                                | 28 |

| Table 19. LED Indicators                                                  | 32 |

| Table 20. Non-redundant Cooling Zones                                     | 34 |

| Table 21. Non-redundant Fan Connector Pin Assingment                      | 36 |

| Table 22. Non-redundant Fan Header Assignment                             | 37 |

| Table 23. Redundant Cooling Zones                                         | 38 |

| Table 24. Redundant Fan Connector Pin Assingment                          | 39 |

| Table 25. Redundant Fan Header Assignment                                 | 40 |

| Table 26. 120-pin Server Board-to-Midplane Bridge Board Connector Pin-out | 44 |

| Table 27. Midplane Fan Header Pin-outs                                    | 46 |

| Table 28. Midplane Power Connector Pin-out                                | 46 |

| Table 29. Midplane-to-Backplane Card Edge Connector #1 Pin-out            | 47 |

| Table 30. Midplane-to-Backplane Card Edge Connector #2 Pin-out            | 47 |

| Table 31. Active Midplane SAS RAID Battery Backup Connector Pin-out       | 49 |

| Table 32. Passive Midplane SATA/SAS Connector Pin-outs                                            | 49   |

|---------------------------------------------------------------------------------------------------|------|

| Table 33. 2x4 SAS/SATA Backplane Power Connector Pin-out (J8L1)                                   | 51   |

| Table 34. 1x7 Tape Drive Option Power Connector Pin-out (J2N2)                                    | 51   |

| Table 35. Slimline Optical Drive Slot Connector (J6C1)                                            | 52   |

| Table 36. I <sup>2</sup> C Connector (J2M2) (located on the back side of the backplane)           | 52   |

| Table 37. PCI Express* X4 Slot Connector from Midplane (J4N1)                                     | 53   |

| Table 38. PCI Express* X4 Slot Connector from Midplane (J6N1)                                     | 54   |

| Table 39. Control Panel Connector (J2N1)                                                          | 55   |

| Table 40. SAS/SATA Hard Drive Connector Pin-outs (J1B1, J2B1, J1B2, J2B2, J3B1, J4B1, J3B2, J4B2) |      |

| Table 41. Hard Drive LED Function Definitions                                                     | 68   |

| Table 42. Hard Drive Activity LED Functionality                                                   | 68   |

| Table 43. Control Button and Intrusion Switch Functions                                           | 70   |

| Table 44. Control Panel LED Functions                                                             | 71   |

| Table 45. SSI Power LED Operation                                                                 | 72   |

| Table 46. Control Panel LED Operation                                                             | 72   |

| Table 47. External USB Connectors (J2D1)                                                          | 74   |

| Table 48. Video Connector (J1D1)                                                                  | 74   |

| Table 49. 50-pin Control Panel Connector (J2B1)                                                   | 76   |

| Table 50. Control Panel LED Functions                                                             | 78   |

| Table 51. SSI Power LED Operation                                                                 | 79   |

| Table 52. Control Panel LED Operation                                                             | 79   |

| Table 53. 50-pin Control Panel Connector                                                          | 81   |

| Table 54. Internal USB Header                                                                     | 81   |

| Table 55. Riser Card Options                                                                      | 83   |

| Table 56. System Environmental Limits Summary                                                     | 88   |

| Table 57. Time Estimate for System Maintenance Procedures                                         | 88   |

| Table 58. POST Progress Code LED Example                                                          | .101 |

| Table 59. Diagnostic LED POST Code Decoder                                                        | .102 |

| Table 60. POST Error Messages and Handling                                                        | .106 |

| Table 61. POST Error Beep Codes                                                                   | .109 |

| Table 62. Integrated BMC Beep Codes                                                               | .109 |

<This page is intentionally left blank.>

# 1. Introduction

This Technical Product Specification (TPS) provides system-specific information detailing the features, functionality, and high-level architecture of the *Intel®* Server System SR2625UR. The *Intel®* Server Board S5520UR, S5520URT Technical Product Specification should also be referenced to obtain greater detail of functionality and architecture specific to the integrated server board, which are also supported on this server system.

In addition, design-level information for specific subsystems can be obtained by ordering the External Product Specifications (EPS) or External Design Specifications (EDS) for a given subsystem. EPS and EDS documents are not publicly available. They are only made available under NDA with Intel<sup>®</sup> and must be ordered through your local Intel<sup>®</sup> representative.

The Intel<sup>®</sup> Server System SR2625UR may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Refer to the Intel<sup>®</sup> Server Board S5520UR/S5520URT/Intel<sup>®</sup> Server System SR2625UR Specification Update for published errata.

## 1.1 Chapter Outline

This document is divided into the following chapters:

- Chapter 1 Introduction

- Chapter 2 Product Overview

- Chapter 3 Power Subsystem

- Chapter 4 Cooling Subsystem

- Chapter 5 System Board Interconnects

- Chapter 6 Peripheral and Hard Drive Support

- Chapter 7 Standard Control Panel

- Chapter 8 Intel<sup>®</sup> Local Control Panel

- Chapter 9 PCI Riser Cards and Assembly

- Chapter 10 Environmental Specifications

- Chapter 11 Regulatory and Certification Information

- Appendix A Integration and Usage Tips

- Appendix B POST Code Diagnostic LED Decoder

- Appendix C Post Code Errors

- Glossary

- Reference Documents

## 1.2 Server Board Use Disclaimer

Intel Corporation server boards support add-in peripherals and contain a number of highdensity VLSI and power delivery components that need adequate airflow to cool. Intel<sup>®</sup> ensures through its own system development and testing that when Intel<sup>®</sup> server building blocks are used together, the fully integrated system will meet the intended thermal requirements of these components. It is the responsibility of the system integrator who chooses not to use Intel<sup>®</sup>developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of air flow required for their specific application and environmental conditions. Intel Corporation cannot be held responsible if components fail or the server board does not operate correctly when used outside any of their published operating or non-operating limits.

# 2. Product Overview

The Intel<sup>®</sup> Server System SR2625 is a 2U server system that is designed to support the Intel<sup>®</sup> Server Board S5520UR/S5520URT. The server board and the system have features that are designed to support the high-density server market. The system is integrated with an Intel<sup>®</sup> Server Board S5520UR and is offered in two different system configurations:

- Configuration 1: System integrated with an active SAS/SATA midplane, a redundant fan module, and a 5-slot PCI Express\* riser (SR2625URLX, SR2625URLXT)

- Configuration 2: System integrated with a passive midplane, a non-redundant fan module, and a 3-slot PCI Express\* riser (SR2625URBRP).

This chapter provides a high-level overview of the system features. Greater detail for each major system component or feature is provided in the following chapters.

| Feature               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Peripheral Interfaces | <ul> <li>External connections:</li> <li>DB-15 video connector (back)</li> <li>RJ-45 serial Port A connector</li> <li>Two RJ-45 10/100/1000 Mb network connections</li> <li>Four USB 2.0 connectors (back)</li> <li>One USB 1.1 connector (front)</li> <li>Internal connections:</li> <li>One USB 2x5 pin header, which supports two USB 2.0 ports</li> <li>One low-profile USB 2x5 pin header to support low-profile USB Solid State</li> </ul>                          |

|                       | <ul> <li>drives</li> <li>One DH-10 Serial Port B header</li> <li>Six Serial ATA (SATA) II connectors</li> <li>Two I/O module connectors</li> <li>One RMM3/GCM4 connector to support optional Intel<sup>®</sup> Remote Management Module 3</li> <li>SATA Software 5 Activation Key connector</li> <li>One SSI-EEB compliant front panel header</li> <li>One SSI-EEB compliant 24-pin main power connector</li> <li>One SSI-compliant 8-pin CPU power connector</li> </ul> |

| Video                 | <ul> <li>One SSI-compliant auxiliary power connector</li> <li>On-board ServerEngines* LLC Pilot II Controller</li> <li>Integrated 2D Video Controller</li> </ul>                                                                                                                                                                                                                                                                                                         |

| LAN                   | <ul> <li>64 MB DDR2 Memory</li> <li>Two 10/100/1000 Intel<sup>®</sup> 82575 PHYs with Intel<sup>®</sup> I/O Acceleration Technology 2 support.</li> </ul>                                                                                                                                                                                                                                                                                                                |

#### Table 1. System Feature Set

| Feature                | Description                                                                                                       |

|------------------------|-------------------------------------------------------------------------------------------------------------------|

| Expansion Capabilities | The following riser card options are available:                                                                   |

|                        | <ul> <li>Three full-height PCI Express* slots (passive)</li> </ul>                                                |

|                        | <ul> <li>Two full-height PCI-X slots with an on-board PXH bridge chip and three PCI<br/>Express* slots</li> </ul> |

|                        | Five full-height PCI Express* slots                                                                               |

| Hard Drive Options     | Eight 2.5-inch hot-swap SATA/SAS hard drives                                                                      |

|                        | <ul> <li>Flex bay for or two additional fixed 2.5-inch hard drives or a 3.5-inch tape<br/>drive</li> </ul>        |

| Peripherals            | Slimline bay for slimline SATA optical drive                                                                      |

|                        | PCI riser card bracket                                                                                            |

| Control Panel          | Standard control panel                                                                                            |

|                        | <ul> <li>Intel<sup>®</sup> Local Control Panel</li> </ul>                                                         |

| LEDs and displays      | With standard control panel:                                                                                      |

|                        | <ul> <li>NIC1 Activity</li> </ul>                                                                                 |

|                        | NIC2 Activity                                                                                                     |

|                        | Power/Sleep                                                                                                       |

|                        | <ul> <li>System Status</li> </ul>                                                                                 |

|                        | <ul> <li>System Identification</li> </ul>                                                                         |

|                        | Hard Drive Activity                                                                                               |

|                        | Intel <sup>®</sup> Light-Guided diagnostics:                                                                      |

|                        | Fan Fault                                                                                                         |

|                        | DIMM Fault                                                                                                        |

|                        | CPU Fault                                                                                                         |

|                        | <ul> <li>5V-STBY</li> </ul>                                                                                       |

|                        | System Status                                                                                                     |

|                        | <ul> <li>System Identification</li> </ul>                                                                         |

|                        | POST Code Diagnostics                                                                                             |

| Devier Cuerk           |                                                                                                                   |

| Power Supply           | Up to two 750-W power supply modules                                                                              |

| Security               | Trusted Platform Module                                                                                           |

| Fans                   | Intel <sup>®</sup> Server System SR2625URBRP:                                                                     |

|                        | <ul> <li>Non-redundant fan option containing three system fans</li> </ul>                                         |

|                        | <ul> <li>Two non-redundant fans in power supply</li> </ul>                                                        |

|                        | Intel <sup>®</sup> Server System SR2625URLX/SR2625URLXT:                                                          |

|                        | <ul> <li>Redundant fan option containing six system fans</li> </ul>                                               |

|                        | <ul> <li>Two non-redundant fans in power supply</li> </ul>                                                        |

| System Management      | On-board ServerEngines* LLC Pilot II Controller                                                                   |

|                        | <ul> <li>Integrated Baseboard Management Controller (Integrated BMC), IPMI 2.0<br/>compliant</li> </ul>           |

|                        | <ul> <li>Integrated Super I/O on LPC interface</li> </ul>                                                         |

|                        | Support for Intel <sup>®</sup> System Management Software 3.1                                                     |

|                        |                                                                                                                   |

\*\*The Trusted Platform Module is only availabe in SR2625URLXT

### 2.1.1 Processor Support

The Intel<sup>®</sup> Server Boards S5520UR supports the following processors:

- One or two Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5500 Series with a 4.8 GT/s, 5.86 GT/s, or 6.4 GT/s Intel<sup>®</sup> QPI link interface and Thermal Design Power (TDP) up to 95 W.

- One or two Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5600 Series with a 6.4 GT/s Intel<sup>®</sup> QPI link interface and Thermal Design Power (TDP) up to 130 W.

The server boards do not support previous generations of the Intel<sup>®</sup> Xeon<sup>®</sup> Processors.

For a complete updated list of supported processors, see:

http://www.intel.com/p/en\_US/support/highlights/server/s5520ur. On the **Support** tab, look for **Compatibility** and then **Supported Processor List**.

### 2.1.1.1 Processor Population Rules

**Note:** Although the server board does support dual-processor configurations consisting of different processors that meet the defined criteria below, Intel<sup>®</sup> does not perform validation testing of this configuration. For optimal system performance in dual-processor configurations, Intel<sup>®</sup> recommends that identical processors be installed.

When using a single processor configuration, the processor must be installed into the processor socket labeled CPU1. A terminator is not required in the second processor socket when using a single processor configuration.

When two processors are installed, the following population rules apply:

- Both processors must be of the same processor family.

- Both processors must have the same front-side bus speed.

- Both processors must have the same cache size.

- Processors with different speeds can be mixed in a system, given the prior rules are met. If this condition is detected, all processor speeds are set to the lowest common denominator (highest common speed) and an error is reported.

- Processor stepping within a common processor family can be mixed as long as it is listed in the processor specification updates published by Intel Corporation.

The following table describes mixed processor conditions and recommended actions for all Intel<sup>®</sup> server boards and systems that use the Intel<sup>®</sup> 5520 Chipset. The errors fall into one of the following two categories:

- **Fatal:** If the system can boot, it goes directly to the error manager, regardless of whether the **Post Error Pause** setup option is enabled or disabled.

- **Major:** If the **Post Error Pause** setup option is enabled, system goes directly to the error manager. Otherwise, the system continues to boot and no prompt is given for the error. The error is logged to the error manager.

| Processor family not<br>identical       Fatal       The BIOS detects the error condition and responds as fo<br>Logs the error into the system event log (SEL).         Alerts the Integrated BMC of the configuration error wi<br>command.       Does not disable the processor.         Processor cache not<br>identical       Fatal       The BIOS detects the error condition and responds as fo         Processor cache not<br>identical       Fatal       The BIOS detects the error condition and responds as fo         Processor cache not<br>identical       Fatal       The BIOS detects the error condition and responds as fo         Processor frequency (speed)<br>not identical       Fatal       The BIOS detects the error condition and responds as fo         Processor frequency (speed)<br>not identical       Major       The BIOS detects the error condition and responds as fo         Processor frequency (speed)<br>not identical       Major       The BIOS detects the error condition and responds as fo         Processor frequency (speed)<br>not identical       Major       The BIOS detects the error condition and responds as fo         Processor frequency (speed)<br>not identical       Major       The BIOS detects the error condition and responds as fo         Processor frequency (speed)<br>not identical       Major       The BIOS detects the error condition and responds as fo         Processor frequency (speed)<br>not identical       Major       The BIOS detects the error condition and responds as fo         Processor frequencic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Processor cache not<br>identical       Fatal         Processor frequency (speed)<br>not identical       Fatal         Processor frequency (speed)<br>not identical       Major         Processor frequency (speed)<br>not identical       Major         Processor frequency (speed)<br>not identical       Major         Processor microcode<br>missing       Fatal         The BIOS detects the error condition and responds as fo<br>Logs the error into the SEL.         Alerts the Integrated BMC of the configuration error wi<br>command.         Processor frequency (speed)<br>not identical         Major         The BIOS detects the error condition and responds as fo<br>- Adjusts all processor frequencies to lowest common<br>denominator.         Processor frequency (speed)<br>not identical         Major         The BIOS detects the error condition and responds as fo<br>- Adjusts all processor frequencies to lowest common<br>denominator.         Processor microcode         Fatal         Processor microcode         Major         The BIOS detects the error condition and responds as fo<br>- Adjusts all processor speeds mismatched" mess<br>error manager.         Halts the system.         Processor microcode         Fatal         Displays "0197: Processor ox unable to apply microcod<br>command.         Does not disable processor.         Displays "816x: Processor 0x unable to apply microc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ollows:      |

| Processor cache not<br>identical       Fatal       The BIOS detects the error condition and responds as fo<br>- Logs the error into the SEL.         Processor frequency (speed)<br>not identical       Fatal       The BIOS detects the error condition and responds as fo<br>- Logs the error into the SEL.         Processor frequency (speed)<br>not identical       Major       The BIOS detects the error condition and responds as fo<br>- Does not disable the processor.         Processor frequency (speed)<br>not identical       Major       The BIOS detects the error condition and responds as fo<br>- Adjusts all processor frequencies to lowest common<br>denominator.         Processor microcode<br>missing       Major       The BIOS detects the error condition and responds as fo<br>- Adjusts all processor scannot be adjusted to<br>same, then the BIOS:         Processor microcode<br>missing       Fatal       The BIOS detects the error condition and responds as fo<br>- Adjusts all processor scannot be adjusted to<br>same, then the BIOS:         Processor microcode<br>missing       Fatal       The BIOS detects the error condition and responds as fo<br>- Logs the error into the SEL.         Processor microcode<br>missing       Fatal       The BIOS detects the error condition and responds as fo<br>- Logs the error into the SEL.         Alerts the Integrated BMC of the configuration error wi<br>command.       - Alerts the Integrated BMC of the configuration error wi<br>command.         Processor microcode<br>missing       Fatal       The BIOS detects the error condition and responds as fo<br>- Logs the error into the SEL.         Alerts the In                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

| Processor cache not<br>identical       Fatal       The BIOS detects the error condition and responds as fo<br>Logs the error into the SEL.         Processor frequency (speed)<br>not identical       Major       The BIOS detects the error condition and responds as fo<br>Logs the error into the SEL.         Processor frequency (speed)<br>not identical       Major       The BIOS detects the error condition and responds as fo<br>- Logs the error manager.         Processor frequency (speed)<br>not identical       Major       The BIOS detects the error condition and responds as fo<br>- Adjusts all processor frequencies to lowest common<br>denominator.         Processor microcode<br>missing       Major       The BIOS detects the error condition and responds as fo<br>- Adjusts all processors cannot be adjusted to<br>same, then the BIOS:         Processor microcode<br>missing       Fatal       The BIOS detects the error condition and responds as fo<br>- Adjusts all processor speeds mismatched" mess<br>error manager.         Processor microcode<br>missing       Fatal       The BIOS detects the error condition and responds as fo<br>- Logs the error into the SEL.         Processor microcode<br>missing       Fatal       The BIOS detects the error condition and responds as fo<br>- Logs the error into the SEL.         Alerts the Integrated BMC of the configuration error wi<br>command.       - Logs the error into the SEL.         Alerts the Integrated BMC of the configuration error wi<br>command.       - Does not disable processor.         Displays "816x: Processor Ox unable to apply microcox                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | /ith an IPMI |

| Processor cache not<br>identical       Fatal       The BIOS detects the error condition and responds as fo<br>Logs the error into the SEL.         Alerts the Integrated BMC of the configuration error wi<br>command.       Does not disable the processor.         Displays "0192: Cache size mismatch detected" mess<br>error manager.         Halts the system.         Processor frequency (speed)<br>not identical         Major         The BIOS detects the error condition and responds as fo<br>Adjusts all processor frequencies to lowest common<br>denominator.         Continues to boot the system successfully.         If the frequencies for all processors cannot be adjusted to<br>same, then the BIOS:         Logs the error into the SEL.         Displays "0197: Processor speeds mismatched" mess<br>error manager.         Halts the system.         Processor microcode<br>missing         Fatal         The BIOS detects the error condition and responds as fo<br>Logs the error into the SEL.         Alats the system.         Processor microcode<br>missing         Fatal         Does not disable processor.         Displays "816x: Processor Ox unable to apply microcom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

| Processor cache not<br>identical       Fatal       The BIOS detects the error condition and responds as fo<br>Logs the error into the SEL.         Alerts the Integrated BMC of the configuration error wi<br>command.       Does not disable the processor.         Displays "0192: Cache size mismatch detected" mess-<br>error manager.         Halts the system.         Processor frequency (speed)<br>not identical         Major         The BIOS detects the error condition and responds as fo<br>. Adjusts all processor frequencies to lowest common<br>denominator.         Continues to boot the system successfully.         If the frequencies for all processors cannot be adjusted to<br>same, then the BIOS:         Logs the error into the SEL.         Displays "0197: Processor speeds mismatched" mess<br>error manager.         Halts the system.         Processor microcode<br>missing         Fatal         The BIOS detects the error condition and responds as fo<br>. Logs the error into the SEL.         Processor microcode<br>missing         Fatal         Obes not disable processor.         Logs the error into the SEL.         Malts the system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ' message    |

| identical       Logs the error into the SEL.         Alerts the Integrated BMC of the configuration error wicommand.         Does not disable the processor.         Displays "0192: Cache size mismatch detected" messierror manager.         Halts the system.         Processor frequency (speed) not identical         Major not identical         The BIOS detects the error condition and responds as for         Logs the error into the SEL.         Logs the error into the SEL.         Halts the system.         Processor microcode missing         Fatal         The BIOS detects the error condition and responds as for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

| Processor frequency (speed) not identical       Major         Processor frequency (speed) not identical       Major         The BIOS detects the error condition and responds as for adjusts all processor frequencies to lowest common denominator.         Continues to boot the system successfully.         If the frequencies for all processor scannot be adjusted to same, then the BIOS:         Logs the error into the SEL.         Processor microcode missing         Fatal         The BIOS detects the error condition and responds as for all processor speeds mismatched" mess error manager.         Halts the system successfully.         If the frequencies for all processor speeds mismatched" mess error manager.         Halts the system.         Processor microcode missing         Fatal         Displays "0197: Processor speeds mismatched" mess error manager.         Halts the system.         Processor microcode missing         Fatal         Does not disable processor.         Does not disable processor.         Does not disable processor.         Does not disable processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ollows:      |

| command.Does not disable the processor.Displays "0192: Cache size mismatch detected" messi<br>error manager.Processor frequency (speed)<br>not identicalMajorThe BIOS detects the error condition and responds as fo<br>• Adjusts all processor frequencies to lowest common<br>denominator.Continues to boot the system successfully.If the frequencies for all processors cannot be adjusted to<br>same, then the BIOS:Logs the error into the SEL.Displays "0197: Processor speeds mismatched" mess<br>error manager.Processor microcode<br>missingFatalProcessor microcode<br>missingFatalDisplays "816x: Processor 0x unable to apply microcode<br>v "816x: Processor 0x unable to apply microcode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

| • Displays "0192: Cache size mismatch detected" messiverror manager.         • Halts the system.         Processor frequency (speed) not identical         Major not identical         Major not identical         The BIOS detects the error condition and responds as for a Adjusts all processor frequencies to lowest common denominator.         • Continues to boot the system successfully.         If the frequencies for all processors cannot be adjusted to same, then the BIOS:         • Logs the error into the SEL.         • Displays "0197: Processor speeds mismatched" messierror manager.         • Halts the system.         Processor microcode missing         Fatal         Displays "0197: Processor speeds mismatched" messierror manager.         • Halts the system.         Processor microcode missing         Fatal         Displays "816x: Processor 0x unable to apply microcode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ∕ith an IPMI |

| error manager.         Processor frequency (speed) not identical         Major         The BIOS detects the error condition and responds as for endition and responds as for endition.         Continues to boot the system successfully.         If the frequencies for all processors cannot be adjusted to same, then the BIOS:         Logs the error into the SEL.         Displays "0197: Processor speeds mismatched" mess error manager.         Halts the system.         Processor microcode missing         Fatal         The BIOS detects the error condition and responds as for error with the system.         Processor microcode missing         Fatal         Does not disable processor.         Displays "816x: Processor 0x unable to apply microcode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |

| Processor frequency (speed)<br>not identical       Major       The BIOS detects the error condition and responds as fo         Adjusts all processor frequencies to lowest common<br>denominator.       Adjusts all processor frequencies to lowest common<br>denominator.         Continues to boot the system successfully.       If the frequencies for all processors cannot be adjusted to<br>same, then the BIOS:         Logs the error into the SEL.       Displays "0197: Processor speeds mismatched" mess<br>error manager.         Processor microcode<br>missing       Fatal         The BIOS detects the error condition and responds as fo         Logs the error into the SEL.         Output         Processor microcode         Fatal         Does the error into the SEL.         Alerts the Integrated BMC of the configuration error wi<br>command.         Does not disable processor.         Displays "816x: Processor 0x unable to apply microcom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | sage in the  |

| not identical <ul> <li>Adjusts all processor frequencies to lowest common denominator.</li> <li>Continues to boot the system successfully.</li> <li>If the frequencies for all processors cannot be adjusted to same, then the BIOS:             <ul> <li>Logs the error into the SEL.</li> <li>Displays "0197: Processor speeds mismatched" mess error manager.</li> <li>Halts the system.</li> </ul> </li> </ul> <li>Processor microcode missing         <ul> <li>Fatal</li> <li>The BIOS detects the error condition and responds as for<ul> <li>Logs the error into the SEL.</li> <li>Alerts the Integrated BMC of the configuration error with command.</li> <li>Does not disable processor.</li> <li>Displays "816x: Processor 0x unable to apply microcommand.</li> <li>Displays "816x: Processor 0x unable to apply microcommand.</li> </ul> </li> </ul> </li>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| Processor mequancies to lowest common denominator.         Continues to boot the system successfully.         If the frequencies for all processors cannot be adjusted to same, then the BIOS:         Logs the error into the SEL.         Displays "0197: Processor speeds mismatched" mess error manager.         Halts the system.         Processor microcode missing         Fatal         The BIOS detects the error condition and responds as for         Logs the error into the SEL.         Alerts the Integrated BMC of the configuration error wit command.         Does not disable processor.         Displays "816x: Processor 0x unable to apply microcode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ollows:      |

| If the frequencies for all processors cannot be adjusted to same, then the BIOS:         Logs the error into the SEL.         Displays "0197: Processor speeds mismatched" mess error manager.         Halts the system.         Processor microcode missing         Fatal         The BIOS detects the error condition and responds as for         Logs the error into the SEL.         Alerts the Integrated BMC of the configuration error wi command.         Does not disable processor.         Displays "816x: Processor 0x unable to apply microcoded processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |

| same, then the BIOS:         Logs the error into the SEL.         Displays "0197: Processor speeds mismatched" mess error manager.         Halts the system.         Processor microcode missing         Fatal         The BIOS detects the error condition and responds as for         Logs the error into the SEL.         Alerts the Integrated BMC of the configuration error wi command.         Does not disable processor.         Displays "816x: Processor 0x unable to apply microcoded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |

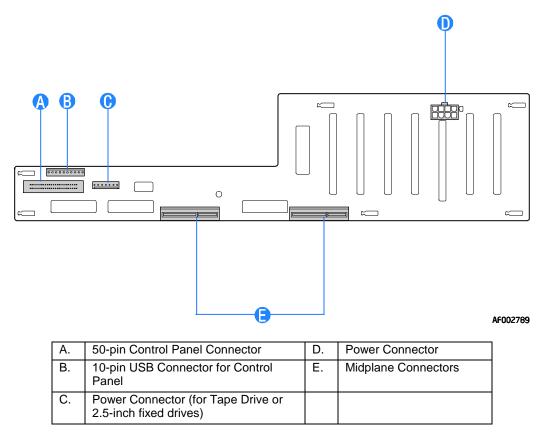

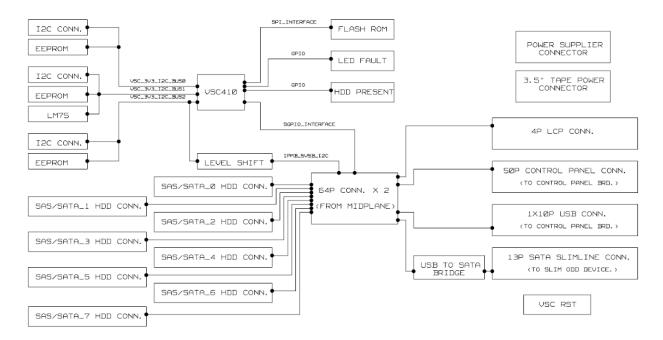

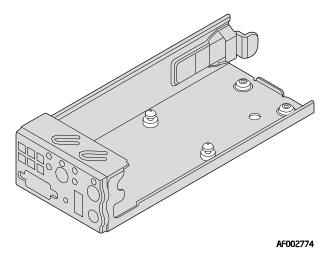

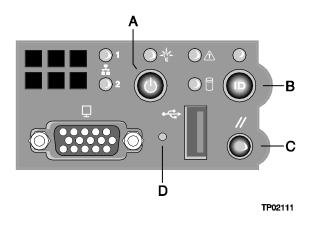

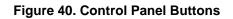

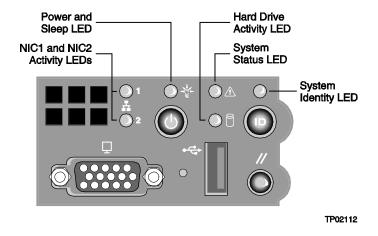

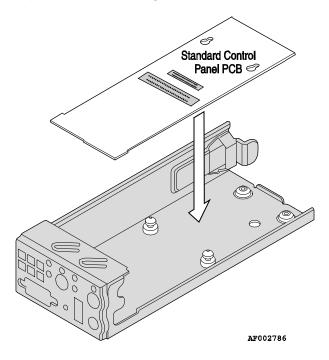

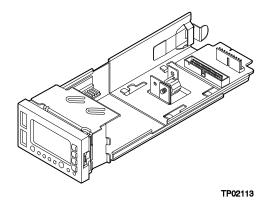

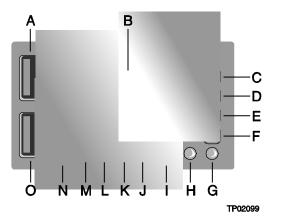

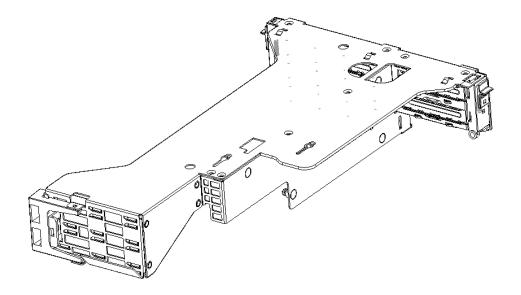

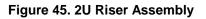

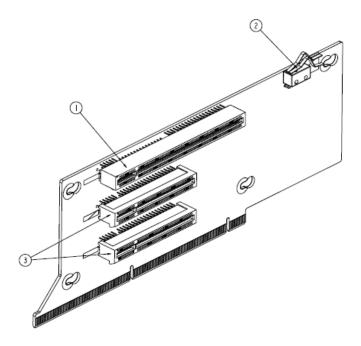

| <ul> <li>Displays "0197: Processor speeds mismatched" mess error manager.</li> <li>Halts the system.</li> <li>Processor microcode missing</li> <li>Fatal</li> <li>The BIOS detects the error condition and responds as for</li> <li>Logs the error into the SEL.</li> <li>Alerts the Integrated BMC of the configuration error wi command.</li> <li>Does not disable processor.</li> <li>Displays "816x: Processor 0x unable to apply microcode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | to be the    |