# Intel<sup>®</sup> Server System S7000FC4UR

**Technical Product Specification**

Intel order number E18291-001

**Revision 1.0**

July 13, 2007

**Enterprise Platforms and Services Division - Marketing**

### **Revision History**

| Date          | Revision<br>Number | Modifications |

|---------------|--------------------|---------------|

| July 13, 2007 | 1.0                | First release |

|               |                    |               |

|               |                    |               |

### Disclaimers

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

The Intel® Server System S7000FC4UR may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2007. All rights reserved.

# Table of Contents

| 1. | Introduc | ction                                     | 1 |

|----|----------|-------------------------------------------|---|

| 2. | Main Bo  | pard                                      | 2 |

| 2  | .1       | Introduction                              | 2 |

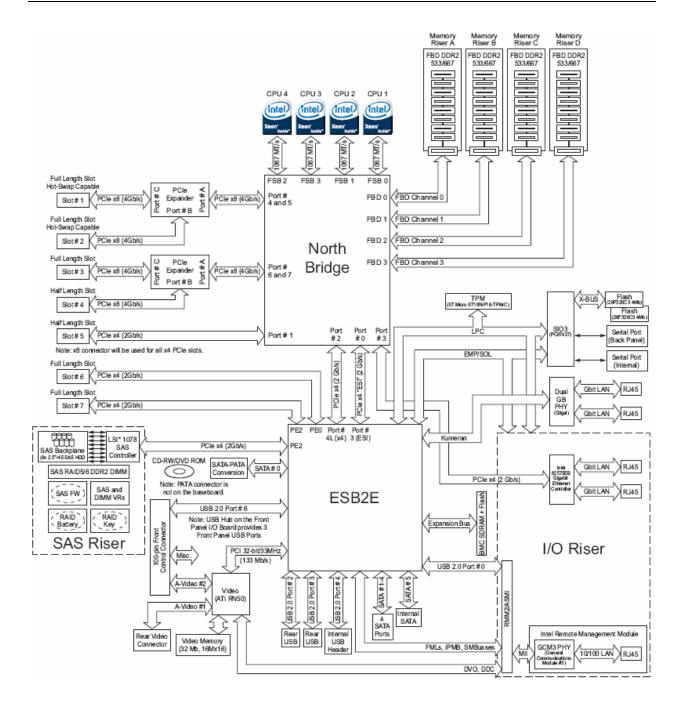

|    | 2.1.1    | Main Board Block Diagram                  | 2 |

| 2  | .2       | Functional Architecture                   | 4 |

|    | 2.2.1    | Intel® Xeon® Processors                   | 4 |

|    | 2.2.2    | Intel® 7300 Chipset Memory Controller Hub | 5 |

|    | 2.2.3    | Enterprise Southbridge 2                  | 6 |

|    | 2.2.4    | PCI-Express* Subsystem                    | 7 |

|    | 2.2.5    | PCI 32-Bit Subsystem1                     | 0 |

|    | 2.2.6    | Main board Memory Interface1              | 1 |

|    | 2.2.7    | Main Board I/O Riser Interface1           | 2 |

|    | 2.2.8    | Main Board SAS Riser Interface1           | 2 |

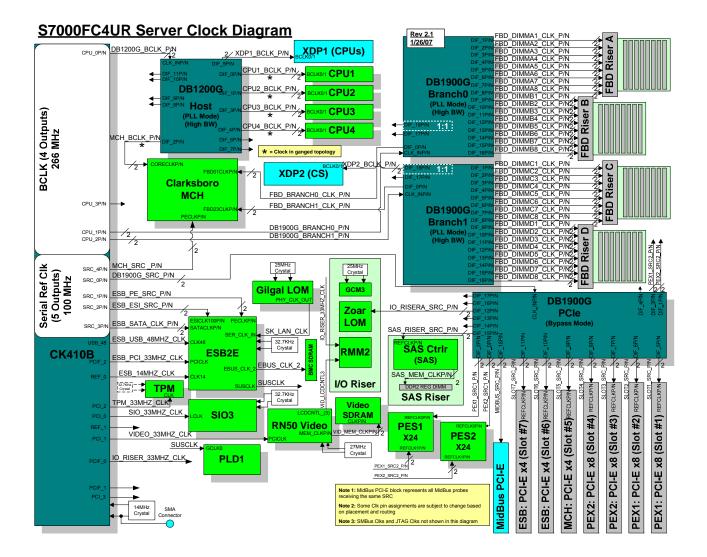

|    | 2.2.9    | Clock Subsystem1                          | 2 |

|    | 2.2.10   | Serial-ATA (SATA) Sub-system1             | 6 |

|    | 2.2.11   | Flash Devices1                            | 7 |

|    | 2.2.12   | Video Subsystem                           | 7 |

|    | 2.2.13   | USB 2.0 Subsystem1                        | 7 |

|    | 2.2.14   | Trusted Platform Module1                  | 7 |

|    | 2.2.15   | Serial Port Support1                      | 8 |

|    | 2.2.16   | LAN on Motherboard 1 (LOM1)1              | 8 |

|    | 2.2.17   | Post Code LEDs1                           | 8 |

|    | 2.2.18   | Programmable Logic Devices (PLDs)1        | 9 |

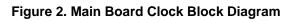

|    | 2.2.19   | Interrupt and Error Logic Block Diagram2  | 2 |

|    | 2.2.20   | Circuit Breaker Type Jumper2              | 3 |

|    | 2.2.21   | Power Delivery Block Diagram24            | 4 |

|    | 2.2.22   | Reset and Powergood Diagram2              | 6 |

|    | 2.2.23   | Power Sequencing/Timing Diagrams2         | 7 |

|    | 2.2.24   | Thermal Specifications                    | 0 |

| 3. | Main Bo  | oard Server Management3                   | 1 |

|    | 3.1.1    | IPMI 2.0 Features                         | 1 |

|    | 3.1.2    | Non IPMI Features                         | 2 |

| 3            | .2       | Functional Architecture                        | 33 |

|--------------|----------|------------------------------------------------|----|

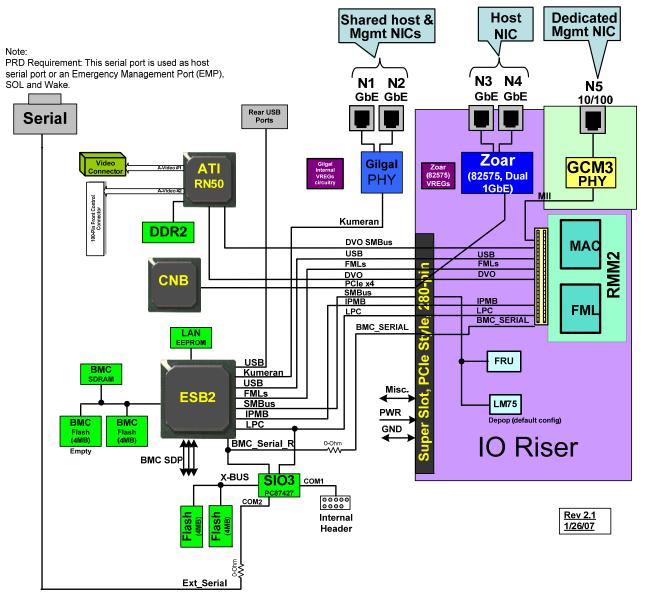

|              | 3.2.1    | I/O Riser / Server Management Diagram          | 34 |

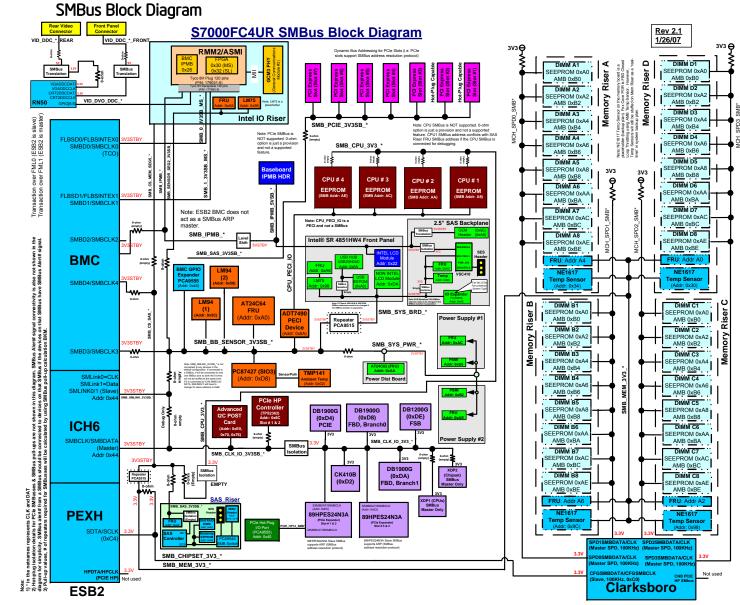

|              | 3.2.2    | SMBus Block Diagram                            | 35 |

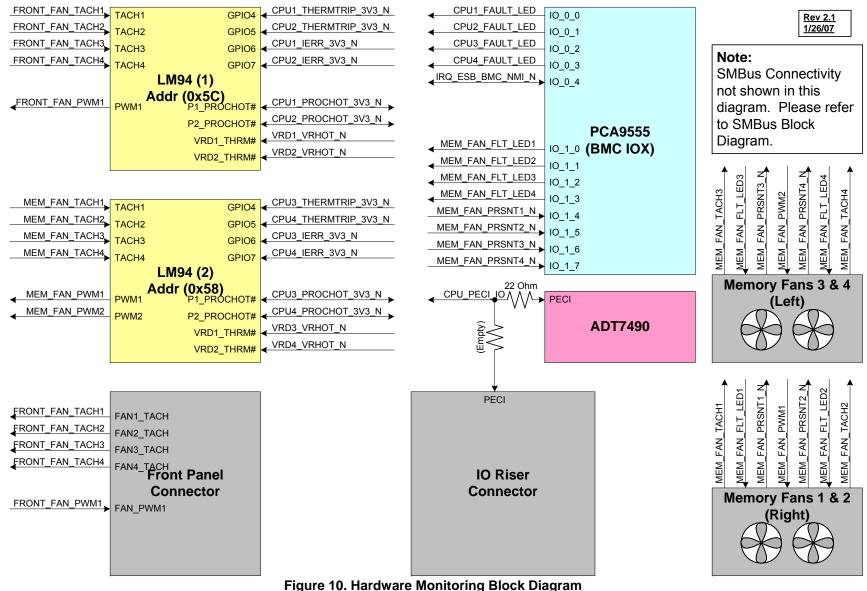

|              | 3.2.3    | Hardware Monitoring Block Diagram              | 36 |

|              | 3.2.4    | Sensor Data Record SDR (SDR) Repository        | 37 |

|              | 3.2.5    | Field Replaceable Unit (FRU) Inventory Devices | 37 |

|              | 3.2.6    | System Event Log (SEL)                         | 38 |

|              | 3.2.7    | Real-Time Clock (RTC) Access                   | 38 |

|              | 3.2.8    | Rolling BIOS                                   | 38 |

|              | 3.2.9    | BMC EBus Memory Sub-System                     | 38 |

| 3            | .3       | Supported Features                             | 39 |

|              | 3.3.1    | Fan Speed Control                              | 39 |

|              | 3.3.2    | Hardware Monitoring (LM94*)                    | 39 |

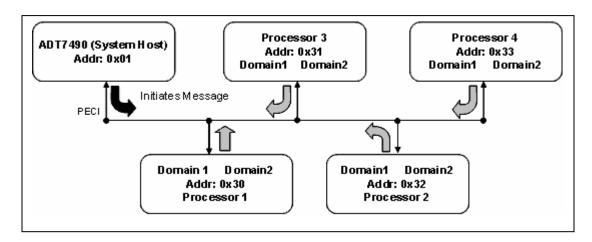

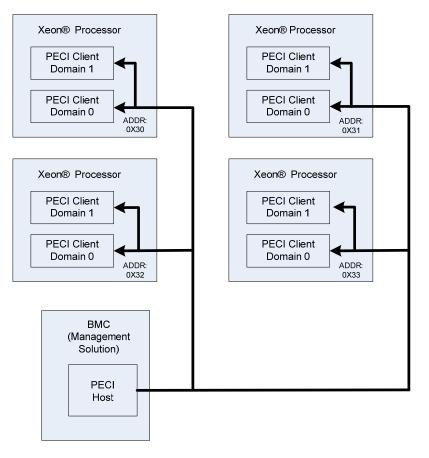

|              | 3.3.3    | PECI (ADT7490*)                                | 39 |

|              | 3.3.4    | Processor Throttling                           | 42 |

|              | 3.3.5    | Memory Throttling                              | 43 |

|              | 3.3.6    | ACPI Power Control                             | 43 |

|              | 3.3.7    | Wake On LAN                                    | 44 |

|              | 3.3.8    | Secure Mode Operation                          | 45 |

|              | 3.3.9    | Intelligent Platform Management Bus (IPMB)     | 46 |

|              | 3.3.10   | Serial Over LAN (SOL)                          | 46 |

|              | 3.3.11   | Emergency Management Port (EMP) Interface      | 46 |

|              | 3.3.12   | Chassis Intrusion                              | 47 |

| 4.           | Memory   | Riser                                          | 48 |

| 4            | .1       | Functional Architecture                        | 48 |

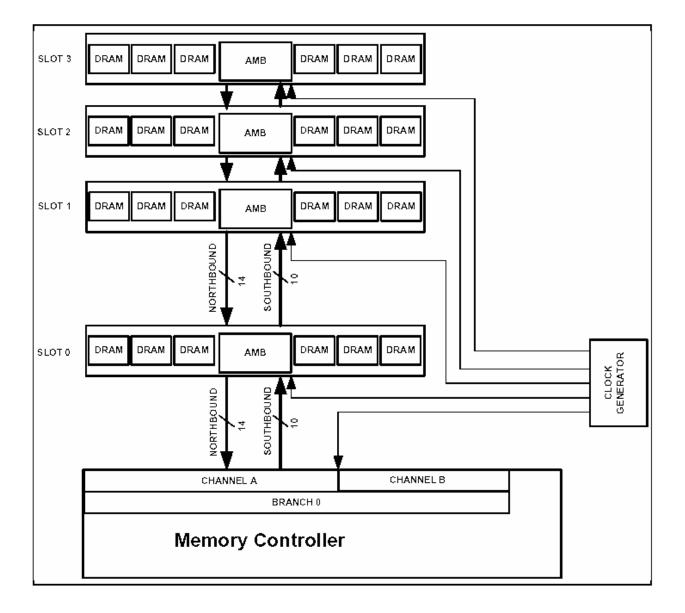

|              | 4.1.1    | FBD Memory Sub-system Overview                 | 48 |

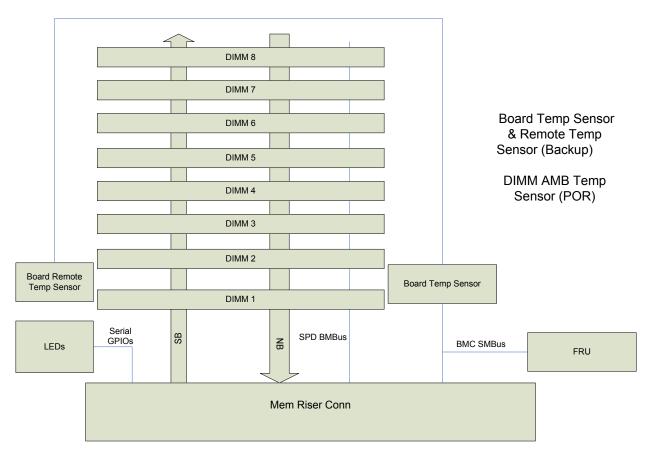

|              | 4.1.2    | Memory Riser Functional Diagram                | 51 |

|              | 4.1.3    | Supported Memory                               | 51 |

|              | 4.1.4    | Temperature Sensors, FRU, and SPD, BMC Bus     | 52 |

|              | 4.1.5    | Memory Riser LEDs                              | 53 |

|              | 4.1.6    | Power Rails                                    | 53 |

| 5.           | I/O Rise | r                                              | 54 |

| 5            | .1       | I/O Riser Features                             | 54 |

| 5            | .2       | Functional Architecture                        | 55 |

| 6. SAS Riser |          | 56                                             |    |

|    | 6.1.1  | SAS Riser Features                                | . 56 |

|----|--------|---------------------------------------------------|------|

| 6  | .2     | Functional Architecture                           | . 56 |

|    | 6.2.1  | Intel <sup>®</sup> SAS RAID-on-MotherBoard (ROMB) | . 56 |

|    | 6.2.2  | FRU and SES                                       | . 57 |

|    | 6.2.3  | SMBus                                             | . 58 |

|    | 6.2.4  | SAS Riser Power                                   | . 58 |

| 7. | SAS Ba | ckplane                                           | . 59 |

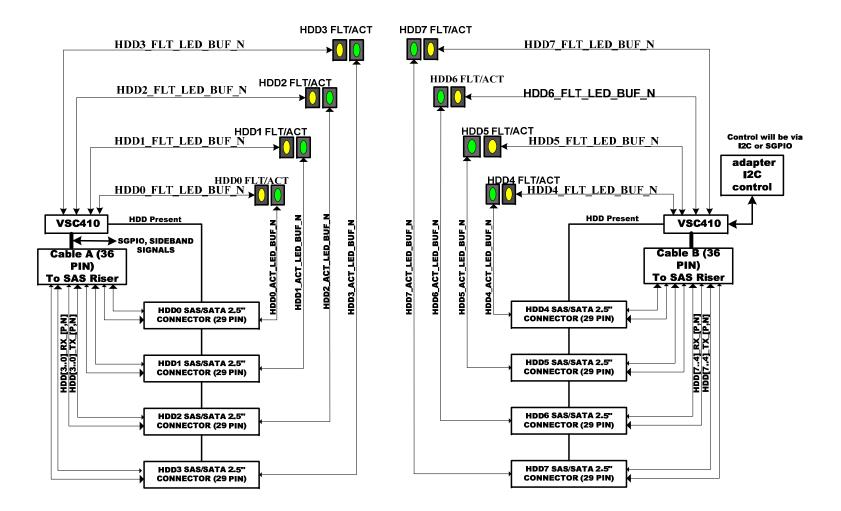

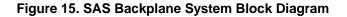

|    | 7.1.1  | System Block Diagram                              | . 60 |

| 7  | .2     | Architectural Overview                            | . 61 |

|    | 7.2.1  | 3Gbit SAS Port Expanders                          | . 61 |

| 7  | .3     | Functional Architecture                           | . 62 |

|    | 7.3.1  | SAS Buses                                         | . 62 |

|    | 7.3.2  | SAS Backplane                                     | . 62 |

|    | 7.3.3  | Full-duplex Serial Mode Operation                 | . 62 |

|    | 7.3.4  | SAS Controller                                    | . 63 |

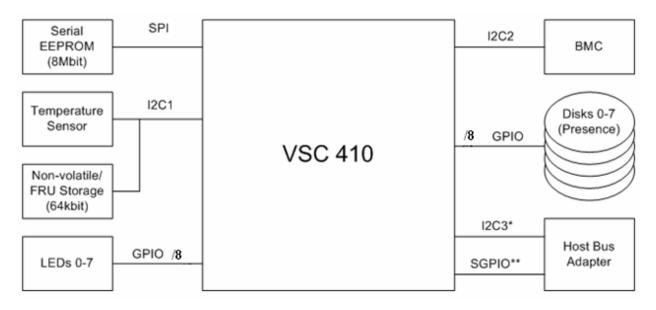

|    | 7.3.5  | Vitesse* VSC410 Controller Functionality          | . 63 |

|    | 7.3.6  | SAS Drive Functionality                           | . 64 |

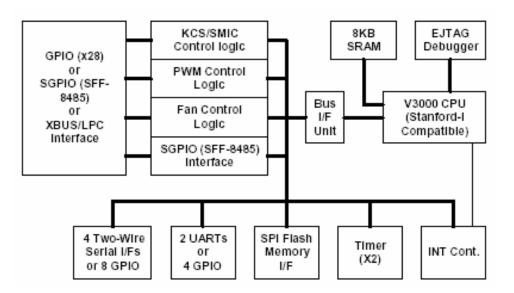

|    | 7.3.7  | Power Control Interlock                           | . 64 |

|    | 7.3.8  | SAS Enclosure Management                          | . 64 |

|    | 7.3.9  | Server Management Interface                       | . 65 |

|    | 7.3.10 | Resets                                            | . 66 |

|    | 7.3.11 | Connector Interlocks                              | . 67 |

|    | 7.3.12 | Clock Generation                                  | . 67 |

|    | 7.3.13 | Programmed Devices                                | . 67 |

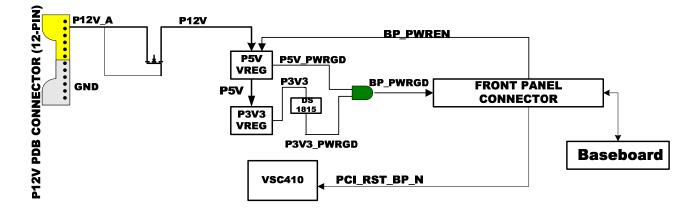

| 8. | System | Overview                                          | .68  |

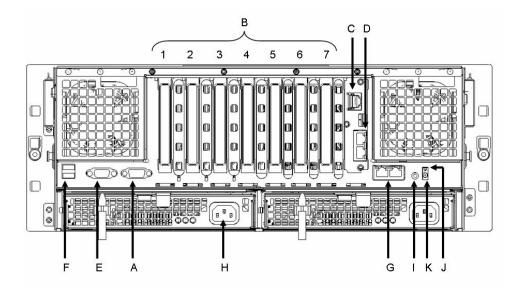

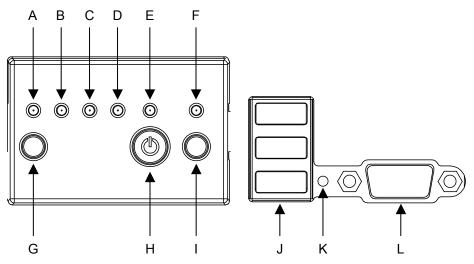

| 8  | .1     | External Chassis Features – Front                 | . 70 |

|    | 8.1.1  | Front Panel                                       | . 70 |

|    | 8.1.2  | Hard Drive and Peripheral Device Bays             | .71  |

| 8  | .2     | External Chassis Features – Rear                  | .71  |

|    | 8.2.1  | User-Accessible Connectors, PCI Slots and LEDs    | .72  |

|    | 8.2.2  | Power Distribution Board (PDB)                    | .73  |

|    | 8.2.3  | Front Panel I/O Board                             | .73  |

|    | 8.2.4  | Front Panel Control Board                         | .73  |

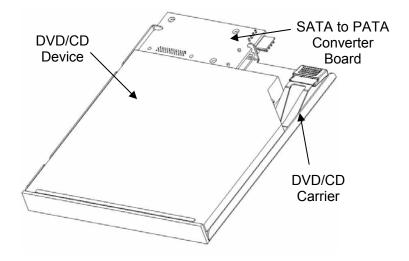

|    | 8.2.5  | SATA-to-PATA Converter Board                      | .73  |

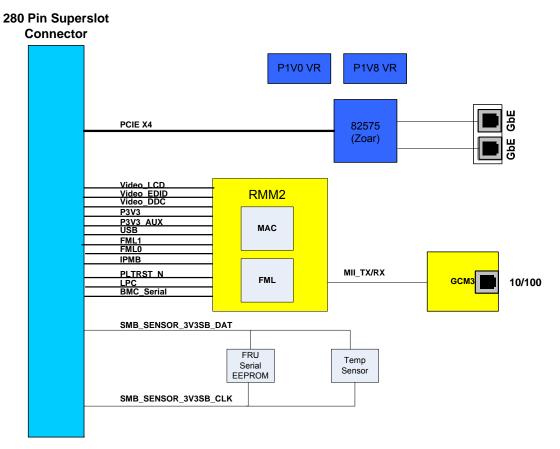

|    | 8.2.6  | Intel® Remote Management Module 2 (Intel® RMM2)   | .73  |

| 8  | 8.3    | Power Subsystem                    | 73 |

|----|--------|------------------------------------|----|

| 8  | 8.4    | Cooling Subsystem                  | 74 |

| 8  | 8.5    | Specifications                     | 75 |

|    | 8.5.1  | Environmental Specifications       | 75 |

|    | 8.5.2  | Physical Specifications            | 75 |

| 9. | System | Chassis and Sub-Assemblies         | 77 |

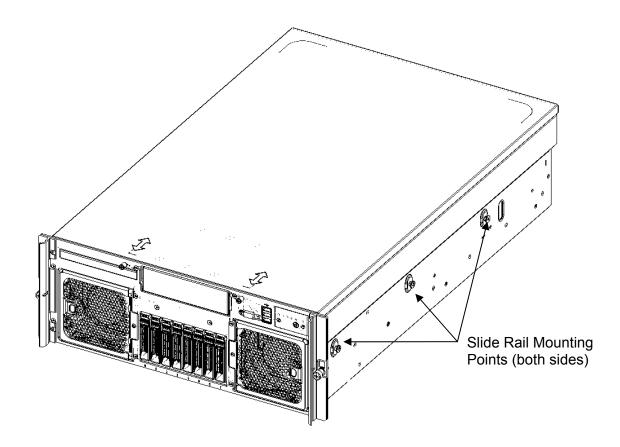

| ę  | 9.1    | Base Chassis and Top Covers        | 77 |

|    | 9.1.1  | Base Chassis                       | 77 |

|    | 9.1.2  | Top Cover                          | 77 |

|    | 9.1.3  | Slide Rails                        | 77 |

| ę  | ).2    | Power and Fan Subsystems           | 78 |

|    | 9.2.1  | Power Subsystem                    | 78 |

|    | 9.2.2  | Fan Subsystem                      | 79 |

| ę  | 0.3    | Main Board Subsystem               | 81 |

| ę  | 9.4    | Peripheral Bay Subsystem           | 81 |

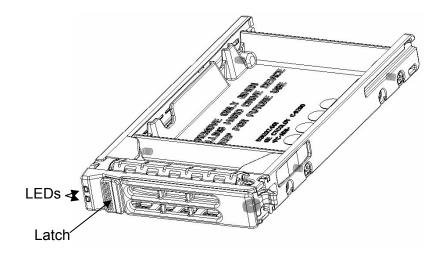

|    | 9.4.1  | Hard Drive Carrier                 | 82 |

|    | 9.4.2  | Optical Drive Carrier              | 82 |

| ę  | 9.5    | Front Bezel                        | 83 |

| 10 | 1570W  | Power Supply                       | 84 |

| 1  | 0.1    | AC Input Requirement               | 84 |

|    | 10.1.1 | AC Input Voltage Specification     | 84 |

|    | 10.1.2 | Efficiency                         | 84 |

|    | 10.1.3 | Input Over-Current Protection      | 84 |

|    | 10.1.4 | Inrush Current                     | 84 |

|    | 10.1.5 | Auto Restart                       | 85 |

|    | 10.1.6 | Power Factor Correction (PFC)      | 85 |

|    | 10.1.7 | AC Input Connector                 | 85 |

| 1  | 0.2    | DC Output Requirements             | 85 |

|    | 10.2.1 | Hot Swap Functionality             | 85 |

|    | 10.2.2 | Output Current Rating              | 86 |

|    | 10.2.3 | Over- and Under-Voltage Protection | 86 |

|    | 10.2.4 | Over-Current Protection            | 87 |

|    | 10.2.5 | Short Circuit Protection           | 87 |

|    | 10.2.6 | Reset After Shutdown               | 87 |

|    | 10.2.7 | Current Sharing                    | 88 |

| 10.2.8                       | I <sup>2</sup> C Devices                                                    | 88  |

|------------------------------|-----------------------------------------------------------------------------|-----|

| 10.2.9                       | Power Supply Module LED indicators                                          | 89  |

| 10.3                         | Regulatory Agency Requirements                                              | 89  |

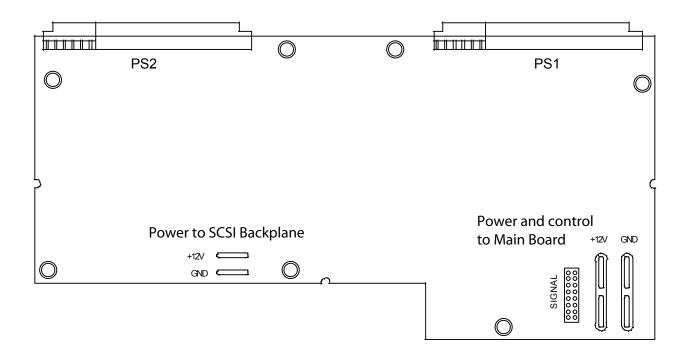

| 11. Power Distribution Board |                                                                             | 90  |

| 11.1.1                       | Remote On/Off (-PS_ON)                                                      | 90  |

| 11.1.2                       | POWER GOOD SIGNAL (POK, or P_GOOD)                                          | 90  |

| 11.1.3                       | VIN_GOOD                                                                    | 91  |

| 12. Front P                  | anel I/O and Control Boards                                                 | 92  |

| 12.1                         | Architectural Overview                                                      | 92  |

| 12.2                         | Functional Architecture                                                     | 93  |

| 12.2.1                       | VGA                                                                         | 93  |

| 12.2.2                       | USB                                                                         | 93  |

| 12.2.3                       | FRU                                                                         | 93  |

| 12.2.4                       | Thermal Sensor                                                              | 93  |

| 12.2.5                       | 50-pin Control Panel Connector                                              | 93  |

| 12.2.6                       | Speaker                                                                     | 93  |

| 12.2.7                       | NMI Button                                                                  | 93  |

| 12.2.8                       | Main Board and SAS Backplane Connectors                                     | 93  |

| 12.3                         | Front Panel Control Module                                                  | 94  |

| 12.3.1                       | System ID Buttons and LEDs                                                  | 94  |

| 13. Basic Ir                 | nput/Output System (BIOS)                                                   | 96  |

| 13.1                         | BIOS Architecture                                                           | 96  |

| 13.1.1                       | Data Structure Descriptions                                                 | 96  |

| 13.2                         | BIOS Identification String                                                  | 96  |

| 14. BIOS In                  | itialization                                                                | 98  |

| 14.1                         | Processors                                                                  | 98  |

| 14.1.1                       | Multiple Processor Initialization                                           | 98  |

| 14.1.2                       | Processor Built-In Self Test (BIST)                                         | 98  |

| 14.1.3                       | Processor Cache                                                             | 98  |

| 14.1.4                       | Microcode Update                                                            | 99  |

| 14.1.5                       | Enhanced Intel SpeedStep <sup>®</sup> Technology                            | 99  |

| 14.1.6                       | Thermal Monitor Technology                                                  | 99  |

| 14.1.7                       | Intel <sup>®</sup> Extended Memory 64 Technology (Intel <sup>®</sup> EM64T) | 99  |

| 14.1.8                       | Execute Disable Bit Feature                                                 | 100 |

| 14.1.9                       | Enhanced Halt State (C1E)                                                   | 100 |

| 14.1.10 | Hardware Prefetch                                      |     |

|---------|--------------------------------------------------------|-----|

| 14.1.11 | Adjacent Cache Line Prefetch                           |     |

| 14.1.12 | Intel <sup>®</sup> Core Multi-Processing (CMP)         |     |

| 14.1.13 | Intel <sup>®</sup> Virtualization Technology           |     |

| 14.1.14 | "Fake MSI" Support                                     |     |

| 14.1.15 | Direct Cache Access (DCA)                              |     |

| 14.1.16 | Snoop Filter                                           |     |

| 14.1.17 | Platform Environmental Control Interface (PECI)        |     |

| 14.1.18 | Processor Configuration Errors                         |     |

| 14.2    | Memory                                                 |     |

| 14.2.1  | Memory Sub-System Nomenclature                         |     |

| 14.2.2  | Memory Population Table                                |     |

| 14.2.3  | Modes of Operation                                     | 112 |

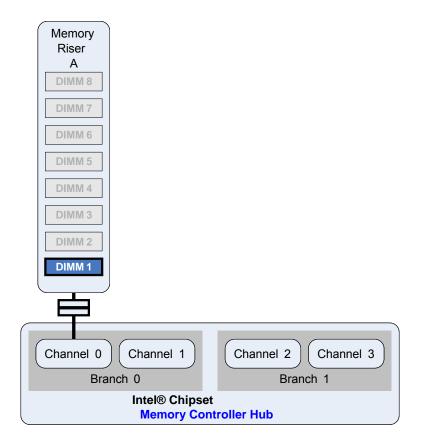

| 14.2.4  | Single and Dual Channel Configuration Population Rules | 112 |

| 14.2.5  | DIMM Sparing Population Rules                          | 119 |

| 14.2.6  | Mirroring Population Rules                             |     |

| 14.2.7  | Memory Sizing and Configuration                        |     |

| 14.2.8  | Support for Mixed-Speed Memory Modules                 | 123 |

| 14.2.9  | Memory Reservation for Memory-Mapped Functions         |     |

| 14.2.10 | Memory Interleaving                                    |     |

| 14.2.11 | POST Memory Test                                       |     |

| 14.2.12 | Publishing System Memory                               |     |

| 14.2.13 | Memory Reliability, Availability, Serviceability (RAS) |     |

| 14.2.14 | Memory Sub-System Errors                               |     |

| 14.2.15 | Server Management Aspects of Memory and Memory RAS     |     |

| 14.3    | I/O Subsystem                                          | 141 |

| 14.3.1  | I/O Subsystem Specification Compliance                 | 141 |

| 14.3.2  | Crystal Beach Technology                               | 141 |

| 14.3.3  | Peripheral Component Interconnect (PCI) Bus            | 141 |

| 14.3.4  | PCI Express* Hot-plug                                  | 143 |

| 14.3.5  | PnP ISA                                                | 146 |

| 14.3.6  | Keyboard / Mouse                                       | 146 |

| 14.3.7  | Universal Serial Bus (USB)                             | 146 |

| 14.3.8  | Serial ATA (SATA) Support                              | 147 |

| 14.3.9  | Removable Media Drives                                 |     |

| 14.3.10     | Flash ROM                                         |     |

|-------------|---------------------------------------------------|-----|

| 14.4        | Fan Speed Control and Thermal Management          | 148 |

| 14.4.1      | FBDIMM Thermal Management                         | 148 |

| 14.4.2      | Processor Thermal Management                      | 150 |

| 15. BIOS Us | ser Interface                                     | 151 |

| 15.1        | Splash Logo / Diagnostic Screen                   | 151 |

| 15.1.1      | Splash Logo Screen                                | 151 |

| 15.1.2      | Diagnostic Screen                                 | 151 |

| 15.2        | BIOS Setup Utility                                | 152 |

| 15.2.1      | Features                                          | 152 |

| 15.2.2      | Page Layout                                       | 152 |

| 15.2.3      | BIOS Setup Utility Screens                        | 154 |

| 15.3        | Loading BIOS Defaults                             |     |

| 16. BIOS U  | odate Support                                     | 194 |

| 16.1        | Rolling BIOS                                      |     |

| 16.1.1      | Operating Modes                                   |     |

| 16.1.2      | Rolling BIOS Jumper Behavior (Normal Mode)        | 194 |

| 16.1.3      | Rolling BIOS Jumper Behavior (Force Other Bank)   |     |

| 16.2        | OEM Binary                                        |     |

| 16.2.1      | OEM Splash Logo                                   |     |

| 16.2.2      | OEM Strings                                       |     |

| 17. Operati | ng System Boot, Sleep, and Wake                   | 197 |

| 17.1        | Boot Device Selection                             |     |

| 17.1.1      | Server Managment Boot Device Control              |     |

| 17.1.2      | USB Device Booting                                |     |

| 17.1.3      | USB Boot Device Reordering                        |     |

| 17.2        | Operating System Support                          | 198 |

| 17.2.1      | Microsoft Windows* Compatibility                  |     |

| 17.2.2      | Advanced Configuration and Power Interface (ACPI) |     |

| 17.3        | Front Control Panel Support                       |     |

| 17.3.1      | Power Button                                      |     |

| 17.3.2      | Reset Button                                      |     |

| 17.3.3      | NMI Button                                        |     |

| 17.4        | Sleep and Wake Support                            | 201 |

| 17.4.1      | System Sleep States                               | 201 |

| 17.4.2     | Supported Wake Events                              | 201 |

|------------|----------------------------------------------------|-----|

| 17.5       | Non-Maskable Interrupt (NMI) Handling              |     |

| 18. BIOS R | ole in Server Management                           | 204 |

| 18.1       | IPMI                                               | 204 |

| 18.2       | Console Redirection                                | 204 |

| 18.2.1     | Keystroke Mappings                                 |     |

| 18.2.2     | Interface to Server Management                     |     |

| 18.3       | IPMI Serial Interface                              |     |

| 18.3.1     | Channel Access Modes                               |     |

| 18.3.2     | Interaction with BIOS Console Redirection          |     |

| 18.3.3     | Serial Over LAN                                    |     |

| 18.4       | Wired For Management (WFM)                         |     |

| 18.4.1     | PXE BIOS Support                                   |     |

| 18.5       | System Management BIOS (SMBIOS)                    |     |

| 18.5.1     | Access Methods                                     |     |

| 18.5.2     | OEM Modification                                   | 210 |

| 18.5.3     | SMBIOS Stuctures Supported                         | 210 |

| 18.6       | Security                                           |     |

| 18.6.1     | Password                                           |     |

| 18.6.2     | Password Clear Jumper                              | 221 |

| 18.7       | BMC Timestamp Synchronization                      | 221 |

| 19. BIOS E | rror Handling                                      |     |

| 19.1       | Fault Resilient Booting                            |     |

| 19.1.1     | BSP POST Failure (FRB-2)                           |     |

| 19.1.2     | Operating System Load Failure (OS Boot Timer)      |     |

| 19.1.3     | Operating System Watchdog Failure                  |     |

| 19.1.4     | Boot Event                                         |     |

| 19.2       | Error Handling and Logging                         |     |

| 19.2.1     | Runtime Error Handler                              |     |

| 19.2.2     | Error Sources and Types                            |     |

| 19.2.3     | System Event Logging (SEL) Format Conventions      |     |

| 19.2.4     | IPMI Sensor Type Events — Memory                   | 230 |

| 19.2.5     | IPMI Sensor Type Events — System Firmware Progress | 231 |

| 19.2.6     | IPMI Sensor Type Events — Event Logging Disabled   | 232 |

| 19.2.7     | IPMI Sensor Type Events — Critical Interrupt       | 233 |

| 19.3       | POST Progress Codes and Errors                                            | 235 |

|------------|---------------------------------------------------------------------------|-----|

| 19.3.1     | POST Error Beep Codes                                                     | 235 |

| 19.3.2     | POST Codes                                                                | 235 |

| 19.3.3     | POST Error Manager Messages and Handling                                  | 238 |

| 20. New Te | echnologies                                                               | 247 |

| 20.1       | Intel <sup>®</sup> I/O Acceleration Technology (Intel <sup>®</sup> I/OAT) | 247 |

| 20.2       | Trusted Platform Module (TPM) Security                                    | 247 |

| 20.2.1     | TPM Security BIOS                                                         | 247 |

| 20.2.2     | Physical Presence                                                         | 248 |

| 20.2.3     | TPM Security Setup Options                                                | 248 |

| 20.3       | Internet SCSI (iSCSI)                                                     | 249 |

| 21. Basebo | oard Management Controller (BMC)                                          | 250 |

| 21.1       | ESB2 South Bridge                                                         | 250 |

| 21.1.1     | ESB2 Baseboard Management Controller Functionality                        | 251 |

| 22. BMC Fu | unctional Specifications                                                  | 252 |

| 22.1       | Power System                                                              | 252 |

| 22.1.1     | Power Supply Interface Signals                                            | 252 |

| 22.1.2     | Power-Good Dropout                                                        | 252 |

| 22.1.3     | Power-up Sequence                                                         |     |

| 22.1.4     | Power Down Sequence                                                       | 253 |

| 22.1.5     | Power Control Sources                                                     |     |

| 22.1.6     | Power State Retention                                                     | 254 |

| 22.1.7     | Power State Restoration                                                   | 254 |

| 22.1.8     | Wake-On-LAN (WOL)                                                         | 254 |

| 22.2       | Advanced Configuration and Power Interface (ACPI)                         | 255 |

| 22.2.1     | ACPI Power Control                                                        | 255 |

| 22.2.2     | ACPI State Synchronization                                                | 255 |

| 22.2.3     | ACPI Power State Notify                                                   | 256 |

| 22.3       | System Reset Control                                                      | 256 |

| 22.3.1     | Reset Signal Output                                                       | 256 |

| 22.3.2     | Reset Control Sources                                                     | 256 |

| 22.3.3     | Front Panel System Reset                                                  |     |

| 22.3.4     | Soft Reset and Hard Reset                                                 |     |

| 22.3.5     | BMC Command to Cause System Reset                                         | 257 |

| 22.3.6  | Watchdog Timer Expiration                      | 257 |

|---------|------------------------------------------------|-----|

| 22.4    | BMC Reset Control                              | 257 |

| 22.4.1  | BMC Exits Firmware Update Mode                 | 257 |

| 22.4.2  | Standby Power Comes Up                         | 257 |

| 22.5    | System Initialization                          | 257 |

| 22.5.1  | Processor TControl Setting                     | 257 |

| 22.5.2  | Fault Resilient Booting (FRB)                  | 258 |

| 22.5.3  | Processor Presence and Population Check        | 258 |

| 22.5.4  | Processor Disabling                            | 258 |

| 22.5.5  | BSP Identification                             | 258 |

| 22.6    | Integrated Front Panel User Interface          | 258 |

| 22.6.1  | Power LED                                      | 259 |

| 22.6.2  | System Status LED                              | 259 |

| 22.6.3  | Chassis ID LED                                 | 261 |

| 22.6.4  | Front Panel / Chassis Inputs                   | 261 |

| 22.6.5  | Secure Mode and Front Panel Lock-out Operation | 262 |

| 22.6.6  | Set Fault Indication Command                   | 263 |

| 22.6.7  | Button Sensor                                  | 263 |

| 22.7    | Watchdog Timer                                 | 263 |

| 22.8    | BMC Internal Timestamp Clock                   | 263 |

| 22.9    | System Event Log (SEL)                         | 264 |

| 22.9.1  | Servicing Events                               | 264 |

| 22.9.2  | SEL Entry Deletion                             | 264 |

| 22.9.3  | SEL Erasure                                    | 264 |

| 22.10   | Sensor Data Record (SDR) Repository            | 264 |

| 22.10.1 | SDR Repository Erasure                         | 265 |

| 22.11   | Field Replaceable Unit (FRU) Inventory Device  | 265 |

| 22.12   | Diagnostics and Beep Code Generation           | 265 |

| 22.13   | NMI                                            | 265 |

| 22.13.1 | Signal Generation                              | 266 |

| 22.14   | General Sensor Behavior                        | 267 |

| 22.14.1 | Sensor Initialization                          | 267 |

| 22.15   | Processor Sensors                              | 267 |

| 22.15.1 | Processor Status Sensors                       | 267 |

| 22.15.2 | Processor VRD Over-Temperature Sensor          | 268 |

| 22.15.3    | Digital Thermal Sensor                           |     |

|------------|--------------------------------------------------|-----|

| 22.15.4    | Processor Thermal Control Monitoring (Prochot)   |     |

| 22.15.5    | CPU Missing Sensor                               |     |

| 22.16      | Standard Fan Management                          | 270 |

| 22.16.1    | Hot Swap Fans                                    |     |

| 22.16.2    | Sleep State Fan Control                          | 271 |

| 22.16.3    | Fan Redundancy Detection                         | 271 |

| 22.16.4    | Fan Domains                                      | 271 |

| 22.16.5    | Nominal Fan Speed                                | 271 |

| 22.17      | Acoustic Management (Acoustic Monitoring)        | 271 |

| 22.17.1    | Interactions with DIMM Thermal Management        |     |

| 22.17.2    | ASHRAE Compliance                                |     |

| 22.17.3    | Platform Configuration                           | 272 |

| 22.18      | Power Supply Management Interface (PSMI)         |     |

| 22.19      | Power Unit Management                            |     |

| 22.19.2    | Power Supply Status Sensors                      |     |

| 22.19.3    | Power Unit Redundancy                            |     |

| 22.19.4    | Power Fault Analysis                             |     |

| 22.19.5    | Power Safe                                       |     |

| 22.20      | System Memory RAS and Bus Error Monitoring       |     |

| 22.21      | BMC Self Test                                    | 276 |

| 22.22      | Field Replaceable Unit (FRU) / Fault LED Control |     |

| 22.23      | Hot-Swap Controller                              |     |

| 22.23.1    | Backplane Types                                  |     |

| 22.24      | Intel® Remote Management Module 2 (Intel® RMM2)  |     |

| 22.25      | Memory Region Temperature Monitoring             | 278 |

| 22.25.1    | DIMM Temperature Monitoring                      |     |

| 22.25.2    | Memory Riser Board Temperature Monitoring        |     |

| 22.26      | LAN Leash Event Monitoring                       | 279 |

| 22.27      | SMTP Alerting                                    | 279 |

| 23. BMC Me | essaging Interfaces                              |     |

| 23.1.1     | Server Management Software (SMS) Interface       |     |

| 23.1.2     | SMM Interface                                    |     |

| 23.2       | IPMB Communication Interface                     |     |

| 23.3       | IPMI Serial Feature                              |     |

| 23.3.1                                                                                                                                                                                                                           | COM Port Switching                                                                                                                                                                                                                                                                        | 281                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 23.3.2                                                                                                                                                                                                                           | Terminal Mode                                                                                                                                                                                                                                                                             | 281                                                               |

| 23.3.3                                                                                                                                                                                                                           | Invalid Passwords                                                                                                                                                                                                                                                                         |                                                                   |

| 23.4                                                                                                                                                                                                                             | LAN Interface                                                                                                                                                                                                                                                                             |                                                                   |

| 23.4.1                                                                                                                                                                                                                           | IPMI 1.5 Messaging                                                                                                                                                                                                                                                                        |                                                                   |

| 23.4.2                                                                                                                                                                                                                           | ESB2 Embedded LAN Channels                                                                                                                                                                                                                                                                |                                                                   |

| 23.4.3                                                                                                                                                                                                                           | Address Resolution Protocol (ARP)                                                                                                                                                                                                                                                         |                                                                   |

| 23.4.4                                                                                                                                                                                                                           | Internet Control Message Protocol (ICMP)                                                                                                                                                                                                                                                  |                                                                   |

| 24. Event F                                                                                                                                                                                                                      | Filtering and Alerting                                                                                                                                                                                                                                                                    |                                                                   |

| 24.1                                                                                                                                                                                                                             | Platform Event Filtering (PEF)                                                                                                                                                                                                                                                            |                                                                   |

| 24.2                                                                                                                                                                                                                             | Alert-over-LAN                                                                                                                                                                                                                                                                            |                                                                   |

| 24.3                                                                                                                                                                                                                             | Alert Policies                                                                                                                                                                                                                                                                            |                                                                   |

| 24.4                                                                                                                                                                                                                             | MIB File                                                                                                                                                                                                                                                                                  |                                                                   |

| 25. BMC FI                                                                                                                                                                                                                       | ash Update                                                                                                                                                                                                                                                                                |                                                                   |

| 25.1                                                                                                                                                                                                                             | BMC Flash Update                                                                                                                                                                                                                                                                          |                                                                   |

| 25.1.1                                                                                                                                                                                                                           | Immediate Firmware Update                                                                                                                                                                                                                                                                 |                                                                   |

| 25.1.2                                                                                                                                                                                                                           | On-line Firmware Update                                                                                                                                                                                                                                                                   |                                                                   |

| 26 BIOS-B                                                                                                                                                                                                                        | MC Interactions                                                                                                                                                                                                                                                                           | 200                                                               |

| 20. DI03-D                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                           |                                                                   |

|                                                                                                                                                                                                                                  | S                                                                                                                                                                                                                                                                                         |                                                                   |

| 27. Sensor                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                           |                                                                   |

| 27. Sensor                                                                                                                                                                                                                       | S                                                                                                                                                                                                                                                                                         | 290<br>301                                                        |

| 27. Sensor<br>28. Hot-Sw                                                                                                                                                                                                         | s<br>ap Controller (HSC) Architecture                                                                                                                                                                                                                                                     | <b>290</b><br><b>301</b><br>301                                   |

| <ul><li>27. Sensor</li><li>28. Hot-Sw</li><li>28.1.1</li></ul>                                                                                                                                                                   | s<br>ap Controller (HSC) Architecture<br>I <sup>2</sup> C Interfaces                                                                                                                                                                                                                      | <b>290</b><br><b>301</b><br>301<br>301                            |

| <ul><li>27. Sensor</li><li>28. Hot-Sw</li><li>28.1.1</li><li>28.1.2</li></ul>                                                                                                                                                    | s<br>ap Controller (HSC) Architecture<br>I <sup>2</sup> C Interfaces<br>Serial Peripheral Interface (SPI)                                                                                                                                                                                 | <b>290</b><br>301<br>301<br>301<br>302                            |

| <ul> <li>27. Sensor</li> <li>28. Hot-Sw</li> <li>28.1.1</li> <li>28.1.2</li> <li>28.1.3</li> <li>28.1.4</li> </ul>                                                                                                               | s<br>ap Controller (HSC) Architecture<br>I <sup>2</sup> C Interfaces<br>Serial Peripheral Interface (SPI)<br>GPIO Pins                                                                                                                                                                    | <b>290</b><br>301<br>301<br>301<br>302<br>302                     |

| <ul> <li>27. Sensor</li> <li>28. Hot-Sw</li> <li>28.1.1</li> <li>28.1.2</li> <li>28.1.3</li> <li>28.1.4</li> </ul>                                                                                                               | s<br>ap Controller (HSC) Architecture<br>I <sup>2</sup> C Interfaces<br>Serial Peripheral Interface (SPI)<br>GPIO Pins<br>Serial General-purpose Input / Output (SGPIO)                                                                                                                   | <b>290</b><br>301<br>301<br>301<br>302<br>302<br>303              |

| <ul> <li>27. Sensor</li> <li>28. Hot-Sw</li> <li>28.1.1</li> <li>28.1.2</li> <li>28.1.3</li> <li>28.1.4</li> <li>29. HSC Full</li> </ul>                                                                                         | s<br>ap Controller (HSC) Architecture<br>I <sup>2</sup> C Interfaces<br>Serial Peripheral Interface (SPI)<br>GPIO Pins<br>Serial General-purpose Input / Output (SGPIO)<br>Inctional Specifications                                                                                       | <b>290</b><br>301<br>301<br>302<br>302<br>302<br>303              |

| <ul> <li>27. Sensor</li> <li>28. Hot-Sw</li> <li>28.1.1</li> <li>28.1.2</li> <li>28.1.3</li> <li>28.1.4</li> <li>29. HSC Fu</li> <li>29.1</li> </ul>                                                                             | s<br>ap Controller (HSC) Architecture<br>I <sup>2</sup> C Interfaces<br>Serial Peripheral Interface (SPI)<br>GPIO Pins<br>Serial General-purpose Input / Output (SGPIO)<br>Inctional Specifications<br>Platform Determination                                                             |                                                                   |

| <ul> <li>27. Sensor</li> <li>28. Hot-Sw</li> <li>28.1.1</li> <li>28.1.2</li> <li>28.1.3</li> <li>28.1.4</li> <li>29. HSC Fu</li> <li>29.1</li> <li>29.1.1</li> </ul>                                                             | s<br>ap Controller (HSC) Architecture<br>I <sup>2</sup> C Interfaces<br>Serial Peripheral Interface (SPI)<br>GPIO Pins<br>Serial General-purpose Input / Output (SGPIO)<br>Inctional Specifications<br>Platform Determination<br>Auto Detection of Platform Type                          |                                                                   |

| <ul> <li>27. Sensor</li> <li>28. Hot-Sw</li> <li>28.1.1</li> <li>28.1.2</li> <li>28.1.3</li> <li>28.1.4</li> <li>29. HSC Fu</li> <li>29.1</li> <li>29.1.1</li> <li>29.2</li> </ul>                                               | s<br>ap Controller (HSC) Architecture<br>I <sup>2</sup> C Interfaces<br>Serial Peripheral Interface (SPI)<br>GPIO Pins<br>Serial General-purpose Input / Output (SGPIO)<br>Inctional Specifications<br>Platform Determination<br>Auto Detection of Platform Type<br>System Initialization |                                                                   |

| <ul> <li>27. Sensor</li> <li>28. Hot-Sw</li> <li>28.1.1</li> <li>28.1.2</li> <li>28.1.3</li> <li>28.1.4</li> <li>29. HSC Fu</li> <li>29.1</li> <li>29.1.1</li> <li>29.2</li> <li>29.2.1</li> </ul>                               | s<br>ap Controller (HSC) Architecture                                                                                                                                                                                                                                                     | <b>290</b> 301301301302302303303303303303303303303303303303303304 |

| <ul> <li>27. Sensor</li> <li>28. Hot-Sw</li> <li>28.1.1</li> <li>28.1.2</li> <li>28.1.3</li> <li>28.1.4</li> <li>29. HSC Fu</li> <li>29.1</li> <li>29.2</li> <li>29.2.1</li> <li>29.2.2</li> </ul>                               | s<br>ap Controller (HSC) Architecture                                                                                                                                                                                                                                                     |                                                                   |

| <ul> <li>27. Sensor</li> <li>28. Hot-Sw</li> <li>28.1.1</li> <li>28.1.2</li> <li>28.1.3</li> <li>28.1.4</li> <li>29. HSC Fu</li> <li>29.1</li> <li>29.2</li> <li>29.2.1</li> <li>29.2.2</li> <li>29.2.3</li> </ul>               | s<br>ap Controller (HSC) Architecture                                                                                                                                                                                                                                                     |                                                                   |

| <ul> <li>27. Sensor</li> <li>28. Hot-Sw</li> <li>28.1.1</li> <li>28.1.2</li> <li>28.1.3</li> <li>28.1.4</li> <li>29. HSC Fu</li> <li>29.1</li> <li>29.2</li> <li>29.2.1</li> <li>29.2.2</li> <li>29.2.3</li> <li>29.3</li> </ul> | s<br>ap Controller (HSC) Architecture                                                                                                                                                                                                                                                     |                                                                   |

| 29.6                                                                       | Temperature Monitoring                                                                                                                                                                                                                         |                                                             |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 29.7                                                                       | Disk Management                                                                                                                                                                                                                                |                                                             |

| 29.7.1                                                                     | Drive Fault Light Control                                                                                                                                                                                                                      |                                                             |

| 29.7.2                                                                     | Drive Presence Detection                                                                                                                                                                                                                       |                                                             |

| 29.7.3                                                                     | Enclosure Temperature Sensing                                                                                                                                                                                                                  |                                                             |

| 29.8                                                                       | Slot Status to Fault Light State Mapping                                                                                                                                                                                                       |                                                             |

| 30. HSC IPI                                                                | MB Application and Sensors                                                                                                                                                                                                                     |                                                             |

| 30.1                                                                       | LUNs                                                                                                                                                                                                                                           |                                                             |

| 30.2                                                                       | Sensors                                                                                                                                                                                                                                        |                                                             |

| 30.2.1                                                                     | Digital and Discrete Sensor Formats                                                                                                                                                                                                            |                                                             |

| 30.3                                                                       | Event Message Generation                                                                                                                                                                                                                       |                                                             |

|                                                                            |                                                                                                                                                                                                                                                |                                                             |

| 31. HSC Fir                                                                | mware Update                                                                                                                                                                                                                                   | 310                                                         |

| 31. HSC Fir<br>31.1                                                        | mware Update<br>HSC Update Over IPMB                                                                                                                                                                                                           |                                                             |

|                                                                            | -                                                                                                                                                                                                                                              | 310                                                         |

| 31.1                                                                       | HSC Update Over IPMB                                                                                                                                                                                                                           | 310<br>310                                                  |

| 31.1<br>31.1.1                                                             | HSC Update Over IPMB<br>Entering Firmware Transfer Mode                                                                                                                                                                                        | 310<br>310<br>310                                           |

| 31.1<br>31.1.1<br>31.1.2                                                   | HSC Update Over IPMB<br>Entering Firmware Transfer Mode<br>Exiting Firmware Transfer Mode                                                                                                                                                      |                                                             |

| 31.1<br>31.1.1<br>31.1.2<br>31.1.3                                         | HSC Update Over IPMB<br>Entering Firmware Transfer Mode<br>Exiting Firmware Transfer Mode<br>Firmware Transfer Version                                                                                                                         |                                                             |

| 31.1<br>31.1.1<br>31.1.2<br>31.1.3<br>31.1.4                               | HSC Update Over IPMB<br>Entering Firmware Transfer Mode<br>Exiting Firmware Transfer Mode<br>Firmware Transfer Version<br>Verifying Entry Into Firmware Transfer Mode                                                                          |                                                             |

| 31.1<br>31.1.1<br>31.1.2<br>31.1.3<br>31.1.4<br>31.1.5                     | HSC Update Over IPMB<br>Entering Firmware Transfer Mode<br>Exiting Firmware Transfer Mode<br>Firmware Transfer Version<br>Verifying Entry Into Firmware Transfer Mode<br>Set Program Segment Command                                           |                                                             |

| 31.1<br>31.1.1<br>31.1.2<br>31.1.3<br>31.1.4<br>31.1.5<br>31.1.6<br>31.1.7 | HSC Update Over IPMB<br>Entering Firmware Transfer Mode<br>Exiting Firmware Transfer Mode<br>Firmware Transfer Version<br>Verifying Entry Into Firmware Transfer Mode<br>Set Program Segment Command<br>FLASH Erase and Sequential Programming | 310<br>310<br>310<br>310<br>310<br>310<br>311<br>311<br>311 |

# List of Figures

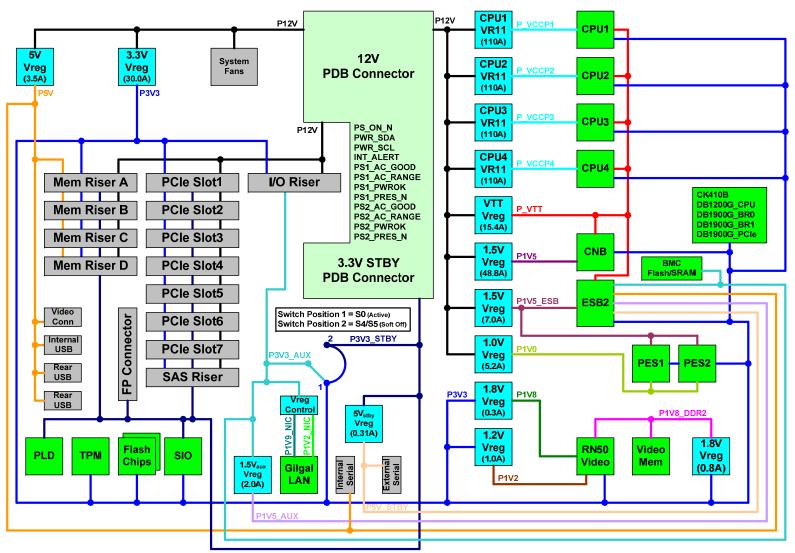

| Figure 1. Main Board Block Diagram                     | 3  |

|--------------------------------------------------------|----|

| Figure 2. Main Board Clock Block Diagram               | 13 |

| Figure 3. Interrupt and Error Logic Block Diagram      | 22 |

| Figure 4. Main board Power Block Diagram               | 25 |

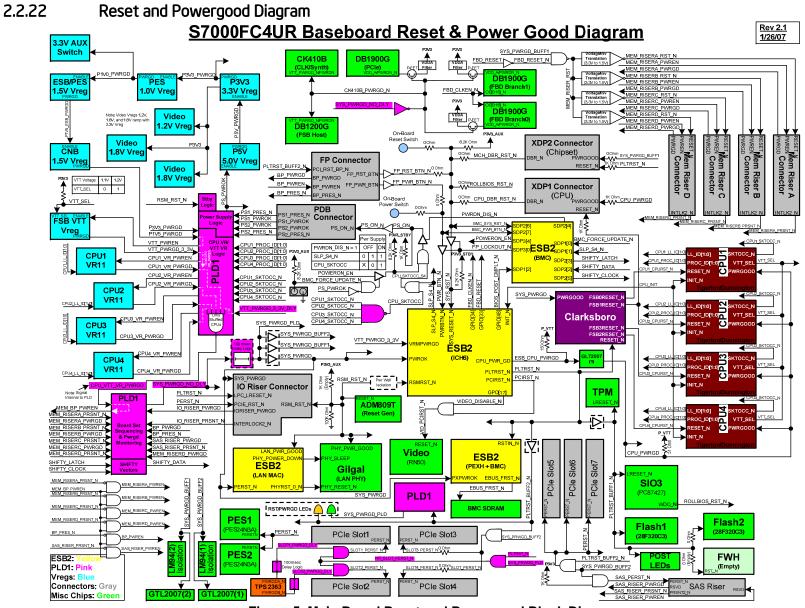

| Figure 5. Main Board Reset and Powergood Block Diagram | 26 |

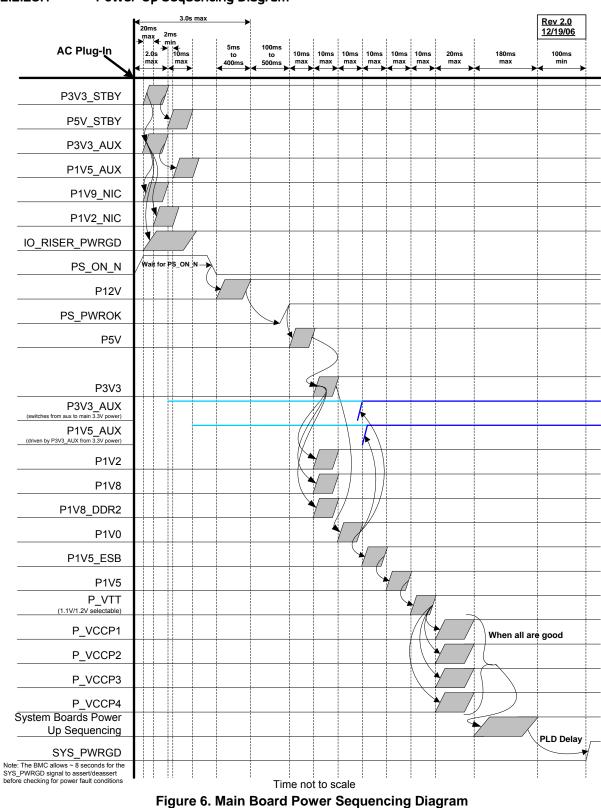

| Figure 6. Main Board Power Sequencing Diagram          | 27 |

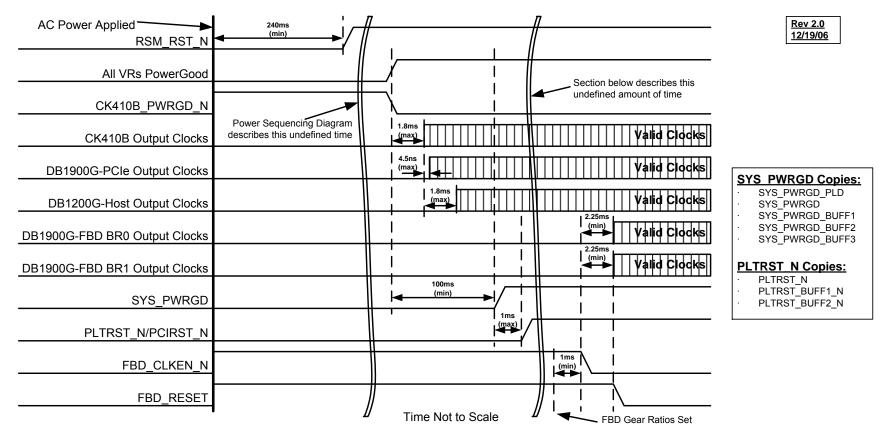

| Figure 7. Main Board Reset Sequencing Diagram          | 28 |

| Figure 8. I/O Riser / Server Management Diagram        | 34 |

| Figure 9. SMBus Block Diagram                          | 35 |

| Figure 10. Hardware Monitoring Block Diagram                                              |     |

|-------------------------------------------------------------------------------------------|-----|

| Figure 11. Main Board PECI Physical Layer Topology                                        | 40  |

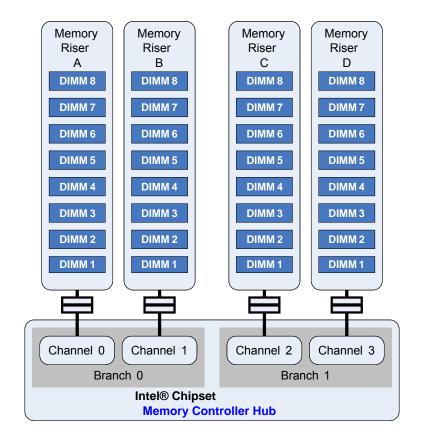

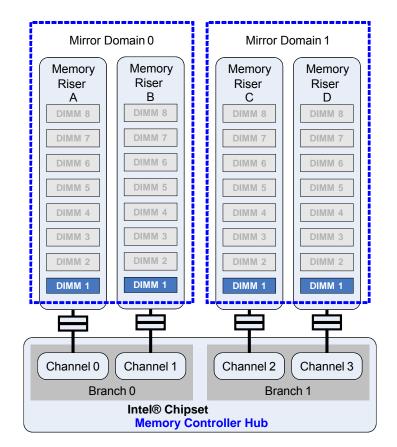

| Figure 12. Fully-Buffered DIMM Topology (Generic)                                         | 50  |

| Figure 13. Memory Riser Functional Diagram                                                | 51  |

| Figure 14. I/O Riser Block Diagram                                                        | 55  |

| Figure 15. SAS Backplane System Block Diagram                                             | 60  |

| Figure 16. VSC410* Block Diagram                                                          | 63  |

| Figure 17. SAS Backplane Reset and Power Good Block Diagram                               | 66  |

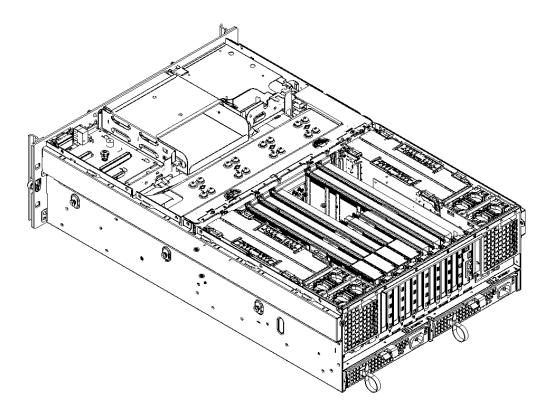

| Figure 18. Intel <sup>®</sup> Server System S7000FC4UR (Front View)                       | 68  |

| Figure 19. Intel <sup>®</sup> Server System S7000FC4UR (rear view with top cover removed) | 69  |

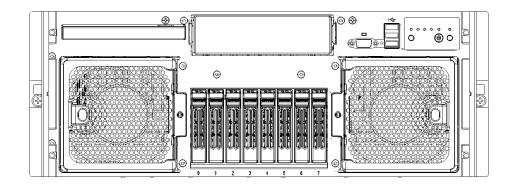

| Figure 20. Front View (without bezel)                                                     | 70  |

| Figure 21. Rear View                                                                      | 72  |

| Figure 22. Slide Rail Mounting Features                                                   | 78  |

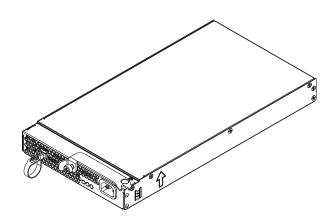

| Figure 23. Power Supply Module                                                            | 79  |

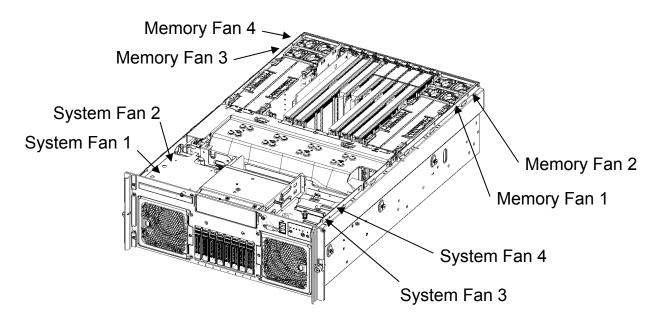

| Figure 24. Fan Locations                                                                  | 79  |

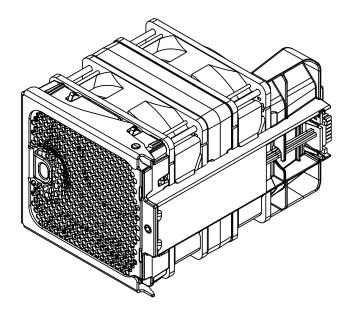

| Figure 25. Front Fan Assembly                                                             | 80  |

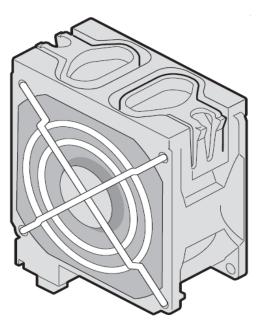

| Figure 26. Rear Fan                                                                       | 80  |

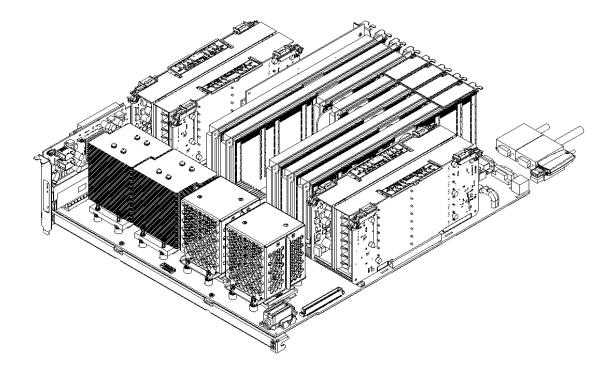

| Figure 27. Main Board and Sheetmetal Tray                                                 | 81  |

| Figure 28. Hard Drive Carrier                                                             | 82  |

| Figure 29. Optical Drive Carrier with Converter Board                                     | 82  |

| Figure 30. Power Distribution Board Layout                                                | 90  |

| Figure 31. Non-LCD Control Module                                                         | 95  |

| Figure 32. PECI Conceptual Quad Socket Block Diagram                                      |     |

| Figure 33. Memory Subsystem Layout                                                        |     |

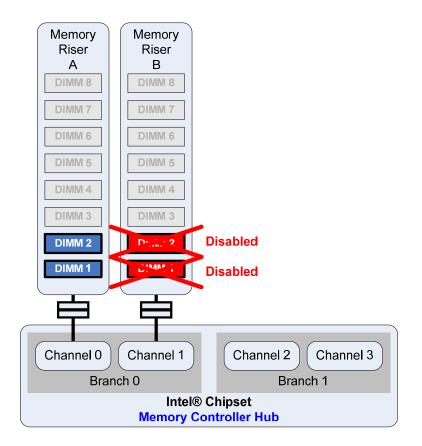

| Figure 34. Memory Population for Single-Channel with Minimal Upgrade                      | 113 |

| Figure 35. Memory Population for Single-Channel with Multiple FBDIMMs                     | 114 |

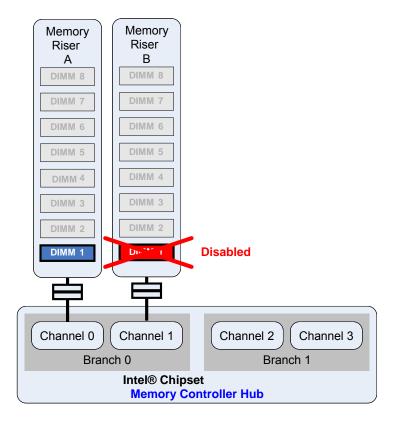

| Figure 36. Memory Population for Single-Channel Failsafe                                  | 115 |

| Figure 37. Memory Population for Single-Channel Failsafe                                  | 116 |

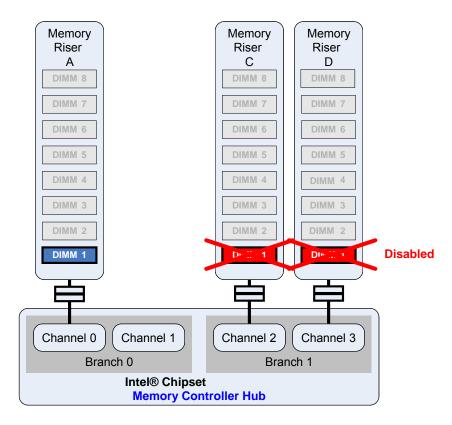

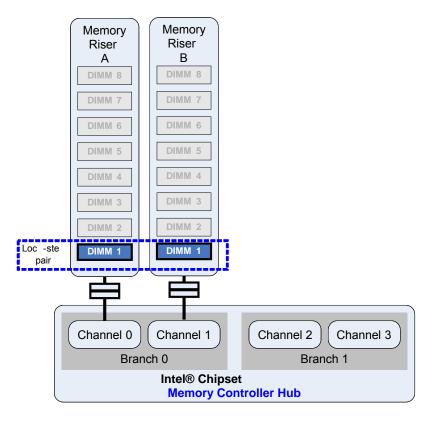

| Figure 38. Memory Population for Dual-Channel Configuration on One Branch                 | 117 |

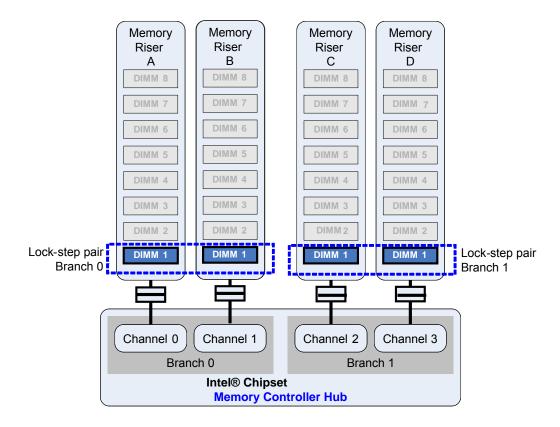

| Figure 39. Memory Population for Dual-Channel Configuration on Both Branches              | 118 |

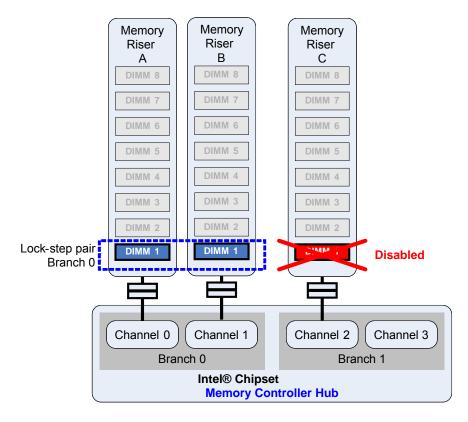

| Figure 40. Memory Population for Dual-Channel Failsafe                                    | 119 |

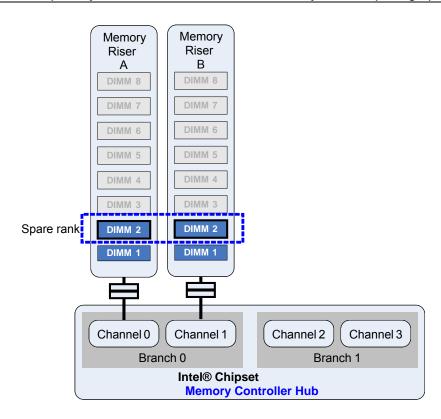

| Figure 41. Memory Population for Dual-Channel on One Branch with Sparing                  |     |

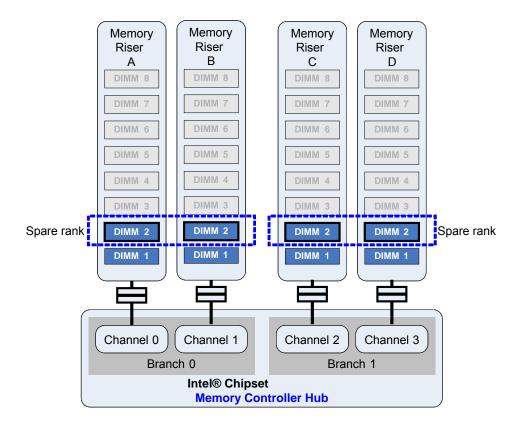

| Figure 42. Memory Population for Dual-Channel on Both Branches with Sparing               | 121 |

| Figure 43. Memory Population for Mirroring                                                | 122 |

| Figure 44. Setup Utility — Main Screen Display                                            |     |

| Figure 45. Setup Utility — Advanced Screen Display                                                 | 157   |

|----------------------------------------------------------------------------------------------------|-------|

| Figure 46. Setup Utility — Processor Configuration Screen Display                                  | 158   |

| Figure 47. Setup Utility — Specific Processor Information Screen Display                           | 160   |

| Figure 48. Setup Utility — Memory Configuration Screen Display                                     | 161   |

| Figure 49. Setup Utility — Configure and View Memory RAS Screen Display                            | 163   |

| Figure 50. Setup Utility — Memory Riser Board Information Screen Display                           | 164   |

| Figure 51. Setup Utility — Mass Storage Controller Configuration Screen Display                    | 165   |

| Figure 52. Setup Utility — Serial Port Configuration Screen Display                                | 168   |

| Figure 53. Setup Utility — USB Controller Configuration Screen Display                             | 169   |

| Figure 54. Setup Utility — PCI Configuration Screen Display                                        | 172   |

| Figure 55. Setup Utility — LAN Configuration Screen Display                                        | 174   |

| Figure 56. Setup Utility — System Acoustic and Performance Configuration Screen Display            | 177 . |

| Figure 57. Setup Utility — Security Configuration Screen Display                                   | 178   |

| Figure 58. Setup Utility — Server Management Configuration Screen Display                          | 180   |

| Figure 59. Setup Utility — Console Redirection Screen Display                                      | 182   |

| Figure 60. Setup Utility — Server Management System Information Screen Display                     | 183   |

| Figure 61. Setup Utility — Intel <sup>®</sup> Remote Management Module Information Screen Display. | 184   |

| Figure 62. Setup Utility — Boot Options Screen Display                                             | 185   |

| Figure 63. Setup Utility — Hard Disk Order Screen Display                                          | 187   |

| Figure 64. Setup Utility — CDROM Order Screen Display                                              | 187   |

| Figure 65. Setup Utility — Floppy Order Screen Display                                             | 188   |

| Figure 66. Setup Utility — Network Device Order Screen Display                                     | 188   |

| Figure 67. Setup Utility — BEV Device Order Screen Display                                         | 189   |

| Figure 68. Setup Utility — Boot Manager Screen Display                                             | 190   |

| Figure 69. Setup Utility — Error Manager Screen Display                                            | 191   |

| Figure 70. Setup Utility — Exit Screen Display                                                     | 192   |

| Figure 71. HSC Interface Routing                                                                   | 301   |

# List of Tables

| Table 1. PCI-Express* Expansion Slot Features | 7  |

|-----------------------------------------------|----|

| Table 2. PCI Hot-plug LEDs                    | 10 |

| Table 3. PCI Interrupt Mapping                | 11 |

| Table 4. IDSEL Mapping                                                     | 11  |

|----------------------------------------------------------------------------|-----|

| Table 5. Arbitration Connections                                           | 11  |

| Table 6. Binary Code Definition                                            | 18  |

| Table 7. POST Code LED Definition                                          | 19  |

| Table 8. Thermal Specifications                                            |     |

| Table 9. FRU Device Location and Size                                      |     |

| Table 10. Secure Mode During ACPI States                                   | 45  |

| Table 11. Memory Riser Max Memory Bandwidth                                | 49  |

| Table 12. Supported Fully-Buffered DIMMs                                   | 52  |

| Table 13. Memory Riser LED Descriptions                                    | 53  |

| Table 14. SAS Hard Drive LED Details                                       | 64  |

| Table 15. I <sup>2</sup> C* Local Bus Addresses                            | 66  |

| Table 16. Global I <sup>2</sup> C* bus Addresses (IPM Bus)                 | 66  |

| Table 17. I <sup>2</sup> C* I/O Bus Addresses                              | 66  |

| Table 18. User-Accessible Connectors, PCI Slots, and LEDs                  | 72  |

| Table 19. Environmental Specifications Summary                             | 75  |

| Table 20. Physical Specifications                                          | 75  |

| Table 21. AC Input Rating                                                  | 84  |

| Table 22. DC Output Voltage Regulation Limits                              | 85  |

| Table 23. 1570W Load Ratings                                               |     |

| Table 24. Over- and Under-Voltage Limits                                   |     |

| Table 25. Over-Current Protection Limits                                   |     |

| Table 26. Output Current Sharing                                           |     |

| Table 27. System ID LED Details                                            | 94  |

| Table 28. Mixed Processor Configurations                                   |     |

| Table 29. Memory Population                                                | 110 |

| Table 30. Leaky Bucket Counter Error Decay Periods                         |     |

| Table 31. Memory Error Reporting Agent Summary                             |     |

| Table 32. Memory Error Handling — POST                                     | 133 |

| Table 33. Memory ECC Error Handling — Runtime, Non-Redundant Configuration | 134 |

| Table 34. Memory ECC Error Handling — Runtime, Redundant Configuration     |     |

| Table 35. Memory RAS Baseboard Management Controller Commands              |     |

| Table 36. Supported On-board PCI Devices                                   | 141 |

| Table 37. PCI Onboard Device Option ROM List                               |     |

| Table 38. PCI Hot-plug Power Indication                                    | 145 |

| Table 39. PCI Hot-plug Attention Indication                                              | . 145 |

|------------------------------------------------------------------------------------------|-------|

| Table 40. Thermal Profile Data SDR Record Format                                         | . 149 |

| Table 41. BIOS Setup — Page Layout                                                       | . 152 |

| Table 42. BIOS Setup — Keyboard Command Bar                                              | . 153 |

| Table 43. Setup Utility — Main Screen Fields                                             | . 156 |

| Table 44. Setup Utility — Processor Configuration Screen Fields                          | . 158 |

| Table 45. Setup Utility — Specific Processor Information Screen Fields                   | . 160 |

| Table 46. Setup Utility — Memory Configuration Screen Fields                             | . 161 |

| Table 47. Setup Utility — Configure and View Memory RAS Screen Fields                    | . 163 |

| Table 48. Setup Utility — Memory Riser Board Information Screen Fields                   | . 165 |

| Table 49. Setup Utility — Mass Storage Controller Configuration Screen Fields            | . 166 |

| Table 50. Setup Utility — Serial Ports Configuration Screen Fields                       | . 168 |

| Table 51. Setup Utility — USB Controller Configuration Screen Fields                     | . 170 |

| Table 52. Setup Utility — PCI Configuration Screen Fields                                | . 173 |

| Table 53. Setup Utility — LAN Configuration Screen Fields                                | . 174 |

| Table 54. Setup Utility — System Acoustic and Performance Configuration Screen Fields    | . 177 |

| Table 55. Setup Utility — Security Configuration Screen Fields                           | . 178 |

| Table 56. Setup Utility — Server Management Configuration Screen Fields                  | . 180 |

| Table 57. Setup Utility — Console Redirection Configuration Fields                       | . 182 |

| Table 58. Setup Utility — Server Management System Information Fields                    | . 183 |

| Table 59. Setup Utility — Intel <sup>®</sup> Remote Management Module Information Fields | . 184 |

| Table 60. Setup Utility — Boot Options Screen Fields                                     | . 185 |

| Table 61. Setup Utility — Hard Disk Order Fields                                         | . 187 |

| Table 62. Setup Utility — CDROM Order Fields                                             | . 187 |

| Table 63. Setup Utility — Floppy Order Fields                                            | . 188 |

| Table 64. Setup Utility — Network Device Order Fields                                    | . 189 |

| Table 65. Setup Utility — BEV Device Order Fields                                        | . 189 |

| Table 66. Setup Utility — Boot Manager Screen Fields                                     | . 190 |

| Table 67. Setup Utility — Error Manager Screen Fields                                    | . 191 |

| Table 68. Setup Utility — Exit Screen Fields                                             | . 192 |