# Intel® Server System P4000SC Family

# **Technical Product Specification**

Intel reference number G63273-001

**Revision 1.0**

**April**, 2012

**Enterprise Platforms and Services Marketing**

# **Revision History**

| Date        | Revision<br>Number | Modifications    |

|-------------|--------------------|------------------|

| April, 2012 | 1.0                | Initial release. |

#### **Disclaimers**

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel®'s Terms and Conditions of Sale for such products, Intel® assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

The Intel® Server System P4000SC and Intel® Server Board S2400SC Family may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel Corporation server baseboards contain a number of high-density VLSI and power delivery components that need adequate airflow to cool. Intel's own chassis are designed and tested to meet the intended thermal requirements of these components when the fully integrated system is used together. It is the responsibility of the system integrator that chooses not to use Intel developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of air flow required for their specific application and environmental conditions. Intel Corporation cannot be held responsible if components fail or the server board does not operate correctly when used outside any of their published operating or non-operating limits.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2012

# **Table of Contents**

| 1. Intel <sup>®</sup> S | Server System P4000SC Overview                | 1  |

|-------------------------|-----------------------------------------------|----|

| 1.1                     | Intergrated System family overview            | 1  |

| 1.1.1                   | Intel® Server System P4304SC2SFEN View        | 3  |

| 1.1.2                   | Intel® Server System P4304SHDR View           | 4  |

| 1.1.3                   | Intel® Server System P4308SC2MHGC View        | 5  |

| 1.2                     | Chassis dimensions                            | 6  |

| 1.3                     | Front control panel feature Overview          | 6  |

| 1.3.1                   | Front Control Panel LED/Button Functionality  | 6  |

| 1.3.2                   | Front Control Panel LED Status                | 8  |

| 1.4                     | Back panel feature Overveiw                   | 8  |

| 1.5                     | Hot swap Hard Drivers and front panel options | 10 |

| 1.6                     | Chassis Security                              | 10 |

| 1.7                     | Front Bezel Features                          | 11 |

| 2. Systen               | n Power Sub-system                            | 13 |

| 2.1                     | 550-W Power Supply                            | 13 |

| 2.1.1                   | Mechanical Overview                           | 13 |

| 2.1.2                   | Temperature Requirements                      | 16 |

| 2.1.3                   | AC Input Requirements                         | 17 |

| 2.1.4                   | Efficiency                                    | 19 |

| 2.1.5                   | DC Output Specification                       | 19 |

| 2.1.6                   | Protection Circuits                           | 24 |

| 2.1.7                   | Control and Indicator Functions               | 25 |

| 2.2                     | 460W Power Supply                             | 26 |

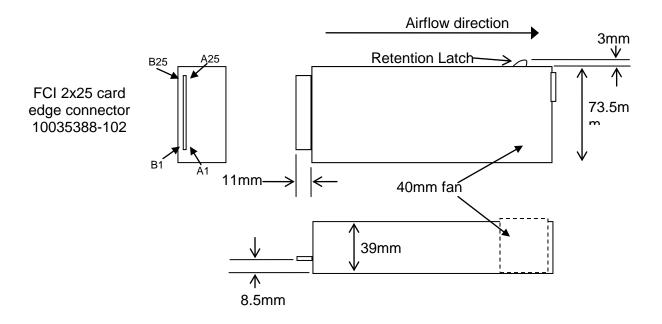

| 2.2.1                   | Mechanical Overview                           | 27 |

| 2.2.2                   | AC Input Requirements                         | 30 |

| 2.2.3                   | Efficiency                                    | 31 |

| 2.2.4                   | DC Output Specification                       | 32 |

| 2.2.5                   | Protection Circuits                           | 36 |

| 2.2.6                   | Control and Indicator Functions               | 37 |

| 2.2.7                   | Thermal CLST                                  | 40 |

| 2.2.8                   | Power Supply Diagnostic "Black Box"           | 40 |

| 4. | Storage | and Peripheral Drive Bays                                             | 85   |

|----|---------|-----------------------------------------------------------------------|------|

|    | 3.5     | Fan Header Connector Descriptions                                     | 84   |

|    | 3.4     | Fan Control                                                           | 83   |

|    | 3.3.2   | Redundant Cooling Solution                                            | 83   |

|    | 3.3.1   | Cooling Solution for Intel® Server System P4304SC2SFEN and P4304SC2SH | IDR8 |

|    | 3.3     | System Fan Configuration                                              | 81   |

|    | 3.2     | Thermal Management Overview                                           | 81   |

|    | 3.1     | Thermal Operation and Configuration Requirements                      | 81   |

| 3. | Therma  | l Management                                                          | 81   |

|    | 2.5.6   | PMBus                                                                 | 80   |

|    | 2.5.5   | PSON Signal                                                           | 79   |

|    | 2.5.4   | PWOK (Power OK) Signal                                                | 79   |

|    | 2.5.3   | Protection Circuits                                                   | 78   |

|    | 2.5.2   | DC Output Specification                                               | 68   |

|    | 2.5.1   | Mechanical Overview                                                   | 67   |

|    | 2.5     | Higer Current Power Common Redundant Power Distribution Board (PDB)   | 66   |

|    | 2.4.6   | PMBus*                                                                | 66   |

|    | 2.4.5   | PSON Signal                                                           | 66   |

|    | 2.4.4   | PWOK (Power OK) Signal                                                | 65   |

|    | 2.4.3   | Protection Circuits                                                   | 65   |

|    | 2.4.2   | DC Output Specification                                               | 56   |

|    | 2.4.1   | Mechanical Overview                                                   | 54   |

|    | 2.4     | Lower Current Common Redundant Power Distribution Board (PDB)         | 54   |

|    | 2.3.9   | Firmware Uploader                                                     | 54   |

|    | 2.3.8   | Power Supply Diagnostic "Black Box"                                   | 53   |

|    | 2.3.7   | Thermal CLST                                                          | 53   |

|    | 2.3.6   | Control and Indicator Functions                                       | 51   |

|    | 2.3.5   | Protection Circuits                                                   | 50   |

|    | 2.3.4   | DC Output Specification                                               | 46   |

|    | 2.3.3   | Efficiency                                                            | 46   |

|    | 2.3.2   | AC Input Requirements                                                 | 43   |

|    | 2.3.1   | Mechanical Overview                                                   | 41   |

|    | 2.3     | 750-W Power Supply                                                    | 41   |

|    | 2.2.9   | Firmware Uploader                                                     | 40   |

| 4          | 1.1       | 4x 3.5" Hot swap HDD support           | 85   |

|------------|-----------|----------------------------------------|------|

|            | 4.1.1     | Key Features                           | 85   |

|            | 4.1.2     | Board Layout                           | 85   |

|            | 4.1.3     | 4x3.5" HSBP Functional Description     | 87   |

|            | 4.1.4     | 4x3.5" HSBP Connector List and Pinouts | 90   |

|            | 4.1.5     | Pinouts                                | 91   |

|            | 4.1.6     | 4x3.5" HSBP Cabling Requirements       | 91   |

| 2          | 1.2       | 8x3.5" Hot Swap HDD support            | 92   |

|            | 4.2.1     | 3.5" Drive Hot-Swap Backplane Overview | 93   |

|            | 4.2.1     | Overview                               | 93   |

|            | 4.2.2     | 8x 3.5" HSBP Functional Description    | 94   |

|            | 4.2.3     | 8x3.5" HSBP Connector List and Pinouts | 97   |

|            | 4.2.4     | 8x3.5" HSBP Cabling Requirements       | 99   |

| 4          | 1.3       | SAS Expander Card Option               | 99   |

|            | 4.3.2     | Protocol Support                       | .102 |

|            | 4.3.3     | SAS Expander Features                  | .102 |

| 4          | 1.4       | Optical Drive Support                  | .102 |

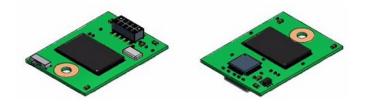

| 4          | 1.5       | Low Profile eUSB SSD Support           | .103 |

| 5.         | Reliabili | ity and Availability                   | .104 |

| 5          | 5.1       | Mean Time between Failure              | .104 |

| <b>ò</b> . | Environ   | mental Limits                          | .106 |

| 6          | 5.1       | System Environment Limits              | .106 |

| 6          | 5.2       | System Environmental Testing           | .107 |

| ٩p         | pendix A: | Integration and Usage Tips             | .108 |

| ilc        | ssary     |                                        | .109 |

| ₹e         | ference D | Occuments                              | .111 |

# **List of Figures**

| Figure 1. Internal Chassis View of Intel® Server System P4304SC2SFEN                                       | 3  |

|------------------------------------------------------------------------------------------------------------|----|

| Figure 2. Internal Chassis View of Intel® Server System P4304SC2SHDR                                       | 4  |

| Figure 3. Internal Chassis View of Intel® Server System P4308SC2MHGC                                       | 5  |

| Figure 11. Front Control Panel LED/Button Arragement                                                       | 6  |

| Figure 12. Back panel feature (for P4000SC2SFEN)                                                           | 9  |

| Figure 13. Hot-Swap Hard Disk Drive Cage                                                                   | 10 |

| Figure 14. Front Closed Chassis View for Fixed Hard Drives Configuration                                   | 11 |

| Figure 15. Front Closed Chassis View for Hot-swap Hard Drives Configuration                                | 12 |

| Figure 23. Mechanical Drawing for 550W Power Supply Enclosure                                              | 13 |

| Figure 24. Output Cable Harness for 550W Power Supply                                                      | 14 |

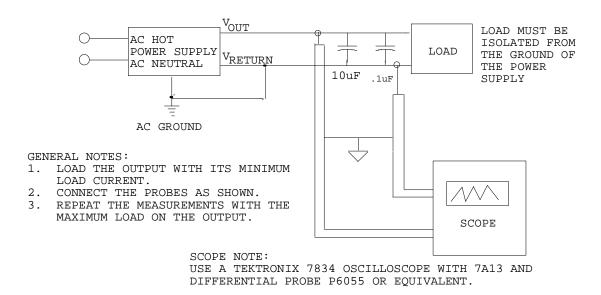

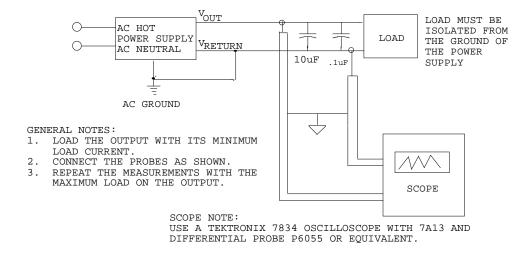

| Figure 25. Differential Noise test setup                                                                   | 22 |

| Figure 26. Output Voltage Timing                                                                           | 23 |

| Figure 27. Turn On/Off Timing (Power Supply Signals)                                                       | 24 |

| Figure 28. PSON# Required Signal Characteristic                                                            | 26 |

| Figure 29. Power Supply Outline Drawing                                                                    | 27 |

| Figure 30. Differential Noise test setup                                                                   | 35 |

| Figure 31. Turn On/Off Timing (Power Supply Signals)                                                       | 36 |

| Figure 32. PSON# Required Signal Characteristic                                                            | 38 |

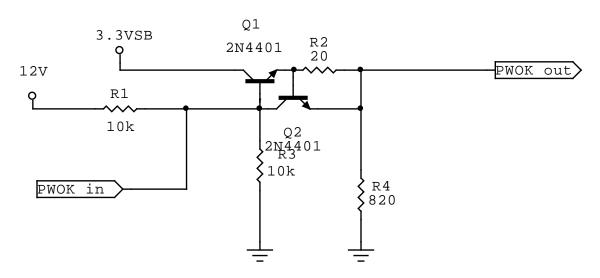

| Figure 33. Implementation of the Power Ok Circuits                                                         | 39 |

| Figure 16. 750-W Power Supply Outline Drawing                                                              | 41 |

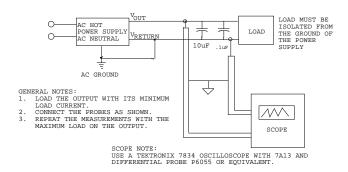

| Figure 17. Differential Noise test setup                                                                   | 49 |

| Figure 18. Turn On/Off Timing (Power Supply Signals)                                                       | 50 |

| Figure 19. PSON# Required Signal Characteristic                                                            | 52 |

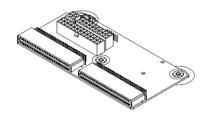

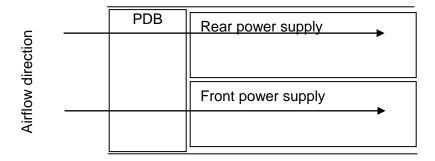

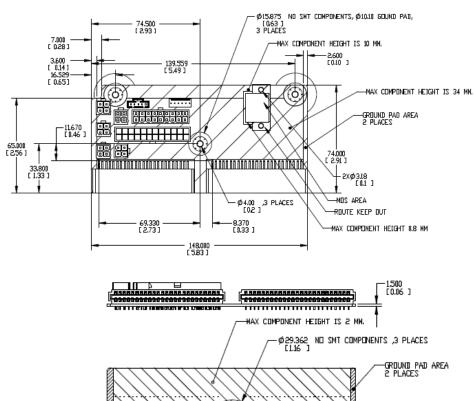

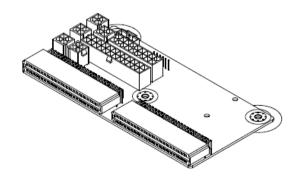

| Figure 34. Outline Drawing                                                                                 | 55 |

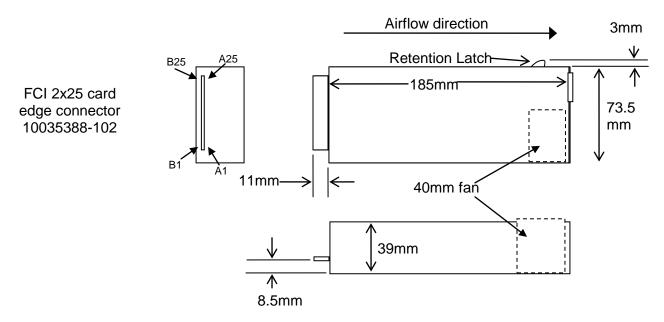

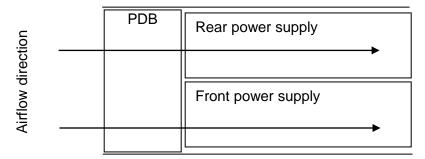

| Figure 35. Airflow Diagram                                                                                 | 56 |

| Figure 36. Differential Noise test setup                                                                   | 64 |

| Figure 29. Outline Drawing                                                                                 | 67 |

| Figure 30. Airflow Diagram                                                                                 | 68 |

| Figure 31. Differential Noise test setup                                                                   | 77 |

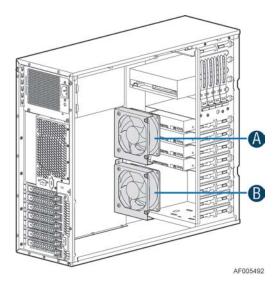

| Figure 32. Chassis Fans default location in Intel <sup>®</sup> Server System P4304SC2SFEN and P4304SC2SHDR | 82 |

| Figure 33. Hot-swap Fans in Intel <sup>®</sup> Server System P4308SC2MHGC                                  | 83 |

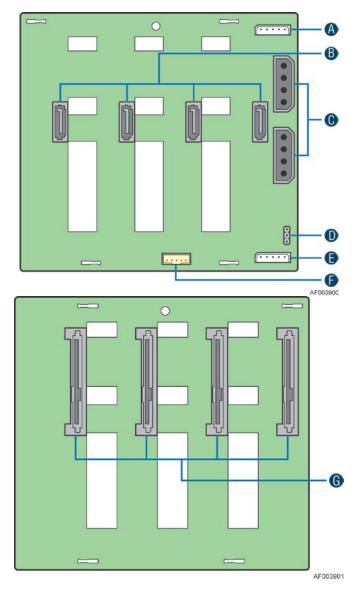

| Figure 42. 4x3.5" HSBP Board Layout                                          | 86  |

|------------------------------------------------------------------------------|-----|

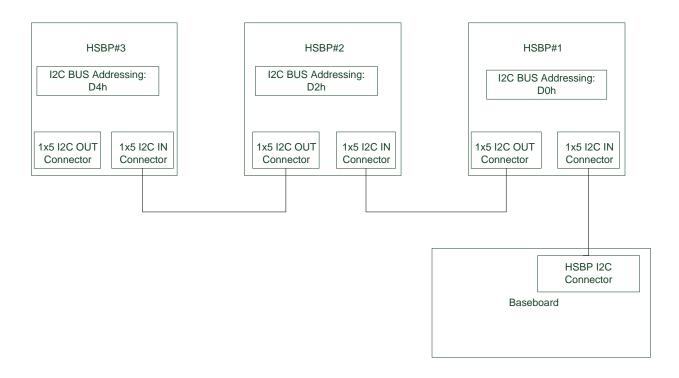

| Figure 43. 4x 3.5" HSBP I2C Connectivity                                     | 89  |

| Figure 38. 3.5" Hard Disk Drive Cage                                         | 92  |

| Figure 39. 3.5" Hard Disk Drive Support - LED Status                         | 92  |

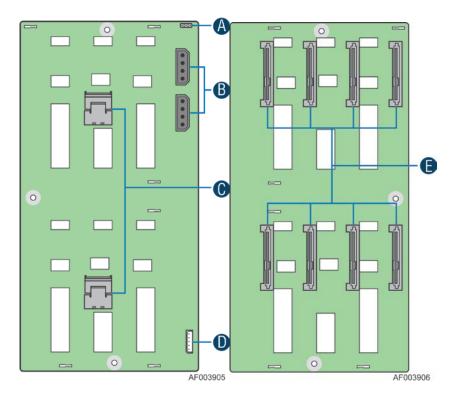

| Figure 55. 8x3.5" HSBP Board Layout                                          | 94  |

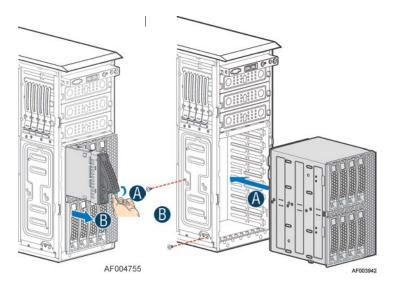

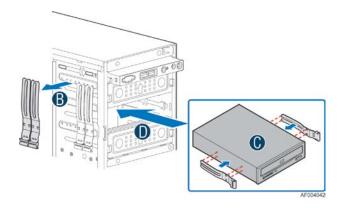

| Figure 42. Internal SAS Expander Installation                                | 99  |

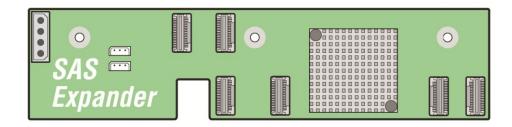

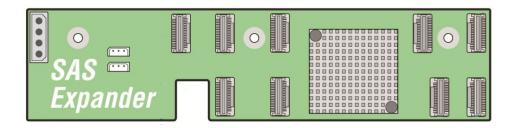

| Figure 43. Internal 24-Port SAS Expander Card                                | 100 |

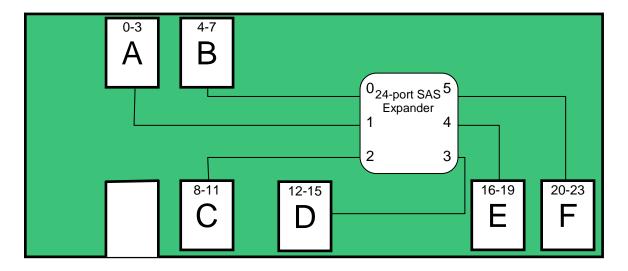

| Figure 44. 24-Port Expander SAS Connector/Drive Identification Block Diagram | 100 |

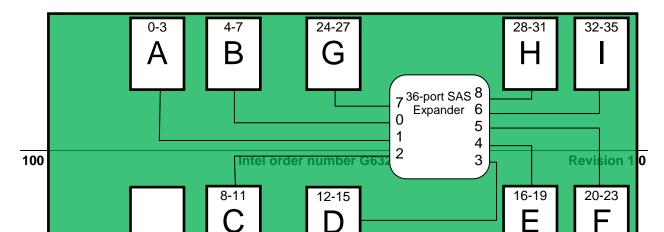

| Figure 45. Internal 36-Port SAS Expander Card                                | 100 |

| Figure 46. 36-Port Expander SAS Connector/Drive Identification Block Diagram | 101 |

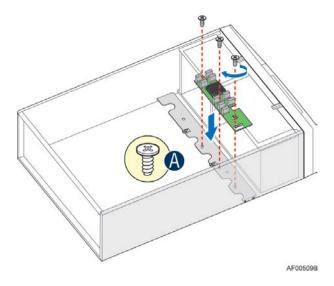

| Figure 47. Optical Drive                                                     | 103 |

| Figure 48. eUSB SSD Support                                                  | 103 |

# **List of Tables**

| Table 1. Intel <sup>®</sup> Server System P4000SC configuration base feature | 2  |

|------------------------------------------------------------------------------|----|

| Table 4. Power/Sleep LED Functional States                                   | 7  |

| Table 5. Front Control Panel LED Status                                      | 8  |

| Table 25. Power Supply Cable Lengths                                         | 15 |

| Table 26. P1 Main Power Connector                                            | 15 |

| Table 27. P2 Processor#1 Power Connector                                     | 16 |

| Table 28. P3 Processor#1 Power Connector                                     | 16 |

| Table 29. Peripheral Power Connectors                                        | 16 |

| Table 30. SATA Power Connector                                               | 16 |

| Table 31. Thermal Requirements                                               | 17 |

| Table 32. Power Factor Requirements for Computer Servers                     | 17 |

| Table 33. AC Input Voltage Range                                             | 17 |

| Table 34. AC Line Holdup time                                                | 18 |

| Table 35. AC Line Sag Transient Performance                                  | 18 |

| Table 36. AC Line Surge Transient Performance                                | 18 |

| Table 37. Silver Efficiency Requirement                                      | 19 |

| Table 38. Over Voltage Protection Limits                                     | 19 |

| Table 39. Loading Conditions                                                 | 20 |

| Table 40. Voltage Regulation Limits                                          | 20 |

| Table 41. Transient Load Requirements                                        | 20 |

| Table 42. Capacitive Loading Conditions                                      | 21 |

| Table 43. Ripples and Noise                                                  | 22 |

| Table 44. Output Voltage Timing                                              | 22 |

| Table 45. Turn On/Off Timing                                                 | 23 |

| Table 46. Over Current Limits                                                | 24 |

| Table 47. PSON# Signal Characteristic                                        | 25 |

| Table 48. PWOK Signal Characteristics                                        | 26 |

| Table 49. DC Output Selector                                                 | 27 |

| Table 50. LED Characteristics                                                | 28 |

| Table 51. LED Indicator States                                               | 28 |

| Table 52. Environmental Requirements                                         | 29 |

| Table 53. AC Input Voltage Range                                             | 30 |

| Table 54 AC Line Sag Transient Performance                  | 31 |

|-------------------------------------------------------------|----|

| Table 55. AC Line Surge Transient Performance               | 31 |

| Table 56. Gold Efficiency Requirement                       | 32 |

| Table 57. Minimum Load Ratings                              | 32 |

| Table 58. Voltage Regulation Limits                         | 32 |

| Table 59. Transient Load Requirements                       | 33 |

| Table 60. Capacitive Loading Conditions                     | 33 |

| Table 61. Ripples and Noise                                 | 34 |

| Table 62. Timing Requirements                               | 35 |

| Table 63. Over Current Protection                           | 37 |

| Table 64. Over Voltage Protection (OVP) Limits              | 37 |

| Table 65. PSON# Signal Characteristic                       | 38 |

| Table 66. PWOK Signal Characteristics                       | 38 |

| Table 67. SMBAlert# Signal Characteristics                  | 40 |

| Table 6. DC Output Connector                                | 41 |

| Table 7. LED Characteristics                                | 42 |

| Table 8. Power Supply LED Functionality                     |    |

| Table 9. Environmental Requirements                         | 43 |

| Table 10. Power Factor Requirements for Computer Servers    | 43 |

| Table 11. AC Input Voltage Range                            |    |

| Table 12. AC Line Holdup Time                               | 44 |

| Table 13. AC Line Sag Transient Performance                 | 45 |

| Table 14. AC Line Surge Transient Performance               | 45 |

| Table 15. Silver Efficiency Requirement                     | 46 |

| Table 16. Minimum Load Ratings                              | 46 |

| Table 17. Voltage Regulation Limits                         | 47 |

| Table 18. Transient Load Requirements                       | 47 |

| Table 19. Capacitive Loading Conditions                     | 47 |

| Table 20. Ripples and Noise                                 | 48 |

| Table 21. Timing Requirements                               |    |

| Table 22. Over Current Protection                           | 51 |

| Table 23. Over Voltage Protection (OVP) Limits for 750W PSU | 51 |

| Table 24. PSON# Signal Characteristic                       | 51 |

| Table 25 PWOK Signal Characteristics                        | 52 |

| Table 26. | SMBAlert# Signal Characteristics                    | .53 |

|-----------|-----------------------------------------------------|-----|

| Tabel 68. | Thermal Requirements                                | .56 |

| Table 69. | Input Connector and Pin Assignment Diagrams         | .56 |

| Table 70. | PDB Cable Length                                    | .57 |

| Table 71. | P1 Baseboard Power Connector                        | .58 |

| Table 72. | P0 Processor Power Connector                        | .58 |

| Table 73. | P1 Processor Power Connector                        | .58 |

| Table 74. | Power Signal Connector                              | .59 |

| Table 75. | Aux baseboard power connector                       | .59 |

| Table 76. | P8, P9, P10, P11 Legacy Peripheral Power Connectors | .59 |

| Table 77. | P7 Legacy Peripheral Power Connectors               | .59 |

| Table 78. | SATA Peripheral Power Connectors                    | .59 |

| Table 79. | Remote Sense Connection Points                      | .60 |

| Table 80. | Remote Sense Requirements                           | .60 |

| Table 81. | 12V Rail Distribution                               | .61 |

| Table 82. | Hard Drive 12V rail configuration options           | .61 |

| Table 83. | DC/DC Converters Load Ratings                       | .62 |

| Table 84. | 5VSB Loading                                        | .62 |

| Table 85. | Voltage Regulation Limits                           | .62 |

| Table 86. | Transient Load Requirements                         | .63 |

| Table 87. | Capacitive Loading Conditions                       | .63 |

| Table 88. | Ripple and Noise                                    | .63 |

| Table 89. | Output Voltage Timing                               | .64 |

| Table 90. | PDB Over Current Protection Limits/240VA Protection | .65 |

| Table 91. | Over Voltage Protection (OVP) Limits                | .65 |

| Table 92. | System PWOK Requirements                            | .66 |

| Table 93. | PDB addressing                                      | .66 |

| Table 67. | Thermal Requirements                                | .68 |

| Table 68. | Input Connector and Pin Assignment Diagrams         | .69 |

| Table 69. | PDB Cable Length                                    | .69 |

| Table 70. | P1 Baseboard Power Connector                        | .70 |

| Table 71. | P0 Processor Power Connector                        | .71 |

| Table 72. | P1 Processor Power Connector                        | .71 |

| Table 73. | Power Signal Connector                              | .71 |

| Table 74. P12 12V connectors                                  | 72 |

|---------------------------------------------------------------|----|

| Table 75. P13 - P16 12V connectors                            | 72 |

| Table 76. P8, P9, P10, P11 Legacy Peripheral Power Connectors | 72 |

| Table 77. P7Legacy Peripheral Power Connectors                | 72 |

| Table 78. SATA Peripheral Power Connectors                    | 72 |

| Table 79. Remote Sense Connection Points                      | 73 |

| Table 80. Remote Sense Requirements                           | 73 |

| Table 81. 12V Rail Distribution                               | 74 |

| Table 82. Hard Drive 12V rail configuration options           | 75 |

| Table 83. DC/DC Converters Load Ratings                       | 75 |

| Table 84. 5VSB Loading                                        | 75 |

| Table 85. Voltage Regulation Limits                           | 76 |

| Table 86. Transient Load Requirements                         |    |

| Table 87. Capacitive Loading Conditions                       | 76 |

| Table 88. Ripple and Noise                                    | 77 |

| Table 89. Output Voltage Timing                               | 78 |

| Table 90. PDB Over Current Protection Limits/240VA Protection | 79 |

| Table 91. Over Voltage Protection (OVP) Limits                |    |

| Table 92. System PWOK Requirements                            | 79 |

| Table 93. PDB addressing                                      |    |

| Table 98. 4x3.5" HSBP Microcontroller Pinouts                 |    |

| Table 99. 4x3.5" HSBP SATA 6X Mode Host Jumper Block          |    |

| Table 100. Romley LED Functionality                           |    |

| Table 101. HDD Activity LED Functionality                     |    |

| Table 102. 4x3.5" HSBP Connector List                         |    |

| Table 103. 4x3.5" HSBP SGPIO Connector Pinouts                |    |

| Table 104. 4x3.5" HSBP I2C(In) Connector Pinouts              |    |

| Table 105. 4x3.5" HSBP I2C (Out) Connector List               |    |

| Table 106. 4x3.5" HSBP Power Connector Pinouts                |    |

| Table 96. 3.5" Hard Disk Drive Status LED States              |    |

| Table 97. 3.5" Hard Disk Drive Activity LED States            |    |

| Table 151. 8x3.5" HSBP Microcontroller Pinouts                |    |

| Table 152. 8x3.5" HSBP SATA 6X Mode Host Jumper Block         |    |

| Table 153. LED Functionality                                  | 96 |

| Table 154. BP HDD Activity LED Functionality                | 96  |

|-------------------------------------------------------------|-----|

| Table 155. 8x3.5" HSBP Connector List and Pinouts           | 97  |

| Table 156. 1x5 Pin I2C Connector (In)                       | 97  |

| Table 157.1x4 Pin Power Connector                           | 97  |

| Table 158. 36Pin Input RA Mini-SAS Connector                | 98  |

| Table 159.1x3 SATA 6X Host Jumper                           | 99  |

| Table 98. Calculated Mean Time Between Failure P4304SC2SFEN | 104 |

| Table 98. Calculated Mean Time Between Failure P4304SC2SHDR | 104 |

| Table 98. Calculated Mean Time Between Failure P4308SC2MHGC | 105 |

| Table 99. System Environment Limits Summary                 | 106 |

<This page is intentionally left blank.>

## Intel® Server System P4000SC Overview

Intel® Server System P4000SC is 4U pedestal length server chassis that is designed to support Intel® Server Board S2400SC. This chapter provides a high-level overview of the chassis features. Greater detail for each major chassis component or feature is provided in the following chapters.

#### 1.1 Intergrated System family overview

Intel® Server System P4000SC makes extensive use of tool-less hardware features and, depending on configuration and upgrade features, provides redundant power supply, redundant cooling and hot swappable hard drives capability. Intel® Server System P4000SC comes with the following configuration:

#### Your Intel® Server System P4304SC2SFEN ships with the following items:

- One Intel<sup>®</sup> Server Board S2400SC

- One fixed 550W power supply, installed in the chassis

- One fixed system CPU zone fan, installed in the chassis

- One fixed system PCI zone fan, installed in the chassis

- Four fixed HDD carrier tray, installed in the chassis

- Front panel, installed in the chassis

- Front Bezel for fixed hard drive, EMI shield, 5.25" bay filler

- Pre-routing cables

- Two heat sinks

#### Your Intel® Server System P4304SC2SHDR ships with the following items:

- One Intel<sup>®</sup> Server Board S2400SC

- Two CRPS 460W power supply, installed in the chassis

- One fixed system CPU zone fan, installed in the chassis

- One fixed system PCI zone fan, installed in the chassis

- 4x3.5 hot swap HDD cage with four 3.5" HDD carrier, installed in the chassis

- One Intel® Remote Management Module 4 Lite, installed on the server board.

- Front panel, installed in the chassis

- Front Bezel for hot-swap hard drive, EMI shield, 5.25" bay filler

- Pre-routing cables

- Two heat sinks

#### Your Intel® Server System P4308SC2MHGC ships with the following items:

- One Intel<sup>®</sup> Server Board S2400SC

- Two CRPS 750W power supply, installed in the chassis

- Five hot-swap redundant system fans, installed in the chassis

- 8x3.5" hot-swap HDD cage with eight 3.5" HDD carrier, installed in the chassis

- One Intel® Remote Management Module 4, installed on the server board.

- Front panel, installed in the chassis

- Front Bezel for hot-swap hard drive, EMI shield, 5.25" bay filler

- Pre-routing cables

- Two heat sinks

The following table summarizes the features for all System combinations:

Table 1. Intel<sup>®</sup> Server System P4000SC configuration base feature

| Configuration                                 | P4304SC2SFEN                                                                                                                                                    | P4304SC2SHDR                                                                              | P4308SC2MHGC                                                                                  |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|

| Intel <sup>®</sup> Server<br>Board<br>Support | Intel® Server Board S2400SC                                                                                                                                     |                                                                                           |                                                                                               |  |

| Power                                         | 550W non-redundant fixed power supply                                                                                                                           | Two 460W redundant hot-swap power supplies                                                | Two 750W redundant hot-swap power supplies                                                    |  |

| System<br>Cooling                             | Two 92x32mm non-redundant fa                                                                                                                                    | ns                                                                                        | Five 80x38mm redundant hot swap fans                                                          |  |

| Peripherals<br>Bays                           | Three (3) half height 5-1/4" bays for optical devices.                                                                                                          |                                                                                           |                                                                                               |  |

| Drive Bays                                    | Includes one fixed drive bay.<br>Supports up to four 3.5" fixed<br>hard drives.                                                                                 | Includes one 4x3.5" hot-swap hard drive cage. Supports up to four 3.5" fixed hard drives. | Includes one 8x3.5" hot-swap hard drive cage. Supports up to eight 3.5" hot-swap hard drives. |  |

| Expansion<br>Slots                            | Support up to six (6) full height, f                                                                                                                            | ull length PCI form factor cards med                                                      | chanically.                                                                                   |  |

| Front Panel                                   |                                                                                                                                                                 | utton, NMI Button, ID Button with LE<br>, two USB ports, Optional front seria             |                                                                                               |  |

| Appearance                                    | Color: Cosmetic black (GE 701 o                                                                                                                                 | or equivalent), service Intel blue, hot                                                   | swap Intel green.                                                                             |  |

|                                               | Support for Intel standard front panel or LCD                                                                                                                   |                                                                                           |                                                                                               |  |

| Dimensions<br>Pedestal                        | 17.24 in (438 mm) x 6.81 in (173mm) x 22.05 in (560 mm) (Height X Width X Depth)  17.24 in (438 mm) x 6.81 in (173mm) x 25 in (612 mm) (Height X Width X Depth) |                                                                                           |                                                                                               |  |

| Optional<br>Accessory<br>Kits                 | Zephyr flash storage, RMM4-lite module,                                                                                                                         | modules, TPM module, dedicated N                                                          | IIC module, Expander Card                                                                     |  |

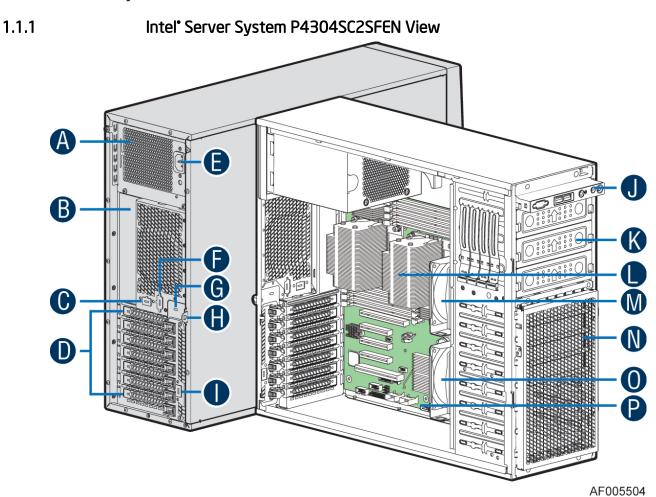

- A. 550-W Fixed Power Supply

- B. I/O Ports

- C. Alternate RMM4 Knockout

- D. PCI Add-in Board Slot Covers

- E. AC Input Power Connector

- F. Serial Port Knockout

- G. A Kensington\* Cable Lock Mounting Hole

- H. Padlock Loop

- I. RMM4 Knockout

- J. Front Control Panel

- K. 5.25" Peripheral Bays

- L. Heatsink

- M. Fixed CPU Zone System Fan

- N. EMI Filler

- O. Fixed PCI Zone System Fan P. Intel® Server Board S2400SC

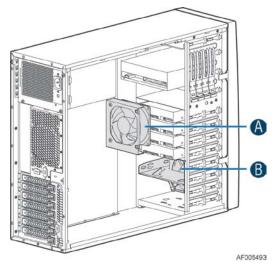

Figure 1. Internal Chassis View of Intel® Server System P4304SC2SFEN

1.1.2

#

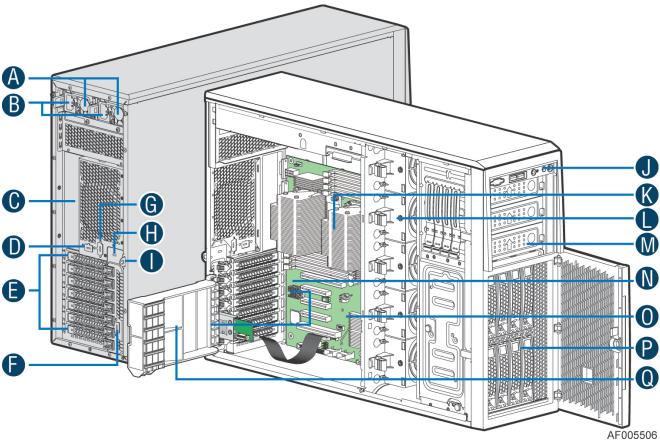

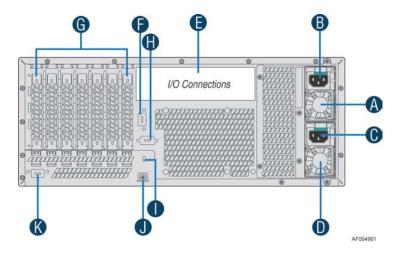

- A. 460-W Hot Swap Power Supply (Two)

- B. AC Input Power Connector

- C. I/O Ports

- D. Alternate RMM4 Knockout

- E. PCI Add-in Board Slot Covers

- F. Alternate Serial Port Knockout

- G. A Kensington\* Cable Lock Mounting Hole

- H. Padlock Loop

- I. RMM4 Knockout

- J. Front Control Panel

- K. 5.25" Peripheral Bays

- L. Heat-sink

- M. Fixed System Fan

- N. 4x3.5" Hot-swap HDD Cage

- O. Intel® Remote Management Module 4 Lite

- P. Intel® Server Board S2400SC

- Q. EMI Cover

Figure 2. Internal Chassis View of Intel® Server System P4304SC2SHDR

AF005505

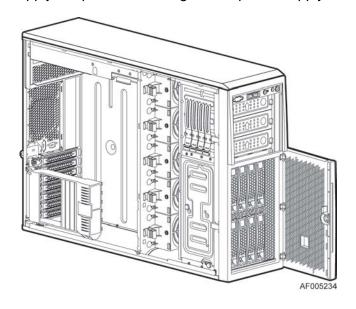

#### 1.1.3 Intel® Server System P4308SC2MHGC View

- A. 750-W Redundant Power Supply (Two)

- B. AC Input Power Connector

- C. I/O Ports

- D. Alternate RMM4 Knockout

- E. PCI Add-in Board Slot Covers

- F. RMM4 Knockout

- G. Alternate Serial Port Knockout

- H. A Kensington\* Cable Lock Mounting Hole

- I. Padlock Loop

- J. Front Control Panel

- K. Heat-sink

- L. Hot-swap system fan

- M. 5.25" Peripheral Bays

- N. Intel® Server Board S2400SC

- O. Intel® Remote Management Module 4

- P. 8x3.5" Hot-swap HDD Cage

- Q. PCI-e Retainer

Figure 3. Internal Chassis View of Intel® Server System P4308SC2MHGC

#### 1.2 Chassis dimensions

Length:

656 mm (without bezel) 698.3 mm (with bezel)

Height:

438 mm

Width:

173 mm

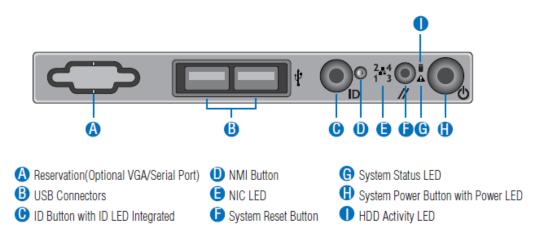

#### 1.3 Front control panel feature Overview

This Front Control Panel conforms to SSI specification with one exception that up to 4 LAN act/link LEDs are supported. The common front panel can support either the standard SSI 2x12 cable interconnect (2 LAN ports) or an Intel customized 2x15 cable interconnect (4 LAN ports).

The Front Control Panel has the following features:

- Power button with integrated power LED (green)

- System ID with integrated ID LED (blue)

- System Status LED (green/amber)

- System Reset button

- HDD activity LED

- 4 NIC activity/link LEDs

- NMI button

- Two USB ports

#### 1.3.1 Front Control Panel LED/Button Functionality

The following figure shows the layout of Front Control Panel:

Figure 4. Front Control Panel LED/Button Arragement

**ID Button with integrated ID LED** – Toggles the integrated ID LED and the Blue server board ID LED on and off. The ID LED is used to identify the system for maintenance when installed in a rack of similar server systems. The ID LED can also be toggled on and off remotely using the IPMI "Chassis Identify" command which will cause the LED to blink for 15 seconds.

**NMI Button** – When the NMI button is pressed, it puts the server in a halt state and issues a non-maskable interrupt (NMI). This can be useful when performing diagnostics for a given issue where a memory download is necessary to help determine the cause of the problem. To prevent an inadvertent system halt, the actual NMI button is located behind the Front Control Panel faceplate where it is only accessible with the use of a small tipped tool like a pin or paper clip.

**Network Activity LEDs (NIC LED)** – The Front Control Panel includes an activity LED indicator for each on-board Network Interface Controller (NIC). When a network link is detected, the LED will turn on solid. The LED will blink once network activity occurs at a rate that is consistent with the amount of network activity that is occurring.

**System Reset Button** – When pressed, this button will reboot and re-initialize the system.

**System Status LED** – The System Status LED is a bi-color (Green/Amber) indicator that shows the current health of the server system. The system provides two locations for this feature; one is located on the Front Control Panel, the other is located on the back edge of the server board, viewable from the back of the system. Both LEDs are tied together and will show the same state. The System Status LED states are driven by the on-board platform management sub-system.

**System Power Button with power LED** – Toggles the system power on and off. This button also functions as a sleep button if enabled by an ACPI compliant operating system. Pressing this button will send a signal to the iBMC, which will either power on or power off the system. The integrated LED is a single color (Green) and is capable of supporting different indicator states as defined in the following table.

State Power LED Description Mode Power-off Non-ACPI Off System power is off, and the BIOS has not initialized the chipset. Power-on Non-ACPI On System power is on S5 ACPI Off Mechanical is off, and the operating system has not saved any context to the hard disk. S4 ACPI Off Mechanical is off. The operating system has saved context to the hard disk. S3-S1 ACPI Slow blink1 DC power is still on. The operating system has saved context and gone into a level of low-power state. S0 ACPI Steady on System and the operating system are up and running.

Table 2. Power/Sleep LED Functional States

**HDD Activity LED** - The drive activity LED on the front panel indicates drive activity from the on-board hard disk controllers. The server board also provides a header giving access to this LED for add-in controllers.

**USB Ports** – In addition, the front panel provides two USB ports. The USB ports are cabled to the 2x5 connector on the server board.

#### 1.3.2 Front Control Panel LED Status

The following table provides a description of each LED status.

**Table 3. Front Control Panel LED Status**

| LED                       | Color | Condition | What It Means                                                                                                                                          |

|---------------------------|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | Green | On        | Power on or S0 sleep.                                                                                                                                  |

| Power/Sleep               | Green | Blink     | S1 sleep or S3 standby only for Server baseboards.                                                                                                     |

|                           |       | Off       | Off (also sleep S4/S5 modes).                                                                                                                          |

|                           | Green | On        | System ready/No alarm.                                                                                                                                 |

|                           | Green | Blink     | System ready, but degraded: redundancy lost such as PS or fan failure; non-critical temp/voltage threshold; battery failure; or predictive PS failure. |

| Status                    | Amber | On        | Critical alarm: Voltage, thermal, or power fault; CPU missing; insufficient power unit redundancy resource offset asserted.                            |

|                           | Amber | Blink     | Non-Critical failure: Critical temp/voltage threshold; VDR hot asserted; min number fans not present or failed.                                        |

|                           |       |           | AC power off: System unplugged.                                                                                                                        |

|                           |       | Off       | AC power on: System powered off and in standby, no prior degraded/non-critical/critical state.                                                         |

| Clobal LIDD Activity      | Green | Blink     | HDD access.                                                                                                                                            |

| Global HDD Activity       |       | Off       | No access and no fault.                                                                                                                                |

|                           | Green | On        | LAN link                                                                                                                                               |

| LAN 1-4<br>Activity/Link  | Green | Blink     | LAN access.                                                                                                                                            |

| / tetrotey/en/ik          |       | Off       | Idle.                                                                                                                                                  |

|                           | Blue  | On        | Front panel chassis ID button pressed.                                                                                                                 |

| Chassis<br>Identification | Blue  | Blink     | Unit selected for identification by software.                                                                                                          |

| identification            |       | Off       | No identification.                                                                                                                                     |

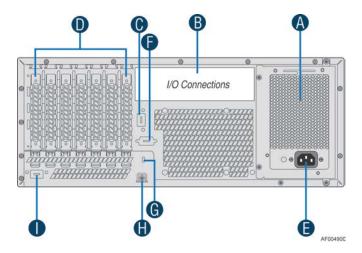

#### 1.4 Back panel feature Overveiw

The following figure shows the layout of Back Panel with fixed power supply and hot-swap redundant power supplies:

| Α | Fixed Power Supply       | F | Serial-B Port (Optional)             |

|---|--------------------------|---|--------------------------------------|

| В | IO Connectors            | G | Kensington* Cable Lock Mounting Hole |

| С | RMM4 NIC Port (Optional) | Н | Padlock Loop                         |

| D | Add in PCI-e cards       | I | RMM4 NIC Port (Optional)             |

| Е | Power Connector          |   |                                      |

Figure 5. Back panel feature (for P4000SC2SFEN)

| Α | Hot-swap Power Supply | G | Add in PCI-e cards                      |

|---|-----------------------|---|-----------------------------------------|

| В | Power Connector       | Н | Serial-B Port (Optional)                |

| С | Power Connector       | I | Kensington* Cable Lock Mounting<br>Hole |

| D | Hot-swap Power Supply | J | Padlock Loop                            |

| Е | IO Connectors            | K | RMM4 NIC Port (Optional) |

|---|--------------------------|---|--------------------------|

| F | RMM4 NIC Port (Optional) |   |                          |

Figure 13. Back panel feature (For P4000SC2SHDR and P4000SC2MHGC)

#### 1.5 Hot swap Hard Drivers and front panel options

Figure 6. Hot-Swap Hard Disk Drive Cage

#### 1.6 Chassis Security

A variety of chassis security options are provided at the system level:

- A removable padlock loop at the rear of the system access cover can be used to prevent access to the microprocessors, memory, and add-in cards. A variety of lock sizes can be accommodated by the 0.270-inch diameter loop.

- A Kensington\* cable lock mounting hole is provided on the rear chassis I/O panel.

- A chassis intrusion switch is provided, allowing server management software to detect unauthorized access to the system side cover.

• In hot-swap hard drives configuration, a door lock is provided on the front bezel assembly with the door to prevent access to the hot-swap hard drives and the interior of the chassis.

**Note:** See the technical product specificationappropriate to the server board and System Service Guide for a description of BIOS and management security features for each specific supported platform. Technical product specifications can be found at <a href="http://www.intel.com/support">http://www.intel.com/support</a>.

#### 1.7 Front Bezel Features

There are two type of front bezel assembly.

1. Front bezel assembly for fixed hard drives configuration on Intel<sup>®</sup> Server System P4304SC2SFEN.

Figure 7. Front Closed Chassis View for Fixed Hard Drives Configuration

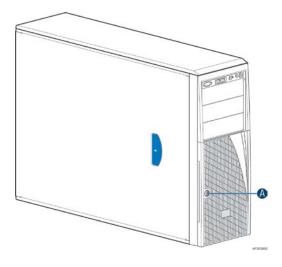

2. Front bezel assembly with the door for hot-swap hard drives configuration on Intel<sup>®</sup> Server System P4304SC2SHDR and P4308SC2MHGC.

A. Security Lock

Figure 8. Front Closed Chassis View for Hot-swap Hard Drives Configuration

Both two pedestal front bezel are constructed of molded plastic and attaches to the front of the chassis with three clips on the right side and two snaps on the left. The snaps at the left attach behind the access cover, thereby preventing accidental removal of the bezel. The bezel can only be removed by first removing the server access cover. This provides additional security to the hard drive and peripheral bay area.

For the front bezel assembly for fixed hard drives configuration, removing the bezel, there is an EMI shield covering the fixed hard drives bay area.

For the front bezel assembly for hot-swap hard drives configuration, the bezel includes a keylocking door that covers the drive cage area and allows access to hot swap drives when a hot swap drive cage is installed.

The peripheral bays are covered with plastic snap-in cosmetic pieces that must be removed to add peripherals to the system. Front panel buttons and lights are located above the peripheral bays.

## 2. System Power Sub-system

#### 2.1 550-W Power Supply

This 550W power supply specification defines a non-redundant power supply that supports pedestal entry server systems. The 550W power supply has 7 outputs; 3.3V, 5V, 12V1, 12V2, 12V3, -12V and 5Vsb, with no less than 550W. The power supply has an AC input and be power factor corrected.

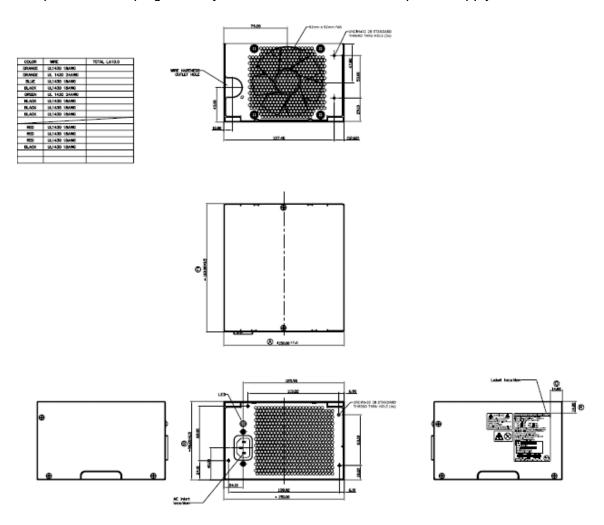

#### 2.1.1 Mechanical Overview

The power supply size is 98mm x 150mm x 160mm (H x W x D) and has a wire harness for the DC outputs. The AC plugs directly into the external face of the power supply.

Figure 9. Mechanical Drawing for 550W Power Supply Enclosure

#### 2.1.1.1 550W Power Supply Output Wire Harness

Listed or recognized component appliance wiring material (AVLV2), CN, rated min 85°C shall be used for all output wiring.

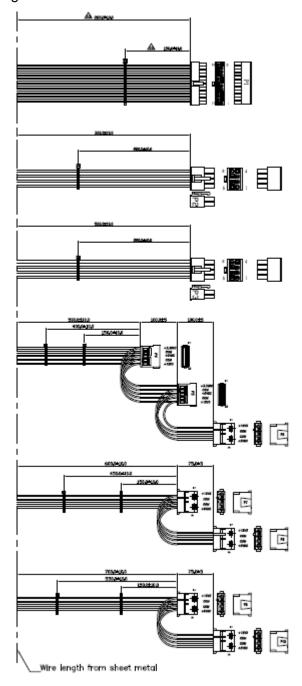

Figure 10. Output Cable Harness for 550W Power Supply

**Table 4. Power Supply Cable Lengths**

| From                         | Length (mm) | To connector # | No of pins | Description                                              |

|------------------------------|-------------|----------------|------------|----------------------------------------------------------|

| Power Supply cover exit hole | 280         | P1             | 24         | Baseboard Power Connector                                |

| Power Supply cover exit hole | 300         | P2             | 8          | Processor 0 connector                                    |

| Power Supply cover exit hole | 500         | P3             | 8          | Processor 1 connector                                    |

| Power Supply cover exit hole | 500         | P4             | 5          | SATA Peripheral Power<br>Connector for 5.25"             |

| Extension from P4            | 100         | P5             | 5          | SATA Peripheral Power<br>Connector for 5.25"             |

| Extension from P5            | 100         | P6             | 4          | Peripheral Power Connector for 5.25"                     |

| Power Supply cover exit hole | 600         | P7             | 4          | 1x4 Legacy HSBP Power<br>Connector                       |

| Extension from P7            | 75          | P8             | 4          | 1x4 Legacy HSBP Power<br>Connector                       |

| Power Supply cover exit hole | 700         | P9             | 4          | 1x4 Legacy HSBP<br>Power/Fixed HDD Adapter<br>Connection |

| Extension from P9            | 75          | P10            | 4          | 1x4 Legacy HSBP<br>Power/Fixed HDD Adapter<br>Connection |

#### 2.1.1.1.1 Main power connector (P1)

Connector housing: 24- Pin Molex Mini-Fit Jr 39-01-2245 (94V2) or equivalent

Contact: Molex Minifit Jr, Crimp 5556 or equivalent

**Table 5. P1 Main Power Connector**

| Pin | Signal   | 18 awg color | Pin | Signal   | 18 awg color |

|-----|----------|--------------|-----|----------|--------------|

| 1   | +3.3 VDC | Orange       | 13  | +3.3 VDC | Orange       |

| 2   | +3.3 VDC | Orange       | 14  | -12 VDC  | Blue         |

| 3   | СОМ      | Black        | 15  | COM      | Black        |

| 4   | +5 VDC*  | Red          | 16  | PSON#    | Green        |

| 5   | СОМ      | Black        | 17  | COM      | Black        |

| 6   | +5 VDC   | Red          | 18  | COM      | Black        |

| 7   | COM      | Black        | 19  | СОМ      | Black        |

| 8   | PWR OK   | Gray         | 20  | Reserved | N.C.         |

| 9   | 5VSB     | Purple       | 21  | +5 VDC   | Red          |

| 10  | +12V3    | Yellow/Black | 22  | +5 VDC   | Red          |

| 11  | +12V3    | Yellow/Black | 23  | +5 VDC   | Red          |

| 12  | +3.3 VDC | Orange       | 24  | COM      | Black        |

Note: 3.3V remote sense shall be double crimped into pin 13 if needed to meet regulation limits.

#### 2.1.1.1.2 Processor/Memory Power Connector (P2)

Connector housing: 8- Pin Molex 39-01-2085 (94V2) or equivalent Contact: Molex, Mini-Fit Jr, HCS, 44476-1111 or equivalent

Table 6. P2 Processor#1 Power Connector

| Pin | Signal | 18 awg color | Pin | Signal | 18 awg color |

|-----|--------|--------------|-----|--------|--------------|

| 1   | COM    | Black        | 5   | +12V1  | Yellow       |

| 2   | COM    | Black        | 6   | +12V1  | Yellow       |

| 3   | COM    | Black        | 7   | +12V1  | Yellow       |

| 4   | COM    | Black        | 8   | +12V1  | Yellow       |

#### 2.1.1.1.3 Processor/Memory Power Connector (P3)

Connector housing: 8- Pin Molex 39-01-2085 (94V2) or equivalent Contact: Molex, Mini-Fit Jr, HCS, 44476-1111 or equivalent

Table 7. P3 Processor#1 Power Connector

| Pin | Signal | 18 awg color | Pin | Signal | 18 awg color |

|-----|--------|--------------|-----|--------|--------------|

| 1   | СОМ    | Black        | 5   | +12V2  | Yellow       |

| 2   | COM    | Black        | 6   | +12V2  | Yellow       |

| 3   | COM    | Black        | 7   | +12V2  | Yellow       |

| 4   | COM    | Black        | 8   | +12V2  | Yellow       |

#### **2.1.1.1.4** *Peripheral Power Connectors (P6,7,8,9,10)*

Connector housing: Amp 1-480424-0 or equivalent

Contact: Amp 61314-1 contact or equivalent

**Table 8. Peripheral Power Connectors**

| Pin | Signal | 18 AWG Color |

|-----|--------|--------------|

| 1   | +12V3  | Yellow/Black |

| 2   | COM    | Black        |

| 3   | COM    | Black        |

| 4   | +5 VDC | Red          |

#### 2.1.1.1.5 SATA Hard Drive Power Connectors (P4, P5)

Connector housing: JWT A3811H00-5P (94V2) or equivalent;

Contact: JWT A3811TOP-0D or equivalent

**Table 9. SATA Power Connector**

| Pin | Signal | 18 AWG Color |

|-----|--------|--------------|

| 1   | +3.3V  | Orange       |

| 2   | COM    | Black        |

| 3   | +5VDC  | Red          |

| 4   | COM    | Black        |

| 5   | +12V3  | Yellow/Black |

#### 2.1.2 Temperature Requirements

The power supply shall operate within all specified limits over the  $T_{\text{op}}$  temperature range.

**Table 10. Thermal Requirements**

| Item                | Description                      | Min | Max  | Units  |

|---------------------|----------------------------------|-----|------|--------|

| T <sub>op</sub>     | Operating temperature range.     | 0   | 50   | °C     |

| T <sub>non-op</sub> | Non-operating temperature range. | -40 | 70   | ۰C     |

| Altitude            | Maximum operating altitude.      |     | 3000 | meters |

#### 2.1.3 AC Input Requirements

#### 2.1.3.1 Power Factor

The power supply meets the power factor requirements stated in the Energy Star® Program Requirements for Computer Servers. These requirements are stated below.

**Table 11. Power Factor Requirements for Computer Servers**

| Output power | 20% load | 50% load | 100% load |

|--------------|----------|----------|-----------|

| Power factor | 0.8      | 0.9      | 0.95      |

Tested at 230Vac, 50Hz and 60Hz and 115VAC, 60Hz.

Tested according to Generalized Internal Power Supply Efficiency Testing Protocol Rev 6.4.3. This is posted at <a href="http://efficientpowersupplies.epri.com/methods.asp">http://efficientpowersupplies.epri.com/methods.asp</a>.

#### 2.1.3.2 AC Inlet Connector

The AC input connector is an *IEC 320 C-14* power inlet. This inlet is rated for 10A/250VAC.

#### 2.1.3.3 AC Input Voltage Specification

The power supply operates within all specified limits over the following input voltage range. Harmonic distortion of up to 10% of the rated line voltage does not cause the power supply to go out of specified limits. Application of an input voltage below 85VAC does not cause damage to the power supply, including a blown fuse.

Table 12. AC Input Voltage Range

|   | Parameter     | Min                  | Rated                    | Vmax                 | Start up vac      | Power off         |

|---|---------------|----------------------|--------------------------|----------------------|-------------------|-------------------|

|   | r drame ter   |                      | Nated                    | VIII OX              |                   | vac               |

|   | Voltage (110) | 90 V <sub>rms</sub>  | 100-127 V <sub>rms</sub> | 140 V <sub>rms</sub> | 85VAC +/-<br>4VAC | 70VAC +/-<br>5VAC |

| F | Voltage (220) | 180 V <sub>rms</sub> | 200-240 V <sub>rms</sub> | 264 V <sub>rms</sub> |                   | 01710             |

|   | Frequency     | 47 Hz                | 50/60                    | 63 Hz                |                   |                   |

#### Notes:

- 1. Maximum input current at low input voltage range shall be measured at 90VAC, at max load.

- 2. Maximum input current at high input voltage range shall be measured at 180VAC, at max load.

- 3. This requirement is not to be used for determining agency input current markings.

#### 2.1.3.4 AC Line Dropout/Holdup

An AC line dropout is defined to be when the AC input drops to 0VAC at any phase of the AC line for any length of time. During an AC dropout the power supply meets dynamic voltage regulation requirements. An AC line dropout of any duration does not cause tripping of control signals or protection circuits. If the AC dropout lasts longer than the holdup time the power supply recovers and meets all turn on requirements. The power supply meets the AC dropout requirement over rated AC voltages and frequencies. A dropout of the AC line for any duration does not cause damage to the power supply.

Table 13. AC Line Holdup time

| Loading | Holdup time |

|---------|-------------|

| 75%     | 12msec      |

#### 2.1.3.5 AC Line Fuse

The power supply has one line fused in the **single line fuse** on the line (Hot) wire of the AC input. The line fusing is acceptable for all safety agency requirements. The input fuse is a slow blow type. AC inrush current does not cause the AC line fuse to blow under any conditions. All protection circuits in the power supply do not cause the AC fuse to blow unless a component in the power supply has failed. This includes DC output load short conditions

#### 2.1.3.6 AC Line Leakage Current

The maximum leakage current to ground for each power supply is 3.5mA when tested at 240VAC.

#### 2.1.3.7 AC Line Transient Specification

AC line transient conditions are defined as "sag" and "surge" conditions. "Sag" conditions are also commonly referred to as "brownout", these conditions is defined as the AC line voltage dropping below nominal voltage conditions. "Surge" is defined to refer to conditions when the AC line voltage rises above nominal voltage.

The power supply meets the requirements under the following AC line sag and surge conditions.

**Table 14. AC Line Sag Transient Performance**

|                   | AC Line Sag (10sec interval between each sagging) |                           |                |                                               |  |  |

|-------------------|---------------------------------------------------|---------------------------|----------------|-----------------------------------------------|--|--|

| Duration          | Sag                                               | Operating AC Voltage      | Line Frequency | Performance Criteria                          |  |  |

| 0 to 1/2 AC cycle | 95%                                               | Nominal AC Voltage ranges | 50/60Hz        | No loss of function or performance            |  |  |

| > 1 AC cycle      | >30<br>%                                          | Nominal AC Voltage ranges | 50/60Hz        | Loss of function acceptable, self recoverable |  |  |

**Table 15. AC Line Surge Transient Performance**

|                 | AC Line Surge |                                  |                |                                    |  |  |  |

|-----------------|---------------|----------------------------------|----------------|------------------------------------|--|--|--|

| Duration        | Surge         | Operating AC Voltage             | Line Frequency | Performance Criteria               |  |  |  |

| Continuous      | 10%           | Nominal AC Voltages              | 50/60Hz        | No loss of function or performance |  |  |  |

| 0 to ½ AC cycle | 30%           | Mid-point of nominal AC Voltages | 50/60Hz        | No loss of function or performance |  |  |  |

#### 2.1.3.8 **Power Recovery**

The power supply recovers automatically after an AC power failure. AC power failure is defined to be any loss of AC power that exceeds the dropout criteria.

#### 2.1.4 **Efficiency**

The following table provides the required minimum efficiency level at various loading conditions. These are provided at three different load levels; 100%, 50% and 20%. Output shall be load according to the proportional loading method defined by 80 Plus in Generalized Internal Power Supply Efficiency Testing Protocol Rev 6.4.3. This is posted at http://efficientpowersupplies.epri.com/methods.asp.

**Table 16. Silver Efficiency Requirement**

| Loading            | 100% of maximum | 50% of maximum | 20% of maximum |

|--------------------|-----------------|----------------|----------------|

| Minimum Efficiency | 85%             | 88%            | 85%            |

The power supply passes with enough margins to make sure in production all power supplies meet these efficiency requirements.

#### 2.1.4.1 Standby Efficiency

When in standby mode; the power supply draws less than 1W AC power with 100mA of 5Vstandby load. This is tested at 115VAC/60Hz and 230VAC/50Hz.

#### 2.1.5 DC Output Specification

#### 2.1.5.1 **Output Power/Currents**

The following tables define the minimum power and current ratings. The power supply meets both static and dynamic voltage regulation requirements for all conditions.

**Table 17. Over Voltage Protection Limits**

| Parameter | Min | Max. | Peak | Unit |

|-----------|-----|------|------|------|

| 3.3V      | 0.5 | 18.0 |      | Α    |

| 5V        | 0.3 | 15.0 |      | Α    |

| 12V1      | 0.7 | 24.0 | 28.0 | Α    |

| 12V2      | 0.7 | 24.0 | 28.0 | Α    |

| 12V3      | 1.5 | 18.0 |      |      |

| - 12V     | 0.0 | 0.5  |      | Α    |

| 5Vstby    | 0.0 | 3.0  | 3.5  | Α    |

#### Notes:

- 1. Max combined power for all output shall not exceed 550W.

- Peak combined power for all outputs shall not exceed 630W for 20 seconds.

Max combined power of 12V1, 12V2 and 12V3 shall not exceed 530W.

Max combined power on 3.3V and 5V shall not exceed 120W.

#### 2.1.5.2 Cross Loading

The power supply maintains voltage regulation limit when operated over the following cross loading conditions.

12V2 3.3V 5.0V 12V1 12V3 -12V 5.0Vstby Total 12V 3.3V/5V Power Power Power Load1 18 12.1 12 12 11.7 0 0.3 550 428 120 Load2 15 12 0.5 13.5 12 11.2 0.3 549 422 120 Load3 2.5 2 20 20 4.2 0 0.3 550 530 18 Load4 2.5 2 13.1 18 0 13.1 0.3 550 530 18 Load5 3 0.5 0.3 15 15 6.5 0.5 3 462 438 Load6 4 16 1 1 3.5 0 0.3 140 66 73 Load7 16 13 1 1 9 0.5 3 271 132 118

**Table 18. Loading Conditions**

#### 2.1.5.3 Standby Output

The 5VSB output is present when an AC input greater than the power supply turn on voltage is applied.

#### 2.1.5.4 Voltage Regulation

The power supply output voltages stay within the following voltage limits when operating at steady state and dynamic loading conditions. These limits include the peak-peak ripple/noise. These shall be measured at the output connectors.

| Parameter | Tolerance  | Min     | Nom    | Max    | Units |

|-----------|------------|---------|--------|--------|-------|

| +3.3V     | - 3%/+5%   | +3.20   | +3.30  | +3.46  | Vrms  |

| +5V       | - 4%/+5%   | +4.80   | +5.00  | +5.25  | Vrms  |

| +12V1     | - 4%/+5%   | +11.52  | +12.00 | +12.60 | Vrms  |

| +12V2     | - 4%/+5%   | +11.52  | +12.00 | +12.60 | Vrms  |

| +12V3     | - 4%/+5%   | +11.52  | +12.00 | +12.60 | Vrms  |

| - 12V     | - 10%/+10% | - 13.20 | -12.00 | -10.80 | Vrms  |

| +5VSB     | - 4%/+5%   | +4.80   | +5.00  | +5.25  | Vrms  |

**Table 19. Voltage Regulation Limits**

#### 2.1.5.5 Dynamic Loading

The output voltages remain within limits specified for the step loading and capacitive loading specified in the table below. The load transient repetition rate is tested between 50Hz and 5kHz at duty cycles ranging from 10%-90%. The load transient repetition rate is only a test specification. The  $\Delta$  step load may occur anywhere within the MIN load to the MAX load conditions.

**Table 20. Transient Load Requirements**

| Output | ∆ Step Load Size<br>(See note 2) | Load Slew Rate | Test capacitive Load |

|--------|----------------------------------|----------------|----------------------|

| +3.3V  | 6.0A                             | 0.5 A/μsec     | 970 μF               |

| Output          | ∆ Step Load Size | Load Slew Rate | Test capacitive Load   |

|-----------------|------------------|----------------|------------------------|

|                 | (See note 2)     |                |                        |

| +5V             | 4.0A             | 0.5 A/μsec     | 400 μF                 |

| 12V1+12V2 +12V3 | 23.0A            | 0.5 A/μsec     | 2200 μF <sup>1,2</sup> |

| +5VSB           | 0.5A             | 0.5 A/μsec     | 20 μF                  |

#### Notes:

- 1. Step loads on each 12V output may happen simultaneously.

- 2. The +12V should be tested with  $2200\mu F$  evenly split between the four +12V rails

- 3. This will be tested over the range of load conditions in section 2.1.6.2.

#### 2.1.5.6 Capacitive Loading

The power supply is stable and meets all requirements with the following capacitive loading ranges.

| Output | Min | Max  | Units |

|--------|-----|------|-------|

| +3.3V  | 250 | 5000 | μF    |

| +5V    | 400 | 5000 | μF    |

| +12V   | 500 | 8000 | μF    |

| -12V   | 1   | 350  | μF    |

| +5VSB  | 20  | 350  | μF    |

**Table 21. Capacitive Loading Conditions**

#### 2.1.5.7 Grounding

The output ground of the pins of the power supply provides the output power return path. The output connector ground pins are connected to the safety ground (power supply enclosure). This grounding is well designed to ensure passing the max allowed Common Mode Noise levels.

The power supply is provided with a reliable protective earth ground. All secondary circuits are connected to protective earth ground. Resistance of the ground returns to chassis does not exceed 1.0 m $\Omega$ . This path may be used to carry DC current.

#### 2.1.5.8 Residual Voltage Immunity in Standby mode

The power supply is immune to any residual voltage placed on its outputs (Typically a leakage voltage through the system from standby output) up to **500mV**. There is neither additional heat generated, nor stressing of any internal components with this voltage applied to any individual or all outputs simultaneously. It also does not trip the protection circuits during turn on.

The residual voltage at the power supply outputs for no load condition does not exceed **100mV** when AC voltage is applied and the PSON# signal is de-asserted.

#### 2.1.5.9 Common Mode Noise

The Common Mode noise on any output does not exceed **350mV pk-pk** over the frequency band of 10Hz to 20MHz.

The measurement is made across a  $100\Omega$  resistor between each of DC outputs, including ground at the DC power connector and chassis ground (power subsystem enclosure). The test set-up shall use a FET probe such as Tektronix model P6046 or equivalent.

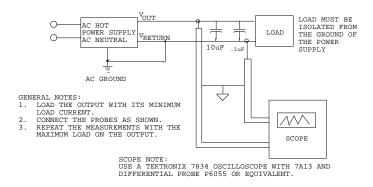

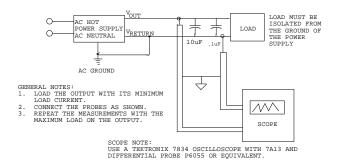

#### 2.1.5.10 Ripple/Noise

The maximum allowed ripple/noise output of the power supply is defined in the table below. This is measured over a bandwidth of 10Hz to 20MHz at the power supply output connectors. A  $10\mu F$  tantalum capacitor in parallel with a  $0.1\mu F$  ceramic capacitor is placed at the point of measurement.

Table 22. Ripples and Noise

| +3.3V   | +5V     | +12V 1, 2, 3 | -12V     | +5VSB   |

|---------|---------|--------------|----------|---------|

| 50mVp-p | 50mVp-p | 120mVp-p     | 200mVp-p | 50mVp-p |

The test set-up shall be as shown below.

Figure 11. Differential Noise test setup

**Note**: When performing this test, the probe clips and capacitors should be located close to the load.

#### 2.1.5.11 Timing Requirements

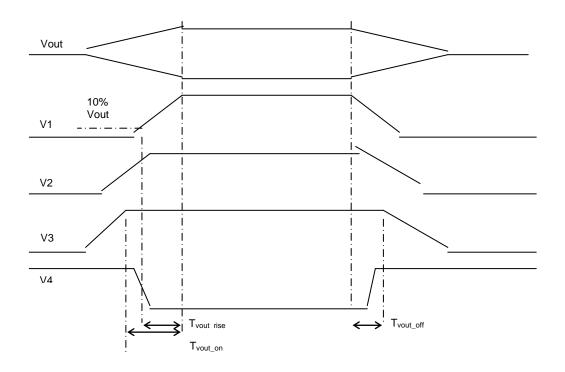

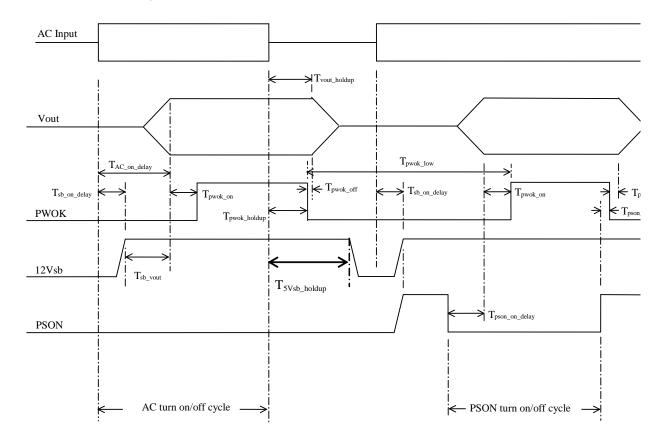

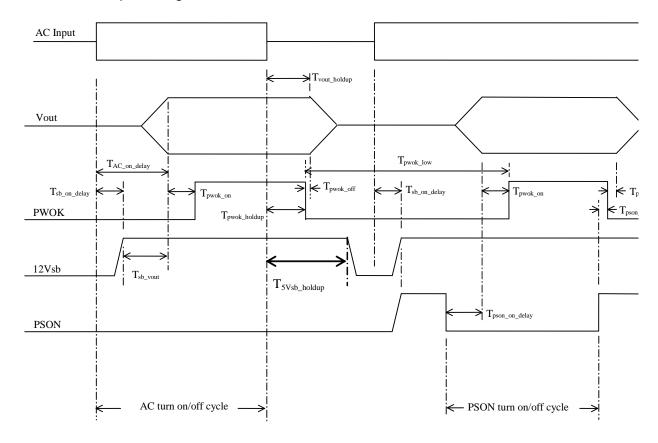

These are the timing requirements for the power supply operation. The output voltages rise from 10% to within regulation limits ( $T_{vout\_rise}$ ) within 2 to 50ms, except for 5VSB - it is allowed to rise from 1 to 25ms. The +3.3V, +5V and +12V1, +12V2, +12V3 output voltages start to rise approximately at the same time. **All outputs rise monotonically**. Each output voltage reach regulation within 50ms ( $T_{vout\_on}$ ) of each other during turn on the power supply. Each output voltage fall out of regulation within 400ms ( $T_{vout\_off}$ ) of each other during turn off. Table 45 shows the timing requirements for the power supply being turned on and off by the AC input, with PSON held low and the PSON signal, with the AC input applied. All timing requirements are met for the cross loading condition in Table 39.

Item Description MIN MAX UNITS T<sub>vout\_rise</sub> Output voltage rise time from each main output. 2 50 ms Output rise time for the 5Vstby output. 25 ms All main outputs must be within regulation of each 50 ms  $T_{vout\_on}$ other within this time. All main outputs must leave regulation within this 400 ms T vout\_off

**Table 23. Output Voltage Timing**

Figure 12. Output Voltage Timing

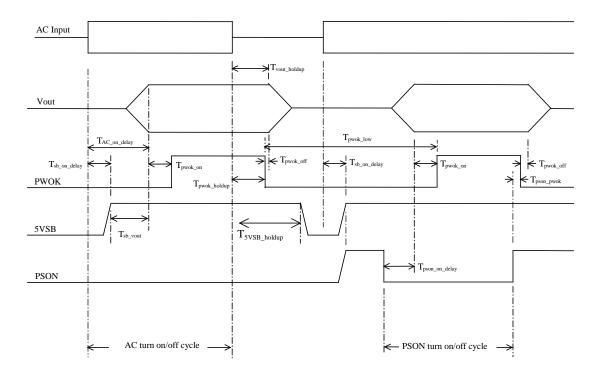

Table 24. Turn On/Off Timing

| Item                       | Description                                                                                             | MIN | MAX  | UNITS |

|----------------------------|---------------------------------------------------------------------------------------------------------|-----|------|-------|

| T <sub>sb_on_delay</sub>   | Delay from AC being applied to 5VSB being within regulation.                                            |     | 1500 | ms    |

| T <sub>ac_on_delay</sub>   | Delay from AC being applied to all output voltages being within regulation.                             |     | 2500 | ms    |

| T <sub>vout_holdup</sub>   | Time all output voltages stay within regulation after loss of AC. Tested at 75% of maximum load.        | 13  |      | ms    |

| $T_{pwok\_holdup}$         | Delay from loss of AC to de-assertion of PWOK. Tested at 75% of maximum load.                           | 12  |      | ms    |

| T <sub>pson_on_delay</sub> | Delay from PSON# active to output voltages within regulation limits.                                    | 5   | 400  | ms    |

| T pson_pwok                | Delay from PSON# deactivate to PWOK being de-asserted.                                                  |     | 50   | ms    |

| T <sub>pwok_on</sub>       | Delay from output voltages within regulation limits to PWOK asserted at turn on.                        | 100 | 500  | ms    |

| T pwok_off                 | Delay from PWOK de-asserted to output voltages (3.3V, 5V, 12V, -12V) dropping out of regulation limits. | 1   |      | ms    |

| T <sub>pwok_low</sub>      | Duration of PWOK being in the de-asserted state during an off/on cycle using AC or the PSON signal.     | 100 |      | ms    |

| T <sub>sb_vout</sub>       | Delay from 5VSB being in regulation to O/Ps being in regulation at AC turn on.                          | 10  | 1000 | ms    |

| Item                     | Description                                                            | MIN | MAX | UNITS |

|--------------------------|------------------------------------------------------------------------|-----|-----|-------|

| T <sub>5VSB_holdup</sub> | Time the 5VSB output voltage stays within regulation after loss of AC. | 70  |     | ms    |

Figure 13. Turn On/Off Timing (Power Supply Signals)

### 2.1.6 Protection Circuits

Protection circuits inside the power supply causes only the power supply's main outputs to shut down. If the power supply latches off due to a protection circuit tripping, an AC cycle OFF for 15sec and a PSON<sup>#</sup> cycle HIGH for 1sec able to reset the power supply.

### 2.1.6.1 Current Limit (OCP)

Below are over current protection limits for each output. If the current limits are exceeded the power supply shuts down and latch off. The latch will be cleared by toggling the PSON<sup>#</sup> signal or by an AC power interruption. The power supply does not be damaged from repeated power cycling in this condition. -12V and 5VSB is protected under over current or shorted conditions so that no damage can occur to the power supply. 5Vsb will be auto-recovered after removing OCP limit.

Output

Min OCP

Max OCP

+3.3V

22 A

Meet 240VA

+5V

16 A

30 A

+12V1,2

29 A

36 A

+12V3 (240VA limited)

18.5 A

20 A

**Table 25. Over Current Limits**

| Output | Min OCP   | Max OCP |

|--------|-----------|---------|

| -12V   | No damage |         |

| 5Vstby | No damage |         |

### 2.1.6.2 Over Voltage Protection (OVP)

The power supply over voltage protection is locally sensed. The power supply shuts down and latch off after an over voltage condition occurs. This latch is cleared by toggling the PSON<sup>#</sup> signal or by an AC power interruption. The table below contains the over voltage limits. The values are measured at the output of the power supply's pins. The voltage shall never exceed the maximum levels when measured at the power pins of the power supply connector during any single point of fail. The voltage shall never trip any lower than the minimum levels when measured at the power pins of the power supply connector. 5VSB will be auto-recovered after removing OVP limit.

Table 24. Over Voltage Protection (OVP) Limits

| Output Voltage | MAX (V) |  |

|----------------|---------|--|

| +3.3V          | 4.5     |  |

| +5V            | 6.5     |  |

| +12V1,2,3      | 14.5    |  |

| +5VSB          | 6.5     |  |

## 2.1.6.3 Over Temperature Protection (OTP)

The power supply will be protected against over temperature conditions caused by loss of fan cooling or excessive ambient temperature. In an OTP condition the PSU will shut down.

#### 2.1.7 Control and Indicator Functions

The following sections define the input and output signals from the power supply. Signals that can be defined as low true use the following convention: Signal# = low true

### 2.1.7.1 PSON# Input Signal

The PSON<sup>#</sup> signal is required to remotely turn on/off the power supply. PSON<sup>#</sup> is an active low signal that turns on the +3.3V, +5V, +12V1, +12V2, +12V3 and -12V power rails. When this signal is not pulled low by the system, or left open, the outputs (except the +5VSB) turn off. This signal is pulled to a standby voltage by a pull-up resistor internal to the power supply. Refer to Figure 27 for the timing diagram.

**Table 26. PSON# Signal Characteristic**

| Signal Type                         |       | Accepts an open collector/drain input from the system. Pull-<br>up to VSB located in power supply. |  |  |

|-------------------------------------|-------|----------------------------------------------------------------------------------------------------|--|--|

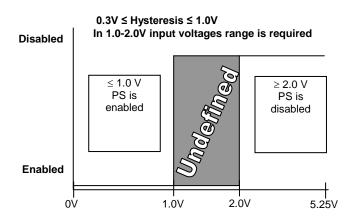

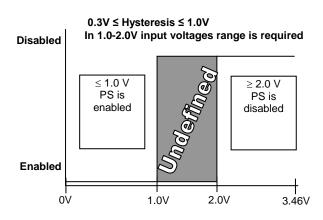

| PSON# = Low                         | ON    |                                                                                                    |  |  |