# Intel<sup>®</sup> Server System R1304BTSSFAN Intel<sup>®</sup> Server System R1304BTLSFAN Intel<sup>®</sup> Server System R1304BTLSHBN

**Technical Product Specification**

Intel order number G17455-003

**Revision 1.1**

May, 2011

**Enterprise Platforms and Services Division – Marketing**

## **Revision History**

| Date           | Revision Number | Modifications                                           |  |

|----------------|-----------------|---------------------------------------------------------|--|

| September 2010 | 0.1             | Initial release.                                        |  |

| November 2010  | 0.5             | Updated the hardware info.                              |  |

| January 2011   | 0.7             | Updated S1200BTS info.                                  |  |

| March 2011     | 1.0             | Updated Regulatory info.                                |  |

| May 2011       | 1.1             | <ul> <li>Updated Chassis Dimensions info.</li> </ul>    |  |

|                |                 | <ul> <li>Updated Operation Temperature info.</li> </ul> |  |

## Disclaimers

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel<sup>®</sup>'s Terms and Conditions of Sale for such products, Intel<sup>®</sup> assumes no liability whatsoever, and Intel<sup>®</sup> disclaims any express or implied warranty, relating to sale and/or use of Intel<sup>®</sup> products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel<sup>®</sup> products are not intended for use in medical, life saving, or life sustaining applications. Intel<sup>®</sup> may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel<sup>®</sup> reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

The server boards/chassis referenced in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2011. All rights reserved.

# **Table of Contents**

| 1. | Introduc | ction                                              | 1 |

|----|----------|----------------------------------------------------|---|

| 1  | .1       | Chapter Outline                                    | 1 |

| 1  | .2       | Server Board Use Disclaimer                        | 1 |

| 2. | Product  | Overview                                           | 3 |

| 2  | .1       | System Views                                       | 5 |

| 2  | .2       | Chassis Dimensions                                 | 5 |

| 2  | .3       | System Components                                  | 6 |

| 2  | .4       | System Boards                                      | 8 |

|    | 2.4.1    | Intel <sup>®</sup> Server System R1304BTSSFAN      | 8 |

|    | 2.4.2    | Intel <sup>®</sup> Server System R1304BTLSFAN      | 8 |

|    | 2.4.3    | Intel <sup>®</sup> Server System R1304BTLSHBN      | 8 |

| 2  | .5       | System Cooling                                     | 9 |

| 2  | .6       | Rack and Cabinet Mounting Options                  | 9 |

| 3. | 250W Po  | ower Subsystem1                                    | 0 |

| 3  | .1       | Mechanical Specifications1                         | 0 |

| 3  | .2       | Output Connectors1                                 | 1 |

|    | 3.2.1    | Baseboard power connector (P1)1                    | 2 |

|    | 3.2.2    | Processor Power Connector (P2)1                    | 2 |

|    | 3.2.3    | SATA Hard Drive Power Connectors (P4, P5, P6, P7)1 | 2 |

|    | 3.2.4    | Mini SATA Hard Drive Power Connectors (P3)1        | 3 |

| 3  | .3       | AC Inlet Connector1                                | 3 |

|    | 3.3.1    | AC Power Cord Specification Requirements1          | 3 |

| 3  | .4       | Marking and Identification1                        | 4 |

| 3  | .5       | Efficiency1                                        | 4 |

| 3  | .6       | AC Input Voltage1                                  | 4 |

| 3  | .7       | Output Power/Currents1                             | 4 |

| 3  | .8       | Protection Circuits1                               | 4 |

|    | 3.8.1    | Over Current Protection (OCP)1                     | 5 |

|    | 3.8.2    | Over Voltage Protection (OVP)1                     | 5 |

|    | 3.8.3    | Over Temperature Protection (OTP)1                 | 5 |

| 4. | 350W Po  | ower Subsystem1                                    | 6 |

| 4  | .1       | Mechanical Specifications1                         | 6 |

| 4  | .2       | Output Connectors1                                 | 7 |

|    | 4.2.1    | Baseboard power connector (P1)1                    | 8 |

|    | 4.2.2    | Processor Power Connector (P2)1                    | 8 |

|    | 4.2.3    | SATA Hard Drive Power Connectors (P4, P5)1         |   |

|    | 4.2.4    | Mini SATA Hard Drive Power Connectors (P8)1        | 9 |

|    | 4.2.5    | AUX Power Connector (P3)1                          | 9 |

|     | 4.2.6                                          | Hot-swap Backplane Power Connector (P7)                       | 19 |  |  |

|-----|------------------------------------------------|---------------------------------------------------------------|----|--|--|

| 4   | .3                                             | AC Inlet Connector                                            | 20 |  |  |

|     | 4.3.1                                          | AC Power Cord Specification Requirements                      | 20 |  |  |

| 4   | .4                                             | Marking and Identification                                    | 20 |  |  |

| 4   | .5                                             | Efficiency                                                    | 20 |  |  |

| 4   | .6                                             | AC Input Voltage                                              | 20 |  |  |

| 4   | .7                                             | Output Power/Currents                                         | 21 |  |  |

| 4   | .8                                             | Protection Circuits                                           | 21 |  |  |

|     | 4.8.1                                          | Over Current Protection (OCP)                                 | 21 |  |  |

|     | 4.8.2                                          | Over Voltage Protection (OVP)                                 | 22 |  |  |

|     | 4.8.3                                          | Over Temperature Protection (OTP)                             | 22 |  |  |

|     | 4.9                                            | PMBus                                                         | 22 |  |  |

|     | 4.9.1                                          | Related Documents                                             | 22 |  |  |

|     | 4.9.2                                          | Addressing                                                    | 23 |  |  |

| 5.  | Cooling                                        | Subsystem                                                     | 25 |  |  |

| 5   | .1                                             | Power Supply Fans                                             | 27 |  |  |

| 5   | .2                                             | CPU Air Duct                                                  | 27 |  |  |

| 6.  | Peripher                                       | al and Hard Drive Support                                     | 29 |  |  |

| 6   | .1                                             | Optical Drive Support                                         | 30 |  |  |

|     | 6.1.1                                          | Optical Drive Support                                         | 30 |  |  |

| 6   | .2                                             | Hard Disk Drive Support                                       | 30 |  |  |

|     | 6.2.1                                          | System Fan Connectors                                         | 30 |  |  |

| 7.  | Front Co                                       | ontrol Panel                                                  | 31 |  |  |

|     | 7.1.1                                          | Power/Sleep LED                                               | 32 |  |  |

|     | 7.1.2                                          | System Status LED                                             | 32 |  |  |

|     | 7.1.3                                          | Drive Activity LED                                            | 32 |  |  |

| 8.  | PCI Rise                                       | er Cards and Assembly                                         | 33 |  |  |

| 9.  | Intel <sup>®</sup> Se                          | erver System R1304BTLSHBN Passive SAS/SATA Hot-swap Backplane | 34 |  |  |

|     | 9.1.1                                          | Hot-swap Drive Trays                                          | 35 |  |  |

| 10. | Support                                        | ed Intel <sup>®</sup> Server Boards                           | 36 |  |  |

| 11. | Environ                                        | mental Specifications                                         | 37 |  |  |

| 1   | 1.1                                            | System Level Environmental Limits                             | 37 |  |  |

|     |                                                | Integration and Usage Tips                                    |    |  |  |

|     |                                                | Integrated BMC Sensor Tables                                  |    |  |  |

|     | Appendix C: POST Code Diagnostic LED Decoder47 |                                                               |    |  |  |

|     | ppendix D: POST Error Beep Codes50             |                                                               |    |  |  |

|     | •                                              |                                                               |    |  |  |

| Ref | Reference Documents                            |                                                               |    |  |  |

# List of Figures

| Figure 1. Intel <sup>®</sup> Server System R1304BTSSFAN/R1304BTLSFAN5                        |

|----------------------------------------------------------------------------------------------|

| Figure 2. Intel <sup>®</sup> Server System R1304BTLSHBN5                                     |

| Figure 3. Intel® Server System R1304BTSSFAN/R1304BTLSFAN Major System Components . 6         |

| Figure 4. Intel <sup>®</sup> Server System R1304BTLSHBN Major System Components7             |

| Figure 5. Intel <sup>®</sup> Server System R1304BTSSFAN/R1304BTLSFAN/R1304BTLSHBN Back Panel |

| Features                                                                                     |

| Figure 7. AC Power Cord Specifications13                                                     |

| Figure 8. Power Supply Enclosure Drawing17                                                   |

| Figure 9. AC Power Cord Specifications                                                       |

| Figure 10. Intel <sup>®</sup> Server System R1304BTSSFAN/R1304BTLSFAN Fan Module Assembly 25 |

| Figure 11. Intel <sup>®</sup> Server System R1304BTLSHBN Fan Module Assembly                 |

| Figure 12. Intel® Server System R1304BTSSFAN/R1304BTLSFAN Air Duct                           |

| Figure 13. Intel <sup>®</sup> Server System R1304BTLSHBN Air Duct28                          |

| Figure 14. Intel® Server Systems R1304BTSSFAN/R1304BTLSFAN Drive Bays                        |

| Figure 15. Intel® Server Systems R1304BTLSHBN Drive Bays                                     |

| Figure 16. Intel <sup>®</sup> Server System R1304BTSSFAN/R1304BTLSFAN/R1304BTLSHBN Front     |

| Control Panel                                                                                |

| Figure 17. PCI–E Riser Card Assembly For Intel <sup>®</sup> Server System R1304BTSSFAN,      |

| R1304BTLSFAN and R1304BTLSHBN                                                                |

| Figure 18. Intel <sup>®</sup> Server System R1304BTLSHBN Hot-swap Backplane                  |

|                                                                                              |

# List of Tables

| Table 1. System Feature Set                                                    | 3      |

|--------------------------------------------------------------------------------|--------|

| Table 2. Intel® Server System R1304BTSSFAN/R1304BTLSFAN/R1304BTLSHBN Dimension | sions5 |

| Table 3. Input Voltage Range                                                   | 10     |

| Table 4. Intel <sup>®</sup> 250W PSU Cable Lengths                             | 11     |

| Table 5. P1 Main Power Connector                                               | 12     |

| Table 6. P2 Processor Power Connector                                          | 12     |

| Table 7. SATA Power Connector                                                  | 13     |

| Table 8. SATA Power Connector                                                  | 13     |

| Table 9. AC Input Rating                                                       | 14     |

| Table 10. Load Ratings                                                         | 14     |

| Table 11. Over Load Protection (OCP) Limits                                    | 15     |

| Table 12. Over Voltage Protection (OVP) Limits                                 | 15     |

| Table 13. Input Voltage Range                                                  | 16     |

| Table 14. 350W PSU Cable Lengths                                               | 18     |

| Table 15. P1 Main Power Connector                                              | 18     |

| Table 16. P2 Processor Power Connector                                         | 18     |

| Table 17. SATA Power Connector                                                 | 19     |

| Table 18. SATA Power Connector                                                 | 19     |

| Table 19. AUX Power Connector                                                  | 19     |

| Table 20. P7 HSBP Power Connector                                              | 19     |

| Table 21. AC Input Rating                                                      | 21     |

| Table 22. Load Ratings                                                         | 21     |

| Table 23. Over Load Protection (OCP) Limits                                    | 22     |

| Table 24. Over Voltage Protection (OVP) Limits                                 | 22     |

| Table 25. System Four-pin Fan Headers Pin-outs (J7J1, J1J4, J6B1, and J6J2)    | 30     |

| Table 26. Control Panel LED Functions                                          | 32     |

| Table 27. SSI Power LED Operation                                              | 32     |

| Table 28. Passive SATA/SAS Backplane Power Connector Pin-out                   | 35     |

| Table 29. Passive SATA/SAS Backplane Connector to Hard Drive Pin-out           | 35     |

| Table 30. System Environmental Limits Summary                                  | 37     |

| Table 31. BMC Core Sensors                                                     | 41     |

| Table 32. POST Progress Code LED Example                                       | 47     |

| Table 33. POST Progress Codes                                                  | 47     |

| Table 34. POST Error Messages and Handling                                     | 50     |

| Table 35. POST Error Beep Codes                                                | 51     |

|                                                                                |        |

## < This page is intentionally left blank. >

## 1. Introduction

The Intel<sup>®</sup> Server Systems R1304BTSSFAN, R1304BTLSFAN, and R1304BTLSHBN are 1U server systems.

- The Intel<sup>®</sup> Server System R1304BTSSFAN supports up to four fixed Serial ATA (SATA) hard disk drives. The Intel<sup>®</sup> Server System R1304BTSSFAN includes the Intel<sup>®</sup> Server Board S1200BTS.

- The Intel<sup>®</sup> Server System R1304BTLSFAN supports up to four fixed Serial ATA (SATA) hard disk drives. The Intel<sup>®</sup> Server System R1304BTLSFAN includes the Intel<sup>®</sup> Server Board S1200BTL.

- The Intel<sup>®</sup> Server System R1304BTLSHBN supports up to four hot-swappable SATA disk drives and includes the Intel<sup>®</sup> Server Board S1200BTL.

- The server boards and the server systems have features designed to support the highdensity server market. This chapter provides a high-level overview of the system features. Subsequent chapters provide greater detail for each major system component or feature.

## 1.1 Chapter Outline

This document is divided into the following chapters:

- Chapter 1 Introduction

- Chapter 2 Product Overview

- Chapter 3 250W Power Sub-system

- Chapter 4 350W Power Sub-system

- Chapter 5 Cooling Sub-system

- Chapter 6 Peripheral and Drive Support

- Chapter 7 Front Control Panel

- Chapter 8 PCI Riser Cards and Assembly

- Chapter 9 Intel<sup>®</sup> Server System R1304BTLSHBN Passive SAS/SATA Hot-swap Backplane

- Chapter 10 Supported Intel<sup>®</sup> Server Boards

- Chapter 11 Environmental Specifications

- Appendix A Integration and Usage Tips

- Appendix B Integrated BMC Sensor Tables

- Appendix C POST Code Diagnostic LED Decoder

- Appendix D Post Error Message and Handling

- Glossary

- Reference Documents

## 1.2 Server Board Use Disclaimer

Intel Corporation server boards contain a number of high-density VLSI and power delivery components that need adequate airflow to cool. Intel<sup>®</sup> ensures through its own chassis

development and testing that when Intel<sup>®</sup> server building blocks are used together, the fully integrated system meets the intended thermal requirements of these components. It is the responsibility of the system integrator who chooses not to use Intel<sup>®</sup> developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of airflow required for their specific application and environmental conditions. Intel Corporation cannot be held responsible if components fail or the server board does not operate correctly when used outside any of their published operating or non-operating limits.

## 2. Product Overview

The Intel<sup>®</sup> Server System R1304BTLSFAN and R1304BTLSHBN are both of 1U server system designed to support the Intel<sup>®</sup> Server Board S1200BTL. The Intel<sup>®</sup> Server System R1304BTSSFAN is 1U server system designed to support the Intel<sup>®</sup> Server Board S1200BTS. Intel<sup>®</sup> Server Board S1200BTL, Intel<sup>®</sup> Server Board S1200BTS and the systems have features designed to support the entry-level market. This chapter provides a high-level overview of the system features. The following chapters provide greater detail for each major system component or feature.

| Feature      | Description                                                                                                                                                                      |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Server Board | Intel <sup>®</sup> Server System R1304BTLSFAN/R1304BTLSHBN:                                                                                                                      |  |  |  |

|              | <ul> <li>Intel<sup>®</sup> Server Board S1200BTL</li> </ul>                                                                                                                      |  |  |  |

|              | Intel <sup>®</sup> Server System R1304BTSSFAN:                                                                                                                                   |  |  |  |

|              | <ul> <li>Intel<sup>®</sup> Server Board S1200BTS</li> </ul>                                                                                                                      |  |  |  |

| Processors   | Support for one Intel <sup>®</sup> Xeon <sup>®</sup> E3-1200 Series or Intel <sup>®</sup> Core <sup>™</sup> Processor i3-2100<br>Series Processor in FC-LGA 1155 socket package. |  |  |  |

|              | <ul> <li>5.0 GT/s point-to-point DMI interface to PCH</li> </ul>                                                                                                                 |  |  |  |

|              | <ul> <li>LGA 1155 pin socket</li> </ul>                                                                                                                                          |  |  |  |

|              | <ul> <li>TDP 95W</li> </ul>                                                                                                                                                      |  |  |  |

| Memory       | Two memory channels with support for 1066/1333 MHz Unbuffered (UDIMM) DDR3.<br>• Up to 2 UDIMMs per channel                                                                      |  |  |  |

|              | <ul> <li>32 GB maximum with x8 ECC UDIMM (2 Gb DRAM)</li> </ul>                                                                                                                  |  |  |  |

| Chipset      | Intel <sup>®</sup> Server Board S1200BTL:                                                                                                                                        |  |  |  |

|              | <ul> <li>Support for Intel<sup>®</sup> C204 Platform Controller Hub (PCH)</li> </ul>                                                                                             |  |  |  |

|              | <ul> <li>ServerEngines* LLC Pilot III BMC controller (Integrated BMC)</li> </ul>                                                                                                 |  |  |  |

|              | Intel <sup>®</sup> Server Board S1200BTS:                                                                                                                                        |  |  |  |

|              | <ul> <li>Support for Intel<sup>®</sup> C202 Platform Controller Hub (PCH)</li> </ul>                                                                                             |  |  |  |

| I/O          | Intel <sup>®</sup> Server System R1304BTLSFAN/R1304BTLSHBN:                                                                                                                      |  |  |  |

|              | External connections:                                                                                                                                                            |  |  |  |

|              | <ul> <li>DB-15 video connector</li> </ul>                                                                                                                                        |  |  |  |

|              | <ul> <li>DB-9 serial Port A connector</li> </ul>                                                                                                                                 |  |  |  |

|              | <ul> <li>Four USB ports on two USB/LAN combo connectors at rear of board</li> </ul>                                                                                              |  |  |  |

|              | <ul> <li>Two USB ports on front panel</li> </ul>                                                                                                                                 |  |  |  |

|              | Internal connections:                                                                                                                                                            |  |  |  |

|              | <ul> <li>Two USB 2x5 pin headers, each supporting two USB 2.0 ports</li> </ul>                                                                                                   |  |  |  |

|              | One 2x5 Serial Port B headers                                                                                                                                                    |  |  |  |

|              | One SATA RAID key connector                                                                                                                                                      |  |  |  |

|              | <ul> <li>Two 6Gb/s SATA ports and four 3Gb/s SATA ports</li> </ul>                                                                                                               |  |  |  |

|              | <ul> <li>One SAS mezzanine slot for optional SAS module</li> </ul>                                                                                                               |  |  |  |

|              | One TPM module connector                                                                                                                                                         |  |  |  |

|              | One RMM4 module connector                                                                                                                                                        |  |  |  |

|              | Intel <sup>®</sup> Server System R1304BTSSFAN:                                                                                                                                   |  |  |  |

|              | External connections:                                                                                                                                                            |  |  |  |

|              | <ul> <li>DB-15 video connector</li> </ul>                                                                                                                                        |  |  |  |

|              | <ul> <li>DB-9 serial Port A connector</li> </ul>                                                                                                                                 |  |  |  |

#### Table 1. System Feature Set

| Feature                                          | Description                                                                                                                                                 |  |  |  |  |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                  | <ul> <li>Four USB ports on two USB/LAN combo connectors at rear of board</li> </ul>                                                                         |  |  |  |  |

|                                                  | <ul> <li>Two USB ports on front panel</li> </ul>                                                                                                            |  |  |  |  |

|                                                  | Internal connections:                                                                                                                                       |  |  |  |  |

|                                                  | <ul> <li>Two USB 2x5 pin headers, each supporting two USB 2.0 ports</li> </ul>                                                                              |  |  |  |  |

|                                                  | <ul> <li>One 2x5 Serial Port B headers</li> </ul>                                                                                                           |  |  |  |  |

|                                                  | <ul> <li>One SATA RAID key connector</li> </ul>                                                                                                             |  |  |  |  |

|                                                  | <ul> <li>Six 3Gb/s SATA ports</li> </ul>                                                                                                                    |  |  |  |  |

| Video                                            | Intel <sup>®</sup> Server System R1304BTLSFAN/R1304BTLSHBN:                                                                                                 |  |  |  |  |

|                                                  | Onboard ServerEngines* LLC Pilot II BMC Controller                                                                                                          |  |  |  |  |

|                                                  | <ul> <li>Integrated 2D Video Controller</li> </ul>                                                                                                          |  |  |  |  |

|                                                  | <ul> <li>External 32MB (or above) DDR3 800MHz memory</li> </ul>                                                                                             |  |  |  |  |

|                                                  | Intel <sup>®</sup> Server System R1304BTSSFAN:                                                                                                              |  |  |  |  |

|                                                  | <ul> <li>Silicon Motion SM712GX04LF02-BA</li> </ul>                                                                                                         |  |  |  |  |

| LAN                                              | One Gigabit Ethernet device 82574L connect to PCI-E x1 interfaces on the PCH.<br>One Gigabit Ethernet PHY 82579 connected to PCH through PCI-E x1 interface |  |  |  |  |

| Expansion Capabilities                           | One x8 PCI Express* Gen 2 PCI riser slot capable of supporting a low-profile PCI Express* add-in card which consumes power less than 25 W.                  |  |  |  |  |

| Hard Drive Options                               | Four SATA drives                                                                                                                                            |  |  |  |  |

| Peripherals                                      | Slimline bay for slimline SATA optical drive                                                                                                                |  |  |  |  |

|                                                  | One PCI Express* x8 Add-in Card slot (Gen 2)                                                                                                                |  |  |  |  |

| Control Panel                                    | Standard control panel                                                                                                                                      |  |  |  |  |

| LEDS and displays                                | LEDs with standard control panel:                                                                                                                           |  |  |  |  |

|                                                  | <ul> <li>NIC1 Activity</li> </ul>                                                                                                                           |  |  |  |  |

|                                                  | <ul> <li>NIC2 Activity</li> </ul>                                                                                                                           |  |  |  |  |

|                                                  | <ul> <li>Power/Sleep</li> </ul>                                                                                                                             |  |  |  |  |

|                                                  | <ul> <li>System Status</li> </ul>                                                                                                                           |  |  |  |  |

|                                                  | Hard Drive Activity                                                                                                                                         |  |  |  |  |

| Power supply                                     | Intel <sup>®</sup> Server System R1304BTLSFAN/R1304BTSSFAN:                                                                                                 |  |  |  |  |

|                                                  | <ul> <li>Single 250-W power supply</li> </ul>                                                                                                               |  |  |  |  |

|                                                  | Intel <sup>®</sup> Server System R1304BTLSHBN:                                                                                                              |  |  |  |  |

|                                                  | <ul> <li>Single 350-W power supply</li> </ul>                                                                                                               |  |  |  |  |

| Fans                                             | Three non-redundant, variable-speed system cooling fans                                                                                                     |  |  |  |  |

| Server Management                                | Intel <sup>®</sup> Server System R1304BTLSFAN/R1304BTLSHBN:                                                                                                 |  |  |  |  |

|                                                  | Onboard LLC Pilot III Controller (iBMC)                                                                                                                     |  |  |  |  |

|                                                  | <ul> <li>Integrated Baseboard Management Controller (Integrated BMC), IPMI 2.0<br/>compliant</li> </ul>                                                     |  |  |  |  |

|                                                  | <ul> <li>Integrated 2D video controller on PCI-E x1</li> </ul>                                                                                              |  |  |  |  |

|                                                  | <ul> <li>Optional Intel<sup>®</sup> Remote Management Module 4 (RMM4) lite and optional dedicated NIC module.</li> </ul>                                    |  |  |  |  |

| Security Intel <sup>®</sup> TPM module connector |                                                                                                                                                             |  |  |  |  |

## 2.1 System Views

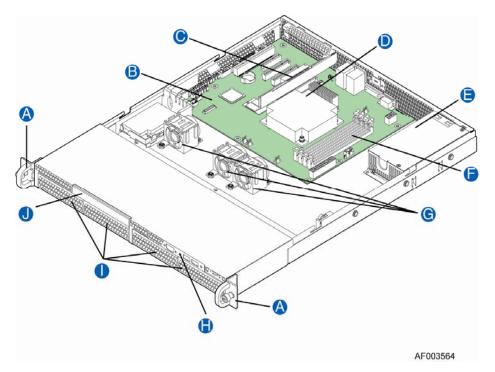

Figure 1. Intel<sup>®</sup> Server System R1304BTSSFAN/R1304BTLSFAN

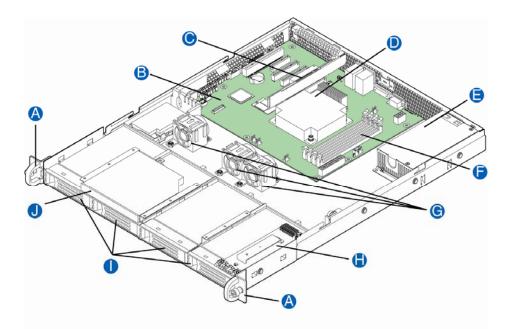

Figure 2. Intel<sup>®</sup> Server System R1304BTLSHBN

## 2.2 Chassis Dimensions

Table 2. Intel<sup>®</sup> Server System R1304BTSSFAN/R1304BTLSFAN/R1304BTLSHBN Dimensions

| Hight | 1.67 inches (4.24 centimeters)  |  |  |

|-------|---------------------------------|--|--|

| Width | 17.25inches (43.82 centimeters) |  |  |

| Depth | 21.8 inches (55.37 centimeters) |  |  |

## 2.3 System Components

| А | Rack handles (two)     | F | System Memory DIMM slots           |

|---|------------------------|---|------------------------------------|

| В | Server Board           | G | Cooling Fans                       |

| С | PCIe* Riser Assembly   | Н | Front Panel                        |

| D | Processor and Heatsink | I | Hard Drive Bays                    |

| Е | Power supply           | J | Front Panel Slimline optical drive |

Figure 3. Intel<sup>®</sup> Server System R1304BTSSFAN/R1304BTLSFAN Major System Components

AF003565

| А | Rack handles (two)     | F | System Memory DIMM slots |

|---|------------------------|---|--------------------------|

| В | Server Board           | G | Cooling Fans             |

| С | PCIe* Riser Assembly   | Н | Front Panel Board        |

| D | Processor and Heatsink | I | Hard Drive Bays          |

| Е | Power supply           | J | Slimline optical drive   |

#### Figure 4. Intel<sup>®</sup> Server System R1304BTLSHBN Major System Components

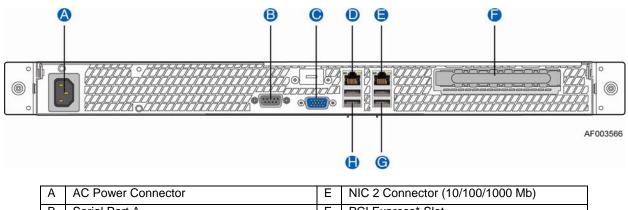

The I/O connector locations on the back of the system are pre-cut, so an I/O shield is not required. The EMI gasket is pre-installed to maintain electromagnetic interference (EMI) compliance levels. The layout arrangement is the same for both the fixed and hot-swap systems.

| A               | A AC Power Connector             |   | NIC 2 Connector (10/100/1000 Mb) |  |

|-----------------|----------------------------------|---|----------------------------------|--|

| B Serial Port A |                                  | F | PCI Express* Slot                |  |

| С               | Video Connector                  | G | USB Ports                        |  |

| D               | NIC 1 Connector (10/100/1000 Mb) | Н | USB Ports                        |  |

# Figure 5. Intel<sup>®</sup> Server System R1304BTSSFAN/R1304BTLSFAN/R1304BTLSHBN Back Panel Features

## 2.4 System Boards

The Intel<sup>®</sup> Server Systems R1304BTSSFAN, R1304BTLSFAN and R1304BTLSHBN include system boards used as internal interconnects and provide feature accessibility. The following section provides a brief description for each.

## 2.4.1 Intel<sup>•</sup> Server System R1304BTSSFAN

The Intel<sup>®</sup> Server System R1304BTSSFAN includes an Intel<sup>®</sup> Server Board S1200BTS. This board supports a PCI Express\* riser card.

PCI Express\* Riser Card – Supports a single, low-profile x8 PCI Express\* riser card.

### 2.4.2 Intel<sup>•</sup> Server System R1304BTLSFAN

The Intel<sup>®</sup> Server System R1304BTLSFAN includes an Intel<sup>®</sup> Server Board S1200BTL. This board supports a PCI Express\* riser card.

PCI Express\* Riser Card – Supports a single, low-profile x8 PCI Express\* riser card.

### 2.4.3 Intel<sup>•</sup> Server System R1304BTLSHBN

The Intel<sup>®</sup> Server System R1304BTLSHBN includes an Intel<sup>®</sup> Server Board S1200BTL. This board supports one riser card options. The Intel<sup>®</sup> Server System R1304BTLSHBN supports a hot-swap SATA/SAS back plane with four SATA/SAS drives.

• PCI Express\* Riser Card – Supports a single, low-profile x8 PCI Express\* riser card.

## 2.5 System Cooling

The Intel<sup>®</sup> Server System R1304BTSSFAN, R1304BTLSFAN and R1304BTLSHBN provide three, non-redundant system cooling fans. When external ambient temperatures remain within specified limits, the cooling system provides sufficient air flow for all drive configurations, processors, supported memory, and add-in cards.

## 2.6 Rack and Cabinet Mounting Options

The server systems were designed to support 19-inches wide by up to 30-inches deep server cabinets. The server systems support the following rack mount option:

Slide rail kit (Product order code – AXXVRAIL): Designed to mount the chassis into a standard (19-inch by up to 30-inch deep) EIA-310D compatible server cabinet.

## 3. 250W Power Subsystem

The power subsystem of the server systems consists of a single, non-redundant 250-W power supply with five outputs: 3.3 V, 5 V, 12 V, -12V and 5 VSB. The form factor fits into a 1U system and provides a wire harness output to the system. An IEC connector is provided on the external face for AC input to the power supply. The power supply provides one; non-redundant 40 mm fan for self -cooling. The power supply fans also provide additional airflow for parts of the system.

The power supply operates within the following voltage ranges and ratings:

| PARAMETER          | MIN     | RATED        | MAX     | Max Input AC Current |

|--------------------|---------|--------------|---------|----------------------|

| Line Voltage (110) | 90Vrms  | 100-127 Vrms | 140Vrms | 6 Arms1              |

| Line Voltage (220) | 180Vrms | 200-240 Vrms | 264Vrms | 3 Arms2              |

| Frequency          | 47 Hz   | 50/60Hz      | 63 Hz   |                      |

#### Table 3. Input Voltage Range

Notes:

1. Maximum input current at low input voltage range shall be measured at 90Vac, at max load.

2. Maximum input current at high input voltage range shall be measured at 180VAC, at max load.

The power supply must operate within all specified limits over the following input voltage ranges shown in the table. Harmonic distortion of up to 10% Total Harmonic Distortion (THD) must not cause the power supply to go out of specified limits.

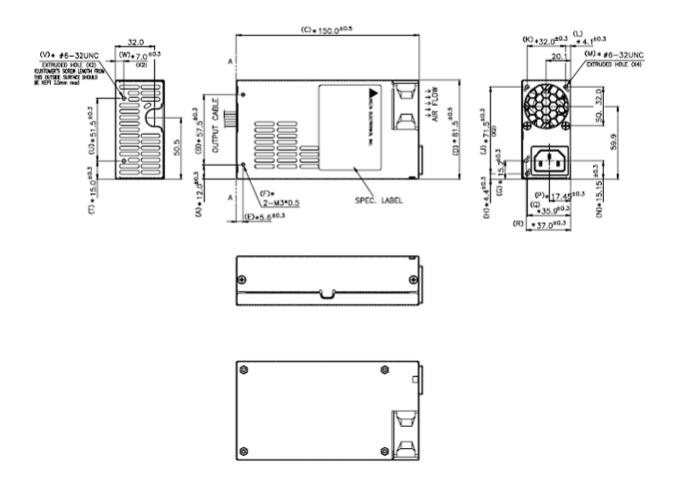

## 3.1 Mechanical Specifications

The 1U 250 W power supply is designed specifically for use in the Intel<sup>®</sup> Server Systems R1304BTSSFAN and R1304BTLSFAN. The physical size of the power supply enclosure is intended to accommodate power ranges from 250 W. The power supply size is 40 mm x 81.5mm x 150 mm and has a wire harness for the DC outputs. The AC input plugs directly into the external face of the power supply; refer to the following figure for more information.

Figure 6. Power Supply Enclosure Drawing

#### Notes:

1. All dimensions are in millimeter.

## 3.2 Output Connectors

Listed or recognized component appliance wiring material (AVLV2), CN, **rated min 80°C**, 300 VDC should be used for all output wiring.

| Table 4. Intel® | 250W PSU | Cable Lengths |  |

|-----------------|----------|---------------|--|

|-----------------|----------|---------------|--|

| From                         | Length<br>(mm) | To connector # | Description               |

|------------------------------|----------------|----------------|---------------------------|

| Power Supply cover exit hole | 230            | P1             | Baseboard Power Connector |

| From                         | Length<br>(mm) | To connector # | Description                     |

|------------------------------|----------------|----------------|---------------------------------|

| Power Supply cover exit hole | 220            | P2             | Processor Power Connector       |

| Power Supply cover exit hole | 440            | P7             | SATA Drive Power Connector      |

| Power Supply cover exit hole | 600            | P3             | Mini SATA Drive Power Connector |

| P7                           | 185            | P6             | SATA Drive Power Connector      |

| P6                           | 185            | P5             | SATA Drive Power Connector      |

| P5                           | 185            | P4             | SATA Drive Power Connector      |

## 3.2.1 Baseboard power connector (P1)

Connector housing: 24-Pin Molex\* Mini-Fit Jr. 39-01-2200 or equivalent. Contact: Molex\* Mini-Fit, HCS, female, crimp 44476-1111 or equivalent approved by Intel<sup>®</sup>.

#### Table 5. P1 Main Power Connector

| Pin | Signal  | 18 AWG Color         | Pin | Signal   | 18 AWG Color      |

|-----|---------|----------------------|-----|----------|-------------------|

| 1*  | +3.3VDC | Orange               | 11  | +3.3VDC  | Orange            |

|     | 3.3V S  | Orange (24AWG)       | 12  | -12VDC   | Blue              |

| 2   | +3.3VDC | Orange               | 13  | GND      | Black             |

| 3   | GND     | Black                | 14  | PSON#    | Green (24AWG)     |

| 4   | +5VDC   | Red                  | 15* | GND      | Black             |

| 5   | GND     | Black                |     | COMRS    | Black (24AWG)     |

| 6   | +5VDC   | Red                  | 16  | GND      | Black             |

| 7   | GND     | Black                | 17  | GND      | Black             |

| 8   | PWR OK  | Gray                 | 18  | Reserved | N.C.              |

| 9   | 5 VSB   | Purple               | 19  | +5VDC    | Red               |

| 10* | +12V    | Yellow               | 20* | +5VDC    | Red               |

|     | 12VRS   | Yellow/White (24AWG) |     | 5VRS     | Red/White (24AWG) |

Notes:

1. Remote Sense wire double-crimped.

2. P1 add cable bend requirement at P1.

### 3.2.2 Processor Power Connector (P2)

Connector housing: 8-Pin Molex\* 39-01-2085 or equivalent. Contact: 44476-1111 or equivalent.

#### Table 6. P2 Processor Power Connector

| Pin | Signal | 20 AWG color | Pin | Signal | 20 AWG Color |

|-----|--------|--------------|-----|--------|--------------|

| 1   | COM    | Black        | 5   | +12V   | Yellow       |

| 2   | COM    | Black        | 6   | +12V   | Yellow       |

| 3   | COM    | Black        | 7   | +12V   | Yellow       |

| 4   | СОМ    | Black        | 8   | +12V   | Yellow       |

## 3.2.3 SATA Hard Drive Power Connectors (P4, P5, P6, P7)

Connector housing: JWT A3811H00-5P (94V2) or equivalent. Contact: JWT A3811TOP-0D or equivalent.

| Pin | Signal | 18 AWG Color |

|-----|--------|--------------|

| 1   | +3.3V  | Orange       |

| 2   | GND    | Black        |

| 3   | +5VDC  | Red          |

| 4   | GND    | Black        |

| 5   | +12V   | Yellow       |

#### Table 7. SATA Power Connector

## 3.2.4 Mini SATA Hard Drive Power Connectors (P3)

Connector housing: AMPHENDOL\* SSATA-111-1201-1-3 or equivalent.

#### Table 8. SATA Power Connector

| Pin | Signal | 18 AWG Color |

|-----|--------|--------------|

| 1   | N/C    | N/C          |

| 2   | +5V    | Red          |

| 3   | +5V    | Red          |

| 4   | N/C    | N/C          |

| 5   | GND    | Black        |

| 6   | GND    | Black        |

## 3.3 AC Inlet Connector

The AC input connector should be an *IEC 320 C-14* power inlet. This inlet is rated for 10A/250 VAC.

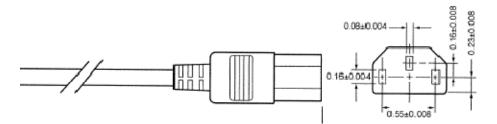

### 3.3.1 AC Power Cord Specification Requirements

The AC power cord must meet the following specification requirements:

| Cable Type         | SJT    |

|--------------------|--------|

| Wire Size          | 16 AWG |

| Temperature Rating | 105º C |

| Amperage Rating    | 13 A   |

| Voltage Rating     | 125 V  |

Figure 7. AC Power Cord Specifications

## 3.4 Marking and Identification

The power supply module marking supports the following requirements: safety agency requirements; government requirements (if required; for example, point of manufacturing); power supply vendor requirements; and Intel<sup>®</sup> manufacturing and field support requirements.

## 3.5 Efficiency

The power supply should have a recommended efficiency of 85% at maximum load and over the specified AC voltage.

## 3.6 AC Input Voltage

The power supply must operate within all specified limits over the following input voltage ranges, shown in the following table.

| Parameter          | Min     | Rated        | Max     | Max Input AC Current |

|--------------------|---------|--------------|---------|----------------------|

| Line Voltage (110) | 90Vrms  | 100-127 Vrms | 140Vrms | 6 Arms1              |

| Line Voltage (220) | 180Vrms | 200-240 Vrms | 264Vrms | 3 Arms2              |

| Frequency          | 47 Hz   | 50/60Hz      | 63 Hz   |                      |

#### Table 9. AC Input Rating

Notes:

1. Maximum input current at low input voltage range should be measured at 90 VAC at max load.

2. Maximum input current at high input voltage range should be measured at 180 VAC at max load.

## 3.7 Output Power/Currents

The following tables define two power and current ratings for this 350-W power supply. The combined output power of all outputs should not exceed the rated output power. The power supply must meet both static and dynamic voltage regulation requirements for the minimum loading conditions.

#### Table 10. Load Ratings

| Voltage | Minimum | Maximum | Output Power |

|---------|---------|---------|--------------|

| +3.3 V  | 0.1 A   | 6 A     | 19.8 W       |

| +5 V    | 0.1 A   | 12 A    | 60 W         |

| +12 V   | 0.75 A  | 17 A    | 204 W        |

| -12 V   | 0 A     | 0.5 A   | 6 W          |

| +5 VSB  | 0.05 A  | 2.0 A   | 10 W         |

Notes:

1. The total output for this PSU is 250W.

2. The total output of +3.3V&+5V will not exceed 60W

3. Peak power shall be 300W for 10sec. The peak 12V current shall be 1sec.

## 3.8 Protection Circuits

Protection circuits inside the power supply should cause only the power supply's main outputs to shut down. If the power supply latches off due to a protection circuit tripping, an AC cycle

OFF for 15sec min (with +5VSB/0.1A) and a PSON# cycle HIGH for 1sec shall be able to reset the power supply.

## 3.8.1 Over Current Protection (OCP)

Each output shall have individual OCP protection circuits. The PSU shall shutdown and latch off after an over current condition occurs. Whereas OCP of +5VSB shall turn the power supply into "hiccup mode" until the OCP condition removed. The values are measured at the PSU harness connectors and shall not be damaged from repeated power cycling in this condition. There shall be current sensors and limit circuits to shut down the entire power supply if the limit is exceeded. The limits are listed below.

| Output Voltage | Continuous Load   |                   |  |

|----------------|-------------------|-------------------|--|

|                | Current Limit MIN | Current Limit MAX |  |

| +12V           | 23A               | 25A               |  |

| +5V            | 14.4 A            | 25A               |  |

| +3.3V          | 15A               | 30A               |  |

| -12V           |                   | 4A                |  |

| +5VSB          |                   | 4.5A              |  |

#### Table 11. Over Load Protection (OCP) Limits

## 3.8.2 Over Voltage Protection (OVP)

Each output shall have individual OVP protection circuits built in and it shall be locally sensed. The PSU shall shutdown and latch off after an over voltage condition occurs. The output voltages are measured at the harness connectors. The voltage shall never exceed the maximum levels when measured at the power pins of the output harness connector during any single point of fail. The voltage shall never trip any lower than the minimum levels when measured at the power pins of the connector.

| Output Voltage | OVP MIN (V) | OVP MAX (V) |

|----------------|-------------|-------------|

| +3.3V          | 3.7         | 4.5         |

| +5V            | 5.6         | 6.5         |

| +12V           | 13.3        | 15.6        |

| -12V           | -13.3       | -15.6       |

| +5VSB          | 5.6         | 6.5         |

#### Table 12. Over Voltage Protection (OVP) Limits

## 3.8.3 Over Temperature Protection (OTP)

The power supply shall be protected against over temperature conditions caused by loss of fan cooling or excessive ambient temperature. In an OTP condition the PSU will shut down. When the power supply temperature drops to within specified limits, the power supply shall restore power automatically, while the +5VSB remains always on. The OTP trip level shall have a minimum of 4° C of ambient temperature hysteresis, so that the power supply will not oscillate on and off due to temperature recovery condition.

## 4. 350W Power Subsystem

The power subsystem of the server systems consists of a single, non-redundant 350-W power supply with five outputs: 3.3 V, 5 V, 12 V, -12V and 5 VSB. The form factor fits into a 1U system and provides a wire harness output to the system. An IEC connector is provided on the external face for AC input to the power supply. The power supply provides one; non-redundant 40 mm fan for self-cooling. The power supply fans also provide additional airflow for parts of the system.

The power supply operates within the following voltage ranges and ratings:

| Parameter          | Min                 | Rated                    | Max                 | Max Input AC Current            |

|--------------------|---------------------|--------------------------|---------------------|---------------------------------|

| Line Voltage (110) | 90V <sub>rms</sub>  | 100-127 V <sub>rms</sub> | 140V <sub>rms</sub> | 6 A <sub>rms</sub> <sup>1</sup> |

| Line Voltage (220) | 180V <sub>rms</sub> | 200-240 V <sub>rms</sub> | 264V <sub>rms</sub> | $3 A_{rms}^{2}$                 |

| Frequency          | 47 Hz               | 50/60Hz                  | 63 Hz               |                                 |

#### Table 13. Input Voltage Range

Notes:

1. Maximum input current at low input voltage range shall be measured at 90Vac, at max load.

2. Maximum input current at high input voltage range shall be measured at 180VAC, at max load.

The power supply must operate within all specified limits over the following input voltage ranges shown in the table. Harmonic distortion of up to 10% Total Harmonic Distortion (THD) must not cause the power supply to go out of specified limits.

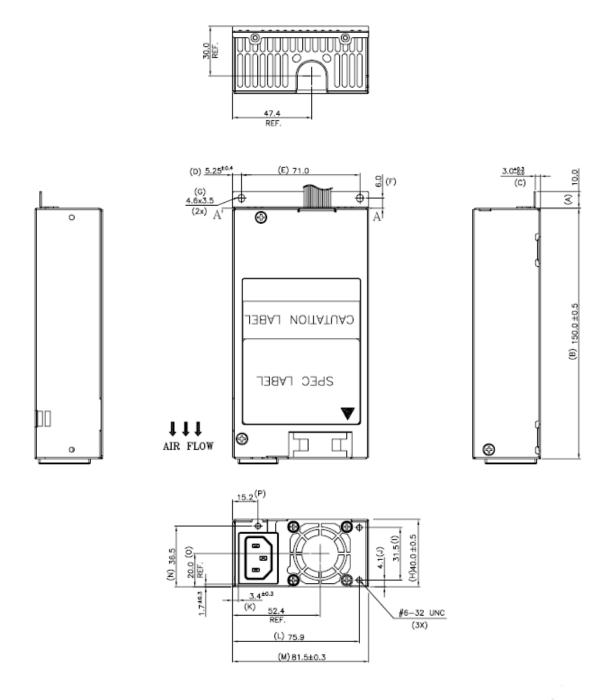

## 4.1 Mechanical Specifications

The 1U 350 W power supply is designed specifically for use in the Intel<sup>®</sup> Server Systems R1304BTLSHBN. The physical size of the power supply enclosure is intended to accommodate power ranges from 350 W. The power supply size is 40 mm x 81.5mm x 150 mm and has a wire harness for the DC outputs. The AC input plugs directly into the external face of the power supply; refer to the following figure for more information.

#### Note:

All dimensions are in millimeter.

## 4.2 Output Connectors

Listed or recognized component appliance wiring material (AVLV2), CN, **rated min 80°C**, 300 VDC should be used for all output wiring.

| From                         | Length<br>(mm) | To connector # | Description                     |

|------------------------------|----------------|----------------|---------------------------------|

| Power Supply cover exit hole | 230            | P1             | Baseboard Power Connector       |

| Power Supply cover exit hole | 220            | P2             | Processor Power Connector       |

| Power Supply cover exit hole | 150            | P3             | AUX Power Connector             |

| Power Supply cover exit hole | 340            | P7             | 2 x 4 HSBP Power Connector      |

| P7                           | 100            | P5             | SATA Drive Power Connector      |

| P5                           | 145            | P4             | SATA Drive Power Connector      |

| Power Supply cover exit hole | 600            | P8             | Mini SATA Drive Power Connector |

#### Table 14. 350W PSU Cable Lengths

#### Baseboard power connector (P1) 4.2.1

Connector housing: 24-Pin Molex\* Mini-Fit Jr. 39-01-2200 or equivalent.

Contact: Molex\* Mini-Fit, HCS, female, crimp 44476-1111 or equivalent approved by Intel®.

| Pin | Signal  | 18 AWG Color         | Pin | Signal   | 18 AWG Color      |

|-----|---------|----------------------|-----|----------|-------------------|

| 1*  | +3.3VDC | Orange               | 11  | +3.3VDC  | Orange            |

|     | 3.3V S  | Orange (24AWG)       | 12  | -12VDC   | Blue              |

| 2   | +3.3VDC | Orange               | 13  | GND      | Black             |

| 3   | GND     | Black                | 14  | PSON#    | Green (24AWG)     |

| 4   | +5VDC   | Red                  | 15* | GND      | Black             |

| 5   | GND     | Black                |     | COMRS    | Black (24AWG)     |

| 6   | +5VDC   | Red                  | 16  | GND      | Black             |

| 7   | GND     | Black                | 17  | GND      | Black             |

| 8   | PWR OK  | Gray                 | 18  | Reserved | N.C.              |

| 9   | 5 VSB   | Purple               | 19  | +5VDC    | Red               |

| 10* | +12V    | Yellow               | 20* | +5VDC    | Red               |

|     | 12VRS   | Yellow/White (24AWG) |     | 5VRS     | Red/White (24AWG) |

#### Table 15. P1 Main Power Connector

Notes:

Remote Sense wire double-crimped.

P1 add cable bend requirement at P1.

#### 4.2.2 Processor Power Connector (P2)

Connector housing: 8-Pin Molex\* 39-01-2085 or equivalent.

Contact: 44476-1111 or equivalent.

#### Table 16, P2 Processor Power Connector

| Pin | Signal | 20 AWG color | Pin | Signal | 20 AWG Color |

|-----|--------|--------------|-----|--------|--------------|

| 1   | COM    | Black        | 5   | +12V   | Yellow       |

| 2   | COM    | Black        | 6   | +12V   | Yellow       |

| 3   | COM    | Black        | 7   | +12V   | Yellow       |

| 4   | COM    | Black        | 8   | +12V   | Yellow       |

## 4.2.3 SATA Hard Drive Power Connectors (P4, P5)

Connector housing: JWT A3811H00-5P (94V2) or equivalent.

Contact: JWT A3811TOP-0D or equivalent.

#### Table 17. SATA Power Connector

| Pin | Signal | 18 AWG Color |

|-----|--------|--------------|

| 1   | +3.3V  | Orange       |

| 2   | GND    | Black        |

| 3   | +5VDC  | Red          |

| 4   | GND    | Black        |

| 5   | +12V   | Yellow       |

## 4.2.4 Mini SATA Hard Drive Power Connectors (P8)

Connector housing: AMPHENDOL\* SSATA-111-1201-1-3 or equivalent.

| Pin | Signal | 18 AWG Color |

|-----|--------|--------------|

| 1   | N/C    | N/C          |

| 2   | +5V    | Red          |

| 3   | +5V    | Red          |

| 4   | N/C    | N/C          |

| 5   | GND    | Black        |

| 6   | GND    | Black        |

#### Table 18. SATA Power Connector

## 4.2.5 AUX Power Connector (P3)

The AUX Power Connector is used for the Power Management Bus- PMBUS.

Connector housing: Molex\* 50-57-9705 or equivalent.

Contact: Molex<sup>\*</sup> 16-02-0087 or equivalent.

#### Table 19. AUX Power Connector

| Pin | Signal | 24 AWG Color | Pin | Signal | 24 AWG Color |

|-----|--------|--------------|-----|--------|--------------|

| 1   | SCL    | White/Green  | 4   | COM    | White/Black  |

| 2   | SDA    | White/Yellow | 5   | +3.3V  | White/Brown  |

| 3   | N/C    | N/C          |     |        |              |

## 4.2.6 Hot-swap Backplane Power Connector (P7)

Connector housing: Molex\* 39-01-2085 or equivalent.

Contact: Molex<sup>\*</sup> 39-00-0079 or equivalent.

#### Table 20. P7 HSBP Power Connector

| Pin | Signal | 18 AWG Color | Pin | Signal | 18 AWG Color |

|-----|--------|--------------|-----|--------|--------------|

| 1   | GND    | Black        | 5   | 12V    | Yellow       |

| 2   | GND    | Black        | 6   | NC     | NC           |

| 3   | +5V    | Red          | 7   | NC     | NC           |

| 4   | NC     | NC           | 8   | 3.3V   | Orange       |

## 4.3 AC Inlet Connector

The AC input connector should be an *IEC 320 C-14* power inlet. This inlet is rated for 10A/250 VAC.

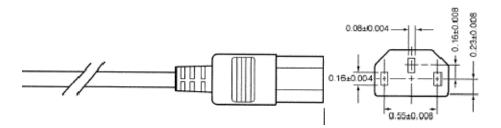

## 4.3.1 AC Power Cord Specification Requirements

The AC power cord must meet the following specification requirements:

| Cable Type         | SJT    |

|--------------------|--------|

| Wire Size          | 16 AWG |

| Temperature Rating | 105º C |

| Amperage Rating    | 13 A   |

| Voltage Rating     | 125 V  |

Figure 9. AC Power Cord Specifications

## 4.4 Marking and Identification

The power supply module marking supports the following requirements: safety agency requirements; government requirements (if required; for example, point of manufacturing); power supply vendor requirements; and Intel<sup>®</sup> manufacturing and field support requirements.

## 4.5 Efficiency

The power supply should have a recommended efficiency of 85% at maximum load and over the specified AC voltage.

## 4.6 AC Input Voltage

The power supply must operate within all specified limits over the following input voltage ranges, shown in the following table.

| Parameter          | Min     | Rated        | Max     | Max Input AC Current |

|--------------------|---------|--------------|---------|----------------------|

| Line Voltage (110) | 90Vrms  | 100-127 Vrms | 140Vrms | 6 Arms1              |

| Line Voltage (220) | 180Vrms | 200-240 Vrms | 264Vrms | 3 Arms2              |

| Frequency          | 47 Hz   | 50/60Hz      | 63 Hz   |                      |

#### Table 21. AC Input Rating

Notes:

- 1. Maximum input current at low input voltage range should be measured at 90 VAC at max load.

- 2. Maximum input current at high input voltage range should be measured at 180 VAC at max load.

## 4.7 Output Power/Currents

The following tables define two power and current ratings for this 350-W power supply. The combined output power of all outputs should not exceed the rated output power. The power supply must meet both static and dynamic voltage regulation requirements for the minimum loading conditions.

| Voltage | Minimum | Maximum | Output Power |

|---------|---------|---------|--------------|

| +3.3 V  | 0.1 A   | 10 A    | 33W          |

| +5 V    | 0.1 A   | 16 A    | 80W          |

| +12 V1  | 0.75 A  | 18 A    | 216W         |

| +12 V2  | 0.75 A  | 18 A    | 216W         |

| -12 V   | 0 A     | 0.5 A   | 6W           |

| +5 VSB  | 0.05 A  | 2.5 A   | 12.5W        |

#### Table 22. Load Ratings

Notes:

1. The total current of +12V1/2 will not exceed 28A.

2. The total output for this PSU is 350W.

3. The total output of +3.3V&+5V will not exceed 100W

## 4.8 Protection Circuits

Protection circuits inside the power supply should cause only the power supply's main outputs to shut down. If the power supply latches off due to a protection circuit tripping, an AC cycle OFF for 15sec min (with +5VSB/0.1A) and a PSON# cycle HIGH for 1sec shall be able to reset the power supply.

## 4.8.1 Over Current Protection (OCP)

Each output shall have individual OCP protection circuits. The PSU shall shutdown and latch off after an over current condition occurs. Whereas OCP of +5VSB shall turn the power supply into "hiccup mode" until the OCP condition removed. The values are measured at the PSU harness connectors and shall not be damaged from repeated power cycling in this condition. There shall be current sensors and limit circuits to shut down the entire power supply if the limit is exceeded. The limits are listed below.

| Output Voltage | Continuous Load   |                   |  |

|----------------|-------------------|-------------------|--|

|                | Current Limit MIN | Current Limit MAX |  |

| +12V1          | 18.2A             | 20A               |  |

| +12V2          | 18.2A             | 20A               |  |

| +5V            | 19.2A             | 24A               |  |

| +3.3V          | 12A               | 15A               |  |

| -12V           |                   | 4A                |  |

| +5VSB          |                   | 4.5A              |  |

#### Table 23. Over Load Protection (OCP) Limits

## 4.8.2 Over Voltage Protection (OVP)

Each output shall have individual OVP protection circuits built in and it shall be locally sensed. The PSU shall shutdown and latch off after an over voltage condition occurs. The output voltages are measured at the harness connectors. The voltage shall never exceed the maximum levels when measured at the power pins of the output harness connector during any single point of fail. The voltage shall never trip any lower than the minimum levels when measured at the pomertor.

#### Table 24. Over Voltage Protection (OVP) Limits

| Output Voltage | OVP MIN (V) | OVP MAX (V) |  |

|----------------|-------------|-------------|--|

| +3.3V          | 3.7         | 4.5         |  |

| +5V            | 5.7         | 6.5         |  |

| +12V1/+12V2    | 13.3        | 15.6        |  |

| -12V           | -13.3       | -15.6       |  |

| +5VSB          | 5.7         | 6.5         |  |

## 4.8.3 Over Temperature Protection (OTP)

The power supply shall be protected against over temperature conditions caused by loss of fan cooling or excessive ambient temperature. In an OTP condition the PSU will shut down. When the power supply temperature drops to within specified limits, the power supply shall restore power automatically, while the +5VSB remains always on. The OTP trip level shall have a minimum of 4°C of ambient temperature hysteresis, so that the power supply will not oscillate on and off due to temperature recovery condition.

## 4.9 PMBus

The PMBus features included in this specification are requirements for ac/dc silver box power supply for use in server systems. This specification is based on the *PMBusTM Specifications Parts I and II*, revision 1.1X3.

### 4.9.1 Related Documents

PMBus<sup>™</sup> Power System Management Protocol Specification Part I – General Requirements, Transport And Electrical Interface; Revision 1.1X3 PMBus<sup>™</sup> Power System Management Protocol Specification Part II – Command Language; Revision 1.1X3 SMBus 2.0.

## 4.9.2 Addressing

The power supply device address locations are shown below. For redundant systems there are two signals to set the address location of the power supply once it is installed in the system; Address0 and Address1. For non-redundant systems the power supply device address locations should align with the Address0/Address1 location of 0/0.

| PDB addressing Address0/Address1 | 0/0 | 0/1 | 1/0 | 1/1 |

|----------------------------------|-----|-----|-----|-----|

| Power supply PMBusTM device      | B0h | B2h | B4h | B6h |

**Note:** Non-redundant power supplies will use the 0/0 address locations.

## 5. Cooling Subsystem

The Intel<sup>®</sup> Server System R1304BTSSFAN, R1304BTLSFAN and R1304BTLSHBN cooling subsystem consists of three fans, CPU air duct, and PS/electronics bay isolation air baffle. These components provide the necessary cooling and airflow to the system. A fan on the processor heatsink is not needed.

To maintain the necessary airflow within the system, the air duct and the top cover must be properly installed.

**Note:** The Intel<sup>®</sup> Server Systems R1304BTSSFAN, R1304BTLSFAN and R1304BTLSHBN do not support redundant cooling. If a fan fails, the system should be powered down as soon as possible to replace the failed fan blower. The system fans are not hot-swappable.

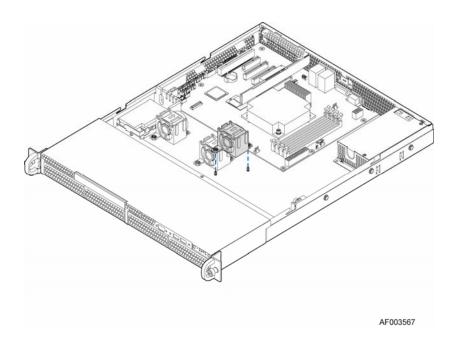

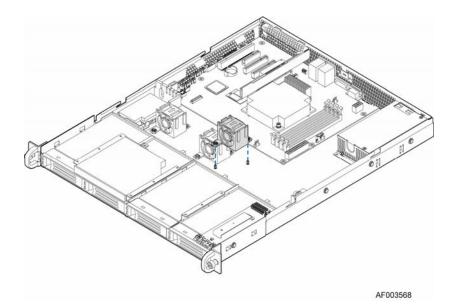

Figure 10. Intel<sup>®</sup> Server System R1304BTSSFAN/R1304BTLSFAN Fan Module Assembly

Figure 11. Intel<sup>®</sup> Server System R1304BTLSHBN Fan Module Assembly

## 5.1 Power Supply Fans

The power supply supports one, non-redundant 40 mm fans. It is responsible for the cooling of the power supply.

## 5.2 CPU Air Duct

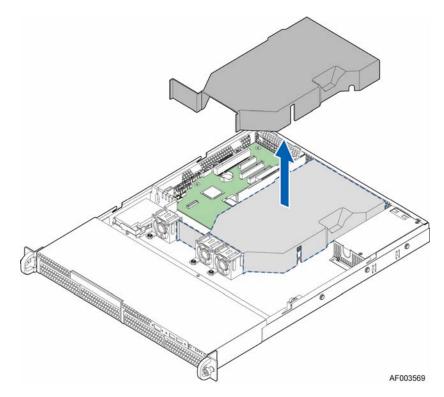

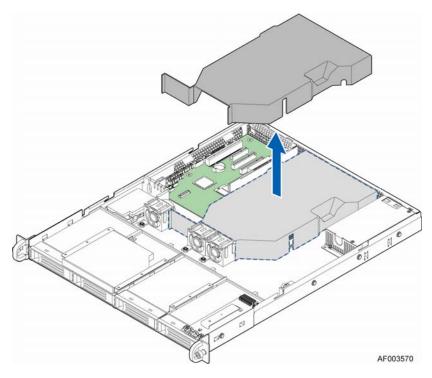

The chassis requires the use of a CPU air duct to direct airflow through the processor's heatsink and memory area.

Figure 12. Intel<sup>®</sup> Server System R1304BTSSFAN/R1304BTLSFAN Air Duct

Figure 13. Intel<sup>®</sup> Server System R1304BTLSHBN Air Duct

# 6. Peripheral and Hard Drive Support

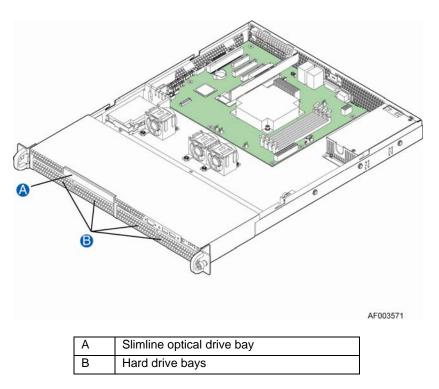

The Intel<sup>®</sup> Server Systems R1304BTSSFAN/R1304BTLSFAN provides support for four fixed hard drive bays and one slimline peripheral drive bay at the front of the chassis. The fixed hard drive bays are designed to support SATA drives only.

Figure 14. Intel<sup>®</sup> Server Systems R1304BTSSFAN/R1304BTLSFAN Drive Bays

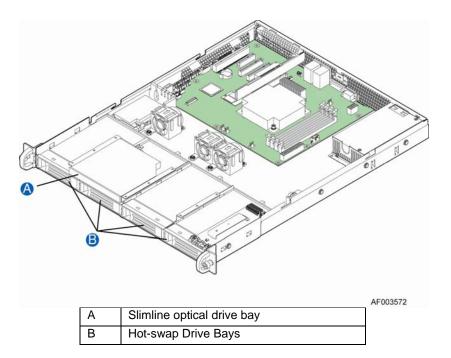

The Intel<sup>®</sup> Server System R1304BTLSHBN provides support for four hot-swap hard drive bays and one slimline peripheral drive bay at the front of the system. The hot-swap drive bays are designed to support SATA/SAS drives.

Figure 15. Intel<sup>®</sup> Server Systems R1304BTLSHBN Drive Bays

## 6.1 Optical Drive Support

Both the fixed and hot-swap systems provide a slimline drive bay that you can configure for an SATA optical CD-ROM or DVD/CDR drive. The slimline devices are not hot-swappable.

## 6.1.1 Optical Drive Support

The server systems support a slimline SATA optical drive.

## 6.2 Hard Disk Drive Support

The Intel<sup>®</sup> Server System R1304BTSSFAN/R1304BTLSFAN supports up to four, 3.5-inch by 1-inch fixed SATA hard disk drives. The drives are mounted inside the chassis and are not hot-swappable. The Intel<sup>®</sup> Server System R1304BTLSHBN supports up to four SATA hard disk drives mounted in hot-swappable drive carriers.

### 6.2.1 System Fan Connectors

The Intel<sup>®</sup> Server Systems R1304BTSSFAN, R1304BTLSFAN and R1304BTLSHBN support three system cooling fans. The following table provides the pin-out for each connector.

| Pin | Signal Name | Туре    | Description                                                           |

|-----|-------------|---------|-----------------------------------------------------------------------|

| 1   | Ground      | Power   | GROUND is the power supply ground.                                    |

| 2   | Fan Power   | Power   | Fan Power                                                             |

| 3   | Fan Tach    | Out     | FAN_TACH signal is connected to the Heceta* to monitor the FAN speed. |

| 4   | PWM         | Control | Pulse Width Modulation – Fan Speed Control signal                     |

#### Table 25. System Four-pin Fan Headers Pin-outs

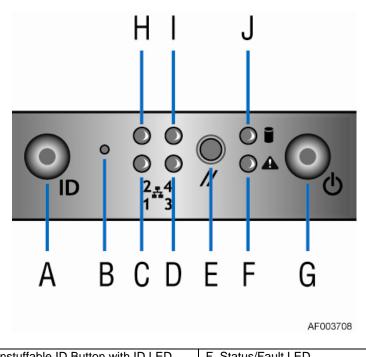

# 7. Front Control Panel

The standard control panel supports a power button, status LED, hard drive activity LED, and NIC 1 and NIC 2 activity LEDs. The control panel assembly comes pre-assembled into the chassis. The control panel assembly module slides into a predefined slot on the front of the chassis. Once installed, communication to the server board is achieved through a standard 24-pin cable connected directly to the server board.

**Note:** The LAN3/4 LEDs are not used on the Intel<sup>®</sup> Server Systems R1304BTSSFAN, R1304BTLSFAN or R1304BTLSHBN. Unstuffable ID Button with ID LED and Status/Fault LED are not used on Intel<sup>®</sup> Server System R1304BTSSFAN.

| A. Unstuffable ID Button with ID LED | F. Status/Fault LED            |

|--------------------------------------|--------------------------------|

| B. NMI Button                        | G. Power Button with power LED |

| C. LAN1 LED                          | H. LAN2 LED                    |

| D. LAN3 LED                          | I. LAN4 LED                    |

| E. Reset Button                      | J. HDD LED                     |

Figure 16. Intel<sup>®</sup> Server System R1304BTSSFAN/R1304BTLSFAN/R1304BTLSHBN Front Control Panel

#### Table 26. Control Panel LED Functions

| LED                               | Color | State        | Description             |  |  |

|-----------------------------------|-------|--------------|-------------------------|--|--|

| NIC1/NIC2                         | Green | On           | NIC Link/no access      |  |  |

| Activity                          | Green | Blink        | LAN access              |  |  |

| Davida (Ola an                    | Green | On           | Power on                |  |  |

| Power/Sleep<br>(on standby power) | Gleen | Blink        | Sleep/ACPI S1 state     |  |  |

|                                   | Off   | Off          | Power Off/ACPI S4 state |  |  |

| System Status                     | N/A   | N/A          | N/A                     |  |  |

| (on standby power)                |       |              |                         |  |  |

| Disk Activity                     | Green | Random blink | HDD access              |  |  |

|                                   | Off   | Off          | No hard disk activity   |  |  |

## 7.1.1 Power/Sleep LED

#### Table 27. SSI Power LED Operation

| State     | Power Mode | LED          | Description                                                                                            |

|-----------|------------|--------------|--------------------------------------------------------------------------------------------------------|

| Power Off | Non-ACPI   | Off          | System power is off, and the BIOS has not initialized the chipset.                                     |

| Power On  | Non-ACPI   | On           | System power is on, but the BIOS has not yet initialized the chipset.                                  |

| S5        | ACPI       | Off          | Mechanical is off, and the operating system has not saved any context to the hard disk.                |

| S4        | ACPI       | Off          | Mechanical is off, and the operating system has saved context to the hard disk.                        |

| S3-S1     | ACPI       | Slow blink 1 | DC power is still on. The operating system has saved context and gone into a level of low-power state. |

| S0        | ACPI       | Steady on    | System and the operating system are up and running.                                                    |

#### Note:

The blink rate is ~ 1 Hz at 50% duty cycle.

## 7.1.2 System Status LED

The system status LED is available on the  $Intel^{\ensuremath{\mathbb{R}}}$  Server Systems R1304BTLSFAN and R1304BTLSHBN.

#### 7.1.3 Drive Activity LED

The drive activity LED on the front panel indicates drive activity from the onboard hard disk controllers.

## 8. PCI Riser Cards and Assembly

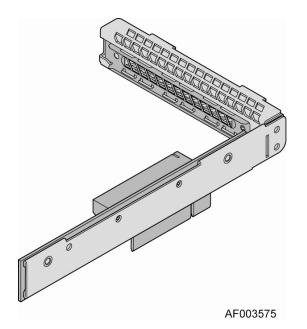

The Intel<sup>®</sup> Server System R1304BTSSFAN, R1304BTLSFAN and R1304BTLSHBN provides one PCI Express\* x8 slot which supports one riser card with one riser card slot. The riser card supports one low-profile PCI Express\* x8 add-in card that consumes power less than 15 W.

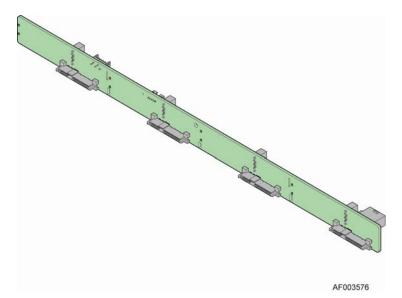

Figure 17. PCI–E Riser Card Assembly For Intel<sup>®</sup> Server System R1304BTSSFAN, R1304BTLSFAN and R1304BTLSHBN

# 9. Intel<sup>®</sup> Server System R1304BTLSHBN Passive SAS/SATA Hot-swap Backplane

The Intel<sup>®</sup> Server System R1304BTLSHBN supports a passive backplane designed to be compatible with the Intel<sup>®</sup> Server Board S1200BTL. The Intel<sup>®</sup> Server Board S1200BTL is connected directly to the SATA backplane (default) or you can connect the backplane to an add-in SAS or SATA adapter.

The system supports a multi-functional SATA/SAS backplane with the following features:

- Four SATA/SAS compatible hot-swap hard drive connectors

- Four SATA/SAS connectors to the baseboard

- Hard Drive Activity LED for each hard drive connector

- One 2x4-pin power connector

The Intel<sup>®</sup> Server Board S1200BTL on-board SATA controller supports the following RAID arrays:

- Intel<sup>®</sup> Embedded Server RAID Technology II RAID 0, 1, and 10.

- Intel<sup>®</sup> Matrix Storage Technology RAID 0, 1, 10, or 5 (Microsoft Windows\* only)

This system support drive status LEDs, You can determine a failed drive and drive rebuild activity by observing the drive activity LED.

Figure 18. Intel<sup>®</sup> Server System R1304BTLSHBN Hot-swap Backplane

| Pin # | Signal Name   |

|-------|---------------|

| 1     | Ground        |

| 2     | Ground        |

| 3     | P5V           |

| 4     | P5V           |

| 5     | P12V          |

| 6     | P12V          |

| 7     | No Connection |

| 8     | P3V3          |

#### Table 28. Passive SATA/SAS Backplane Power Connector Pin-out

#### Table 29. Passive SATA/SAS Backplane Connector to Hard Drive Pin-out

| Pin # | Signal Name      |

|-------|------------------|

| S1    | Ground           |

| S2    | SAS_DRVxA_RX_P   |

| S3    | SAS_DRVxA_RX_N   |

| S4    | Ground           |

| S5    | SAS_DRVxA_TX_N   |

| S6    | SAS_DRVxA_TX_P   |

| S7    | Ground           |

| P1    | TP               |

| P2    | ТР               |

| P3    | ТР               |

| P4    | Ground           |

| P5    | Ground           |

| P6    | Ground           |

| P7    | P5V_DRVx_PRECHG  |

| P8    | P5V              |

| P9    | P5V              |

| P10   | Ground           |

| P11   | LED_DRVx_READY_N |

| P12   | Ground           |

| P13   | P12V_DRVx_PRECHG |

| P14   | P12V             |