# **SCB2 Server Board**

## **Technical Product Specification**

Intel Order Number A70821-003

**Revision 2.0**

August 2002

**Enterprise Platforms and Services Marketing**

## **Revision History**

| Date     | Revision<br>Number | Modifications                                                                                                                                               |

|----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8/1/01   | .05                | First preliminary release.                                                                                                                                  |

| 10/05/01 | 1.0                | First production level release.                                                                                                                             |

| 12/31/01 | 1.1                | Added Riser Card appendix, added PCI riser pin-out tables,                                                                                                  |

| 8/20/02  | 2.0                | Added Appendix C: SCB2 Errata; modified BIOS setup section to reflect<br>options in most recent BIOS; added items to Appendix A; updated POST code<br>table |

## Disclaimers

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no

The SCB2 server system may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2001,2002.

## **Table of Contents**

| 1. | Introd  | uction                                        | 1    |

|----|---------|-----------------------------------------------|------|

| 2. | SCB2    | Server Board Overview                         | 2    |

| 2  | 2.1 SC  | CB2 Feature Set                               | 2    |

| 3. | Functi  | ional Architecture                            | 5    |

| 3  | 3.1 Pr  | ocessor and Memory Subsystem                  | 5    |

|    | 3.1.1   | Processor Support                             | 5    |

|    | 3.1.2   | Memory Subsystem                              | 7    |

| 3  | 3.2 Se  | erverWorks ServerSet* III HE-SL Chipset       | 10   |

|    | 3.2.1   | CNB20HE-SL Champion North Bridge              | 11   |

|    | 3.2.2   | CIOB                                          | 12   |

|    | 3.2.3   | CSB5                                          | 13   |

| 3  | 3.3 Su  | iper I/O                                      | 14   |

|    | 3.3.1   | GPIOs                                         | 15   |

|    | 3.3.2   | Real-time Clock                               | 15   |

|    | 3.3.3   | Serial Ports                                  | 15   |

|    | 3.3.4   | BIOS Flash                                    | 19   |

| 3  | 3.4 Cl  | ock Generation and Distribution               | . 20 |

| 3  | 3.5 PC  | CI I/O Subsystem                              | 20   |

|    | 3.5.1   | P32-A: 32-bit, 33-MHz PCI Subsystem           | 21   |

|    | 3.5.2   | P64-B and P64-C: 64-bit, 66-MHz PCI Subsystem | 21   |

|    | 3.5.3   | Ultra 160* SCSI                               | 23   |

|    | 3.5.4   | ATA-100                                       | 23   |

|    | 3.5.5   | Video Controller                              | 24   |

|    | 3.5.6   | Network Interface Controller (NIC)            | 25   |

| 3  | 3.6 Int | errupt Routing                                | 25   |

|    | 3.6.1   | Legacy Interrupt Routing                      | 26   |

|    | 3.6.2   | APIC Interrupt Routing                        | 26   |

|    | 3.6.3   | Serialized IRQ Support                        | 27   |

|    | 3.6.4   | IRQ Scan for PCIIRQ                           | 27   |

| 3  | 8.7 Sy  | stem Reset Control                            | 30   |

|    | 3.7.1   | Power-up Reset                                | 30   |

|    | 3.7.2  | Hard Reset                                     | . 30 |

|----|--------|------------------------------------------------|------|

|    | 3.7.3  | Soft Reset                                     | 30   |

| 4. | Platfo | rm Management Architecture                     | . 31 |

| 4  | .1 IPI | VI Messaging, Commands, and Abstractions       | 33   |

| 4  | .2 Sa  | halee Baseboard Management Controller(BMC)     | 33   |

|    | 4.2.1  | Watchdog Timer                                 | 36   |

| 4  | .3 Se  | nsors                                          | . 37 |

|    | 4.3.1  | Temperature Sensors                            | . 37 |

|    | 4.3.2  | Voltage Sensors                                | . 38 |

|    | 4.3.3  | Processor Voltage Threshold Auto-configuration | 38   |

|    | 4.3.4  | Processor Voltage Mismatch                     | 38   |

|    | 4.3.5  | SCSI Terminator Voltage Sensors                | . 38 |

|    | 4.3.6  | Fan Sensors and Fan Speed Control              | 39   |

|    | 4.3.7  | Missing Processor/Terminator Module Detection  | 40   |

|    | 4.3.8  | Other Sensors                                  | . 41 |

|    | 4.3.9  | Other Monitored Signal Status                  | 41   |

|    | 4.3.10 | Additional Events                              | 42   |

|    | 4.3.11 | POST Error Logging                             |      |

|    | 4.3.12 | POST Progress FIFO                             | 42   |

|    | 4.3.13 | Control Capabilities                           | 43   |

| 4  | .4 Pla | atform Management Connectors                   | 44   |

|    | 4.4.1  | Auxiliary IPMB Connector                       | 44   |

|    | 4.4.2  | ICMB Transceiver Header                        | 44   |

| 4  | .5 Ch  | assis Management Interconnection               | 45   |

|    | 4.5.1  | IPMB Routing                                   | 45   |

|    | 4.5.2  | ICMB Connection                                | 45   |

|    | 4.5.3  | PCI Management Bus Connection                  | 46   |

|    | 4.5.4  | Power Control Signals                          | 46   |

|    | 4.5.5  | Hot-swap Backplane Management                  | 46   |

| 4  | .6 Fie | eld Replaceable Unit Information               | 46   |

|    | 4.6.1  | System Interface Ports                         | 46   |

|    | 4.6.2  | BMC Front Panel Control                        | 47   |

| 4  | .7 Int | elligent Platform Management Buses (IPMB)      | 49   |

| 4  | .8 PC  | CI Management Bus                              | 50   |

| 4.9  | Priv         | ate Management Buses                                                                | 50 |

|------|--------------|-------------------------------------------------------------------------------------|----|

| 4.10 | W            | ake-on-LAN / Power On LAN and Magic Packet Support                                  | 50 |

| 4.1  | 0.1          | Wake-on-LAN in S4/S5                                                                | 50 |

| 4.11 | Er           | mergency Management Port (EMP)                                                      | 51 |

| 4.1  | 1.1          | Serial/Modem Alerting                                                               | 51 |

| 4.1  | 1.2          | Serial/Modem Channel Specifications                                                 | 52 |

| 4.1  | 1.3          | BMC-Emergency Management Port Connection                                            | 53 |

| 4.1  | 1.4          | Emergency Management Port Direct Connect and Modem Connect Options                  | 53 |

| 4.1  | 1.5          | Emergency Management Port Access Mode Options                                       | 53 |

| 4.1  | 1.6          | BIOS Console Redirection Interaction with the Emergency Management Port             | 55 |

| 4.1  | 1.7          | PPP Activation of the Emergency Management Port                                     | 55 |

| 4.1  | 1.8          | Callback Security Option                                                            | 55 |

|      | 1.9<br>inage | Microsoft* 'Headless' Console Escape Sequence Activation of the Emergency ment Port | 56 |

| 4.1  | 1.10         | Ring Indicate and DCD Activation of the Emergency Management Port                   | 56 |

| 4.1  | 1.11         | Emergency Management Port Interaction with Wake-on-Ring                             | 56 |

| 4.1  | 1.12         | Activation of the Emergency Management Port during Console Redirection              | 57 |

| 4.1  | 1.13         | System Management Software Activation of the Emergency Management Port .            | 57 |

| 4.1  | 1.14         | Modem Setup                                                                         | 58 |

| 4.1  | 1.15         | Connection Timeout                                                                  | 58 |

| 4.1  | 1.16         | Emergency Management Port User Passwords                                            | 58 |

| 4.1  | 1.17         | Invalid Password Handling                                                           | 58 |

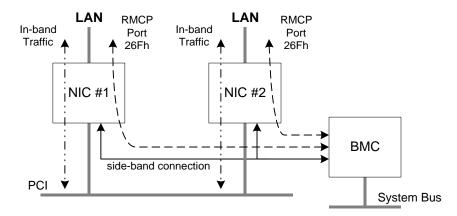

| 4.12 | Di           | rect Platform Control (IPMI over LAN)                                               | 58 |

| 4.1  | 2.1          | LAN Channel Specifications                                                          | 60 |

| 4.1  | 2.2          | Network Controller Teaming and Failover Restrictions                                | 60 |

| 4.1  | 2.3          | LAN Drivers and Setup                                                               | 61 |

| 4.1  | 2.4          | BIOS Boot Flags                                                                     | 61 |

| 4.1  | 2.5          | Boot Flags and LAN Console Redirection                                              | 61 |

| 4.13 | Pl           | atform Event Filtering and Alerting                                                 | 61 |

| 4.1  | 3.1          | Pre-defined Event Filters                                                           | 62 |

| 4.1  | 3.2          | Alert Policies                                                                      | 63 |

| 4.1  | 3.3          | Alert Destinations                                                                  | 63 |

| 4.1  | 3.4          | Alert Destination Priorities                                                        | 64 |

| 4.1  | 3.5          | Alert Acknowledge                                                                   |    |

| 4.1  | 3.6          | System Identification in Alerts                                                     | 65 |

|    | 4.13.7                                                                                                     | Platform Alerting Setup                                                                                                                                                                                                                                                                                                                               | 65                                                             |

|----|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|    | 4.13.8                                                                                                     | Alerting On Power-Down Events                                                                                                                                                                                                                                                                                                                         | 65                                                             |

|    | 4.13.9                                                                                                     | Alerting On System Reset Events                                                                                                                                                                                                                                                                                                                       | 65                                                             |

|    | 4.13.10                                                                                                    | Alert-in-Progress Termination                                                                                                                                                                                                                                                                                                                         | 66                                                             |

| 4. | .14 A                                                                                                      | CPI Support                                                                                                                                                                                                                                                                                                                                           | 66                                                             |

|    | 4.14.1                                                                                                     | ACPI Power Control Support                                                                                                                                                                                                                                                                                                                            | 66                                                             |

|    | 4.14.2                                                                                                     | One- and Two-Button Model                                                                                                                                                                                                                                                                                                                             | 66                                                             |

|    | 4.14.3                                                                                                     | Watchdog Timer Operation under ACPI Sleep                                                                                                                                                                                                                                                                                                             | 67                                                             |

|    | 4.14.4                                                                                                     | Fan Control under ACPI                                                                                                                                                                                                                                                                                                                                | 67                                                             |

|    | 4.14.5                                                                                                     | ACPI Power State Notification                                                                                                                                                                                                                                                                                                                         | 67                                                             |

|    | 4.14.6                                                                                                     | Wake-Up Sources (ACPI and Legacy)                                                                                                                                                                                                                                                                                                                     | 67                                                             |

| 4. | .15 S                                                                                                      | ecure Mode Control                                                                                                                                                                                                                                                                                                                                    | 68                                                             |

|    | 4.15.1                                                                                                     | Front Panel Lockout                                                                                                                                                                                                                                                                                                                                   | 68                                                             |

|    | 4.15.2                                                                                                     | Video Blank and Floppy Write Protect                                                                                                                                                                                                                                                                                                                  | 68                                                             |

|    | 4.15.3                                                                                                     | Keyboard / Mouse Inactivity Time-out                                                                                                                                                                                                                                                                                                                  | 68                                                             |

| 5. | System                                                                                                     | BIOS                                                                                                                                                                                                                                                                                                                                                  | 69                                                             |

|    | 5.1.1                                                                                                      | System Flash ROM Layout                                                                                                                                                                                                                                                                                                                               | 69                                                             |

| 5. | .2 Sys                                                                                                     | stem Configuration and Initialization                                                                                                                                                                                                                                                                                                                 | 69                                                             |

|    | 5.2.1                                                                                                      | Memory                                                                                                                                                                                                                                                                                                                                                | 69                                                             |

|    | 5.2.1                                                                                                      | wentory                                                                                                                                                                                                                                                                                                                                               | . 00                                                           |

|    | 5.2.1                                                                                                      | Processors                                                                                                                                                                                                                                                                                                                                            |                                                                |

|    | 5.2.2                                                                                                      |                                                                                                                                                                                                                                                                                                                                                       | 72                                                             |

|    | 5.2.2                                                                                                      | Processors                                                                                                                                                                                                                                                                                                                                            | 72<br>72                                                       |

|    | 5.2.2<br>5.2.3<br>5.2.4                                                                                    | Processors<br>Extended System Configuration Data (ESCD) and Plug and Play (PnP)                                                                                                                                                                                                                                                                       | 72<br>72<br>74                                                 |

|    | 5.2.2<br>5.2.3<br>5.2.4                                                                                    | Processors<br>Extended System Configuration Data (ESCD) and Plug and Play (PnP)<br>NVRAM API                                                                                                                                                                                                                                                          | 72<br>72<br>74<br>74                                           |

|    | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                                                                           | Processors<br>Extended System Configuration Data (ESCD) and Plug and Play (PnP)<br>NVRAM API<br>Automatic Detection of Video Adapters                                                                                                                                                                                                                 | 72<br>72<br>74<br>74<br>74                                     |

|    | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6                                                                  | Processors<br>Extended System Configuration Data (ESCD) and Plug and Play (PnP)<br>NVRAM API<br>Automatic Detection of Video Adapters<br>Keyboard/Mouse Configuration                                                                                                                                                                                 | 72<br>72<br>74<br>74<br>74<br>74<br>75                         |

| 5. | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8                                                | Processors<br>Extended System Configuration Data (ESCD) and Plug and Play (PnP)<br>NVRAM API<br>Automatic Detection of Video Adapters<br>Keyboard/Mouse Configuration<br>Floppy Drives                                                                                                                                                                | 72<br>72<br>74<br>74<br>74<br>75<br>75                         |

| 5. | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8                                                | Processors<br>Extended System Configuration Data (ESCD) and Plug and Play (PnP)<br>NVRAM API<br>Automatic Detection of Video Adapters<br>Keyboard/Mouse Configuration<br>Floppy Drives<br>Universal Serial Bus (USB)                                                                                                                                  | 72<br>72<br>74<br>74<br>74<br>75<br>75<br>76                   |

| 5. | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>.3 BIC                                      | Processors<br>Extended System Configuration Data (ESCD) and Plug and Play (PnP)<br>NVRAM API<br>Automatic Detection of Video Adapters<br>Keyboard/Mouse Configuration<br>Floppy Drives<br>Universal Serial Bus (USB)<br>OS-Supported Server Management Features                                                                                       | 72<br>72<br>74<br>74<br>74<br>75<br>75<br>75<br>76             |

| -  | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>.3 BIC<br>5.3.1<br>5.3.2                    | Processors<br>Extended System Configuration Data (ESCD) and Plug and Play (PnP)<br>NVRAM API<br>Automatic Detection of Video Adapters<br>Keyboard/Mouse Configuration<br>Floppy Drives<br>Universal Serial Bus (USB)<br>S-Supported Server Management Features<br>Console Redirection                                                                 | 72<br>72<br>74<br>74<br>74<br>75<br>75<br>76<br>80             |

| -  | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>.3 BIC<br>5.3.1<br>5.3.2<br>.4 Wir          | Processors<br>Extended System Configuration Data (ESCD) and Plug and Play (PnP)<br>NVRAM API<br>Automatic Detection of Video Adapters<br>Keyboard/Mouse Configuration<br>Floppy Drives<br>Universal Serial Bus (USB)<br>OS-Supported Server Management Features<br>Console Redirection<br>Service Partition Boot                                      | 72<br>72<br>74<br>74<br>75<br>75<br>76<br>80<br>80             |

| 5. | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>.3 BIC<br>5.3.1<br>5.3.2<br>.4 Wir<br>5.4.1 | Processors<br>Extended System Configuration Data (ESCD) and Plug and Play (PnP)<br>NVRAM API<br>Automatic Detection of Video Adapters<br>Keyboard/Mouse Configuration<br>Floppy Drives<br>Universal Serial Bus (USB)<br>OS-Supported Server Management Features<br>Console Redirection<br>Service Partition Boot<br>hdows* Compatibility              | 72<br>72<br>74<br>74<br>75<br>75<br>76<br>80<br>80<br>81       |

| 5. | 5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>.3 BIC<br>5.3.1<br>5.3.2<br>.4 Wir<br>5.4.1 | Processors<br>Extended System Configuration Data (ESCD) and Plug and Play (PnP)<br>NVRAM API<br>Automatic Detection of Video Adapters<br>Keyboard/Mouse Configuration<br>Floppy Drives<br>Universal Serial Bus (USB)<br>OS-Supported Server Management Features<br>Console Redirection<br>Service Partition Boot<br>dows* Compatibility<br>Quiet Boot | 72<br>74<br>74<br>74<br>75<br>75<br>76<br>80<br>80<br>81<br>82 |

| 5.6    | BIC   | DS and System Setup                        |     |

|--------|-------|--------------------------------------------|-----|

| 5.6    | 6.1   | BIOS Setup Utility                         |     |

| 5.7    | BIC   | DS Security Features                       |     |

| 5.7    | 7.1   | Operating Model                            |     |

| 5.7    | 7.2   | Password Protection                        |     |

| 5.7    | 7.3   | Inactivity Timer                           | 101 |

| 5.7    | 7.4   | Hot Key Activation                         | 102 |

| 5.7    | 7.5   | Password Clear Jumper                      | 102 |

| 5.7    | 7.6   | Secure Mode (Unattended Start)             | 102 |

| 5.7    | 7.7   | Front Panel Lock                           | 102 |

| 5.7    | 7.8   | Video Blanking                             | 102 |

| 5.7    | 7.9   | PS/2 Keyboard And Mouse Lock               | 102 |

| 5.7    | 7.10  | Secure Boot (Unattended Start)             | 102 |

| 5.8    | OE    | M Splash Screen                            | 103 |

| 5.9    | Lo    | calization                                 | 103 |

| 6. Erı | ror F | Reporting and Handling                     | 104 |

| 6.1    | Err   | or Sources and Types                       | 104 |

| 6.1    | 1.1   | PCI Bus Errors                             | 104 |

| 6.1    | 1.2   | Processor Failure                          | 104 |

| 6.1    | 1.3   | Processor Bus Errors                       | 104 |

| 6.1    | 1.4   | Single-Bit ECC Error Throttling Prevention | 105 |

| 6.1    | 1.5   | Memory Bus Errors                          | 105 |

| 6.2    | Fa    | ult Resilient Booting                      | 105 |

| 6.2    | 2.1   | FRB Status Flags                           | 106 |

| 6.2    | 2.2   | FRB-3 Retries                              | 106 |

| 6.2    | 2.3   | FRB-3 Processor Disable Sequencing         | 106 |

| 6.2    | 2.4   | FRB Log Limits                             | 107 |

| 6.2    | 2.5   | General Notes on FRB                       | 107 |

| 6.3    | Sys   | stem Fault & Status LEDs                   | 107 |

| 6.3    | 3.1   | DIMM LEDs                                  | 108 |

| 6.3    | 3.2   | CPU LEDs                                   | 108 |

| 6.3    | 3.3   | Fan LED's                                  | 108 |

| 6.3    | 3.4   | 5VSB Status LED                            | 108 |

| 6.3    | 3.5   | System Status LED                          | 108 |

|    | 6.3. | .6   | ID LED                                              | 110 |

|----|------|------|-----------------------------------------------------|-----|

| 6  | .4   | PO   | ST Codes, Error Messages, and Error Codes           | 110 |

|    | 6.4. | .1   | Port-80 Diagnostic LEDs                             | 110 |

|    | 6.4. | 2    | POST Error Codes and Messages                       | 115 |

|    | 6.4. | 3    | POST Error Beep Codes                               | 117 |

| 6  | .5   | "PC  | DST Error Pause" option                             | 118 |

| 7. | SCI  | B2 ( | Connectors and Jumper Blocks                        | 119 |

| 7  | .1   | Mai  | in Power Connector                                  | 119 |

| 7  | .2   | PC   | I I/O Riser Slot Connector                          | 120 |

| 7  | .3   | Sys  | stem Management Headers                             | 123 |

|    | 7.3. | .1   | ICMB Header                                         | 123 |

|    | 7.3. | 2    | OEM IPMB Header                                     | 123 |

|    | 7.3. | 3    | SCSI IPMB Header                                    | 123 |

| 7  | .4   | Fro  | nt Panel Connectors                                 | 124 |

|    | 7.4. | .1   | High Density 100-Pin Floppy/FP/IDE Connector (J2H1) | 125 |

| 7  | .5   | VG   | A Connector                                         | 127 |

| 7  | .6   | SC   | SI Connectors                                       | 128 |

| 7  | .7   | NIC  | Connector                                           | 129 |

| 7  | .8   | AT   | A Connectors                                        | 129 |

| 7  | .9   | US   | B Connector                                         | 131 |

| 7  | .10  | F    | loppy Connector                                     | 132 |

| 7  | .11  | S    | erial Port Connector                                | 132 |

| 7  | .12  | K    | eyboard and Mouse Connector                         | 133 |

| 7  | .13  | N    | liscellaneous Headers                               | 134 |

|    | 7.13 | 3.1  | Fan Headers                                         | 134 |

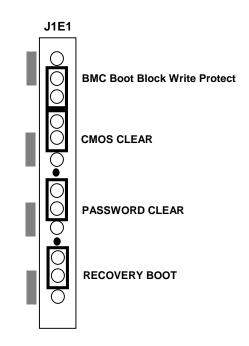

| 7  | .14  | S    | system Recovery and Update Jumpers                  | 135 |

| 7  | .15  | E    | xternal RJ45 Serial Port Jumper Block               | 136 |

| 8. | Ger  | nera | Il Specifications                                   | 137 |

| 8  | .1   | Abs  | solute Maximum Ratings                              | 137 |

| 8  | .2   | SC   | B2 Power Budget                                     | 137 |

| 8  | .3   | Pov  | ver Supply Specifications                           | 138 |

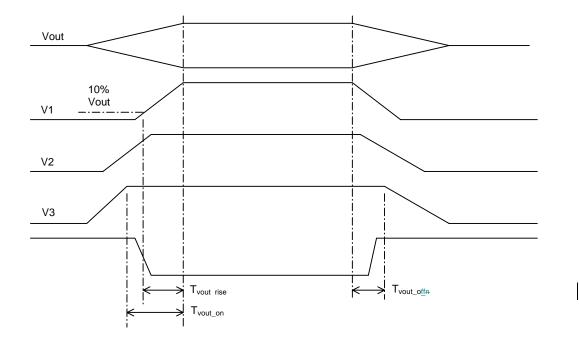

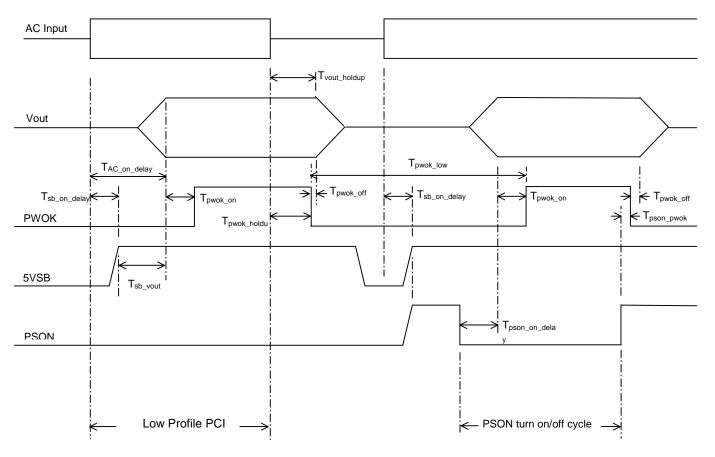

|    | 8.3. | .1   | Power Timing                                        | 138 |

|    | 8.3. | .2   | Voltage Recovery Timing Specifications              | 141 |

| 8  | .4   | Pro  | duct Regulatory Compliance                          | 142 |

| 8.4.1 Product Safety Compliance 142                                                    | 2  |

|----------------------------------------------------------------------------------------|----|

| 8.4.2 Product EMC Compliance 142                                                       | 2  |

| 8.4.3 Product Regulatory Compliance Markings 143                                       | 3  |

| 8.5 Electromagnetic Compatibility Notices 143                                          | 3  |

| 8.5.1 Europe (CE Declaration of Conformity)143                                         | 3  |

| 8.5.2 Australian Communications Authority (ACA) (C-Tick Declaration of Conformity) 143 | 3  |

| 8.5.3 Ministry of Economic Development (New Zealand) Declaration of Conformity 143     | 3  |

| 8.5.4 BSMI (Taiwan)                                                                    | 3  |

| 8.6 Replacing the Back-Up Battery 144                                                  | 4  |

| 8.7 Calculated Mean Time Between Failures (MTBF) 148                                   | 5  |

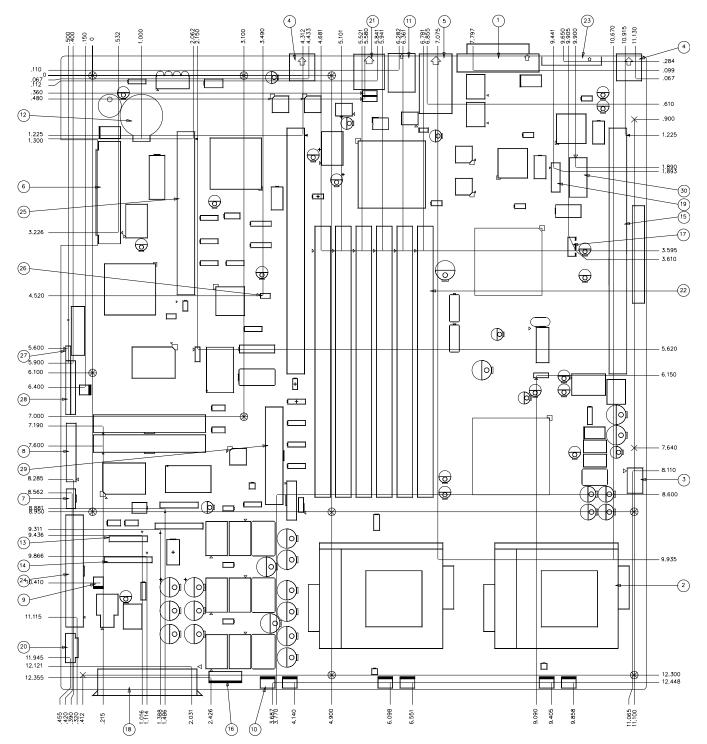

| 8.8 Mechanical Specifications 146                                                      | 6  |

| 8.8.1 PCI Riser Cards 148                                                              | 8  |

| Appendix A: SCB2 Integration and Usage Tips                                            | I  |

| Appendix B: Riser Card Design Guide for Reference Chassis II                           |    |

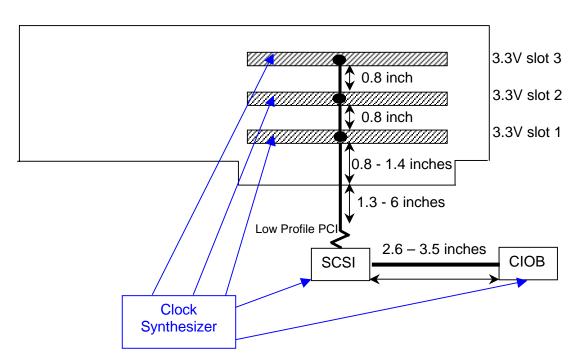

| Routing Rules for SCB2 PCI-66MHz Riser Cards II                                        | 11 |

| Appendix C: SCB2 Errata                                                                | V  |

| GlossaryV                                                                              | /  |

| Reference DocumentsI)                                                                  | X  |

| Index                                                                                  | X  |

## **List of Figures**

| Figure 1. SCB2 Server Board Block Diagram          | 4   |

|----------------------------------------------------|-----|

| Figure 2. Memory Sub-system Block Diagram          | 8   |

| Figure 3. Memory Bank Label Definition             | 9   |

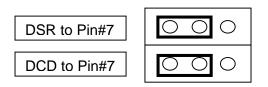

| Figure 4. J6A2 Jumper Block for DSR Signal         | 17  |

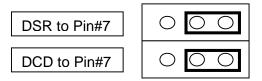

| Figure 5. J6A2 Jumper Block for DCD Signal         | 17  |

| Figure 6. J6A2 Jumper Block for DCD Signal         | 18  |

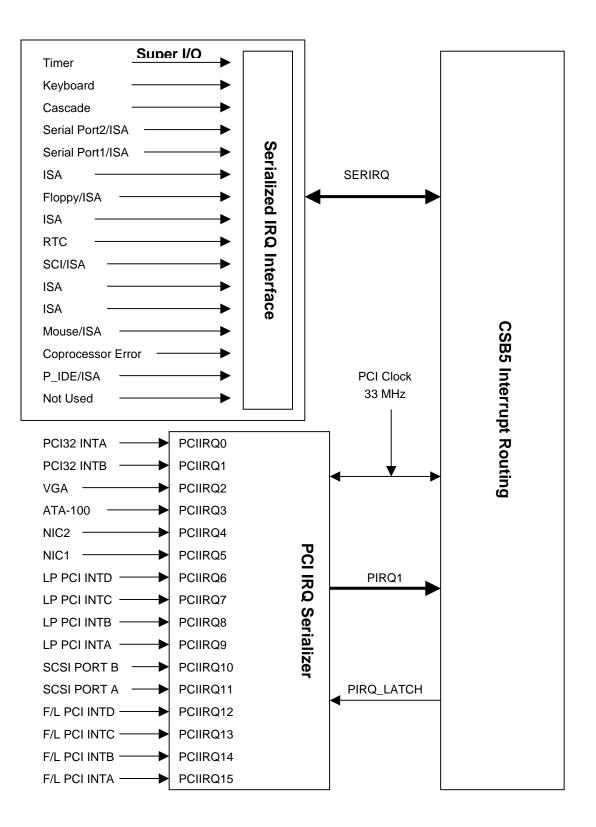

| Figure 7. SCB2 Interrupt Routing Diagram           |     |

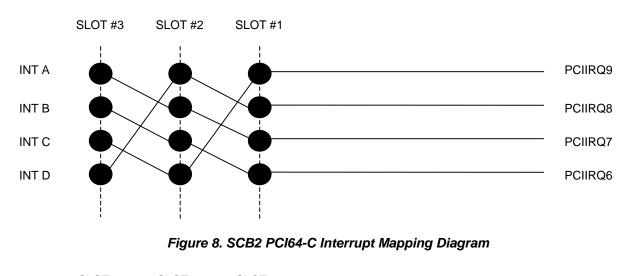

| Figure 8. SCB2 PCI64-C Interrupt Mapping Diagram   |     |

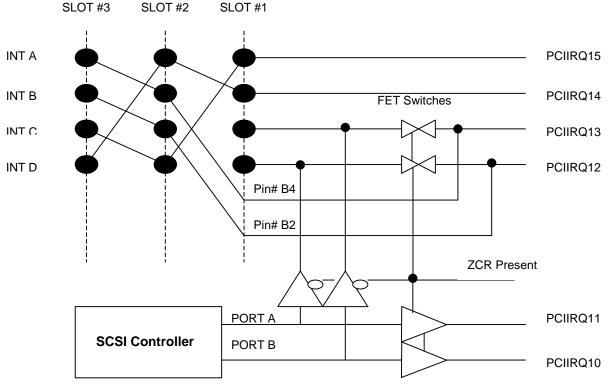

| Figure 9. SCB2 PCI64-B Interrupt Mapping Diagram   |     |

| Figure 10. SCB2 Baseboard Management Block Diagram | 32  |

| Figure 11. IPMI-over-LAN                           | 59  |

| Figure 12. SCB2 Configuration Jumpers (J1E1)       | 135 |

| Figure 13. Output Voltage Timing                   | 139 |

| Figure 14. Turn on / off Timing                    | 141 |

| Figure 15. SCB2 Server Board Mechanical Drawing    | 146 |

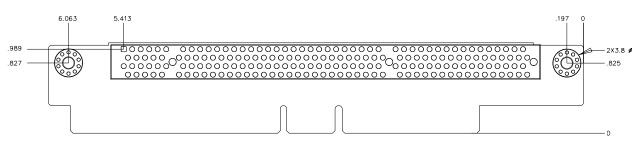

| Figure 16. 1-Slot PCI Riser Mechanical Drawing     | 148 |

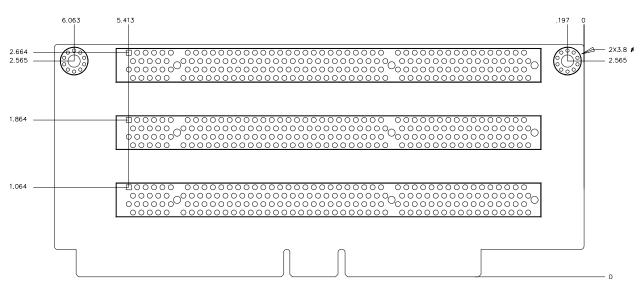

| Figure 17. 3-Slot PCI Riser Mechanical Drawing     | 148 |

## **List of Tables**

| Table 32. | PCI Configuration, Embedded PCI Devices                         | 91 |

|-----------|-----------------------------------------------------------------|----|

|           | Peripheral Configuration Sub-menu Selections                    |    |

| Table 34. | Memory Configuration Menu Selections                            | 92 |

| Table 35. | Advanced Chipset Control Sub-menu Selections                    | 93 |

| Table 36. | Security Menu Selections                                        | 93 |

| Table 37. | Server Menu Selections                                          | 94 |

| Table 38. | System Management Sub-menu Selections                           | 94 |

| Table 39. | Console Redirection Sub-menu Selections                         | 95 |

| Table 40. | Event Log Configuration Sub-menu Selections                     | 95 |

| Table 41. | Fault Resilient Booting                                         | 95 |

| Table 42. | Boot Menu Selections                                            | 96 |

| Table 43. | Boot Device Priority Selections                                 | 96 |

| Table 44. | Hard Drive Selections                                           | 97 |

| Table 45. | Removable Devices Selections                                    | 97 |

| Table 46. | ATAPI* CDROM Drives                                             | 97 |

| Table 47. | Exit Menu Selections                                            | 97 |

| Table 48: | Security Features Operating Model                               | 98 |

| Table 49. | POST Code Table – Port 80h Codes 1                              | 11 |

| Table 50. | Standard POST Error Messages and Codes 1                        | 15 |

| Table 51. | Extended POST Error Messages and Codes 1                        | 16 |

| Table 52. | BMC Generated POST Beep Codes 1                                 | 17 |

| Table 53. | BIOS Generated POST Error Beep Codes 1                          | 17 |

| Table 54. | POST Memory Error 3-Beep Codes 1                                | 17 |

| Table 55. | BIOS Recovery Beep Codes 1                                      | 18 |

| Table 56. | Power Connector Pin-out (J2K1) 1                                | 19 |

| Table 57. | Power Supply Signal Connector (J1K1) 1                          | 19 |

| Table 58. | P64-B 5V 64-bit/66 MHz Full Length PCI Riser Slot Pin-out 1     | 20 |

| Table 59. | P64-C 3.3V 64-bit/ (66/33) MHz Low-Profile Riser Slot Pin-out 1 | 21 |

| Table 60. | ICMB Header Pin-out (J9B1) 1                                    | 23 |

| Table 61. | IPMB Header Pin-out (J9D1) 1                                    | 23 |

| Table 62. | IPMI Header Pin-out (J1H1) 1                                    | 23 |

| Table 63. | High-Density Front Panel 34-Pin Header Pin Out (J1J2) 1         | 24 |

| Table 64. | 34-pin Front Panel Connector signal descriptions1               | 24 |

| Table 65. | SSI Compliant 24-pin Front Panel Connector Pinout (J1G1) 1      | 25 |

| Table 66. High-Density 100-Pin FLOPPY/FP/IDE Connector Pin Out (J2H1)         | 126 |

|-------------------------------------------------------------------------------|-----|

| Table 67. VGA Connector Pin-out (J9A1)                                        | 127 |

| Table 68. 68-pin VHDCI SCSI and Wide Connectors Pin Out (J1C1, J8A1)          | 128 |

| Table 69. Stacked Dual RJ-45 Connector Pin Out (J7A1)                         | 129 |

| Table 70. ATA-100, 40-pin Connectors Pin Out (J2F1, J2G1)                     | 129 |

| Table 71: ATA-33 Low-Density, 40-pin Connector Pin Out (J1J1)                 | 130 |

| Table 72. USB Connectors Pin Out (J5A1, J10A2)                                | 131 |

| Table 73. Optional USB Connection Header Pin-out (J10G1)                      | 131 |

| Table 74. Legacy 34-pin Floppy Connector Pin Out (J4G1)                       | 132 |

| Table 75. External Low-Profile RJ-45 Serial 2 Port Pin-out (J6A1)             | 133 |

| Table 76. 9-pin Header Serial 1 Port Pin Out (J9B2)                           | 133 |

| Table 77. Keyboard & Mouse PS/2 Connector Pin Out (J6A3)                      | 133 |

| Table 78. Three-Pin Fan Headers Pin- Out (J4K1, J4K2, J6K1, J6K2, J9K1, J9K2) | 134 |

| Table 79. Seven-Pin Fan Header Pin Out (J3K1)                                 | 134 |

| Table 80. Configuration Jumper Options                                        | 136 |

| Table 81. Absolute Maximum Ratings                                            | 137 |

| Table 82. SCB2 Power Budget                                                   | 137 |

| Table 83. SCB2 Static Power Supply Voltage Specification                      | 138 |

| Table 84. SCB2 Dynamic Power Supply Voltage Specification                     | 138 |

| Table 85. Voltage Timing Parameters                                           | 139 |

| Table 86. Turn On / Off Timing                                                | 140 |

| Table 87. Transient Load Requirements                                         | 142 |

| Table 88. SCB2 MTBF                                                           | 145 |

| Table 89. Server Board Connector Specifications                               | 147 |

## 1. Introduction

The SCB2 Technical Product Specification (TPS) provides a high level technical description for the Intel<sup>®</sup> SCB2 Server Board. It details the architecture and feature set for all functional subsystems that make up the server board.

This document is sub-divided into the following main categories:

Chapter 2: Hardware Overview

Chapter 3: Hardware Architecture

Chapter 4: Platform Management Architecture

Chapter 5: System BIOS

Chapter 6: Error Handling and Reporting

Chapter 7: Connectors and Jumper Blocks

Chapter 8: General Specifications

The contents of this document are derived from several of the SCB2's External Product Specifications (EPS). For a more detailed, lower level description of a particular functional subsystem, the EPS for the sub-system should be ordered from your Intel field representative. The EPS documents available for the SCB2 server board include the following:

- SCB2 BIOS EPS

- SCB2 Baseboard Management Controller EPS

- Sahallee Core BMC EPS for IPMI v1.5

- SCB2 Server Management EAS

- Platform Instrumentation EPS

- Direct Platform Control EPS

- FRUSDR Loader EPS

- LAN Alert Viewer EPS

The SCB2 server board supports the Intel® Server Control Version 3.5 server management software. Several additional EPS documents are available to provide technical detail on the feature set of the server management software. These include:

- ISC Console EPS

- ISC Install EPS

- Service Partition EPS

- Client System Setup Uility EPS

- ISC Customization Guide

## 2. SCB2 Server Board Overview

The SCB2 server board is a monolithic printed circuit board with features that were designed to support the high-density 1U and 2U server market.

## 2.1 SCB2 Feature Set

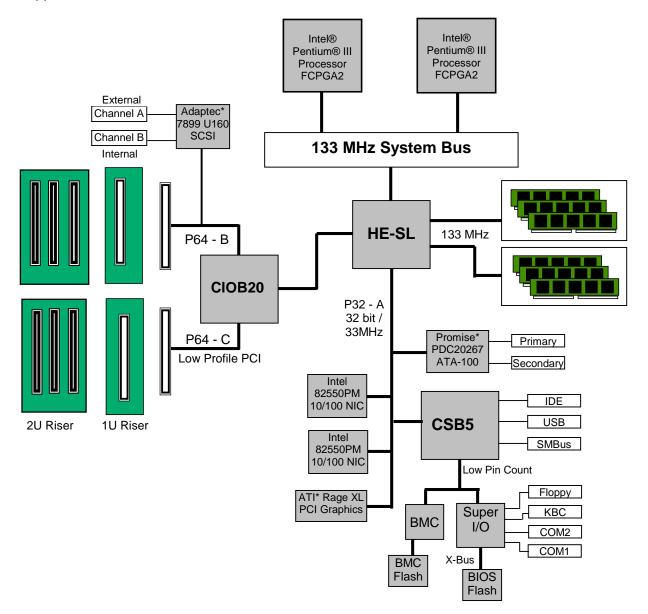

There are two different SCB2 server boards available, each offering a different onboard hard drive controller. One will provide an embedded Ultra-160\* SCSI interface and the other will provide an embedded ATA-100\* "Valu-Raid" interface. Both boards support the following feature set:

- Dual Intel<sup>®</sup> Pentium III<sup>®</sup> processors with 256 KB<sup>1</sup> or 512 KB L2 cache

- 133 MHz Front Side Bus

- ServerWorks ServerSet\* III HE-SL chipset

- HE-SL North Bridge

- CIOB20 I/O Bridge

- CSB5 South Bridge

- Support for up to six PC-133 compliant registered ECC SDRAM DIMMs providing up to 6 GB of memory

- Three separate and independent PCI buses:

- Segment A: 32-bit, 33 MHz, 5 V (P32-A) with four embedded devices:

- 1. 2D/3D graphics controller: ATI Rage\* XL Video Controller with 8 MB of SDRAM

- 2. Two Intel10/100 82550PM Fast Ethernet Controllers

- 3. ATA-100 controller: Promise Technology\* PDC20267 (ATA-100 version only)

- Segment B: 64-bit, 66 MHz, 3.3 V, (P64-B) supporting the following configuration:

- 4. One PCI I/O riser slot capable of supporting full length PCI add-in cards

- 5. Dual-channel Adaptec\* AIC-7899W wide Ultra-160 SCSI Controller providing one internal and one high density external channel support: (SCSI version only)

- 6. Zero Channel RAID (ZCR) support. (SCSI version only)

- Segment C: 64-bit, 66/33 MHz, 3.3 V (P64-C) supporting the following device:

- 7. One PCI I/O riser slot capable of supporting low-profile PCI add-in cards

- LPC (Low Pin Count) bus segment with two embedded devices:

- Platform Management Controller (PMC) providing monitoring, alerting, and logging of critical system information obtained from embedded sensors on the server board

- Super I/O controller chip providing all PC-compatible I/O (floppy, serial, keyboard, mouse)

- X-Bus segment with one embedded device:

<sup>&</sup>lt;sup>1</sup> The SCB2 server board supports Intel Pentium III processors with 256 KB or 512 KB L2 cache that use the socket370 FCPGA2 processor package. Intel Pentium III processors with 256 KB L2 cache, that use the FCPGA processor package, are not supported on the SCB2.

- Flash ROM device for system BIOS: Intel 32 megabit 28F320C3 Flash ROM

- Two external Universal Serial Bus (USB) ports with an additional internal header providing two optional USB ports for front panel support. (USB 1.1 Compatible)

- One external low-profile RJ45 serial 2 port, with an optional serial 2 interface for front panel support. An internal header is also available providing an optional serial 1 (COM1) port.

- One IDE connector, supporting one or two ATA-33 compatible devices

- Support for up to six system fans

- Fault/Status LEDs throughout the server board

- Multiple server management headers providing on-board interconnects to server management features

- SSI-compliant connectors for SSI interface support: front panel, floppy, and ATA-33

The figure below shows the functional blocks of the server board and the plug-in modules that it supports.

Figure 1. SCB2 Server Board Block Diagram

## 3. Functional Architecture

This chapter provides a high-level description of the functionality distributed between the architectural blocks of the SCB2 server board.

## 3.1 **Processor and Memory Subsystem**

The ServerSet III HE-SL chipset provides a 36-bit address, 72-bit data (64-bit data + 8-bit ECC) processor host bus interface, operating at 133 MHz in the AGTL signaling environment. The HE-SL component of the chipset provides an integrated memory controller, the interface to a 32-bit, 33-MHz, Rev 2.2-compliant PCI bus, and two Inter-Module Bus (IMB) interfaces.

The IMB provides the interface to two 64-bit, 66-MHz, Rev 2.2-compliant PCI buses via the CIOB20. The SCB2 server board directly supports up to 6 GB of ECC memory, using six PC/133-compliant registered SDRAM DIMMs. The ECC implementation in the HE-SL can detect and correct single-bit errors, and it can detect multiple-bit errors.

## 3.1.1 Processor Support

The SCB2 server board supports one or two Intel Pentium III processors with 256 KB<sup>2</sup> or 512 KB L2 cache. The server board will support all versions of the Pentium III DP processor that use the Socket370 FCPGA2 package. When two processors are installed, all processors must be of identical revision, core voltage, and bus/core speed. When only one processor is installed, the other socket must have an AGTL terminator card installed. The support circuitry on the server board consists of the following:

- Dual Socket370 FCPGA2 CPU sockets supporting 133 MHz FSB (if using one processor, an AGTL terminator card goes in the empty socket).

- Processor host bus AGTL support circuitry, including termination power supply.

| Processor<br>Family | Package<br>Type | Processor<br>Code Name     | Frequency        | Cache<br>Size | Single/Dual<br>Processor Capable | SCB2<br>Support |

|---------------------|-----------------|----------------------------|------------------|---------------|----------------------------------|-----------------|

| Intel Pentium III   | FCPGA           | Coppermine<br>(A – D step) | 866 MHz – 1GHz   | 256KB         | Dual                             | No              |

| Intel Pentium III   | FCPGA2          | Coppermine-T               | 1 GHz and faster | 256KB         | Dual                             | Yes             |

| Intel Pentium III   | FCPGA2          | Tualatin                   | All              | 256KB         | Single                           | Yes             |

| Intel Pentium III   | FCPGA2          | Tualatin                   | All              | 512KB         | Dual                             | Yes             |

Table 1. SCB2 Processor Support Matrix

**Notes:** All processor sockets must be populated with either a processor or a termination module. The BMC will not allow DC power to be applied to the system unless both processor sockets contain a properly seated processor or termination module.

Processors must be populated in sequential order. That is, processor socket #1 must be populated before processor socket #2.

<sup>&</sup>lt;sup>2</sup> The SCB2 server board supports Intel Pentium III processors with 256 KB or 512 KB L2 cache that use the socket370 FCPGA2 processor package. Intel Pentium III processors with 256 KB L2 cache, that use the FCPGA processor package, are not supported on the SCB2.

In addition to the circuitry described above, the processor subsystem contains the following:

- Reset configuration logic.

- Processor module presence detection logic.

- APIC bus.

- Server management registers and sensors.

## 3.1.1.1 Processor VRM

The SCB2 baseboard has a single VRM (voltage regulator module) to support two processors. It is compliant with the VRM 8.5 specification and provides a maximum of 60 AMPs, which is capable of supporting current supported processors as well as those supported in the future.

The board hardware and BMC must read the processor VID (voltage identification) bits for each processor before turning on the VRM. If the VIDs of the two processors are not identical, then the BMC will not turn on the VRM and a beep code is generated.

## 3.1.1.2 Reset Configuration Logic

The BIOS determines the processor stepping, cache size, etc. through the CPUID instruction. The requirements are as follows:

- All processors in the system must operate at the same frequency and have the same cache sizes. No mixing of product families is supported.

- Processors run at a fixed speed and cannot be programmed to operate at a lower or higher speed.

**Note:** When the CMOS clear function is enabled, the BIOS defaults the processor frequency to a safe mode at 533 MHz when <u>pre-production</u> unlocked processors are used.

On the SCB2 platform, the BIOS is responsible for configuring the processor speeds. The BIOS uses CMOS settings to determine which speed to program into the speed setting device ( $I^2C^*$ -based EEPROM Mux).

The processor information is read at every system power-on. The EEMUX is set to correspond to the speed of the slowest processor installed.

**Note:** No manual processor speed setting options exist either in the form of a BIOS Setup option or jumpers when using production level processors.

## 3.1.1.3 Processor Module Presence Detection

Logic is provided on the baseboard to detect the presence and identity of installed processors or termination card. The BMC checks the logic and will not turn on the system DC power until the processor bus is terminated properly.

## 3.1.1.4 APIC Bus

Interrupt notification and generation for the processors are done using an independent path between local APICs in each processor and the I/O APIC in the CSB5 located on the baseboard. This independent bus consists of two data signals and one clock line.

## 3.1.1.5 Server Management Registers and Sensors

The baseboard management controller manages registers and sensors associated with the processor / memory subsystem.

## 3.1.2 Memory Subsystem

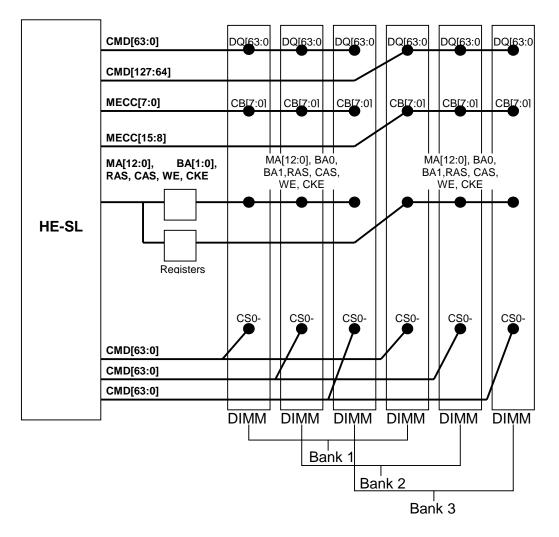

The SCB2 server board provides six DIMM slots and supports a maximum memory capacity of 6 GB. The DIMM organization is x72 which includes eight ECC check bits. ECC from the DIMMs are passed through to the processor's front side bus. The SDRAM interface runs at the same frequency as the processor bus. The memory controller supports memory scrubbing, single-bit error correction and multiple-bit error detection. Memory can be implemented with either single-sided (one row) or double-sided (two row) DIMMs.

**Note**: Due to the use of vertical or 90 degree DIMM slots, only low profile DIMMs can be supported in a 1U server chassis.

Data transfers between the HE-SL and DIMMs in a two-way interleaved fashion. This requires that two DIMMs be populated per bank in order for the system to operate. At least one bank has to be fully populated in order for the system to boot. If additional banks have less than two DIMMs, the memory for that bank(s) will not be available to the system. The smallest supported DIMM size is 64 MB. Therefore, the minimum main memory configuration is 2 x 64 MB or 128 MB. The largest size DIMM supported is a 1-GB stacked registered PC-133 ECC DIMM based on 256-Mbit technology.

The figure below provides a block diagram of the memory sub-system implemented on the SCB2 server board.

#### Figure 2. Memory Sub-system Block Diagram

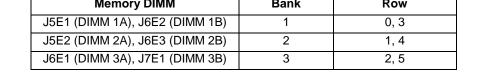

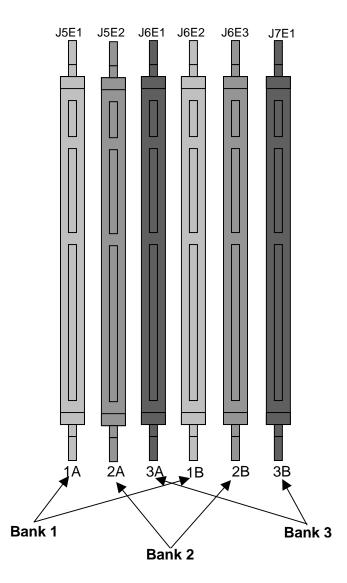

There are three banks of DIMMs; labeled as 1, 2, and 3. Bank 1 contains DIMM locations 1A and 1B, bank 2 contains 2A and 2B, and bank 3 contains 3A and 3B. DIMM socket identifiers are marked with a silk screen next to each DIMM socket on the baseboard. Note that the sockets associated with any given bank are NOT located next to each other.

The baseboard's signal integrity and cooling are optimized when memory banks are populated in order. Therefore, when installing memory, DIMMs should be installed starting with bank 1 and ending with bank 3.

| Memory DIMM                    | Bank | Row  |

|--------------------------------|------|------|

| J5E1 (DIMM 1A), J6E2 (DIMM 1B) | 1    | 0, 3 |

| J5E2 (DIMM 2A), J6E3 (DIMM 2B) | 2    | 1, 4 |

| J6E1 (DIMM 3A), J7E1 (DIMM 3B) | 3    | 2, 5 |

Table 2. Memory Bank Labels

Figure 3. Memory Bank Label Definition

DIMM and memory configurations must adhere to the following:

- PC133 SDRAM registered ECC DIMM modules

- DIMM organization: x72 ECC

- Pin count: 168

- DIMM capacity: 64 MB, 128 MB, 256 MB, 512 MB, 1 GB DIMMs

- Serial PD: JEDEC Rev 2.0

- Voltage Options: 3.3 V (VDD/VDDQ)

- Interface: LVTTL

- Two DIMMs must be populated in a bank for a x144 wide memory data path.

- Any or all memory banks may be populated

Only DIMMs tested and qualified by Intel or a designated memory test vendor will be supported on the SCB2 server board. A list of qualified memory can be downloaded from the following web site: <u>http://support.intel.com/support/motherboards/server/scb2/scb2\_mem.htm</u>.

Note that all DIMMs are supported by design, but only fully qualified DIMMs will be supported.

## 3.1.2.1 I<sup>2</sup>C\* Bus

An I<sup>2</sup>C bus is between the Baseboard Management Controller (BMC) and the six DIMM slots. This bus is used by the system BIOS to retrieve DIMM information needed to program the HE-SL memory registers which are required to boot the system.

## 3.2 ServerWorks ServerSet\* III HE-SL Chipset

The SCB2 server board is designed around the ServerWorks ServerSet III HE-SL chipset. The chipset provides an integrated I/O bridge and memory controller and a flexible I/O subsystem core (PCI), targeted for multiprocessor systems and standard high-volume servers. The ServerWorks ServerSet III chipset consists of three components:

- HE-SL: Champion North Bridge. The HE-SL North Bridge accepts access requests from the host (processor) bus and directs those accesses to memory or to one of the PCI buses. The HE-SL monitors the host bus, examining addresses for each request. Accesses may be directed to a memory request queue for subsequent forwarding to the memory subsystem, or to an outbound request queue for subsequent forwarding to one of the PCI buses. The HE-SL also accepts inbound requests from the CIOB20 and the legacy PCI bus. The HE-SL is responsible for generating the appropriate controls to control data transfer to and from memory.

- CIOB20: Champion I/O Bridge. The CIOB20 provides the interface for two 64-bit, 66-MHz Rev. 2.2-compliant PCI buses. The CIOB is both master and target on both PCI buses.

- **CSB5: South Bridge.** The CSB5 controller has several components. It provides the interface for a 32-bit, 33-MHz Rev. 2.2-compliant PCI bus. The CSB5 can be both a master and a target on that PCI bus. The CSB5 also includes a USB controller and an IDE controller. The CSB5 is also responsible for much of the power management

functions, with ACPI control registers built in. The CSB5 also provides a number of GPIO pins and has the LPC bus to support a low-speed legacy I/O.

The CNB20HE-SL, CIOB, and CSB5 chips provide the pathway between processor and I/O systems. The CNB20HE-SL is responsible for accepting access requests from the host (processor) bus, and directing all I/O accesses to one of the PCI buses or legacy I/O locations. If the cycle is directed to one of the 64-bit PCI segments, the HE-SL communicates with the CIOB through a private interface called the IMB. If the cycle is directed to the 32-bit PCI segment or to the CSB5, the cycle is output on the HE-SL's 32-bit PCI bus. The CIOB translates the IMB bus operation to a 64-bit PCI Rev. 2.1-compliant signaling environment operating at either 66 MHz or 33 MHz.

The IMB bus consists of two data paths, one upstream (to the CNB20HE-SL from the CIOB) and one downstream (from the CNB20HE-SL to the CIOB). The interface is 16 bits wide and operates at 133 MHz with double pumped data, providing over 1 GB per second of bandwidth or 533 MB per second in each direction concurrently.

All I/O for the SCB2, including PCI and PC-compatible, is directed through the CNB20HE-SL, and then through either the CIOB or the HE-SL provided PCI buses.

- The HE provides a 32-bit, 33-MHz PCI bus hereafter called P32-A.

- The CIOB provides two independent 64-bit, 66-MHz PCI buses hereafter called P64-B, and P64-C.

This independent bus structure allows all three PCI buses to operate concurrently and provides 1.2 GB per second of I/O bandwidth.

## 3.2.1 CNB20HE-SL Champion North Bridge

The Champion North Bridge Rev 2.0 High End Super Lite (CNB20HE-SL) is the third generation product in ServerWorks's Champion North Bridge Technology. The CNB20HE-SL is a 644-pin ball-grid array (BGA) device and uses the proven components of previous generations like the Pentium<sup>®</sup> Pro Bus interface unit, the PCI interface unit and the SDRAM memory interface unit. In addition, the CNB20HE-SL incorporates an Intra Module Bus (IMB) Interface. The IMB interface enables the CNB20HE-SL to directly interface with the CIOB20. The CNB20HE-SL also increases the main memory interface bandwidth and maximum memory configuration with a 144-bit wide memory interface.

The CNB20HE-SL integrates three main functions:

- An integrated, high performance main memory subsystem

- An IMB bus interface that provides a high-performance data flow path between the processor bus and the I/O subsystem

- A PCI interface which provides an interface to the compatibility PCI bus segment and the CSB5 (South Bridge).

Other features provided by the CNB20HE include the following:

- Full support of ECC on the processor bus.

- Full support of ECC on the memory interface.

- Eight deep in-order queue.

- Full support of registered PC-133 ECC SDRAM DIMMs.

- Support for 6 GB of 2-way interleaved SDRAM

- Memory scrubbing

## 3.2.1.1 Memory Architecture Overview

The CNB20HE-SL supports a 2-way interleaved memory sub-system that can support a maximum of 6 Gbytes (using 1GB DIMMs). The memory interface runs at 133 MHz, matching that of the processor front side bus. The memory interface supports a 144-bit wide memory array. It uses fifteen address lines (BA[1:0] and MA[12:0]) and supports 1Mx72, 2Mx72, 4Mx72, 8Mx72, 16Mx72, 32Mx72, 64Mx72, and stacked 128Mx72 DIMMs. The SDRAM DIMM interface supports memory scrubbing, single-bit error correction, and multiple-bit error detection.

## 3.2.1.2 PCI Bus P32-A I/O Subsystem

The CNB20HE-SL provides a legacy 32-bit PCI subsystem and acts as the central resource on this PCI interface.

P32-A supports the following embedded devices and connectors:

- CSB5 South Bridge.

- Two Intel 82550PM 10/100 Fast Ethernet PCI network interface controllers

- An ATI Rage\* XL video controller with 3D/2D graphics accelerator

- Promise Technology\* PDC20267 Dual channel ATA-100 Controller. (ATA-100 board only)

## 3.2.2 CIOB

The Champion I/O Bridge (CIOB) is a 352-pin ball-grid array device and provides an integrated I/O bridge that provides a high-performance data flow path between the IMB and the 64-bit I/O subsystem. This subsystem supports peer 64-bit PCI segments. Having multiple PCI interfaces, the CIOB is able to provide large and efficient I/O configurations. The CIOB functions as the bridge between the IMB and the multiple 64-bit PCI I/O segments.

The IMB interface is capable of supporting 512 MB/s of data bandwidth in both the upstream and downstream direction simultaneously.

The internal PCI arbiter implements the Least Recently used algorithm to grant access to requesting masters.

## 3.2.2.1 PCI Bus P64-B I/O Subsystem

P64-B supports the following embedded devices and connectors:

One 184-pin, 5-volt keyed, 64-bit PCI expansion slot connector. The expansion slot can be used for either a 1-slot or a 3-slot PCI riser card. The riser cards both support 184pin, 3.3V keyed, 64-bit PCI expansion slots. The PCI slots on the P64-B PCI bus support both full-length PCI cards and low-profile PCI cards with the appropriate face plate.

- One Adaptec 7899 dual channel Ultra-160 SCSI controller. (\*\*SCB2-SCSI Only)

- Support for ZCR or M-ROMB that allows the on-board SCSI controller to be "hidden" from the system and used by the RAID processor on the add-in card. (\*\*SCB2-SCSI board only)

## 3.2.2.2 PCI Bus P64-C I/O Subsystem

P64-C supports one 184-pin, 5-Volt keyed, 64-bit PCI expansion slot connector. The expansion slot can be used for either a 1-slot or a 3-slot PCI riser card. Both riser cards support 184-pin, 3.3V keyed, 64-bit PCI expansion slots. The PCI slots on the P64-C PCI bus support only low-profile PCI cards due to component interferences on the server board.

## 3.2.3 CSB5

The CSB5 is a multi-function PCI device, housed in a 272-pin BGA device, providing a PCI-to-LPC bridge, a PCI IDE interface, a PCI USB controller, and a power management controller. Each function within the CSB5 has its own set of configuration registers. Once configured, each appears to the system as a distinct hardware controller sharing the same PCI bus interface.

On the SCB2 server board, the primary role of the CSB5 is to provide the gateway to all PCcompatible I/O devices and features. The SCB2 uses the following CSB5 features:

- 32-bit/33MHz PCI bus interface

- LPC bus interface

- IDE interface, with Ultra DMA 33 capability

- USB interface

- PC-compatible timer/counter and DMA controllers

- APIC and 8259 interrupt controller

- Power management

- General purpose I/O (GPIO)

The following are the descriptions of how each supported feature is used on SCB2.

## 3.2.3.1 PCI Bus Interface

The CSB5 provides a 32-bit 33 MHz PCI master/slave interface, in accordance with the *PCI Local Bus Specification, Revision 2.2.*

## 3.2.3.2 PCI Bus Master IDE Interface

The CSB5 acts as a PCI-based Ultra DMA/33 IDE controller that supports programmed I/O transfers and bus master IDE transfers. The SCB2 provides two separate but common interfaces to the IDE controller which can support up to two drives. The first interface is a single SSI compliant 40-pin (2x20) IDE connector located on the edge of the baseboard next to the main power connector. The second interface is provided through the high-density 100-pin floppy / IDE / front panel connector that is used with Intel's SR1200 and SR2200 server chassis.

**Note:** Using both the SSI IDE connector and the high-density "Floppy/IDE/Front Panel" connector in a common configuration is not supported. Using both connectors in a common configuration may result in unreliable data transfers and can cause data corruption. The SCB2 IDE interface supports Ultra DMA/33 Synchronous DMA Mode transfers.

## 3.2.3.3 USB Interface

The CSB5 contains a USB controller and four USB hubs compliant with the USB 1.1 specification. The USB controller moves data between main memory and the four USB connectors. All four ports function identically and with the same bandwidth.

The SCB2 provides two external USB ports located on the back edge of the server board. The first external connector is located within the standard ATX\* I/O panel area while the second is located directly behind the P64-B full-length PCI card slot. The USB specification defines the external connectors.

The third and fourth USB ports are optional and can be accessed by cabling the internal 9-pin connector located on the baseboard (J10G1) to external USB ports located either in front or the back of a given chassis.

## 3.2.3.4 Compatibility Interrupt Control

The CSB5 provides the functionality of two 82C59 PIC devices for ISA-compatible interrupt handling.

## 3.2.3.5 APIC

The CSB5 integrates a 32-entry I/O APIC that is used to distribute 32 PCI interrupts. It also includes an additional 16-entry I/O APIC for distribution of legacy ISA interrupts.

## 3.2.3.6 General Purpose Input and Output Pins

The CSB5 provides a number of general purpose input and output pins. Many of these pins have alternate functions and are not available.

## 3.2.3.7 Power Management

One of the embedded functions of the CSB5 is a power management controller. The SCB2 server board uses this to implement ACPI-compliant power management features. The SCB2 supports sleep states S0, S1, S4, and S5.

## 3.3 Super I/O

The National Semiconductor\* PC87417 Super I/O device contains the system Real Time Clock (RTC), all of the necessary circuitry to control two serial ports, one parallel port, floppy disk, and PS/2-compatible keyboard and mouse. The SCB2 server board supports the following features:

- GPIOs

- Two Serial Ports

- Floppy Disk

- Keyboard and mouse through a single PS/2 connector

- System Real Time Clock

- Wake Up Control

Note: The SCB2 does not support a parallel port.

## 3.3.1 GPIOs

The National Semiconductor PC87417 Super I/O provides a number of GPIO pins. The following table identifies which functions are utilized on the SCB2:

| Description                                    |

|------------------------------------------------|

| Power Supply Off button                        |

| Diagnostic LED strobe                          |

| Current Sleep S5 State                         |

| SIO Requested Power Off                        |

| Sleep Button from SIO                          |

| Diagnostics LED Data                           |

| Board ID 0– Used to identify revision of board |

| Board ID 1– Used to identify revision of board |

| Board ID 2– Used to identify revision of board |

| Front Panel Power Idicator                     |

| PME# from P64-B                                |

| PME from NICs                                  |

#### Table 3. Super I/O GPIO Usage Table

## 3.3.2 Real-time Clock

The Super I/O contains an RTC with an external battery backup. The device also contains 242 bytes of general purpose, battery-backed CMOS RAM.

## 3.3.3 Serial Ports

The SCB2 server board provides two serial ports, Serial 1 and Serial 2. Serial 1 is optional with its signals accessed through an internal connector on the baseboard. Serial 2 has multiple interfaces and is typically used to access the server management features of the baseboard.

**Note:** In order to comply with Microsoft\* WHQL requirements, all references to serial ports utilizing an RJ-45 type of connector will be denoted as "Serial 2 Port" only. References to the RJ45 serial port as "COM2" will not be used.

## 3.3.3.1 Serial 1 Port

Serial 1 is an optional port, accessed through a 9-pin internal connector (J9B2). A standard DH-10 to DB9 cable can be used to direct Serial 1 signals out the back of a given chassis. The Serial 1 interface follows the standard RS232 pinout. The baseboard has a "COM1" silkscreen label next to the connector as well as a location designator of J9B2. The Serial 1 connector is located next to the P64-C low-profile PCI riser slot.

| Pin | Signal Name | COM1 Pin-out |

|-----|-------------|--------------|

| 1   | DCD         |              |

| 2   | DSR         |              |

| 3   | RX          | 3 0 0 4      |

| 4   | RTS         |              |

| 5   | ТХ          | 5 0 0 6      |

| 6   | CTS         | 7 0 0 8      |

| 7   | DTR         | 9 0 1        |

| 8   | RI          |              |

| 9   | GND         |              |

Table 4. COM1 Pin-out

## 3.3.3.2 Serial 2 Port(s)

The SCB2 provides three common interfaces for accessing the Serial 2 port signals: an external low profile 8-pin RJ45 connector is located on the back edge of the baseboard, with the second and third interfaces accessed through two high-density front panel connectors on the baseboard. References to the different Serial 2 interfaces will be denoted as "Back" and "Front".

The front Serial 2 port is for direct connect or PC-to-PC server management access only with no modem support, since it lacks a Ring Indicate (RI) signal.

## 3.3.3.2.1 Back RJ45 Serial 2 Port

The back RJ45 Serial 2 port can support any standard serial device. An RJ45 type connector was chosen in order to support serial port concentrators which are widely used in the high-density server market and which typically use RJ45 type connectors.

To give support for either of two serial configuration standards used by serial port concentrators, the J6A2 jumper block, located directly behind the rear RJ45 serial port, must be jumpered appropriately according to which standard is desired.

**Note:** By default, as configured in the factory, the SCB2 baseboard will have the back RJ45 serial port configured to support a DSR signal which is compatible with the Cisco\* standard.

For serial devices that require a DSR signal (default), the J6A2 jumper block must be configured as follows: the DSR jumper in position 1 and 2, and the DCD jumper in position 1 and 2. Pin 1, on the jumper, is denoted by an arrow directly next to the jumper block.

#### Figure 4. J6A2 Jumper Block for DSR Signal

For serial devices that require a DCD signal, the J6A2 jumper block must be configured as follows: The DCD jumper in position 2 and 3, and the DSR jumper in position 2 and 3. Pin 1, on the jumper, is denoted by an arrow directly next to the jumper block. The following diagram provides the jumper block pinout for this configuration.

For those serial devices that require a DB9 type of serial connector, an 8-pin RJ45-to-DB9 adapter must be used. The following table provides the pinout required for the adapter to provide RS232 support.

| RJ45 | Signal              | Abbr.   | DB9     |

|------|---------------------|---------|---------|

| 1    | Request to Send     | RTS     | 7       |

| 2    | Data Terminal Ready | DTR     | 4       |

| 3    | Transmitted Data    | TD      | 3       |

| 4    | Signal Ground       | SGND    | 5       |

| 5    | Ring Indicator      | RI      | 9       |

| 6    | Received Data       | RD      | 2       |

| 7    | DCD or DSR          | DCD/DSR | 1 or 6* |

| 8    | Clear To Send       | CTS     | 8       |

#### Table 5. Back Serial 2 Port Adapter Pinout

Notes:

- The RJ45-to-DB9 adapter used should match both the signal requirements of the serial device and the external RJ45 serial port. The external RJ45 serial port provides all standard serial port signals, however having only 8 pins, Pin #7 can be manually configured to support either a DCD or DSR signal by setting the J6A2 jumper block appropriately.

- For systems configured with both a front and back RJ45 serial connectors, the adapters used for the back connector cannot be used with the front connector, as the pin-out for both RJ45 ports are different.

Usage Example: When using an external modem to access the server management features of the baseboard, you must first set the J6A2 jumper to support a DCD signal and make or choose the appropriate RJ-45-to-DB9 adapter.

## Figure 6. J6A2 Jumper Block for DCD Signal

If you choose to develop your own RJ-45-to-DB9 adapter, see *Table 5. Back Serial 2 Port Adapter Pinout* for the appropriate pinout configuration.

## Notes:

- Only the back Serial 2 port has modem support

- Intel provides an orderable accessory kit for (Intel order number AXXRJ45DB9) which contains all three RJ45-to-DB9 adapters: rear DSR peripherals, rear DCD modem, and front Emergency Management Port (EMP).

## 3.3.3.2.2 Front RJ45 Serial 2 Port

Some server chassis may support a second RJ45 Serial 2 port on the front of the chassis, which share common signals with the back RJ45 Serial 2 port. The signals for the front Serial 2 port are accessed through either of two high-density front panel connectors on the baseboard. These connectors are found at locations J2H1, labeled FLOPPY/FP/IDE, and J1J2, labeled FRONT PANEL.

The intended usage model for a front panel mounted serial port is to provide a direct connect or PC-to-PC serial communications to access the server management features of the baseboard.

By default, the front Serial 2 port is disabled whenever there is no cable or adapter is installed. When a cable or adapter is installed, the port is enabled and the back Serial 2 port is disabled. This is accomplished by grounding pin 5 of the front 8-pin RJ45 connector.

For a direct connect or PC-to-PC serial communication, either an 8-pin RJ45-to-DB9 adapter or a cable supporting both DB-9 and RJ45 connectors will be necessary. The following table provides a pinout for the front RJ45-to-DB9 adapter or cable.

| Signal Name | RJ45 | DB9 |

|-------------|------|-----|

| No connect  | N/A  | 1   |

| SIN         | 6    | 2   |