# Intel<sup>®</sup> Server Board SE7501HG2

**Technical Product Specification**

**Revision 1.2**

June 2004

**Enterprise Platforms and Services Division**

Intel Enterprise Platforms and Services Division

| Date              | Revision<br>Number | Modifications                                                         |

|-------------------|--------------------|-----------------------------------------------------------------------|

| October 25, 2002  | 0.5 (Draft)        | Initial release.                                                      |

| November 7, 2002  | 0.6 (Draft)        | Fab-2 edits                                                           |

| November 15, 2002 | 0.7                | Additional Fab-2 notations, processor support, signal changes         |

| January 18, 2003  | 1.0                | Final Release                                                         |

| June 9, 2003      | 1.1                | Corrected location of ID LED to near VGA connector (NOT near Speaker) |

| June 3, 2004      | 1.2                | Pre-Design Disclaimer Dropped from Page 3                             |

# **Revision History**

# Disclaimers

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The **Intel® Server Board** SE7501HG2 may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document and the software described in it is furnished under license and may only be used or copied in accordance with the terms of the license. The information in this manual is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2004.

# **Table of Contents**

| 1. | Introdu | ction                                    | 1    |

|----|---------|------------------------------------------|------|

| 1  | .1      | Audience                                 | 1    |

| 2. | SE7501  | HG2 Server Board Overview                | 2    |

| 2  | .1      | SE7501HG2 Feature Set                    | 2    |

| 3. | Functio | nal Architecture                         | 5    |

| 3  | .1      | Processor and Memory Subsystem           | 5    |

|    | 3.1.1   | Processor Support                        | 5    |

|    | 3.1.2   | Memory Subsystem                         | 7    |

| 3  | .2      | Intel® E7501 Chipset                     | . 11 |

|    | 3.2.1   | MCH Memory Architecture Overview         | . 12 |

|    | 3.2.2   | MCH Memory Controller Hub                | . 12 |

|    | 3.2.3   | P64H2 I/O Bridge                         | . 13 |

|    | 3.2.4   | ICH3-S I/O Controller Hub (South Bridge) | . 13 |

| 3  | .3      | Super I/O                                | . 15 |

|    | 3.3.1   | GPIOs                                    | . 16 |

|    | 3.3.2   | Serial Ports                             | . 16 |

|    | 3.3.3   | Parallel Port                            | . 16 |

|    | 3.3.4   | Floppy Disk Controller                   | . 16 |

|    | 3.3.5   | Keyboard and Mouse                       | . 17 |

|    | 3.3.6   | Wake-up Control                          | . 17 |

|    | 3.3.7   | BIOS Flash                               | . 17 |

| 4. | Configu | ration and Initialization                | . 18 |

| 4  | .1      | Memory Space                             | . 18 |

|    | 4.1.1   | DOS Compatibility Region                 | . 19 |

|    | 4.1.2   | Extended Memory                          | .21  |

|    | 4.1.3   | Memory Shadowing                         | . 22 |

|    | 4.1.4   | System Management Mode Handling          | . 23 |

| 4  | .2      | I/O Мар                                  | . 23 |

| 4  | .3      | Accessing Configuration Space            | . 23 |

|    | 4.3.1   | CONFIG_ADDRESS Register                  | . 24 |

| 4  | .4      | Hardware Initialization                  | . 25 |

| 5. | Clock G | eneration and Distribution               | . 26 |

| 6. | PCI I/O     | Subsystem                                     | . 28 |

|----|-------------|-----------------------------------------------|------|

| 6  | 6.1         | PCI Subsystem                                 | . 28 |

|    | 6.1.1       | P32-A: 32-bit, 33-MHz PCI Subsystem           | . 28 |

|    | 6.1.2       | P64-B: 64-bit, 100/66-MHz PCI-X Subsystem     | . 29 |

|    | 6.1.3       | P64-C: 64-bit, 133/100/66-MHz PCI-X Subsystem | . 31 |

| 6  | 6.2         | Ultra 320 SCSI                                | . 31 |

| 6  | 6.3         | Onboard RAID support                          | . 32 |

| 6  | 6.4         | Video Controller                              | . 32 |

|    | 6.4.1       | Video Modes                                   | . 33 |

|    | 6.4.2       | Video Memory Interface                        | . 33 |

|    | 6.4.3       | Host Bus Interface                            | . 34 |

| 6  | 6.5         | Network Interface Controller (NIC)            | . 35 |

|    | 6.5.1       | NIC Connector and Status LEDs                 | . 36 |

| 6  | 6.6         | Interrupt Routing                             | . 36 |

|    | 6.6.1       | Legacy Interrupt Routing                      | . 36 |

| 7. | Server I    | Management                                    | . 39 |

| 7  | <b>'</b> .1 | Intel® Server Management v5.5 (ISM) Overview  | .40  |

| 7  | <b>.</b> .2 | Platform Management Technology                | .41  |

| 7  | 7.3         | Sahalee Baseboard Management Controller       | .42  |

|    | 7.3.1       | Fault Resilient Booting                       | . 49 |

| 7  | <b>'</b> .4 | System Reset Control                          | . 50 |

|    | 7.4.1       | Power-up Reset                                | . 50 |

|    | 7.4.2       | Hard Reset                                    | . 51 |

|    | 7.4.3       | Soft Reset                                    | . 51 |

| 7  | <b>'</b> .5 | Intelligent Platform Management Buses (IPMB)  | . 51 |

| 7  | <b>'</b> .6 | Inter Chassis Management Bus (ICMB)           | . 52 |

| 7  | 7.7         | Error Reporting                               | . 52 |

|    | 7.7.1       | Error Sources and Types                       | . 52 |

|    | 7.7.2       | PCI Bus Errors                                | . 52 |

|    | 7.7.3       | Intel® Xeon™ Processor Bus Errors             | . 52 |

|    | 7.7.4       | Memory Bus Errors                             | . 53 |

|    | 7.7.5       | ID LED                                        | . 53 |

|    | 7.7.6       | System Status LED                             | . 53 |

|    | 7.7.7       | POST Progress Codes                           | . 54 |

|    | 7.7.8       | POST Error Codes and Messages                 | . 57 |

|     | 7.7.9   | POST Error Beep Codes              | . 59 |

|-----|---------|------------------------------------|------|

|     | 7.7.10  | BIOS Recovery Beep Codes           | . 60 |

|     | 7.7.11  | Bootblock Error Beep Codes         | . 61 |

| 7   | .8      | Temperature Sensors                | . 62 |

| 8.  | SE7501  | HG2 ACPI Implementation            | . 63 |

| 8   | .1      | ACPI                               | . 63 |

|     | 8.1.1   | Front Panel Switches               | . 63 |

|     | 8.1.2   | Wake up Sources (ACPI and Legacy)  | . 65 |

| 9.  | SE7501  | HG2 Connectors                     | . 66 |

| ç   | .1      | Main Power Connector               | . 66 |

| ç   | .2      | Memory Module Connector            | . 67 |

| ç   | .3      | Processor Socket                   | . 68 |

| ç   | .4      | System Management Headers          | 71   |

|     | 9.4.1   | ICMB Header                        | 71   |

|     | 9.4.2   | OEM IPMB Header                    | 71   |

|     | 9.4.3   | SCSI IPMB Header                   | 72   |

| g   | .5      | PCI Slot Connector                 | 72   |

| g   | .6      | Front Panel Connectors             | .77  |

|     | 9.6.1   | VGA Connector                      | . 78 |

|     | 9.6.2   | SCSI Connectors                    | . 78 |

|     | 9.6.3   | NIC Connectors                     | . 79 |

|     | 9.6.4   | ATA Connectors                     | . 80 |

|     | 9.6.5   | USB Connector                      | . 81 |

|     | 9.6.6   | Floppy Connector                   | . 82 |

|     | 9.6.7   | Serial Port Connector              | . 82 |

|     | 9.6.8   | Parallel Port                      | . 83 |

|     | 9.6.9   | Keyboard and Mouse Connector       | . 84 |

| ĝ   | .7      | Miscellaneous Headers              | . 84 |

|     | 9.7.1   | Fan Headers                        | . 84 |

| 10. | Configu | iration Jumpers                    | . 85 |

| 1   | 0.1     | System Recovery and Update Jumpers | . 85 |

| 11. | Power I | nformation                         | . 87 |

| 1   | 1.1     | Absolute Maximun Ratings           | . 87 |

| 1   | 1.2     | SE7501HG2 Power Budget             | . 87 |

| 1   | 1.3     | Power Supply Specifications        | . 88 |

| Index       |                                                                              | 107  |

|-------------|------------------------------------------------------------------------------|------|

| Reference I | Documents                                                                    | 106  |

| Appendix A  | A: Intel® Server System SE7501HG2 Platform Sensors                           | 100  |

| Glossary    |                                                                              | . 98 |

| 13. Mechar  | nical Specifications                                                         | . 95 |

| 12.3        | Replacing the Back up Battery                                                | 93   |

| 12.2.4      | BSMI (Taiwan)                                                                | 93   |

| 12.2.3      | Ministry of Economic Development (New Zealand) Declaration of Conformity     | . 93 |

| 12.2.2      | Australian Communications Authority (ACA) (C-Tick Declaration of Conformity) | . 93 |

| 12.2.1      | Europe (CE Declaration of Conformity)                                        | 93   |

| 12.2        | Electromagnetic Compatibility Notices                                        | 93   |

| 12.1.3      | Product Regulatory Compliance Markings                                       | 92   |

| 12.1.2      | Product EMC Compliance                                                       | 92   |

| 12.1.1      | Product Safety Compliance                                                    | 92   |

| 12.1        | Product Regulatory Compliance                                                | 92   |

| 12. Regulat | tory and Integration Information                                             | 92   |

| 11.3.2      | Voltage Recovery Timing Specifications                                       | 90   |

| 11.3.1      | Power Timing                                                                 | 88   |

# **List of Figures**

| Figure 1. Intel <sup>®</sup> Server Board SE7501HG2 Block Diagram         | 4  |

|---------------------------------------------------------------------------|----|

| Figure 2. Memory Sub-system Block Diagram                                 | 8  |

| Figure 3. Memory Bank Label Definition                                    | 10 |

| Figure 4. Intel® Xeon™ Processor Memory Address Space                     | 18 |

| Figure 5. DOS Compatibility Region                                        | 19 |

| Figure 6. Extended Memory Map                                             | 21 |

| Figure 7. CONFIG_ADDRESS Register                                         | 24 |

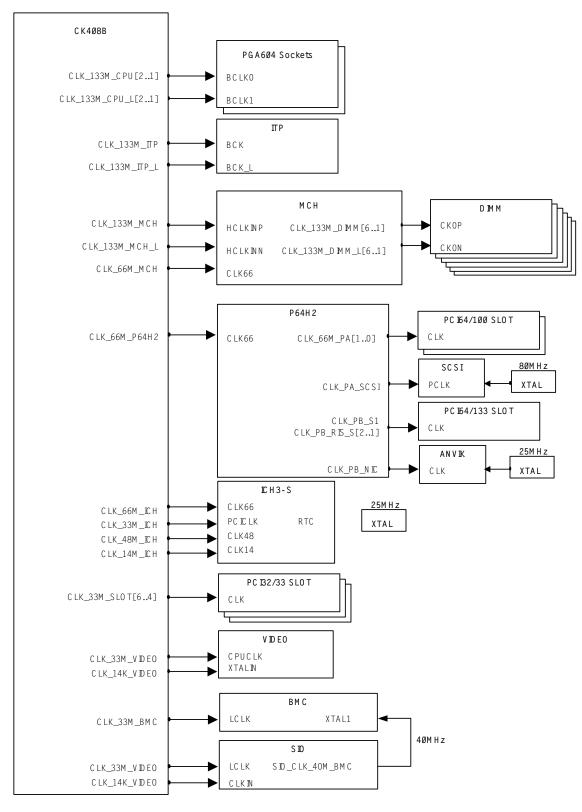

| Figure 8. Intel® Server Board SE7501HG2 Clock Distribution                | 27 |

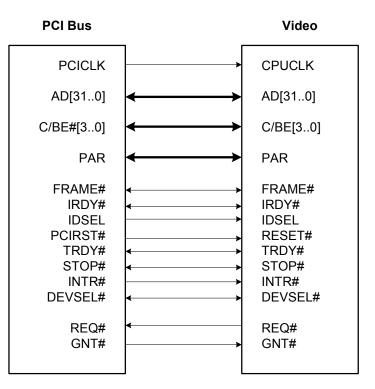

| Figure 9. Video Controller PCI Bus Interface                              | 34 |

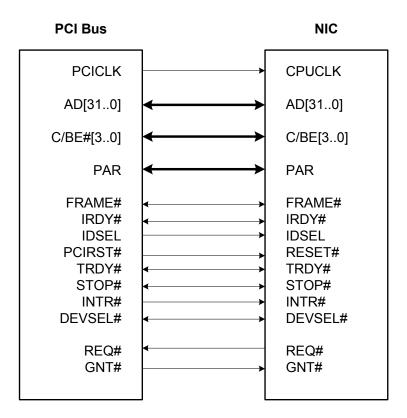

| Figure 10. NIC Controller PCI Bus Interface                               | 35 |

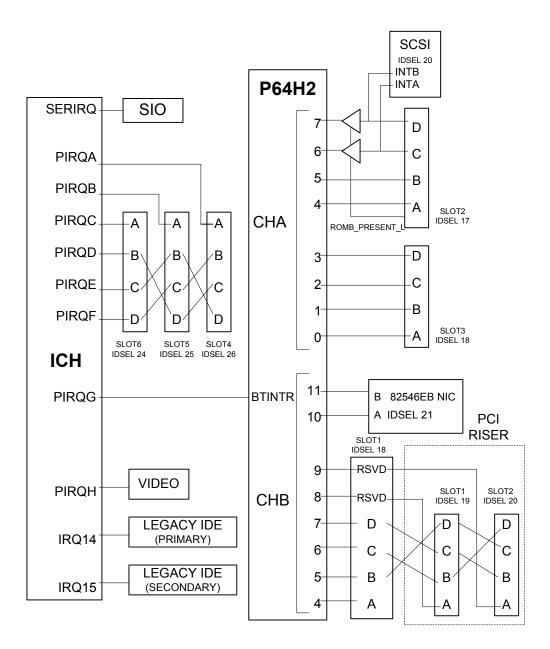

| Figure 11. Intel® Server Board SE7501HG2 Interrupt Routing Diagram        |    |

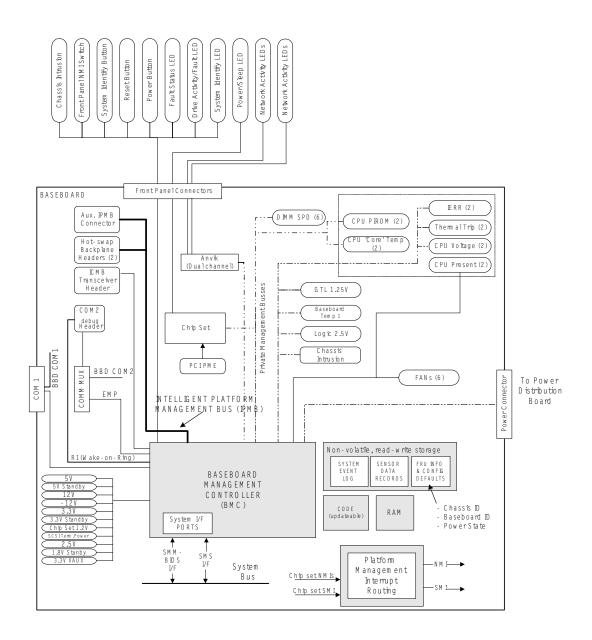

| Figure 12. Intel® Server Board SE7501HG2 Sahalee BMC Block Diagram        |    |

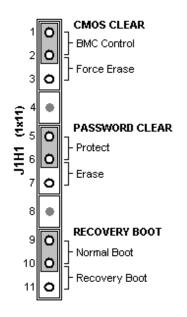

| Figure 13. Intel® Server Board SE7501HG2 Configuration Jumpers (J1H1)     | 85 |

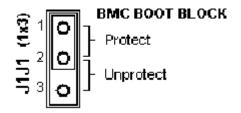

| Figure 14. Intel® Server Board SE7501HG2 BMC Configuration Jumpers (J1J1) |    |

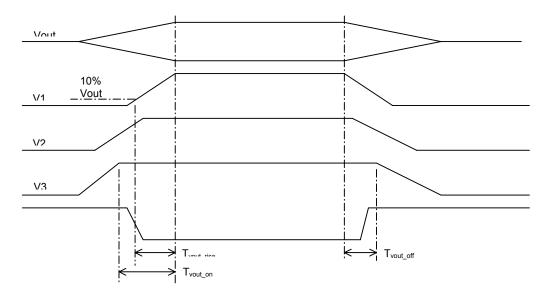

| Figure 15. Output Voltage Timing                                          |    |

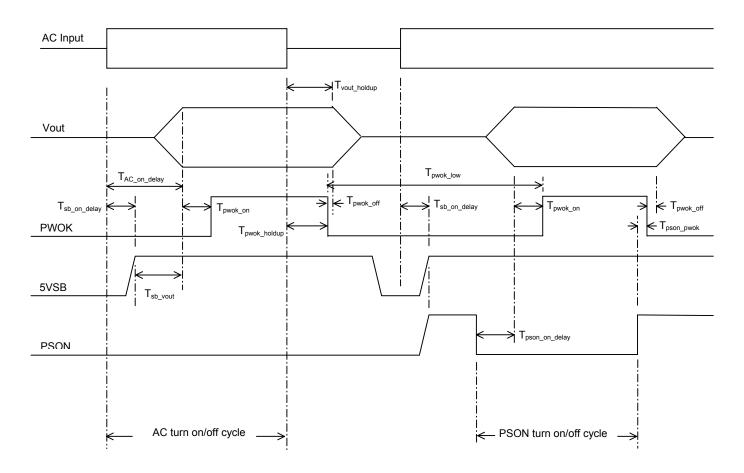

| Figure 16. Turn On/Off Timing                                             | 90 |

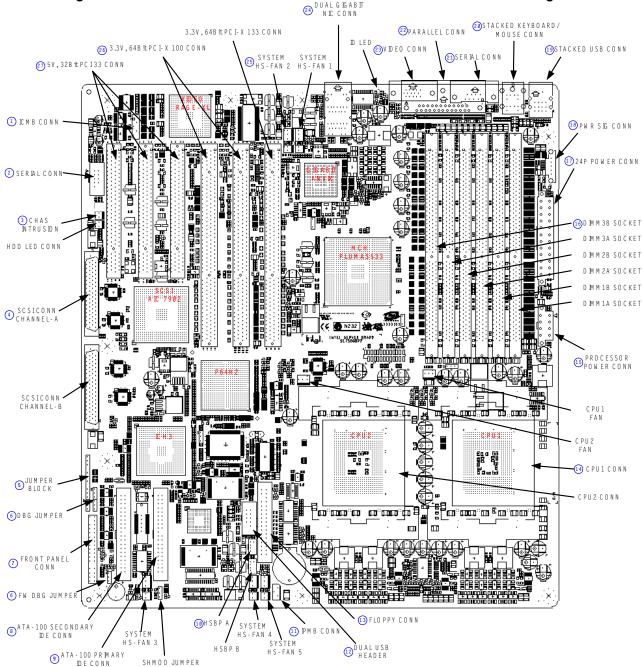

| Figure 17. Intel® Server Board SE7501HG2 Server Board Mechanical Drawing  | 95 |

# **List of Tables**

| Table 1. SE7501HG2 Intel <sup>®</sup> Xeon™ Processor Support Matrix     | 5  |

|--------------------------------------------------------------------------|----|

| Table 2. Memory Bank Labels                                              | 9  |

| Table 3. I <sup>2</sup> C* Addresses for Memory Module SMB               | 10 |

| Table 4. Supported DDRs                                                  | 12 |

| Table 5. ICH-3 GPIO Usage Table                                          | 15 |

| Table 6. Super I/O GPIO Usage Table                                      | 16 |

| Table 7. PCI Device IDs                                                  | 25 |

| Table 8. PCI Bus Segment Characteristics                                 | 28 |

| Table 9. P32-A Configuration IDs                                         | 29 |

| Table 10. P32-A Arbitration Connections                                  | 29 |

| Table 11. P64-B Configuration IDs                                        | 30 |

| Table 12. P64-B Arbitration Connections                                  | 30 |

| Table 13. P64-C Configuration IDs                                        | 31 |

| Table 14. P64-C Arbitration Connections                                  | 31 |

| Table 15. Video Modes                                                    | 33 |

| Table 16. Video Memory Interface                                         | 34 |

| Table 17. NIC Status LED                                                 | 36 |

| Table 18. Interrupt Mapping                                              | 36 |

| Table 19. Sahalee BMC Pin-out                                            | 43 |

| Table 20. ADM1026 Input Definition                                       | 48 |

| Table 21. Intel® Server Board SE7501HG2 I <sup>2</sup> C Bus Address Map | 51 |

| Table 22. Boot Block POST Progress Codes                                 | 53 |

| Table 23. Boot Block POST Progress Codes                                 | 54 |

| Table 24. POST Progress Code Table                                       | 55 |

| Table 25. Standard POST Error Messages and Codes                         | 57 |

| Table 26. Extended POST Error Messages and Codes                         | 58 |

| Table 27. BIOS Recovery Beep Codes                                       | 61 |

| Table 28. Bootblock Error Beep Codes                                     | 61 |

| Table 29. 3-Beep Boot Block Failure Error Codes                          | 62 |

| Table 30. Temperature Sensors                                            | 62 |

| Table 31. Supported Wake Events                                          | 65 |

| Table 32. Power Connector Pin-out (J9C1)                                 | 66 |

| Table 33. | Power Supply Signal Connector (J9B1)                                           | 66    |

|-----------|--------------------------------------------------------------------------------|-------|

| Table 34. | 12V Power Connector (J4E1)                                                     | 67    |

| Table 35. | DIMM Connectors (J9D1, J8D3, J8D2, J8D1, J7D2, J7D1)                           | 67    |

| Table 36. | Socket 604 Processor Socket Pin-out (J6H1, J8H1)                               | 68    |

| Table 37. | ICMB Header Pin-out (J1A1)                                                     | 71    |

| Table 38. | IPMB Header Pin-out (J4K6)                                                     | 71    |

| Table 39. | IPMB Header Pin-out (J4J2, J4K1)                                               | 72    |

| Table 40. | PCI Slot Characteristics                                                       | 72    |

| Table 41. | Slot 1 PCI-X 64-bit 3.3V Pin-out (J4D1)                                        | 72    |

| Table 42. | Slot 2 PCI-X 64-bit 3.3V ZCR(Zero Channel RAID) Pin-out (J3D2)                 | 74    |

| Table 43. | Slot 3 PCI-X 64-bit3.3V Pin-out (J3D1)                                         | 75    |

| Table 44. | Slots 4, 5 and 6 32-bit 5V Pin-out (J2C2, J2C1, J1C4)                          | 76    |

| Table 45. | Front Panel 34-Pin Header Pin-out (J1J2)                                       | 77    |

| Table 46. | VGA Connector Pin-out (J7A1)                                                   | 78    |

| Table 47. | 68-Pin SCSI Connector Pin-out (J1D1, J1F1)                                     | 78    |

| Table 48. | Dual NIC Stacked RJ45 Connector Pin-out (J5A2)                                 | 79    |

| Table 49. | ATA-100 40-Pin Connectors Pin-out (J1J4, J2J2)                                 | 80    |

| Table 50. | USB Connectors Pin-out (J9A2)                                                  | 81    |

| Table 51. | Optional USB Connection Header Pin-out (J4J1)                                  | 81    |

| Table 52. | Legacy 34-Pin Floppy Connector Pin-out (J4J3)                                  | 82    |

| Table 53. | Rear DB-9 Serial A Port Pin-out (J8A1)                                         | 82    |

| Table 54. | 9-Pin Header Serial B Port Pin-out (J1B1)                                      | 83    |

| Table 55. | DB-25 Parallel Port Pin-out (J7A2)                                             | 83    |

| Table 56. | Keyboard and Mouse PS2 Connector Pin-out (J9A1)                                | 84    |

| Table 57. | 3-Pin Fan Headers Pin-out (J5A1, J4A1, J4K4, J4K2, J2K4, J2K1, J7F1, J5F1)     | 84    |

| Table 58. | 2-Pin Hot-Swap Fan Optional Headers Pin-out (J5B1, J4B1, J4K5, J4K3, J2K5, J2K | (2)84 |

| Table 59. | Configuration Jumper Options                                                   | 85    |

| Table 60. | BMC Configuration Jumper Options                                               | 86    |

| Table 61. | Absolute Maximum Ratings                                                       | 87    |

| Table 62. | Intel® Server Board SE7501HG2 Power Budget                                     | 87    |

| Table 63. | Intel® Server Board SE7501HG2 Static Power Supply Voltage Specification        | 88    |

| Table 64. | Intel® Server Board SE7501HG2 Dynamic Power Supply Voltage Specification       | 88    |

| Table 65. | Voltage Timing Parameters                                                      | 89    |

| Table 66. | Turn On/Off Timing                                                             | 89    |

| Table 67. | Transient Load Requirements                                                    | 91    |

| Table 68. Server Board Connector Specifications |  |

|-------------------------------------------------|--|

|-------------------------------------------------|--|

# 1. Introduction

The Intel® Server Board SE7501HG2 Technical Product Specification (TPS) provides technical details for the server board's functional architecture and feature set. It also provides a high-level detail of some of the board's functional sub-systems.

This document is sub-divided into the following main chapters:

Chapter 2: SE7501HG2 Server Board Overview

Chapter 3: Functional Architecture

Chapter 4: Configuration and Initialization

Chapter 5: Clock Generation and Distribution

Chapter 6: PCI I/O Subsystem

Chapter 7: Server Management

Chapter 8: SE7501HG2 ACPI Implementation

Chapter 9: SE7501HG2 Connectors

Chapter 10: Configuration Jumpers

Chapter 11: Power Information

Chapter 12: Regulatory and Integration Information

Chapter 13: Mechanical Specifications

### 1.1 Audience

This document is intended for technical personnel who desire a technical overview of the SE7501HG2 server board. Familiarity with personal computers, device interfaces, Intel® server architecture and the Peripheral Component Interconnect (PCI and PCI-X) local bus architecture is assumed.

# 2. SE7501HG2 Server Board Overview

The server board SE7501HG2 is a monolithic printed circuit board with features that were designed to support the general-purpose volume server market. The architecture is based on the Intel<sup>®</sup> E7501 chipset and is capable of supporting one or two Intel<sup>®</sup> Xeon<sup>™</sup> processors and up to twelve gigabytes of memory.

## 2.1 SE7501HG2 Feature Set

The SE7501HG2 sever board supports the following feature set:

- Dual Intel<sup>®</sup> Xeon<sup>™</sup> processors in FC-PGA2P package using Socket 604

- 533 MHz Front Side Bus

- Intel<sup>®</sup> E7501 chipset

- E7501 Memory Controller Hub

- o P64H2 PCI/PCI-X 64-bit PCI/PCI-X Controller Hub2

- ICH3-S I/O Controller Hub

- Support for six DDR266 compliant registered ECC DDR DIMMs providing up to 12 GB of memory.

- Three separate and independent PCI buses:

- Segment A: 32-bit, 33 MHz, 5 V, Full-length PCI (P32-A) with one embedded devices:

- Three slots: 32-bit/33MHz PCI Slot (PCI Slot 4, Slot 5 and Slot 6)

- 2D/3D graphics controller: ATI RAGE\* XL Video Controller with 8 MB of SDRAM

- Segment B: 64-bit, 100 MHz, 3.3 V, Full-length PCI (P64-B) supporting the following configuration:

- Two slots: 64-bit/100MHz PCI-X<sup>1</sup> Slots (PCI-X Slot 2 and Slot 3)

- Dual-channel Adaptec\* AIC-7902 wide Ultra-320 SCSI Controller

- Dual-channel Adaptec\* HostRAID support

- Zero Channel RAID (ZCR) support. Also known as modular M-ROMB (Slot2)

- Segment C: 64-bit, 133 MHz, 3.3 V, Full-length PCI (P64-C) supporting the following configuration:

- One slot: 64-bit/133MHz PCI-X<sup>1</sup> Slots (PCI-X Slot 1)

- Dual –channel Intel® 82546EB Gigabit Ethernet Controller

- LPC (Low Pin Count) bus segment with two embedded devices:

- Baseboard Management Controller (BMC) providing monitoring, alerting, and logging of critical system information obtained from embedded sensors on server board

<sup>&</sup>lt;sup>1</sup> The BIOS is responsible for setting the mode (PCI or PCI-X) and bus speed for the two segments provided by the P64H2. The actual bus mode/speed will be determined by the least capable card installed on that bus.

- Super I/O controller chip providing all PC-compatible I/O (floppy, serial, parallel, keyboard, mouse) X-Bus segment with one embedded device:

- Flash ROM device for system BIOS: Intel<sup>®</sup> 32 megabit 28F320C3 Flash ROM

- Three external Universal Serial Bus (USB) ports on the rear of the board with an additional internal header that provides one optional USB port for front panel.

- Two serial ports: One serial port on the rear of the board and one internal header is also available providing an optional Serial B port.

- Two IDE connectors, supporting up to four ATA-100 compatible devices

- Six hot swappable multi-speed system fans and two single-speed CPU fans

- Multiple server management headers providing on-board interconnects to the board's server management features

- SSI-EEB3.0 compliant board form factor, the board size is 12 inch by 13 inch

- SSI-compliant connectors for SSI interface support the 34-pin front panel, floppy, ATA-100 and power connectors

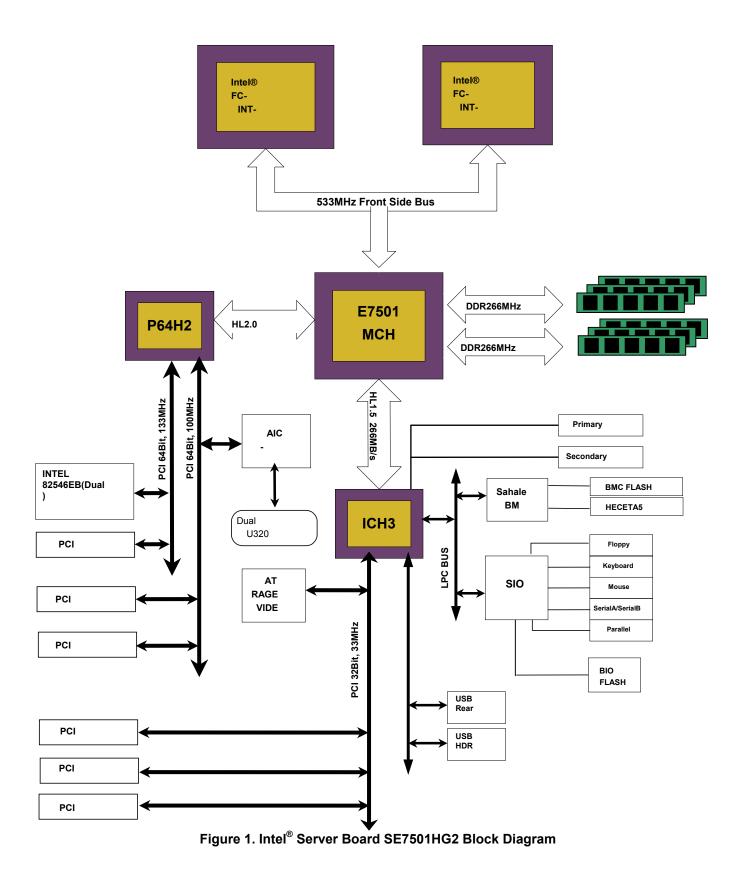

The following figure shows the functional blocks of the server board and the plug-in modules that it supports.

# 3. Functional Architecture

This chapter provides a high-level description of the functionality distributed between the architectural blocks of the Intel® Server Board SE7501HG2.

### 3.1 Processor and Memory Subsystem

The Intel<sup>®</sup> E7501 chipset provides a 36-bit address, 64-bit data processor host bus interface, operating at 533MHz in the AGTL+ signaling environment. The MCH component of the chipset provides an integrated memory controller, an 8-bit hub interface, and three 16-bit hub interfaces.

The hub interface can provide the interface to two 64-bit, 133-MHz, Rev 1.0 compliant PCI-X buses via the P64H2. The server board SE7501HG2 directly supports up to 12 GB of ECC memory, using six DDR266-compliant registered DIMMs. The ECC implementation in the MCH can detect and correct single-bit errors, can detect multiple-bit errors, and supports the Intel® SDDC feature with x4 DIMMs.

#### 3.1.1 Processor Support

The server board SE7501HG2 supports one or two Intel<sup>®</sup> Xeon<sup>™</sup> processors in the Socket 604 FCPGA2P package. The server board will support the Intel<sup>®</sup> Xeon processors with 512KB L2 cache. When two processors are installed, both processors must be of identical revision, core voltage, and bus/core speed. When only one processor is installed, it should be in the socket labeled CPU-1 (nearest to the edge of the board) and the other socket must be empty. The support circuitry on the server board consists of the following:

Dual Socket Support for either FC-mPGA2P (533Mhz 604 pin) or INT3-mPGA (400Mhz 603 pin) processor packages (in dual processor configurations both processors must be identical)

| Processor<br>Family | Package Type | FSB<br>Frequency | Frequency | Cache Size | Support |

|---------------------|--------------|------------------|-----------|------------|---------|

| Intel® Xeon™        | INT3-mPGA    | 400 MHz          | 1.8 GHz   | 512KB      | Yes     |

| Intel® Xeon         | INT3-mPGA    | 400 MHz          | 2.0 GHz   | 512KB      | Yes     |

| Intel® Xeon         | INT3-mPGA    | 400 MHz          | 2.2 GHz   | 512KB      | Yes     |

| Intel® Xeon         | INT3-mPGA    | 400 MHz          | 2.4 GHz   | 512KB      | Yes     |

| Intel® Xeon         | INT3-mPGA    | 400 MHz          | 2.6 GHz   | 512KB      | Yes     |

| Intel® Xeon         | INT3-mPGA    | 400 MHz          | 2.8 GHz   | 512KB      | Yes     |

| Intel® Xeon         | INT3-mPGA    | 400 MHz          | 3.0 GHz   | 512KB      | Yes     |

| Intel® Xeon         | FC-mPGA2P    | 533 MHz          | 1.8 GHz   | 512KB      | Yes     |

| Intel® Xeon         | FC-mPGA2P    | 533 MHz          | 2.0 GHz   | 512KB      | Yes     |

| Intel® Xeon         | FC-mPGA2P    | 533 MHz          | 2.2 GHz   | 512KB      | Yes     |

| Intel® Xeon         | FC-mPGA2P    | 533 MHz          | 2.4 GHz   | 512KB      | Yes     |

| Intel® Xeon         | FC-mPGA2P    | 533 MHz          | 2.6 GHz   | 512KB      | Yes     |

| Intel® Xeon         | FC-mPGA2P    | 533 MHz          | 2.8 GHz   | 512KB      | Yes     |

| Intel® Xeon         | FC-mPGA2P    | 533 MHz          | 3.06 GHz  | 512KB      | Yes     |

Table 1. SE7501HG2 Intel<sup>®</sup> Xeon™ Processor Support Matrix

#### Notes:

- The SE7501HG2 incorporates an auto-termination feature on the second processor socket (labeled CPU #2), which is designed to automatically terminate signal lines that would not be in use in a single processor configuration. If a single processor is to be used, the processor must be located in the primary socket which is closest to the edge of the system board (labeled CPU #1). For socket locations, refer to Figure 17 of this document.

- The server board SE7501HG2 is designed to provide up to 75 Amps per processor. Processors with higher current requirements are not supported.

In addition to the circuitry described above, the processor subsystem contains the following:

- Processor module presence detection logic

- Server management registers and sensors

- Reset configuration logic

- APIC Bus

#### 3.1.1.1 Processor VRM

The SE7501HG2 baseboard has a single VR (voltage regulator) to support two processors. It is compliant with the VRM 9.1 specification and provides a maximum of 150 Amps, which is capable of supporting current supported processors as well as future processors that do not exceed the 150 Amp limit.

The board hardware and BMC will read the processor VID (voltage identification) bits for each processor before turning on the VRM. If the VIDs of the two processors are not identical, then the BMC will not turn on the VRM and a beep code is generated.

#### 3.1.1.2 Reset Configuration Logic

The BIOS determines the processor stepping, cache size, etc., through the CPUID instruction. The requirements are that all processors in the system must operate at the same frequency and have the same cache sizes. No mixing of product families is supported.

The processor information is read at every system power-on and the speed is set to the fixed processor speed.

**Note:** No manual processor speed setting options exist either in the form of a BIOS setup option or jumpers when using production level processors.

#### 3.1.1.3 Processor Module Presence Detection

Logic on the baseboard detects the presence and identity of installed processors. The PMC checks the logic and will not turn on the system DC power unless the VIDs of both the processors match in a DP configuration.

#### 3.1.1.4 Interrupts and APIC

Interrupt generation and notification to the processors are done by the APICs in the ICH3-S and the P64H2 using messages on the front side bus.

#### 3.1.1.5 Server Management Registers and Sensors

The baseboard management controller manages registers and sensors associated with the processor / memory subsystem.

#### 3.1.2 Memory Subsystem

The server board SE7501HG2 supports up to six DIMM slots for a maximum memory capacity of 12 GB. The DIMM organization is x72, which includes eight ECC check bits. The memory interface runs at 266MHz. The memory controller supports memory scrubbing, single-bit error correction and multiple-bit error detection and Intel® Single Device Data Correction (SDDC) support with x4 DIMMs. Memory can be implemented with either single-sided (one row) or double-sided (two row) DIMMs.

**Note:** Intel does not test, recommend, or support mixing of memory types within the same server system. Functionality issues may occur if mixed memory types are installed in the same server system. Intel recommends that memory modules of identical size, type, banking and stacking technology, and vendor are installed in each server system. Intel will not provide support for issues encountered when mixed memory configurations are in use.

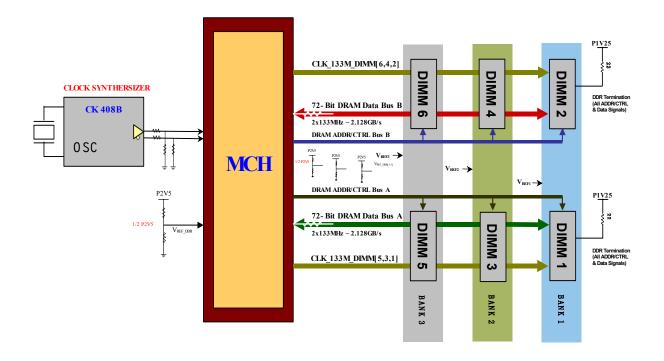

The following figure provides a block diagram of the memory sub-system implemented on the server board SE7501HG2.

Figure 2. Memory Sub-system Block Diagram

#### 3.1.2.1 Memory DIMM Support

The server board SE7501HG2 supports DDR266 compliant registered ECC DIMMs and DDR 266-compliant ECC DIMMs operating at 266 MHz DDR. Only DIMMs tested and qualified by Intel or a designated memory test vendor are supported on the server board SE7501HG2. A list of qualified DIMMs will be made available. Note that all DIMMs are supported by design, but only fully qualified DIMMs will be supported. The minimum supported DIMM size is 128 MB. Therefore, the minimum main memory configuration is 2 x 128 MB or 256 MB. The largest size DIMM supported is a 2 GB stacked registered DDR266 ECC DIMM based on 512 megabit technology.

- Only registered DDR266 compliant, ECC, DDR memory DIMMs will be supported

- ECC single-bit errors will be corrected and multiple-bit errors will be detected.

- SE7501HG2 supports the Intel® Single Device Data Correction (SDDC) feature with x4 DIMMs.

- The maximum memory capacity is 12 GB

- The minimum memory capacity is 256 MB

#### 3.1.2.2 Memory Configuration

Memory interface between the MCH and DIMMs is 144 bits wide. This requires that two DIMMs be populated per bank in order for the system to operate. At least one bank must be populated before the system will boot. If additional banks have less than two DIMMs, the memory for that bank(s) will not be available to the system.

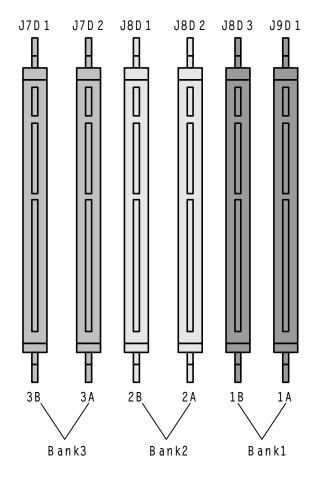

There are three banks of DIMMs, labeled 1, 2, and 3. Bank 1 contains DIMM locations 1A and 1B; Bank 2 contains 2A and 2B; Bank 3 contains 3A and 3B. DIMM socket identifiers are marked with a silk screen next to each DIMM socket on the baseboard. Note that the sockets associated with any given bank are located next to each other.

The baseboard's signal integrity and cooling are optimized when memory banks are populated in order. Therefore, Bank 1 must be installed in pair before Banks 2 and 3.

DIMM and memory configurations must adhere to the following:

- DDR266 DDR registered DIMM modules

- DIMM organization: x72 ECC

- Pin count: 184

- DIMM capacity: 128 MB, 256 MB, 512 MB, 1 GB, 2GB DIMMs

- Serial PD: JEDEC Rev 2.0

- Voltage options: 2.5 V (VDD/VDDQ)

- Two DIMMs must be populated in a bank for a x144 wide memory data path

#### Table 2. Memory Bank Labels

| Memory DIMM                    | Bank | Row  |

|--------------------------------|------|------|

| J9D1 (DIMM 1A), J8D3 (DIMM 1B) | 1    | 0, 1 |

| J8D2 (DIMM 2A), J8D1 (DIMM 2B) | 2    | 2, 3 |

| J7D2 (DIMM 3A), J7D1 (DIMM 3B) | 3    | 4, 5 |

Figure 3. Memory Bank Label Definition

#### 3.1.2.3 I<sup>2</sup>C\* Bus

An I<sup>2</sup>C bus connects the BMC ICH3-S, MCH, P64H2 and the six DIMM slots. This bus is used by the system BIOS to retrieve DIMM information needed to program the MCH memory registers which are required to boot the system. The following table provides the I<sup>2</sup>C addresses for each DIMM slots.

| Device  | Address |

|---------|---------|

| DIMM 1A | 0xA4    |

| DIMM 1B | 0xAC    |

| DIMM 2A | 0xA2    |

| DIMM 2B | 0xAA    |

| DIMM 3A | 0xA0    |

| DIMM 3B | 0xA8    |

### 3.2 Intel® E7501 Chipset

The server board SE7501HG2 is designed around the Intel® E7501 chipset. The chipset provides an integrated I/O bridge and memory controller, and a flexible I/O subsystem core (PCI-X). This is targeted for multiprocessor systems and standard high-volume servers. The Intel® E7501 chipset consists of three components:

- MCH: Memory Controller Hub North Bridge. The MCH North Bridge accepts access requests from the host (processor) bus and directs those accesses to memory or to one of the PCI buses. The MCH monitors the host bus, examining addresses for each request. Accesses may be directed to a memory request queue for subsequent forwarding to the memory subsystem, or to an outbound request queue for subsequent forwarding to one of the PCI buses. The MCH also accepts inbound requests from the P64H2 and the ICH3-S. The MCH is responsible for generating the appropriate controls to control data transfer to and from memory.

- **P64H2: PCI-X 64bit Hub 2.0 I/O Bridge.** The P64H2 provides the interface for 64-bit, 133MHz Rev. 1.0 compliant PCI-X buses. The P64H2 is both master and target on both PCI-X buses.

- ICH3-S: South Bridge. The ICH3-S controller has several components. It provides the interface for a 32-bit, 33-MHz Rev. 2.2-compliant PCI bus. The ICH3-S can be both a master and a target on that PCI bus. The ICH3-S also includes a USB controller and an IDE controller. The ICH3-S is also responsible for much of the power management functions, with ACPI control registers built in. The ICH3-S also provides a number of GPIO pins and has the LPC bus to support low speed legacy I/O.

The MCH, P64H2, and ICH3-S chips provide the pathway between processor and I/O systems. The MCH is responsible for accepting access requests from the host (processor) bus, and directing all I/O accesses to one of the PCI buses or legacy I/O locations. If the cycle is directed to one of the 64-bit PCI segments, the MCH communicates with the P64H2 through a private interface called the HI (Hub Interface) 2.0 bus. If the cycle is directed to the ICH3-S, the cycle is output on the MCH's 8-bit HI 1.5 bus. The P64H2 translates the HI 2.0 bus operation to a 64-bit PCI Rev. 2.2-compliant signaling environment operating at from 133MHz to 33 MHz.

The HI 2.0 bus is 16-bit wide and operates at 66 MHz running 8x data transfers, providing over 1 GB per second of bandwidth.

All I/O for the SE7501HG2, including PCI and PC-compatible, is directed through the MCH and then through either the P64H2 or the ICH3-S provided PCI buses.

- The ICH3-S provides a 32-bit/33-MHz PCI bus hereafter called P32-A

- The P64H2 provides two independent 64-bit buses hereafter called P64-B, and P64-C. P64-C is the PCI-X bus with dual channel gigabit Ethernet controller and P64-B is the PCI-X bus with SCSI controller integrated.

This independent bus structure allows all three PCI buses to operate concurrently.

#### 3.2.1 MCH Memory Architecture Overview

The MCH supports a 144-bit wide memory sub-system that can support a maximum of 12 GB on SE7501HG2 (using 2 GB DIMMs). In this configuration, the MCH supports six DDR266 compliant registered stacked DIMMs for maximum of 12 GB.

The memory interface runs at 266MHz. It uses fifteen address lines (BA [1:0] and MA [12:0]) and supports 64 MB, 128 MB, 256 MB, and 512 MB DRAM densities. The DDR DIMM interface supports memory scrubbing, single-bit error correction, multiple bit error detection, and Intel® Single Device Data Correction (SDDC) with x4 DIMMs.

#### 3.2.1.1 DDR Configurations

The DDR interface supports up to 12 GB of main memory and supports single- and doubledensity DIMMs. The DDR can be any industry-standard DDR. The following table shows the DDR DIMMs supported.

| DIMM<br>Capacity | DIMM<br>Organization | SDRAM<br>Density | SDRAM<br>Organization | # SDRAM Devices /<br>Rows / Banks | # Address bits Rows /<br>Banks / Column |

|------------------|----------------------|------------------|-----------------------|-----------------------------------|-----------------------------------------|

| 128MB            | 16M x 72             | 64Mbit           | 16M x 4               | 18/1/4                            | 12/2/10                                 |

| 128MB            | 16M x 72             | 64Mbit           | 8M x 8                | 18/2/4                            | 12/2/9                                  |

| 128MB            | 16M x 72             | 128Mbit          | 16M x 8               | 9/1/4                             | 12/2/10                                 |

| 256MB            | 32M x 72             | 64Mbit           | 16M x 4               | 36/2/4                            | 12/2/10                                 |

| 256MB            | 32M x 72             | 128Mbit          | 32M x 4               | 18/1/4                            | 12/2/11                                 |

| 256MB            | 32M x 72             | 128Mbit          | 16M x 8               | 18/2/4                            | 12/2/10                                 |

| 256MB            | 32M x 72             | 256Mbit          | 32M x 8               | 9/1/4                             | 13/2/10                                 |

| 512MB            | 64M x 72             | 128Mbit          | 32M x 4               | 36/2/4                            | 12/2/11                                 |

| 512MB            | 64M x 72             | 256Mbit          | 64M x 4               | 18/1/4                            | 13/2/11                                 |

| 512MB            | 64M x 72             | 256Mbit          | 32M x 8               | 18/2/4                            | 13/2/10                                 |

| 512MB            | 64M x 72             | 512Mbit          | 64M x 8               | 9/1/4                             | 13/2/11                                 |

| 1GB              | 128M x 72            | 256Mbit          | 64M x 4               | 36/2/4                            | 13/2/11                                 |

| 1GB              | 128M x 72            | 512Mbit          | 64M x 8               | 18/2/4                            | 13/2/11                                 |

| 1GB              | 128M x 72            | 512Mbit          | 128M x 4              | 18/1/4                            | 13/2/12                                 |

| 2GB              | 256M x 72            | 512Mbit          | 128M x 4              | 36/2/4                            | 13/2/12                                 |

#### Table 4. Supported DDRs

#### 3.2.2 MCH Memory Controller Hub

The E7501 MCH North Bridge (MCH) is a 1005 ball FC-BGA device and uses the proven components of previous generations. In addition, the MCH incorporates a Hub Interface (HI) 2.0. The HI 2.0 interface enables the MCH to directly interface with the P64H2. The MCH also increases the main memory interface bandwidth and maximum memory configuration with a 144-bit wide memory interface.

The MCH integrates three main functions:

- An integrated high performance main memory subsystem

- An HI 2.0 bus interface that provides a high-performance data flow path between the host bus and the I/O subsystem

• A HI 1.5 bus which provides an interface to the ICH3-S (South Bridge).

Other features provided by the MCH include the following:

- Full support of ECC on the memory bus

- Full support of Intel® Single Device Data Correction (SDDC) on the memory interface with x4 DIMMs

- Twelve deep in-order queue

- Full support of registered DDR266 ECC DIMMs

- Support for 12 GB of DDR memory

- Memory scrubbing

#### 3.2.3 P64H2 I/O Bridge

The P64H2 is a 567-ball FCBGA device and provides an integrated I/O bridge that provides a high-performance data flow path between the HI 2.0 and the 64-bit I/O subsystem. This subsystem supports two peer 64-bit PCI-X segments. Because it has two PCI interfaces, the P64H2 can provide large and efficient I/O configurations. The P64H2 functions as the bridge between the HI 2.0 and the two 64-bit PCI-X I/O segments. The HI 2.0 interface can support 1 GB/s of data bandwidth.

**Note:** BIOS is responsible for setting the mode (PCI or PCI-X) and bus speed for the two segments provided by the P64H2 PCI-X I/O Bridge. The actual bus mode/speed will be determined by the least capable card installed on that bus.

#### 3.2.3.1 PCI Bus P64H2 (PCI-X I/O Bridge) Segment-B I/O Subsystem

P64H2 Segment-B supports the following embedded devices and connectors:

- Two 64-bit/100MHz, 3.3V keyed PCI-X slots (PCI-X slots 2 and 3)

- One Adaptec\* 7902 dual-channel Ultra-320 SCSI controller

- PCI slot 2 supports Zero Channel RAID (ZCR) or M-ROMB that allows the on-board SCSI controller to be "hidden" from the system and used by the RAID processor on the add-in card.

- Full length PCI card support

#### 3.2.3.2 PCI Bus P64H2 (PCI-X I/O Bridge) Segment-C I/O Subsystem

P64H2 Segment-C supports the following connectors:

- One 64-bit/133MHz 3.3V keyed PCI-X slot (PCI-X slot 1)

- One Intel® 82546EB dual-channel gigabit Ethernet controller

- Full length PCI card support

#### 3.2.4 ICH3-S I/O Controller Hub (South Bridge)

The ICH3-S South Bridge is a multi-function PCI device, housed in a 421-pin BGA device, providing a PCI-to-LPC bridge, a PCI IDE interface, a PCI USB controller, and a power

management controller. Each function within the ICH3-S has its own set of configuration registers. Once configured, each appears to the system as a distinct hardware controller sharing the same PCI bus interface.

On the server board SE7501HG2, the primary role of the ICH3-S is to provide the gateway to all PC-compatible I/O devices and features. The SE7501HG2 uses the following ICH3-S features:

- PCI bus interface

- LPC bus interface

- IDE interface, with Ultra DMA 100 capability

- Universal Serial Bus (USB) interface

- PC-compatible timer/counter and DMA controllers

- APIC and 8259 interrupt controller

- Power management

- General purpose I/O

- System RTC

The following are the descriptions of how each supported feature is used on the server board SE7501HG2.

#### 3.2.4.1 PCI Bus P32-A I/O Subsystem

The ICH3-S provides a legacy 32-bit PCI subsystem and acts as the central resource on this PCI interface.

P32-A supports the following embedded devices:

- An ATI\* RAGE XL video controller with 3D/2D graphics accelerator

- Three 32-bit/33 MHz, 5V keyed PCI slots (PCI Slot 4, 5 and 6)

#### 3.2.4.2 PCI Bus Master IDE Interface

The ICH3-S acts as a PCI-based Ultra DMA/100 IDE controller that supports programmed I/O transfers and bus master IDE transfers. The ICH3-S supports two IDE channels, supporting two drives each (drives 0 and 1) through two 40-pin (2x20) IDE connectors. The SE7501HG2 IDE interface supports Ultra DMA/100 Synchronous DMA Mode transfers on each channel.

#### 3.2.4.3 USB Interface

The ICH3-S contains three USB1.1 controllers for up to six USB ports. The USB controller moves data between main memory and USB connectors. All six ports function identically and with the same bandwidth.

The SE7501HG2 provides three external USB ports on the ATX I/O panel area of the server board. The fourth and fifth USB ports are optional and can be accessed by special cabling (not bundled with product) from the internal 9-pin connector located on the baseboard to external USB ports located either in the front or the rear of a given chassis.

#### 3.2.4.4 Compatibility Interrupt Control

The ICH3-S provides the functionality of two 82C59 PIC devices for ISA-compatible legacy AT interrupt handling.

#### 3.2.4.5 APIC

The ICH3-S integrates an IO APIC that is used to distribute 24 PCI interrupts.

#### 3.2.4.6 General Purpose Input and Output Pins (GPIO)

The ICH3-S provides a number of general purpose input and output pins. Many of these pins have alternate functions, and thus all are not available. The following table lists the GPI and GPO pins used on the SE7501HG2 baseboard and gives a brief description of their function.

| Pin # | Signal Name               | Description                                         |

|-------|---------------------------|-----------------------------------------------------|

| D4    | P64H_RASERR_L             | Reliability, Availability, Serviceability Error     |

| B6    | ICH3_RST_VIDEO_L          | Disable Video Controller                            |

| B3    | ICH3_RST_SCSI_L           | Disable SCSI Controller                             |

| Y3    | ICH3_RST_NIC1_L           | Disable Network Interface Controller #1             |

| Y2    | SIO_PME_L                 | PME# from SIO                                       |

| V2    | IDE_CBL_DET_P             | Primary IDE Bus 80 Conductor Cabel Detect           |

| V4    | BMC_IRQ_SMI_L             |                                                     |

| F21   | ZZ_MFG_MODE               | detect Manufacturing Mode for test                  |

| G19   | ZZ_PASSWORD_CLR_L         | Password Clear                                      |

| E22   | ZZ_BIOS_RCVR_L            | Enable Recovery Boot                                |

| E21   | ZZ_BB_ID0                 | Baseboard ID 0 - Used to identify revision of board |

| H21   | ZZ_BB_ID1                 | Baseboard ID 1 - Used to identify revision of board |

| G23   | ZZ_BB_ID2                 | Baseboard ID 2 - Used to identify revision of board |

| G21   | ZZ_ICH3_FRB3_TIMER_HALT_L | ICH3 FRB3 Timer Halt Output                         |

| D23   | ZZ_CMOS_CLR_L             | CMOS clear                                          |

| E23   | IDE_CBL_DET_S             | Secondary IDE Bus 80 Conductor Cabel Detect         |

#### Table 5. ICH-3 GPIO Usage Table

#### 3.2.4.7 Power Management

One of the embedded functions of the ICH3-S is a power management controller. The server board SE7501HG2 uses this to implement ACPI-compliant power management features. The SE7501HG2 supports sleep states S0, S1, S4, and S5.

#### 3.2.4.8 Real-time Clock

The SE7501HG2 server board uses the RTC function provided by ICH3-S.

### 3.3 Super I/O

The National Semiconductor\* PC87417 Super I/O device contains the system RTC, all of the necessary circuitry to control two serial ports, one parallel port, floppy disk, and PS/2-

compatible keyboard and mouse. The server board SE7501HG2 supports the following features:

- GPIOs

- Two serial ports

- Parallel Port

- Floppy

- Keyboard and mouse through PS/2 connectors

- Wake event control

#### 3.3.1 GPIOs

The National Semiconductor\* PC87417 Super I/O provides a number of general-purpose input/output pins that the server board SE7501HG2 utilizes. The following table identifies the pin, the signal name used in the schematic and a brief description of each pin's usage.

| Pin # | Signal Name    | Description                      |

|-------|----------------|----------------------------------|

| 49    | ROMB_PRESENT_L | ROMB Present in add-in connector |

| 35    | BMC_SLP_BTN_L  | Sleep Button from BMC            |

| 38    | SIO_PME_L      | PME# to ICH3                     |

| 124   | SIO_EMP_INUSE  | Enable EMP port                  |

| 20    | PA_PCIXCAP     | PCI-X Capability                 |

| 21    | PB_PCIXCAP     | PCI-X Capability                 |

| 50    | PA_PME_L       | PME# from P64H2-channel A        |

| 51    | FP_PWR_LED_L   | Front Panel Power Indicator      |

| 52    | PB_PME_L       | PME# from P64H2-channel B        |

| 53    | BMC_SCI_L      | SCI signal                       |

#### Table 6. Super I/O GPIO Usage Table

#### 3.3.2 Serial Ports

The server board SE7501HG2 provides two serial ports, one DB9 connector (J8A1) is located on the rear I/O to provide Serial Port A and an internal 9-pin header (J1B1) provides Serial Port B. See Section 9.6.7 for the connector pin-outs.

#### 3.3.3 Parallel Port

The server board SE7501HG2 provides one parallel port via a DB-25 connector (J7A2) located on the rear ATX I/O. See Section 9.6.8 for the connector pin-outs.

### 3.3.4 Floppy Disk Controller

The floppy disk controller (FDC) in the SIO (Super I/O) is functionally compatible with floppy disk controllers in the DP8473 and N844077. All FDC functions are integrated into the SIO, including an analog data separator and 16-byte FIFO. The SE7501HG2 provides a SSI compliant 36-pin connector (J4J3).

#### 3.3.5 Keyboard and Mouse

Two PS/2 ports are provided for keyboard and mouse and share a common housing (J9A1). The top one is labeled "mouse" and the bottom one is labeled "keyboard," although the board set supports swapping these connections.

#### 3.3.6 Wake-up Control

The Super I/O contains functionality that allows various events to control the power-on and power-off the system.

#### 3.3.7 BIOS Flash

The server board SE7501HG2 incorporates an Intel<sup>®</sup> 3-Volt Advanced+ Boot Block 28F320C3 Flash memory component. The 28F320C3 is a high-performance 32-megabit memory component that provides 2048K x 16 of BIOS and non-volatile storage space. The flash device is connected through the X-bus from the SIO.

# 4. Configuration and Initialization

This chapter describes the initial programming environment including address maps for memory and I/O, techniques and considerations for programming ASIC registers, and hardware options configuration.

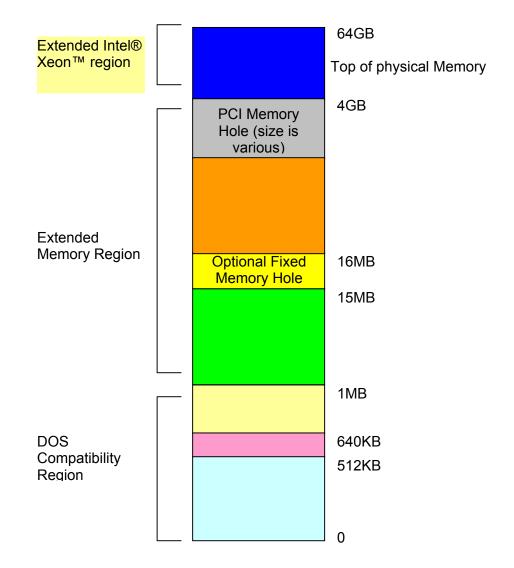

### 4.1 Memory Space

At the highest level, the Intel® Xeon<sup>™</sup> processor address space is divided into three regions, as shown in the following figure. Each region contains sub-regions as described in following sections. Attributes can be independently assigned to regions and sub-regions using the SE7501HG2 registers.

Figure 4. Intel® Xeon™ Processor Memory Address Space

#### 4.1.1 DOS Compatibility Region

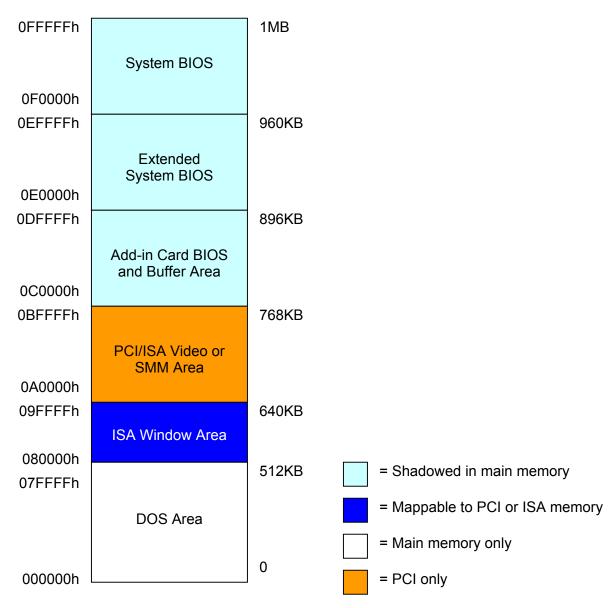

The first region of memory below 1 MB was defined for early PCs, and must be maintained for compatibility reasons. The region is divided into sub-regions as shown in the following figure.

#### 4.1.1.1 DOS Area

The DOS region is 512 KB in the address range 0 to 07FFFFh. This region is fixed and all accesses go to main memory.

#### 4.1.1.2 ISA Window Memory

The ISA Window Memory is 128 KB between the addresses of 080000h to 09FFFFh. This area can be mapped to the PCI bus or main memory.

#### 4.1.1.3 Video or SMM Memory

The 128 KB Graphics Adapter Memory region at 0A0000h to 0BFFFFh is normally mapped to the VGA controller on the PCI bus. This region is also the default region for SMM space.

#### 4.1.1.4 Add-in Card BIOS and Buffer Area

The 128 KB region between addresses 0C0000h to 0DFFFFh is divided into eight segments of 16 KB segments mapped to ISA memory space, each with programmable attributes, for expansion cards buffers. Historically, the 32 KB region from 0C0000h to 0C7FFFh has contained the video BIOS location on the video card.

#### 4.1.1.5 Extended System BIOS

This 64 KB region from 0E0000h to 0EFFFFh is divided into 4 blocks of 16 KB each, and may be mapped with programmable attributes to map to either main memory or to the PCI bus. Typically this area is used for RAM or ROM. This region can also be used for extended SMM space.

#### 4.1.1.6 System BIOS

The 64 KB region from 0F0000h to 0FFFFFh is treated as a single block. By default this area is normally read/write disabled with accesses forwarded to the PCI bus. Through manipulation of R/W attributes, this region can be shadowed into main memory. This region can also be used for extended SMM space.

#### 4.1.2 Extended Memory

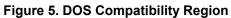

Extended memory on SE7501HG2 is defined as all address space greater than 1MB. The extended memory region covers 4GB of address space from addresses 0100000h to FFFFFFFh, as shown in the following figure.

#### 4.1.2.1 Main Memory

All installed memory greater than 1 MB is mapped to local main memory, up to top of physical memory, which is located at 12 GB. Memory between 1 MB to 15 MB is considered to be standard ISA extended memory. 1 MB of memory starting at 15 MB can be optionally mapped to the PCI bus memory space.

The remainder of this space, up to 12 GB, is always mapped to main memory, unless Extended SMRAM is used, which limits the top of memory to 256 MB.

#### 4.1.2.2 PCI Memory Space

Memory addresses below the 4 GB range are mapped to the PCI bus. This region is divided into three sections: High BIOS, APIC Configuration Space, and General-purpose PCI Memory. The General-purpose PCI Memory area is typically used for memory-mapped I/O to PCI devices. The memory address space for each device is set using PCI configuration registers.

#### 4.1.2.3 High BIOS

The top 2 MB of Extended Memory is reserved for the system BIOS, extended BIOS for PCI devices, and A20 aliasing by the system BIOS. The Intel® Xeon™ processor begins executing from the high BIOS region after reset.

#### 4.1.2.4 I/O APIC Configuration Space

A 64 KB block located 20 MB below 4 GB (0FEC00000 to 0FEC0FFFh) is reserved for the I/O APIC configuration space.

I/O APIC units are located beginning at a base address determined by subtracting 013FFFF0h from the reset vector. The first I/O APIC is located at FEC00000h. Each I/O APIC unit is located at FEC0c000h where x is the I/O APIC unit (0 through F).

#### 4.1.2.5 Extended Intel<sup>®</sup> Xeon<sup>™</sup> Processor Region (above 4GB)

An Intel® Xeon<sup>™</sup> processor-based system can have up to 64 GB of addressable memory. The BIOS uses the Extended Addressing mechanism to use the address ranges.

#### 4.1.3 Memory Shadowing

Any block of memory that can be designated as read-only or write-only can be "shadowed" into main memory. Typically this is done to allow ROM code to execute more rapidly out of RAM. ROM is designated read-only during the copy process while RAM at the same address is designated write-only. After copying, the RAM is designated read-only and the ROM is designated write-only (shadowed). Processor bus transactions are routed accordingly. Transactions originated from the PCI bus or ISA masters and targeted at shadowed memory block will not appear on the processor's bus.

#### 4.1.4 System Management Mode Handling

The Intel® E7501 MCH supports System Management Mode (SMM) operation in standard (compatible) mode. System Management RAM (SMRAM) provides code and data storage space for the SMI\_L handler code, and is made visible to the processor only on entry to SMM, or other conditions, which can be configured using Intel® E7501 PCI registers. Compatible SMRAM is located in main memory below the 1 MB boundary at addresses 000A0000h through 000B0000h. The region is non-cacheable.

### 4.2 I/O Map

The SE7501HG2 allows I/O addresses to be mapped to the processor bus or through designated bridges in a multi-bridge system. Other PCI devices, including the ICH3-S, have built-in features that support PC-compatible I/O devices and functions, which are mapped to specific addresses in I/O space. On the server board SE7501HG2, the ICH3-S provides the bridge to ISA functions through the LPC bus.

### 4.3 Accessing Configuration Space

All PCI devices contain PCI configuration space, accessed using mechanism #1 defined in the PCI Local Bus Specification.

If dual processors are used, only the processor designated as the BSP should perform PCI configuration space accesses. Precautions should be taken to guarantee that only one processor performs system configuration.

Two DWORD I/O registers in the Intel chipset are used for the configuration space register access:

- CONFIG\_ADDRESS (I/O address 0CF8h)

- CONFIG\_DATA (I/O address 0CFCh)

When CONFIG\_ADDRESS is written to with a 32-bit value selecting the bus number, device on the bus, and specific configuration register in the device, a subsequent read or write of CONFIG\_DATA initiates the data transfer to/from the selected configuration register. Byte enables are valid during accesses to CONFIG\_DATA; they determine whether the configuration register is being accessed or not. Only full DWORD reads and writes to CONFIG\_ADDRESS are recognized as a configuration access by the Intel chipset. All other I/O accesses to CONFIG\_ADDRESS are treated as normal I/O transactions.

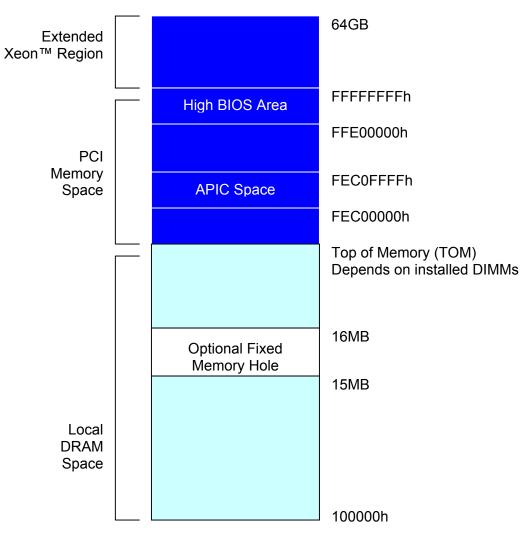

#### 4.3.1 CONFIG\_ADDRESS Register

CONFIG\_ADDRESS is 32 bits wide and contains the field format shown in the following figure. Bits [23::16] choose a specific bus in the system. Bits [15::11] choose a specific device on the selected bus. Bits [10::8] choose a specific function in a multi-function device. Bits [6::2] select a specific register in the configuration space of the selected device or function on the bus.

#### Figure 7. CONFIG\_ADDRESS Register

#### 4.3.1.1 Bus Number

PCI configuration space protocol requires that all PCI buses in a system be assigned a Bus Number. Bus Numbers must be assigned in ascending order within hierarchical buses. Each PCI Bridge has registers containing its PCI Bus Number and subordinate PCI Bus Number, which must be loaded by Postcode. The Subordinate PCI Bus Number is the bus number of the last hierarchical PCI bus under the current bridge. The PCI Bus Number and the Subordinate PCI Bus Number are the same in the last hierarchical bridge.

#### 4.3.1.2 Device Number and IDSEL Mapping

Each device under a PCI bridge has its IDSEL input connected to one bit out of the PCI bus address/data signals AD [31::11] for the PCI bus. Each IDSEL-mapped AD bit acts as a chip select for each device on PCI. The host bridge responds to a unique PCI device ID value, that along with the bus number, cause the assertion of IDSEL for a particular device during configuration cycles. The following table shows the correspondence between IDSEL values and PCI device numbers for the PCI bus. The lower 5-bits of the device number are used in CONFIG\_ADDRESS bits [15::11].

| Device Description    | Bus #<br>(segment) | Device<br>Number<br>(Hex) |

|-----------------------|--------------------|---------------------------|

| North Bridge (MCH)    | 0                  | 00                        |

| ICH3 P2P Bridge       | 0                  | 1E                        |

| ICH3 USB              | 0                  | 1D                        |

| ICH3 IDE              | 0                  | 1F                        |

| Video                 | 1                  | 0C                        |

| P64H2 P2P Bridge A    | 2                  | 1F                        |

| P64H2 P2P Bridge B    | 2                  | 1D                        |

| Dual Gigabit NIC      | 4 (P64-C)          | 05                        |

| Slot 1 (PCI-X 64/133) | 4 (P64-C)          | 02                        |

| Slot 2 (PCI-X 64/100) | 3 (P64-B)          | 01                        |

| Slot 3 (PCI-X 64/100) | 3 (P64-B)          | 02                        |

| Slot 4 (PCI 32/33)    | 1 (P64-A)          | 0A                        |

| Slot 5 (PCI 32/33)    | 1 (P32-A)          | 09                        |

| Slot 6 (PCI 32/33)    | 1 (P32-A)          | 08                        |

| SCSI                  | 3 (P64-B)          | 04                        |

### Table 7. PCI Device IDs

# 4.4 Hardware Initialization

An Intel<sup>®</sup> Xeon<sup>™</sup> processor system based on the Intel<sup>®</sup> E7501 MCH is initialized in the following manner.

- 1. When power is applied, after receiving RST\_PWRGD\_PS from the power supply, the BMC provides resets using the RST\_P6\_PWRGOOD signal. The ICH3-S asserts RST\_PCIRST\_L to MCH, P64H2, and other PCI devices. MCH then asserts RST\_CPURST\_L to reset the processor(s).

- The MCH is initialized, with its internal registers set to default values. Before RST\_CPURST\_L is de-asserted, the MCH asserts BREQ0\_L. Processor(s) in the system determine which host bus agents they are, Agent 0 or Agent 1, based on whether BREQ0\_L or BREQ1\_L is asserted. This determines bus arbitration priority and order.

- 3. After the processor(s) in the system determines which processor will be the BSP, the non-BSP processor becomes an application processor and idles, waiting for a Startup Inter Processor Interrupt (SIPI).

- 4. The BSP begins by fetching the first instruction from the reset vector.

- 5. The Intel® E7501 chipset registers are updated to reflect memory configuration. DIMM is sized and initialized.

- 6. All PCI and ISA I/O subsystems are initialized and prepared for booting.

# 5. Clock Generation and Distribution

All buses on the SE7501HG2 baseboard operate using synchronous clocks. Clock synthesizer/driver circuitry on the baseboard generates clock frequencies and voltage levels as required, including the following:

- 133 MHz at 3.3 V logic levels. For processors, MCH, and ITP port

- 66 MHz at 3.3 V logic levels: For MCH, ICH3-S and P64H2 clock

- 33 MHz at 3.3 V logic levels: For ICH3-S, BMC, Video, SIO, and PCI32/33 Slots

- 48 MHz at 3.3 V logic levels: ICH3-S and SIO

- 14 MHz at 3.3V logic levels: ICH3-S, SIO, and Video controller

The synchronous clock sources on the SE7501HG2 baseboard are:

- 133/100-MHz clock for PCI-X Slot, SCSI, and Intel<sup>®</sup> 82546EB Dual Gigabit NIC

- 133-MHz host clock for processors, MCH, memory DIMMs, and the ITP

- 66-MHz clock for MCH, ICH, and P64H2

- 48-MHz clock for ICH and SIO

- 33-MHz clock for ICH, BMC, video, SIO, and PCI32/33 slots

- 14-MHz clock for ICH and video

For information on processor clock generation, see the *CK408B Synthesizer/Driver Specification*.

The SE7501HG2 baseboard also provides asynchronous clock generators:

- 80-MHz clock for the embedded SCSI controller

- 25-MHz clocks for the embedded network interface controllers

- 32.768-KHz clock for the ICH RTC

- 40-MHz clock for the BMC

The following figure illustrates clock generation and distribution on the server board SE7501HG2.

Figure 8. Intel® Server Board SE7501HG2 Clock Distribution

# 6. PCI I/O Subsystem

# 6.1 PCI Subsystem

The primary I/O bus for the server board SE7501HG2 is PCI, with three independent PCI bus segments. The PCI buses comply with the *PCI Local Bus Specification*, Rev 2.2 and with the *PCI-X Specification*, Rev 1.0. The P32-A bus segment is directed through the ICH while the two 64-bit segments, P64-B and P64-C, are directed through the P64H2. The following table lists the characteristics of the three PCI bus segments.

| Table 8. PCI Bus Segment C | haracteristics |

|----------------------------|----------------|

|----------------------------|----------------|

| PCI Bus Segment | Voltage | Width   | Speed          | Туре     | PCI I/O Riser Slots                  |

|-----------------|---------|---------|----------------|----------|--------------------------------------|

| P32-A           | 5 V     | 32 bits | 33 MHz         | Peer Bus | Supports Full-length cards, 5V bus   |

| P64-B           | 3.3 V   | 64 bits | 100/66 MHz     | Peer Bus | Supports Full-length cards, 3.3V bus |

| P64-C           | 3.3 V   | 64 bits | 133/100/66 MHz | Peer Bus | Supports Full-length cards, 3.3V bus |

# 6.1.1 P32-A: 32-bit, 33-MHz PCI Subsystem

All 32-bit, 33-MHz PCI I/O for the server board SE7501HG2 is directed through the ICH3-S. The 32-bit, 33-MHz PCI segment created by the ICH is known as the P32-A segment. The P32-A segment supports the following embedded devices and connectors:

- 2D/3D Graphics Accelerator: ATI\* RAGE XL Video Controller

- Three 32-bit/33MHz PCI Slots (PCI Slot 4, Slot 5 and Slot 6)

Each of the embedded devices listed above will be allocated a GPIO to disable the device. The PCI segment will support full-length, full-height PCI cards as well as half-length PCI cards.

# 6.1.1.1 Device IDs (IDSEL)

Each device under the PCI hub bridge has its IDSEL signal connected to one bit of AD [31:16], which acts as a chip select on the PCI bus segment in configuration cycles. This determines a unique PCI device ID value for use in configuration cycles. The following table shows the bit to which each IDSEL signal is attached for P32-A devices, and the corresponding device description.

| IDSEL Value | Device                        |

|-------------|-------------------------------|

| 24          | PCI32/33 Slot4                |

| 25          | PCI32/33 Slot5                |

| 26          | PCI32/33 Slot6                |

| 28          | ATI RAGE* XL video controller |

## 6.1.1.2 P32-A Arbitration

P32-A supports five PCI masters (ATI RAGE XL, the ICH3-S, three PCI 32-bit slots). All PCI masters must arbitrate for PCI access, using resources supplied by the ICH3-S. The host bridge PCI interface (ICH3-S) arbitration lines REQx\* and GNTx\* are special cases in that they are internal to the host bridge. The following table defines the arbitration connections.

| Baseboard Signals     | Device                       |

|-----------------------|------------------------------|

| PCI_REQ_L3/PCI_GNT_L3 | PCI32/33 Slot4               |

| PCI_REQ_L2/PCI_GNT_L2 | PCI32/33 Slot5               |

| PCI_REQ_L1/PCI_GNT_L1 | PCI32/33 Slot5               |

| PCI_REQ_L0/PCI_GNT_L0 | ATI RAGE XL video controller |

### Table 10. P32-A Arbitration Connections

## 6.1.2 P64-B: 64-bit, 100/66-MHz PCI-X Subsystem

The 64-bit, 100/66-MHz PCI-X bus segment is directed through the P64H2. This PCI segment, P64-B, provides the following embedded devices and connectors:

- Adaptec\* AIC7902 Dual Channel U320 SCSI controller

- Two 64-bit/100MHz PCI-X Slots (PCI-X Slot 2 and Slot 3).

Note: Slot 2 supports ZCR (Zero Channel RAID).

The PCI segment supports full-length, full-height PCI cards as well as half-length PCI cards.

### 6.1.2.1 Device IDs (IDSEL)

Each device under the PCI hub bridge has its IDSEL signal connected to one bit of AD [31:16], which acts as a chip select on the PCI bus segment in configuration cycles. This determines a unique PCI device ID value for use in configuration cycles. The following table shows the bit to which each IDSEL signal is attached for P64-B devices, and the corresponding device description.

| IDSEL Value | Device                   |  |

|-------------|--------------------------|--|

| 20          | On-board SCSI controller |  |

| 17          | PCI-X Slot2              |  |

| 18          | PCI-X Slot3              |  |

| Table 11. P64-I | B Configuration IDs |

|-----------------|---------------------|

|-----------------|---------------------|

### 6.1.2.2 P64-B Arbitration

P64-B supports four PCI masters (AIC7902, P64H2, and two PCI 64-bit slots). All PCI masters must arbitrate for PCI access using resources supplied by the P64H2. The host bridge PCI interface (P64H2) arbitration lines REQx\* and GNTx\* are special cases in that they are internal to the host bridge. The following table defines the arbitration connections.

### Table 12. P64-B Arbitration Connections

| Baseboard Signals   | Device                   |

|---------------------|--------------------------|

| PA_REQ_L0/PA_GNT_L0 | On-board SCSI controller |

| PA_REQ_L2/PA_GNT_L2 | PCI-X Slot2              |

| PA_REQ_L1/PA_GNT_L1 | PCI-X Slot3              |

## 6.1.2.3 Zero Channel RAID (ZCR) Capable Slot 2

The server board SE7501HG2 is capable of supporting either of two zero channel RAID controllers, the Intel<sup>®</sup> SRCZCR RAID adapter and the Adaptec\* ASR-2010S RAID adapter. These ZCR cards are supported only in slot 2 on the P64-B segment.

The ZCR add-in cards leverage the on-board SCSI controller along with their own built-in intelligence to provide a complete RAID controller subsystem on-board. The baseboard uses an implementation commonly referred to as RAID I/O Steering (RAIDIOS) specification version 1.0 to support this feature.

If either of these supported RAID cards are installed, then the SCSI interrupts are routed to the RAID adapter instead of to the PCI interrupt controller. In addition, the IDSEL of the SCSI controller is not driven to the controller and thus will not respond as an on-board device. The host-based I/O device is effectively hidden from the system.

Note: ZCR cards and RAID I/O Steering (RAIDIOS) are only supported in PCI slot 2.

## 6.1.3 P64-C: 64-bit, 133/100/66-MHz PCI-X Subsystem

The 64-bit, 133/100/66-MHz PCI-X bus segment is directed through the P64H2. This PCI segment, P64-C, provides the following embedded devices and connectors:

- One 64-bit/133MHz PCI-X Slot (PCI-X Slot 1)

- Dual Channel Gigabit Ethernet Controller (Intel® 82546EB)

## 6.1.3.1 Device IDs (IDSEL)

Each device under the PCI hub bridge has its IDSEL signal connected to one bit of AD [31:16], which acts as a chip select on the PCI bus segment in configuration cycles. This determines a unique PCI device ID value for use in configuration cycles. The following table shows the bit to which each IDSEL signal is attached for P64H2 segment-C devices, and the corresponding device description.

| IDSEL Value | Device                          |  |  |

|-------------|---------------------------------|--|--|

| 21          | Intel® 82546EB Dual Gigabit NIC |  |  |

| 18          | PCI-X Slot1                     |  |  |

## 6.1.3.2 P64-C Arbitration

P64-C supports three PCI masters (P64H, 82546EB Dual Gigabit NIC, and PCI-X slot). All PCI masters must arbitrate for PCI access, using resources supplied by the P64H2. The host bridge PCI interface arbitration lines REQx\* and GNTx\* are special cases in that they are internal to the host bridge. The following table defines the arbitration connections.

| Table 1 | 14. P64-C | Arbitration | Connections |

|---------|-----------|-------------|-------------|

|---------|-----------|-------------|-------------|

| Baseboard Signals    | Device                   |

|----------------------|--------------------------|

| PA_REQ_L4/P64_S_GNT4 | 82546EB Dual Gigabit NIC |

| PA_REQ_L1/P64_S_GNT1 | PCI-X Slot1              |

# 6.2 Ultra 320 SCSI

The server board SE7501HG2 provides an embedded dual-channel SCSI bus through the use of the Adaptec\* AIC-7902 SCSI controller, which supports up to Ultra 320 SCSI transfers. The AIC-7902 controller contains single SCSI controller that has a single 64-bit, 133-MHz PCI-X bus master interface as a multi-function device, packaged in a 388-pin BGA.

Internally, the controller is capable of operations using LVD SCSI providing 80 MB/sec (Ultra 2), 160 MB/sec (Ultra 160), or 320 MB/sec (Ultra 320). The controller has its own set of PCI configuration registers and PCI I/O registers. The server board SE7501HG2 supports disabling of the on-board SCSI controller through the BIOS setup menu.

The server board SE7501HG2 provides active terminators, termination voltage, a reset-able fuse, and a protection diode for SCSI channel. By design, the on-board termination will be disabled by BIOS when the SCSI cable is detected. The SCSI channel has two 68-pin connector interfaces.

# 6.3 Onboard RAID support

The SE7501HG2 incorporates the Adaptec\* HostRAID and RAIDSelect utility to provide convenient and reliable entry-level RAID support for SCSI devices utilizing the onboard 7902 SCSI subsystem.

The Adaptec RAIDSelect Utility is a BIOS-based array configuration utility (included with HostRAID) used for HostRAID array management. The utility is entered by pressing <CTRL-A> during POST. The Adaptec RAIDSelect Utility is required to create, delete or view the status of HostRAID arrays on the SE7501HG2 system. This section is intended to introduce the user to the capabilities of the onboard HostRAID subsystem. For a comprehensive explanation of HostRAID features and utility usage, please refer to the Adaptec HostRAID Users Guide.

HostRAID offers the following advanced features:

- Bootable array support

- Support for separate RAID arrays per channel

- Support of Hot Swap drives

- Support for Auto Rebuild (if a spare is dedicated to the volume)

- Support for Auto Verify

- Support for all major SCSI peripherals

- Support for Ultra320 products

- Complete RAID configuration and management utility in the BIOS

- Provides graphical RAID management software

The following HostRAID configurations and related restrictions are available:

- **RAID-0**: (Stripe) One RAID 0 with 3 or 4 drives or Two RAID 0s with two drives each. Minimum 2 drives, maximum 4 drives. Two RAID-0 volumes can be configured per channel, 4 drives total per channel.

- **RAID-1**: (Mirror) Two RAID 1s with one spare each. Minimum 2 drives, maximum 4 drives with 1 spare per mirrored volume. RAID-1 volumes can only consist of 2 drives with the option of adding 1 spare; two volumes can be configured per channel

- **RAID-10**: Is not available with the current version of the utility. (This option, although it may be displayed, will remain grayed out.)

- **SPARE**: Maximum one Spare per RAID-1 volume. Two spares maximum per channel.

- **SPANNING**: The Spanning of RAID volumes or spares across channels is not supported.