# Intel® Server Board SE7520BD2

**Technical Product Specification**

Intel order number C62349-003

**Revision 2.3**

June 15, 2005

**Enterprise Platforms and Services Division - Marketing**

## Revision History

| Date       | Revision<br>Number | Modifications                                                                                                                                                                                                                                                                  |

|------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10/29/2003 | 0.4                | First draft for internal review                                                                                                                                                                                                                                                |

| 12/10/2003 | 0.5                | Conversion from generic hardware spec to Intel® Server Board SE7520BD2 specific spec                                                                                                                                                                                           |

| 02/09/2004 | 0.75               | Updated NIC components, mixed processor support, SCSI mirroring support, and CMOS clear.                                                                                                                                                                                       |

| 03/31/2004 | 1.0                | Correct DIMM SMbus address                                                                                                                                                                                                                                                     |

|            |                    | Updated BIOS setup menu                                                                                                                                                                                                                                                        |

|            |                    | Updated Error reporting and handling                                                                                                                                                                                                                                           |

|            |                    | Updated Board Jumper Blocks                                                                                                                                                                                                                                                    |

| 06/14/2004 | 1.1                | Updated Block Diagrams                                                                                                                                                                                                                                                         |

| 11/15/2004 | 1.2                | Updated serveral references and specified details. Added MTBF data. Removed incorrect references to PXH-D. Added details on the SE7520BD2-V SKU. Added schemated for the SE7520BD2-V SKU. Added EM64T data. Added mBMC sensors table. Updated Block Diagrams and Power Budget. |

| 02/07/2005 | 1.3                | Added fan pin-outs. Updated BIOS menus. Added motherboard identification section. Added current errata as Appedix A.                                                                                                                                                           |

| March 2005 | 2.0                | Update to include DDR2 SKUs                                                                                                                                                                                                                                                    |

| June 2005  | 2.3                | Prepared for publication                                                                                                                                                                                                                                                       |

## **Disclaimers**

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® Server Board SE7520BD2 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation. \*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2004-2005. All rights reserved

## **Table of Contents**

| 1. Introd | uction                                                  | 13 |

|-----------|---------------------------------------------------------|----|

| 1.1       | Purpose                                                 | 13 |

| 1.2       | Audience                                                | 13 |

| 1.3       | Document Outline                                        | 13 |

| 1.4       | Additional Technical Documentation                      | 13 |

| 1.5       | Board Usage Disclaimer                                  | 14 |

| 2. Produ  | ct Overview                                             | 15 |

| 2.1       | Server Board Feature Set                                | 15 |

| 2.2       | DDR Server Board                                        | 16 |

| 2.3       | DDR2 Server Board                                       | 17 |

| 2.4       | Server Board Layout                                     | 18 |

| 2.5       | Identifying the Version of an Intel® Server Board       | 23 |

| 2.6       | Chipset Overview                                        | 24 |

| 2.6.1     | Memory Controller Hub (MCH)                             | 24 |

| 2.6.2     | Front Side Bus (FSB)                                    | 24 |

| 2.6.3     | MCH Memory Sub-System                                   | 25 |

| 2.6.4     | PCI Express*                                            | 25 |

| 2.6.5     | Hub Interface                                           | 26 |

| 2.7       | Processor Subsystem                                     | 26 |

| 2.7.2     | Multiple Processor Initialization                       | 28 |

| 2.7.3     | Processor VRD                                           | 28 |

| 2.7.4     | Reset Configuration Logic                               | 28 |

| 2.7.5     | Processor Module Presence Detection                     | 28 |

| 2.7.6     | GTL2006*                                                | 29 |

| 2.7.7     | Common Enabling Kit (CEK) Design Support                | 29 |

| 2.7.8     | Proccess fan Variable Speed Control                     | 29 |

| 2.8       | Memory Sub-System                                       | 30 |

| 2.8.1     | DDR266 Memory                                           | 31 |

| 2.8.2     | DDR333 Memory                                           | 31 |

| 2.8.3     | DDR266 and DDR333 Memory Population                     | 31 |

| 2.8.4     | DDR2-400 Memory                                         | 32 |

| 2.8.5     | DDR2 DIMM Population Rules and Supported Configurations | 33 |

| 2.8.6     | Single-Channel Operation                        | 34 |

|-----------|-------------------------------------------------|----|

| 2.8.7     | ECC                                             | 34 |

| 2.8.8     | I <sup>2</sup> C Bus                            | 37 |

| 2.9       | PCI Sub-System                                  | 38 |

| 2.9.1     | ICH5R PCI Interface                             | 38 |

| 2.9.2     | PXH                                             | 42 |

| 2.9.3     | Ultra320 SCSI Controller                        | 45 |

| 2.9.4     | Modular RAID on MotherBoard (MROMB)             | 46 |

| 2.10      | IO Sub-System                                   | 47 |

| 2.10.1    | Server I/O                                      | 47 |

| 2.10.2    | Intel® 3-Volt Advanced+ Boot Block Flash Memory | 48 |

| 2.10.3    | Video Controller                                | 48 |

| 2.10.4    | NIC Controllers                                 | 48 |

| 2.11      | Clock Generation and Distribution               | 49 |

| 2.11.1    | CK409 Clock Generator                           | 49 |

| 2.11.2    | DB800 Differential Buffer                       | 49 |

| 3. BIOS A | rchitecture                                     | 50 |

| 3.1       | BIOS Functionality                              | 50 |

| 3.1.1     | Support for BIOS Features                       | 50 |

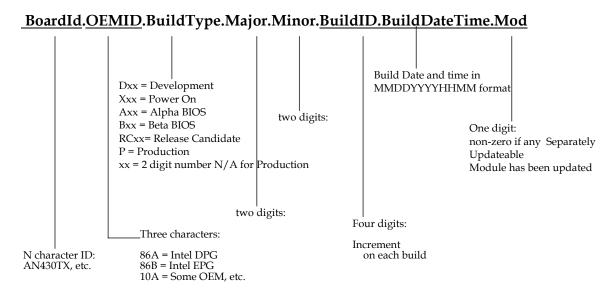

| 3.1.2     | BIOS Identification String                      | 54 |

| 3.1.3     | Hardware Requiring BIOS Support                 | 54 |

| 3.1.4     | BIOS POST                                       | 55 |

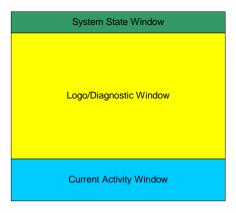

| 3.1.5     | User Interface                                  | 55 |

| 3.2       | BIOS Setup Utility                              | 56 |

| 3.2.1     | Entering BIOS Setup                             | 56 |

| 3.2.2     | Keyboard Commands                               | 56 |

| 3.2.3     | Menu Selection                                  | 57 |

| 3.2.4     | Main Menu                                       | 57 |

| 3.2.5     | Advanced Menu                                   | 58 |

| 3.2.6     | Boot Menu                                       | 69 |

| 3.2.7     | Security Menu                                   | 72 |

| 3.2.8     | Server Menu                                     | 74 |

| 3.2.9     | Exit Menu                                       | 77 |

| 3.3       | Other BIOS Configuration Utilities              | 78 |

| 3.3.1     | Flash Update Utility                            | 78 |

|           |                                                 |    |

| 3.4        | Localization Details                                 | 78  |

|------------|------------------------------------------------------|-----|

| 3.5        | Flash Architecture and Flash Update Utility          | 79  |

| 3.5.1      | Rolling BIOS and On-line Updates                     | 79  |

| 3.5.2      | Flash Update Utility                                 | 79  |

| 3.5.3      | Flash BIOS                                           | 80  |

| 3.5.4      | User Binary Area                                     | 81  |

| 3.6        | Recovery Mode                                        | 82  |

| 3.6.1      | Single Disk BIOS Recovery                            | 82  |

| 3.6.2      | Multi-disk BIOS Recovery                             | 83  |

| 3.6.3      | Update OEM Logo                                      | 84  |

| 3.7        | OEM Binary                                           | 85  |

| 3.8        | PCI Numeration                                       | 87  |

| 3.9        | ACPI Runtime Checkpoints                             | 87  |

| 4. Platfor | m Management Architecture                            | 88  |

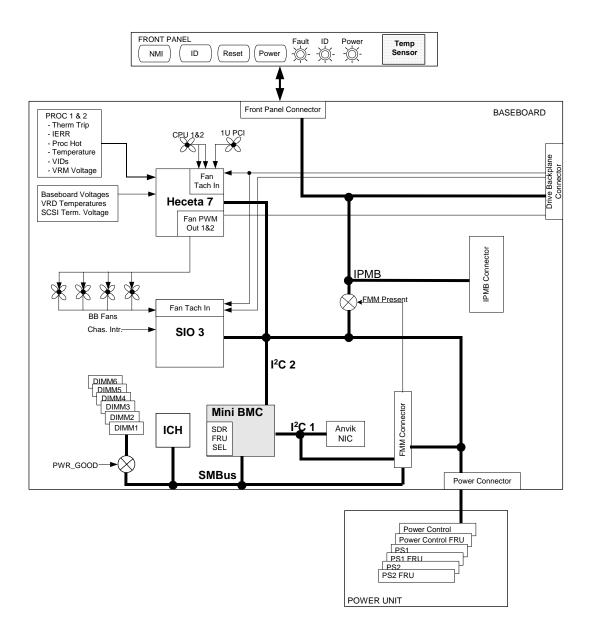

| 4.1        | Management Architecture Overview                     | 88  |

| 4.1.1      | Tiered Server Management Model                       | 88  |

| 4.1.2      | 5V Standby                                           | 93  |

| 4.1.3      | IPMI Messaging, Commands, and Abstractions           | 93  |

| 4.1.4      | IPMI Sensor Model                                    | 94  |

| 4.1.5      | Private Management Buses                             | 95  |

| 4.1.6      | Management Controllers                               | 95  |

| 4.2        | Essentials Management Features and Functionality     | 112 |

| 4.2.1      | Overview of mBMC                                     | 112 |

| 4.2.2      | mBMC Self-test                                       | 112 |

| 4.2.3      | SMBus Interfaces                                     | 113 |

| 4.2.4      | External Interface to mBMC                           | 113 |

| 4.2.5      | Messaging Interfaces                                 | 114 |

| 4.2.6      | Direct Platform Control (IPMI over LAN)              | 116 |

| 4.2.7      | Wake On LAN / Power On LAN and Magic Packet* Support | 118 |

| 4.2.8      | Watchdog Timer                                       | 119 |

| 4.2.9      | System Event Log (SEL)                               | 119 |

| 4.2.10     | Sensor Data Record (SDR) Repository                  | 120 |

| 4.2.11     | Event Message Reception                              | 120 |

| 4.2.12     | Event Filtering and Alerting                         | 120 |

| 4.2.13     | NMI Generation                                       | 123 |

|    | 4.2.14   | SMI Generation                      | 124 |

|----|----------|-------------------------------------|-----|

| 4  | .3       | Platform Management Interconnects   | 124 |

|    | 4.3.1    | Power Supply Interface Signals      | 124 |

|    | 4.3.2    | System Reset Control                | 126 |

|    | 4.3.3    | Fan Speed Control                   | 127 |

|    | 4.3.4    | Front Panel Control                 | 127 |

|    | 4.3.5    | FRU Information                     | 131 |

| 4  | .4       | Sensors                             | 131 |

|    | 4.4.1    | Sensor Type Codes                   | 131 |

| 4  | .5       | Management Buses and Connectors     | 136 |

|    | 4.5.1    | SIO Keyboard and Mouse              | 136 |

|    | 4.5.2    | PS2 Keyboard and Mouse              | 136 |

|    | 4.5.3    | Fast Management Link (FML)          | 136 |

|    | 4.5.4    | LPC/Keyboard Controller Style Ports | 137 |

|    | 4.5.5    | USB                                 | 138 |

|    | 4.5.6    | I <sup>2</sup> C Interfaces         | 138 |

|    | 4.5.7    | 16550*-style UARTs                  | 139 |

|    | 4.5.8    | Interrupts                          | 139 |

|    | 4.5.9    | GPIO Pins and LED Drivers           | 139 |

|    | 4.5.10   | Sleep States Supported              | 139 |

|    | 4.5.11   | Wake Events                         | 140 |

|    | 4.5.12   | AC Power Failure Recovery           | 141 |

|    | 4.5.13   | PCI Power Management Support        | 141 |

| 4  | .6       | System Status Indicators/LEDs       | 142 |

|    | 4.6.1    | Front Panel                         | 142 |

| 5. | Error Re | eporting and Handling               | 145 |

| 5  | .1       | Error Propagation                   | 145 |

| 5  | .2       | Fault Resilient Booting (FRB)       | 145 |

|    | 5.2.1    | FRB-3 – BSP Reset Failures          | 145 |

|    | 5.2.2    | FRB-2 – BSP POST Failures           | 145 |

|    | 5.2.3    | FRB-1 – BSP Self-Test Failures      | 146 |

|    | 5.2.4    | OS Boot Timer - OS Load Failures    | 146 |

|    | 5.2.5    | Application Processor (AP) Failures | 146 |

|    | 5.2.6    | Treatment of Failed Processors      | 146 |

| 5  | .3       | Error Messages and Error Codes      | 147 |

|    | 5.3.1   | POST Error Codes and Messages                               | 147 |

|----|---------|-------------------------------------------------------------|-----|

|    | 5.3.2   | POST Error Beep Codes                                       | 150 |

|    | 5.3.3   | Checkpoints                                                 | 151 |

| 5  | .4      | Error Logging                                               | 153 |

|    | 5.4.1   | Error Sources and Types                                     | 153 |

|    | 5.4.2   | SMI Handler                                                 | 153 |

|    | 5.4.3   | Logging Format Conventions                                  | 155 |

|    | 5.4.4   | POST Code Checkpoints                                       | 159 |

|    | 5.4.5   | Boot Block Initialization Code Checkpoints                  | 161 |

|    | 5.4.6   | Boot Block Recovery Code Checkpoint                         | 162 |

|    | 5.4.7   | DIM Code Checkpoints                                        | 164 |

|    | 5.4.8   | Single-bit ECC Error Throttling Prevention                  | 164 |

| 5  | .5      | Reliability, Availability and Serviceability (RAS) Features | 165 |

|    | 5.5.1   | Memory RAS Features                                         | 165 |

|    | 5.5.2   | PCI Express*                                                | 166 |

|    | 5.5.3   | RAS Features of the Front Side Bus (FSB)                    | 166 |

|    | 5.5.4   | PCI-X*                                                      | 166 |

|    | 5.5.5   | RMC Connector Utilization                                   | 167 |

|    | 5.5.6   | Rolling BIOS                                                | 168 |

| 6. | Connec  | tor Pin-outs and Jumper Blocks                              | 169 |

| 6  | .1      | Board Connector Pin-outs                                    | 169 |

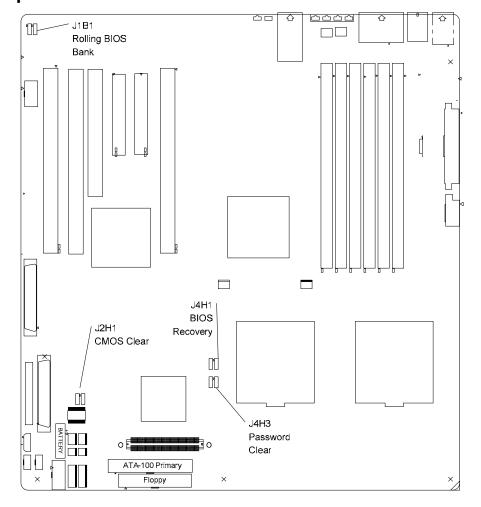

| 6  | .2      | Jumper Blocks                                               | 174 |

|    | 6.2.1   | Rolling BIOS Bank Selection Jumper                          | 175 |

|    | 6.2.2   | BIOS Recovery                                               | 175 |

|    | 6.2.3   | Password Clear                                              | 175 |

|    | 6.2.4   | CMOS Clear                                                  | 175 |

| 7. | Replaci | ng the Back up Battery                                      | 176 |

| 8. | Environ | mental Specifications                                       | 177 |

| 8  | .1      | Environmental Specifications and Cooling Requirements       | 177 |

| 8  | .2      | Power Supply Requirements                                   | 178 |

|    | 8.2.1   | Server board Power Budget                                   | 178 |

|    | 8.2.2   | Voltages Supported                                          | 180 |

|    | 8.2.3   | Standby Powered Device Map                                  | 181 |

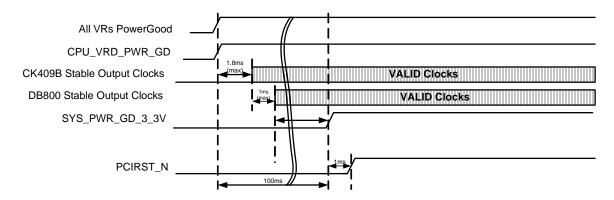

|    | 8.2.4   | System Reset Block Diagram                                  | 181 |

| 8  | .3      | Airflow Requirements                                        | 184 |

#### **Table of Contents**

|    | 8.3.1     | Board Usage Disclaimer                                                       | .184 |

|----|-----------|------------------------------------------------------------------------------|------|

| 8  | 3.4       | Board-level Calculated MTBF                                                  | 184  |

|    | 8.4.1     | Intel SpeedStep® Technology                                                  | 184  |

|    | 8.4.2     | Intel® Extended Memory 64 Technology (Intel® EM64T)                          | 184  |

| 9. | Product   | Regulatory Compliance                                                        | .185 |

| Ś  | 9.1       | Product Safety Compliance                                                    | 185  |

| Ś  | 9.2       | Product EMC Compliance                                                       | 185  |

| Ç  | 9.3       | Mandatory/Standard: Certifications, Registration, Declarations               | 186  |

| Ş  | 9.4       | Product Regulatory Compliance Markings                                       | 186  |

| Ś  | 9.5       | Electromagnetic Compatibility Notices                                        | 186  |

|    | 9.5.1     | Europe (CE Declaration of Conformity)                                        | 186  |

|    | 9.5.2     | Australian Communications Authority (ACA) (C-Tick Declaration of Conformity) | 186  |

|    | 9.5.3     | Ministry of Economic Development (New Zealand) Declaration of Conformity     | 187  |

|    | 9.5.4     | BSMI (Taiwan)                                                                | .187 |

| 10 | . Other U | seful Information                                                            | 188  |

| •  | 10.1      | Platform Confidence Test (PCT)                                               | 188  |

| GI | ossary    |                                                                              | 189  |

| Re | ference C | Occuments                                                                    | 190  |

# **List of Figures**

| Figure 1. Intel® Server Board SE7520BD2 with DDR Memory           | 16  |

|-------------------------------------------------------------------|-----|

| Figure 2. Intel® Server Board SE7520BD2 with DDR2 Memory          | 17  |

| Figure 3. Product Code SE7520BD2SCSI System Block Diagram         | 18  |

| Figure 4. Product Code SE7520BD2SCSID2 System Block Diagram       | 19  |

| Figure 5. Product Code SE7520BD2 System Block Diagram             | 20  |

| Figure 6. Product Code SE7520BD2SATAD2 System Block Diagram       | 21  |

| Figure 7. Product Code SE7520BD2V System Block Diagram            | 22  |

| Figure 8. Intel® Server Board SE7520BD2VD2 System Block Diagram   | 23  |

| Figure 9. 3-pin and 4-pin Heatsink Fan Harnesses                  | 30  |

| Figure 10. DDR DIMM Socket Configuration                          | 31  |

| Figure 11. DIMM Socket Configuration                              | 33  |

| Figure 12. Memory Subsystem                                       | 36  |

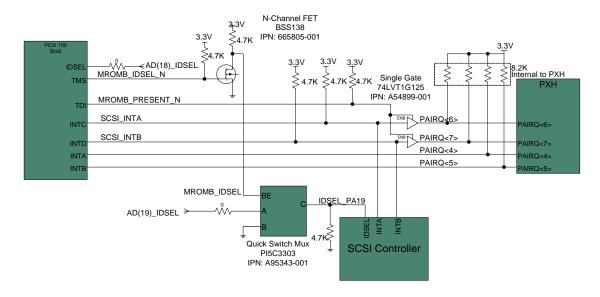

| Figure 13. MROMB Implementation                                   | 46  |

| Figure 14. Block Diagram of Platform Managment Architecture       | 92  |

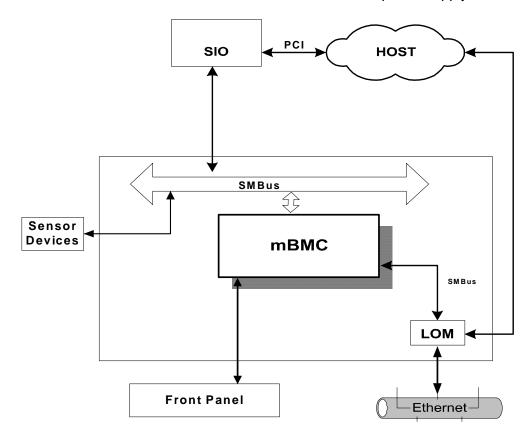

| Figure 15. mBMC in a Server Management System                     | 112 |

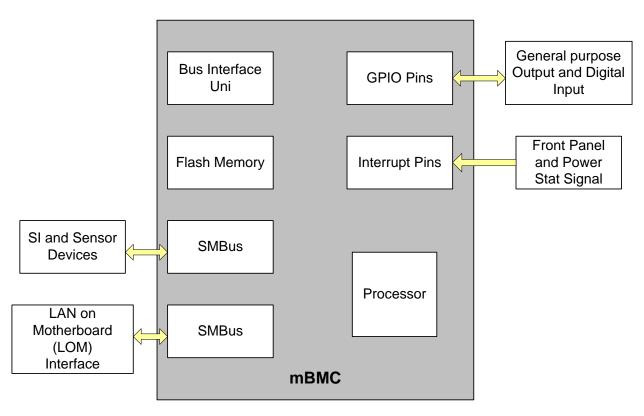

| Figure 16. External Interfaces to the mBMC                        | 113 |

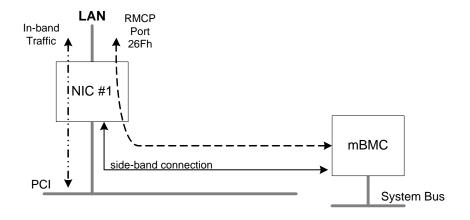

| Figure 17. IPMI-over-LAN                                          | 117 |

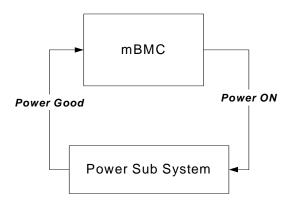

| Figure 18. Power Supply Control Signals                           | 124 |

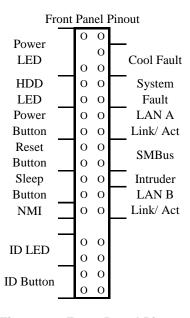

| Figure 19. Front Panel Pinout                                     | 143 |

| Figure 20. Jumper Locations                                       | 174 |

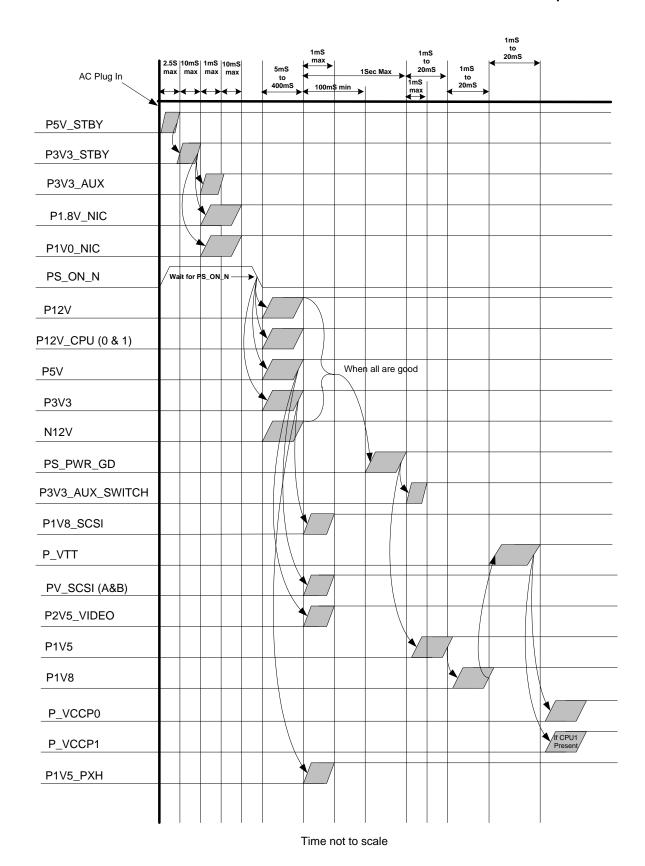

| Figure 21. Reset and PowerGood Timings                            | 182 |

| Figure 22. Intel® Server Board SE7520BD2 Power Sequencing Diagram | 183 |

# **List of Tables**

| Table 1. Processor Support Matrix                                               | 26 |

|---------------------------------------------------------------------------------|----|

| Table 2. Memory Bank Labels                                                     | 30 |

| Table 3. DDR266 Memory Population                                               | 32 |

| Table 4. DDR333 Memory Population                                               | 32 |

| Table 5. Supported DIMM Modules                                                 | 32 |

| Table 6. I <sup>2</sup> C Addresses for Memory Module SMB – DDR SKU's           | 37 |

| Table 7. I <sup>2</sup> C Addresses for Memory Module SMB – DDR2 SKU's          | 37 |

| Table 8. GPIO on the Intel® Server Board SE7520BD2                              | 41 |

| Table 9. Slot 6 PCI-X Pin-out                                                   | 43 |

| Table 10. Signal Description/Functionality                                      | 46 |

| Table 11. Quick Switch MUX Functionality                                        | 46 |

| Table 12. BIOS Feature Support                                                  | 50 |

| Table 13. BIOS Setup Utility Keyboard Commands                                  | 56 |

| Table 14. BIOS Setup, Main Menu Options                                         | 57 |

| Table 15. BIOS Setup, Advanced Menu Options                                     | 58 |

| Table 16. BIOS Setup, Processor Configuration Sub-menu Options                  | 59 |

| Table 17. BIOS Setup IDE Configuration Menu Options                             | 60 |

| Table 18. Mixed PATA-SATA Configuration with only Primary PATA                  | 61 |

| Table 19. BIOS Setup, IDE Device Configuration Sub-menu Selections              | 62 |

| Table 20. BIOS Setup, Floppy Configuration Sub-menu Selections                  | 63 |

| Table 21. BIOS Setup, Super I/O Configuration Sub-menu                          | 63 |

| Table 22. BIOS Setup, USB Configuration Sub-menu Selections                     | 64 |

| Table 23. BIOS Setup, USB Mass Storage Device Configuration Sub-menu Selections | 65 |

| Table 24. BIOS Setup, PCI Configuration Sub-menu Selections                     | 66 |

| Table 25. BIOS Setup, Memory Configuration Sub-menu Selections                  | 68 |

| Table 26. BIOS Setup, Boot Menu Selections                                      | 69 |

| Table 27. BIOS Setup, Boot Settings Configuration Sub-menu Selections           | 70 |

| Table 28. BIOS Setup, Boot Device Priority Sub-menu Selections                  | 70 |

| Table 29. BIOS Setup, Hard Disk Drive Sub-Menu Selections                       | 71 |

| Table 30. BIOS Setup, Removable Drives Sub-menu Selections                      | 71 |

| Table 31. BIOS Setup, CD/DVD Drives Sub-menu Selections                         | 71 |

| Table 32. BIOS Setup, Security Menu Options                                     | 72 |

| Table 33. BIOS Setup, Server Menu Selections                                    | 74 |

| Table 34. BIOS Setup, System Management Sub-menu Selections                        | 75  |

|------------------------------------------------------------------------------------|-----|

| Table 35. BIOS Setup, Serial Console Features Sub-menu Selections                  | 76  |

| Table 36. BIOS Setup, Event Log Configuration Sub-menu Selections                  | 77  |

| Table 37. BIOS Setup, Exit Menu Selections                                         | 77  |

| Table 38. ACPI Runtime Checkpoints                                                 | 87  |

| Table 39. Tiered Platform Management Feature Overview                              | 89  |

| Table 40. Power and Reset Control                                                  | 90  |

| Table 41. Secure Mode Button Actions                                               | 90  |

| Table 42. Memory RAS Feature Support by Server Management Tier                     | 91  |

| Table 43. mBMC Built-in Sensors                                                    | 99  |

| Table 44. Onboard Platform Instrumentaion using the mBMC                           | 100 |

| Table 45. Platform Instrumentation Sensors using the Intel® Management Module      | 103 |

| Table 46. Supported Channel Assigments                                             | 114 |

| Table 47. LAN Channel Capacity                                                     | 116 |

| Table48. LAN Channel Specifications                                                | 117 |

| Table 49. PEF Action Priorities                                                    | 121 |

| Table 50. mBMC Factory Default Event Filters                                       | 121 |

| Table 51. Power Control Initiators                                                 | 125 |

| Table 52. System Reset Sources and Actions                                         | 126 |

| Table 53. Chassis ID LEDs                                                          | 129 |

| Table 54. Fault/Status LED                                                         | 129 |

| Table 55. mBMC Built-in Sensors                                                    | 133 |

| Table 56. Intel® Server Board SE7520BD2 Platform Sensors for Essentials Management | 134 |

| Table 57. Front Panel Color Attributes                                             | 143 |

| Table 58. Error Codes and Messages                                                 | 148 |

| Table 59. Error Codes Sent to Management Module                                    | 149 |

| Table 60. POST Error Beep Codes                                                    | 150 |

| Table 61. Troubleshooting BIOS Beep Codes                                          | 150 |

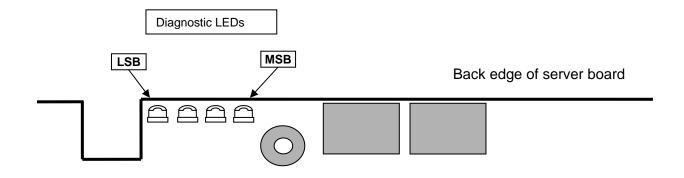

| Table 62. POST Progress Code LED Example                                           | 151 |

| Table 63. Memory Error Codes                                                       |     |

| Table 64. Memory Error Events                                                      | 155 |

| Table 65. Examples of Event Data Field Contents for Memory Errors                  | 156 |

| Table 66. PCI Error Events                                                         |     |

| Table 67. Examples of Event Data Field Contents for PCI Errors                     | 158 |

| Table 68. FRB-2 Error Events                                                       | 158 |

| Table 69. Examples of Event Data Field Contents for FRB-2 Errors | 159 |

|------------------------------------------------------------------|-----|

| Table 70. POST Code Checkpoints                                  | 159 |

| Table 71. Boot block Initialization Code Checkpoints             | 161 |

| Table 72. Boot Block Recovery Code Checkpoint                    | 162 |

| Table 73. Boot Block Recovery Beep Code                          | 163 |

| Table 74. DIM Code Checkpoints                                   | 164 |

| Table 75. Board Connector Matrix                                 | 169 |

| Table 76. Test Support Connector                                 | 169 |

| Table 77. OEM RMC 8-pin (Remote Management Card Support)         | 170 |

| Table 78. EPS12V 2x12 Connector                                  | 170 |

| Table 79. EPS12V 2x4 Connector                                   | 171 |

| Table 80. EPS12V 1x5 Connector                                   | 171 |

| Table 81. Primary IDE Connector                                  | 171 |

| Table 82. Front Panel Connector                                  | 172 |

| Table 83. USB Front Connector                                    | 172 |

| Table 84. USB Rear Connector                                     | 172 |

| Table 85. SATA Connector                                         | 173 |

| Table 86. Battery Holder                                         | 173 |

| Table 87. Piezo* Speaker                                         | 173 |

| Table 88. SCSI LED Connector                                     | 173 |

| Table 89. PLL Multiplier Selection Bit 0                         | 173 |

| Table 90. PLL Multiplier Selection Bit 1                         |     |

| Table 91. CPU 1 and CPU 2 3-pin Fans                             | 173 |

| Table 92. CPU 1 and CPU 2 4-pin Fans for DDR2 Boards             | 173 |

| Table 93. System Fan 1 and System Fan 2 (3-pin plus 2-pin)       | 174 |

| Table 94. System Fan 3 and System Fan 4                          | 174 |

| Table 95. System Fan 5 and System Fan 6                          | 174 |

| Table 96. BIOS Bank Selection Jumper                             | 175 |

| Table 97. BIOS Recovery Jumper Setting                           | 175 |

| Table 98. Password Clear Jumper Setting                          | 175 |

| Table 99. CMOS Clear Jumper Setting                              | 175 |

| Table 100. Server board Power Budget                             | 178 |

| Table 101. Intel® Server Board SE7520BD2 Voltage Table           | 180 |

## 1. Introduction

## 1.1 Purpose

This Intel® Server Board SE7520BD2 Technical Product Specification (TPS) provides technical details on the functional architecture and feature set of the server board.

### 1.2 Audience

This document is intended for technical personnel requiring a technical overview of the Server Board SE7520BD2. Familiarity with the personal computer, Intel® server architecture, Intel® processor architecture, memory technologies and the Peripheral Component Interconnect (PCI) local bus architecture is assumed.

#### 1.3 Document Outline

This document is composed of the following chapters:

- Chapter 1: Introduction

- Chapter 2: Product Overview

- Chapter 3: Board Architecture

- Chapter 4: BIOS

- Chapter 5: Platform Management Architecture

- Chapter 6: Error Reporting and Handling

- Chapter 7: Connector Pin-outs and Jumper Blocks

- Chapter 8: Environmental Specifications

- Chapter 9: Other Useful Information

#### 1.4 Additional Technical Documentation

For additional information on the Server Board SE7520BD2, consult the following documents:

- Intel® Server Board SE7250BD2 with DDR Memory Specification Update

- Intel® Server Board SE7250BD2 with DDR2 Memory Specification Update

- Intel® Server Board SE7520BD2 Tested Hardware and Operating System List

- Intel® Server Chassis SC5300 Technical Product Specification

- Intel® Server Chassis SC5300 Chassis Power Supply Specification

## 1.5 Board Usage Disclaimer

Intel Corporation server baseboards contain a number of high-density VLSI and power delivery components that need adequate airflow to cool. Intel's own chassis are designed and tested to meet the intended thermal requirements of these components when the fully integrated system is used together. It is the responsibility of the system integrator that chooses not to use Intel developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of airflow required for their specific application and environmental conditions. Intel Corporation cannot be held responsible if components fail or the server board does not operate correctly when used outside any of its published operating or non-operating limits.

## 2. Product Overview

The Server Board SE7520BD2 is an Intel® Architecture (IA) 32-based server board capable of supporting dual Intel® Xeon™ processors. Board partitioning is optimized for general purpose (GP)-pedestal design. The platform is based on the Intel® E7520 chipset and incorporates several new high-speed buses and signaling architectures.

#### 2.1 Server Board Feature Set

The Server Board SE7520BD2 supports the following feature set:

- IA-32 server platform, based on the Intel E7520 chipset

- Dual 800MT/s Intel® Xeon™ processors 200MHz FSB

- Six DDR Stacked Registered DIMM memory sockets supporting ECC memory (two memory channels with three DIMMs per channel) or

- Eight DDR2 Stacked Registered DIMM memory sockets supporting ECC memory (two memory channels with four DIMMs per channel)

- Supports Intel® 82801ER I/O Controller Hub (ICH5R), interfaced with an Intel® E7520 Memory Controller Hub (MCH) via Hub Interface 1.5

- Supports PXH PCI-X\* bridge, interfaced with the MCH via x8 PCI Express\* Interface PCI-X 2.0 133MHz slot

- Two PCI-X 1.0 100MHz slots

- One PCI Express x8 slot (unpopulated on product code SE7520BD2V)

- One PCI Express x8 slot (actual x4 plumbing to a x8 physical connector)

- Marvell\* Yukon 88E8050 10/100/1000 LAN, interfaces with the MCH via x1 PCI Express interface

- Intel® 82541PI supporting 10/100/1000 LAN, interface with the ICH5 via PCI 32/33 bus

- LPC server I/O

- One 5V PCI 32/33 slot

- Onboard dual-channel Ultra320 SCSI controller, interfaces with the PXH via 100MHz

Mode 1 PCI-X bus

- Onboard single-channel Ultra320 SCSI controller (SCSI connector B is unpopulated on product codes SE7520BD2V and SE7520BD2VD2).

- Onboard PCI ATI\* RAGE\* XL video controller

- Three USB 2.0 ports at the rear (only on product codes SE7520BD2 and SE7520BD2SCSI)

٥r

Two USB 2.0 ports at the rear (product code SE7520BD2V and all DDR2 product codes)

- Two USB 2.0 ports at the front

- Dual SATA Interface

- Single ATA-100 interface

- Two serial ports

- One back panel connector

- One front panel connector

- One floppy connector

- Redundant fan speed control for the Intel® Server Chassis SC5300, LX version.

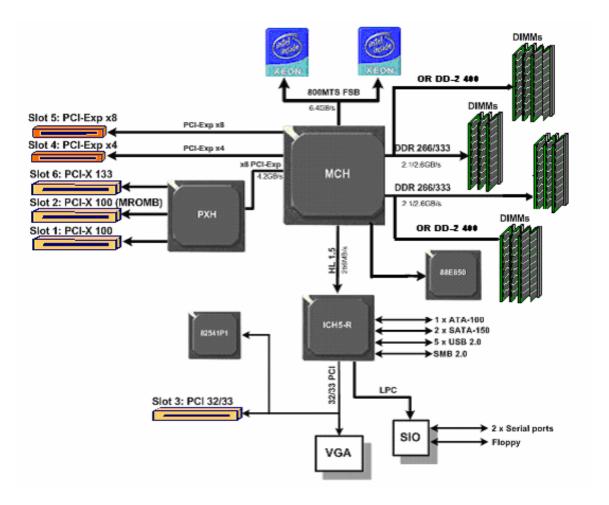

## 2.2 DDR Server Board

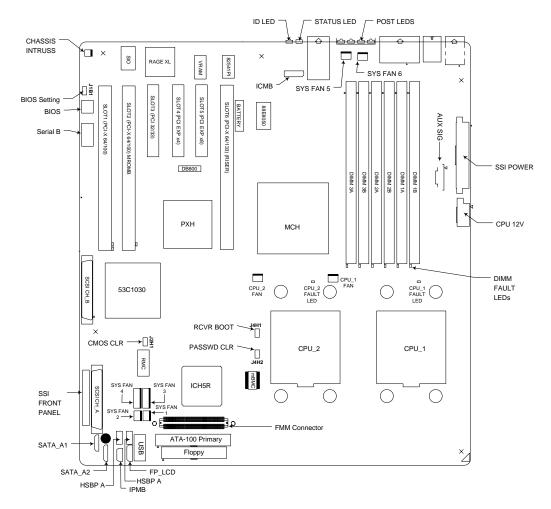

The following figure provides a high-level illustration of the Server Board SE7520BD2.with DDR memory (product codes SE7520BD2, SE7520VD2SCSI, SE7520BD2V).

Figure 1. Intel® Server Board SE7520BD2 with DDR Memory

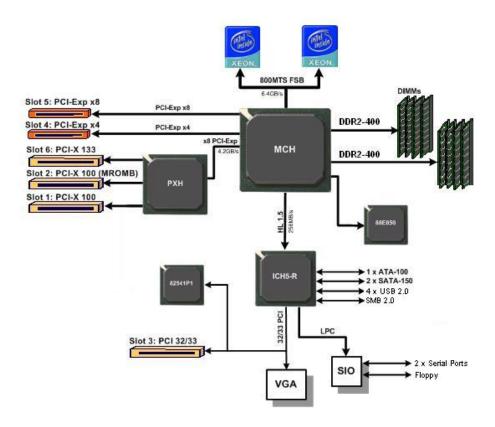

## 2.3 DDR2 Server Board

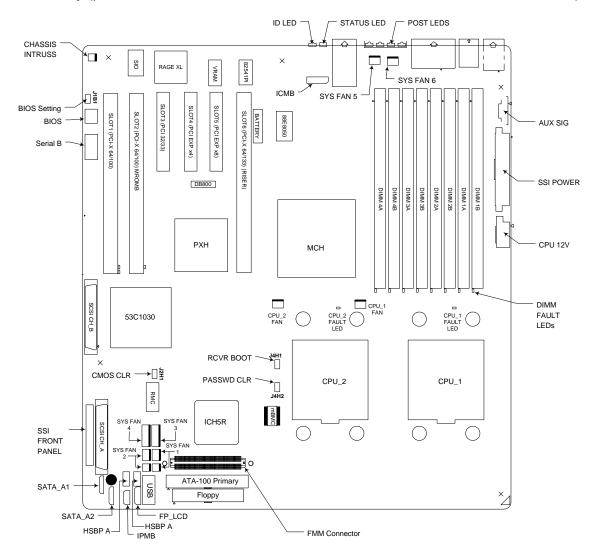

The following figure provides a high-level illustration of the Server Board SE7520BD2 with DDR2 memory (product codes SE7520BD2SATAD2, SE7520VD2SCSID2, SE7520BD2V2).

Figure 2. Intel® Server Board SE7520BD2 with DDR2 Memory

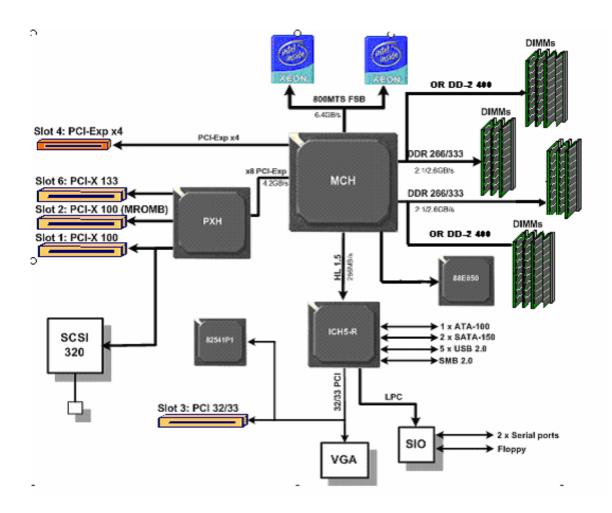

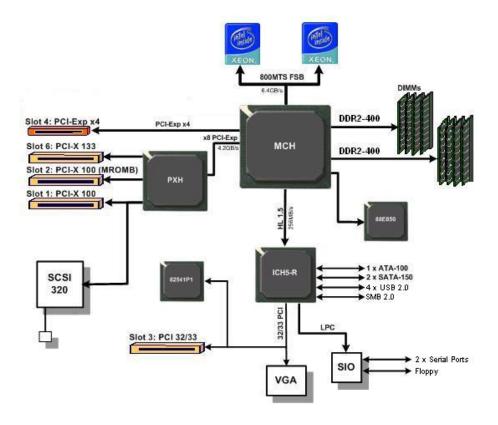

## 2.4 Server Board Layout

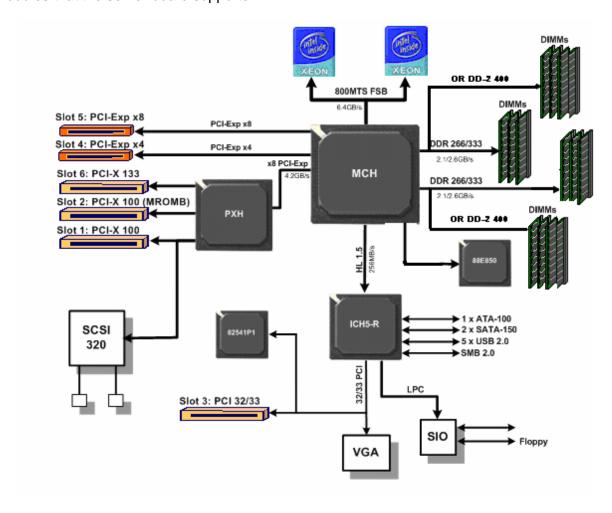

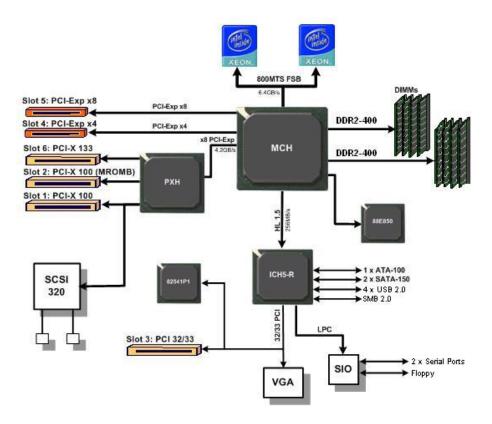

Figure 3 illustrates the functional blocks of the Server Board SE7520BD2 and the plug-in modules that the server board supports.

Figure 3. Product Code SE7520BD2SCSI System Block Diagram

Figure 4. Product Code SE7520BD2SCSID2 System Block Diagram

Figure 5. Product Code SE7520BD2 System Block Diagram

Figure 6. Product Code SE7520BD2SATAD2 System Block Diagram

Figure 7. Product Code SE7520BD2V System Block Diagram

Figure 8. Intel® Server Board SE7520BD2VD2 System Block Diagram

## 2.5 Identifying the Version of an Intel® Server Board

The version of an Intel server board can be determined by decoding the last three digits of the board part number.

Example: C44686-703 The number following the "-" is as follows:

- 7 = Fabrication (FAB) Number

- 03 = Revision 3.

The board part number can be found on the server board. The board part number can also be determined by using Intel® Server Management or by checking the System Management Submenu in BIOS Setup (see Section 3.2.8.1).

## 2.6 Chipset Overview

The architecture of the Server Board SE7520BD2 is designed around the Intel® E7520 chipset. The chipset consists of three components, which together are responsible for providing the interface between all major sub-systems found on the server board, including the processor, memory, and I/O sub-systems. These three components are:

- Memory Controller Hub (MCH)

- I/O Controller Hub (ICH5R)

- Intel® 6700PXH 64-bit Hub (PXH)

The MCH is configured to support the following interfaces:

- CPU Front Side Bus at 200MHz operation using AGTL+ (Assisted Gunner Transceiver Logic) signaling, 4x 64 bit data bus at 6.4GB/s.

- Dual memory channels supporting registered 72-bit data ECC DIMMs for DDR266/333 or DDR2-400. DDR bandwidth of 2.13/2.6GB/s per channel giving 4.26GB/s for both.

- Three PCI Express x8 interfaces with aggregate bandwidth of 4GB/s interfaces to PXH and other onboard devices. Each of these interfaces can be configured as two independent x4 interfaces.

- Hub Interface 1.5, 8 bits, 66MHz, 266MB/s interface to the ICH5R.

- Debug support through XDP (Extended Debug Port) connector.

- RASUM support through memory features and SMBus debug port access.

#### 2.6.1 Memory Controller Hub (MCH)

The MCH uses a 1077-ball FC-BGA package in which it integrates four main functions:

- Front Side Bus

- Memory controller

- PCI Express controller

- Hub Link controller

#### 2.6.2 Front Side Bus (FSB)

The Intel E7520 MCH supports either single or dual population of the Intel® Xeon™ processor. The MCH supports a base system bus frequency of 200MHz. The address and request interface is double-pumped at 400MHz while the 64-bit data interface (+ parity) is quad-pumped to 800MHz. This provides a matched system bus address and data bandwidths of 6.4GB/sec.

The newest generation of Intel® Xeon™ processors for dual-processor (DP) servers and workstations is based on the Intel® NetBurst™ microarchitecture. These processors follow the Intel® Xeon™ processor line, and are similarly backward compatible, while adding several performance enhancing architectural and microarchitectural features. They also have larger L2 caches than the previous generation.

## 2.6.3 MCH Memory Sub-System

#### 2.6.3.1 DDR MCH Memory Sub-System

The MCH provides an integrated memory controller for direct connection to two channels of registered DDR266 or DDR333 memory (stacked or unstacked). The peak theoretical memory data bandwidth using DDR266 technology is 4.26GB/s. The peak theoretical memory data bandwidth using DDR333 technology is 5.33GB/S.

When both DDR channels are populated and operating, they function in lock-step mode. For the Intel E7520 MCH, the maximum supported DDR266 memory size is 32GB. However, the Server Board SE7520BD2 has six DIMM sites, which limits this maximum memory size to 24GB. The maximum supported memory for DDR333 is 16GB.

#### 2.6.3.2 DDR2 MCH Memory Sub-System

The MCH provides an integrated memory controller for direct connection to two channels of registered DDR2-400 memory (stacked or unstacked). The peak theoretical memory data bandwidth using DDR2-400 technology is 6.4GB/s.

When both memory channels are populated and operating, they function in lock-step mode. On the Intel® Server Board SE7520BD2, the maximum supported DDR2-400 memory configuration is 16GB.

## 2.6.3.3 DDR and DDR2 MCH Memory Sub-System RASM Features

The Intel E7520 MCH memory interface provides several RASUM (Reliability, Availability, Serviceability, Usability and Manageability) features, including:

- Memory mirroring that allows for two copies of all data in the memory subsystem (one on each channel) to be maintained.

- Memory sparing that allows for one DIMM per channel to be held in reserve and brought on-line if another DIMM in the channel becomes defective. DIMM sparing and memory mirroring are mutually exclusive of one another.

- Hardware periodic memory scrubbing, including demand scrub support.

- Retry on uncorrectable memory errors.

- Intel® x4 Single Device Data Correction (SDDC) for memory error detection and correction of any number of bit failures in a single x4 memory device.

## 2.6.4 PCI Express\*

The Intel E7520 MCH is the first Intel chipset to support the PCI Express\* high-speed serial I/O interface for superior I/O bandwidth. The scalable PCI Express interface complies with the *PCI Express\* Interface Specification, Rev 1.0a.* The MCH provide three x8 PCI Express interfaces, each with a maximum theoretical bandwidth of 4GB/s.

The Intel E7520 MCH is a root class component as defined in the *PCI Express Interface Specification, Rev 1.0a*. The PCI Express interfaces of the MCH support connection to a variety of bridges and devices compliant with the same revision of the *PCI Express Interface Specification, Rev 1.0a*. See the *Intel® Server Board SE7520BD2 Tested Hardware and OS List* for add-in cards tested with this server board.

#### 2.6.5 **Hub Interface**

The MCH interfaces with the Intel® 82801ER I/O Controller Hub 5-R (ICH5R) via a dedicated Hub Interface supporting a peak bandwidth of 266MB/s using a x4 base clock of 66MHz.

#### 2.7 **Processor Subsystem**

The Server Board SE7520BD2 is designed to support one or two Intel® Xeon™ processors with frequencies starting at 2.8 GHz. These newer generation processors use 90-nanometer technology and an 800MHz front side bus.

**Note**: Previous generations of the Intel® Xeon™ processor are not supported on the Server Board SE7520BD2.

When two processors are installed, both must be of identical revision, core voltage, cache size, and bus/core speed. When only one processor is installed, it must be in the socket labeled "CPU1" and the other socket must be empty. The support circuitry on the server board consists of the following:

- Dual 604-pin zero insertion force (ZIF) processor sockets

- Processor host bus AGTL+ support circuitry

- Reset configuration logic

- Processor module presence detection logic

- BSEL detection capabilities

- CPU signal level translation

- CEK CPU retention support

**Table 1. Processor Support Matrix**

| <b>Processor Family</b> | Package Type | FSB Frequency | Technology | Frequency | Cache Size | Support          |

|-------------------------|--------------|---------------|------------|-----------|------------|------------------|

| Intel® Xeon™            | FC-mPGA4     | 667MHz        |            | 2.8 GHz   | 1024KB     | No               |

| Intel Xeon              | FC-mPGA4     | 800MHz        | 90 nM      | 2.8 GHz   | 1024KB     | Yes              |

| Intel Xeon              | FC-mPGA4     | 800MHz        | 90 nM      | 3.0 GHz   | 1024KB     | Yes              |

| Intel Xeon              | FC-mPGA4     | 800MHz        | 90 nM      | 3.2 GHz   | 1024KB     | Yes              |

| Intel Xeon              | FC-mPGA4     | 800MHz        | 90 nM      | 3.4 GHz   | 1024KB     | Yes              |

| Intel Xeon              | FC-mPGA4     | 800MHz        | 90 nM      | 3.6 GHz   | 1024KB     | Yes              |

| Intel Xeon              | FC-mPGA4     | 800MHz        | 90 nM      | 3.0 GHz   | 2048KB     | Yes <sup>1</sup> |

| Intel Xeon              | FC-mPGA4     | 800MHz        | 90 nM      | 3.2 GHz   | 2048KB     | Yes <sup>1</sup> |

| Intel Xeon              | FC-mPGA4     | 800MHz        | 90 nM      | 3.4 GHz   | 2048KB     | Yes <sup>1</sup> |

| Intel Xeon              | FC-mPGA4     | 800MHz        | 90 nM      | 3.6 GHz   | 2048KB     | Yes 1            |

#### Note:

DDR boards need BIOS P07 or greater to support the Intel® Xeon™ processor with 1. 2MB L2 cache.

The Server Board SE7520BD2 is designed to provide up to 120A per processor. Processors with higher current requirements are not supported.

## 2.7.1.1 Mixed Processor Steppings

For optimum system performance, only identical processors should be installed in a system. Processor steppings can be mixed in a system if there is no more than a 1-stepping difference in all processors installed. If the installed processors are more than 1-stepping apart, an error (8080 through 8183) is logged in the System Event Log (SEL) and an error (01298000 through 01298003) is reported to the Management Module. Acceptable mixed steppings are not reported as errors.

#### 2.7.1.2 Mixed Processor Models

Processor models cannot be mixed in a system. If this condition is detected, an error (8196) is logged in the SEL.

#### 2.7.1.3 Mixed Processor Families

Processor families cannot be mixed in a system. If this condition is detected, an error (8194) is logged in the SEL.

#### 2.7.1.4 Mixed Processor Cache Sizes

If the installed processors have mixed cache sizes, error 8192 will be logged in the SEL and error 196 is reported to the Management Module. The size of all cache levels must match between all installed processors. Mixed cache processors are not supported.

#### **2.7.1.5** Microcode

IA-32 processors have the capability of correcting specific errata through the loading of an Intel-supplied data block (microcode update). The BIOS is responsible for storing the update in nonvolatile memory and loading it into each processor during POST. The BIOS performs all the recommended update signature verification prior to storing the update in the Flash.

#### 2.7.1.6 Processor Cache

The BIOS enables all levels of processor cache as early as possible during POST. There are no user options to modify the cache configuration, size or policies. All detected cache sizes are reported in the SMBIOS Type 7 structures. The largest and highest level cache detected is reported in BIOS Setup.

## 2.7.1.7 Hyper-Threading Technology

Intel® Xeon<sup>™</sup> processors support Hyper-Threading Technology. The BIOS detects processors that support this feature and enables the feature during POST. BIOS Setup provides an option to selectively enable or disable this feature. The default behavior is enabled.

The BIOS creates additional entries in the ACPI MP tables to describe the virtual processors. The SMBIOS Type 4 structure shows only the physical processors installed.

## 2.7.2 Multiple Processor Initialization

IA32 processors have a microcode-based BSP-arbitration protocol. On reset, all of the processors compete to become the bootstrap processor (BSP). If a serious error is detected during a Built-in Self-Test (BIST), that processor will not participate in the initialization protocol. A single processor that successfully passes BIST is automatically selected by the hardware as the BSP and starts executing from the reset vector (F000:FFF0h). A processor that does not perform the role of BSP is referred to as an application processor (AP).

The BSP is responsible for executing the BIOS power-on self-test (POST) and preparing the machine to boot the operating system. At boot time, the system is in virtual wire mode and the BSP alone is programmed to accept local interrupts (INTR driven by programmable interrupt controller (PIC) and non-maskable interrupt (NMI)). For single processor configurations, the system is put in the virtual wire mode, which uses the local APIC of the processor.

As a part of the boot process, the BSP wakes each AP. When awakened, an AP programs its Memory Type Range Registers (MTRRs) to be identical to those of the BSP. All APs execute a halt instruction with their local interrupts disabled. The System Management Mode (SMM) handler expects all processors to respond to an SMI. If the BSP determines that an AP exists that is a lower-featured processor or that has a lower value returned by the CPUID function, the BSP will switch to the lowest-featured processor in the system.

#### 2.7.3 Processor VRD

The Server Board SE7520BD2 has two Voltage Regulator Downs (VRDs) providing the appropriate voltages to the installed processors. Each VRD is compliant with the VRD 10.1 specification and is designed to support current and next generation Intel® Xeon™ processors that require up to a sustained maximum of 105A and peak support of 120A.

The server board supports the Flexible MotherBoard (FMB) for all Intel® Xeon™ processors with respect to current requirements and processor speed requirements. FMB is an estimation of the maximum values the processors will have over their lifetime. The value is only an estimate and actual specifications for future processors may differ. Currently, the demand per FMB is a sustained maximum of 105 Amps and a peak support of 120 Amps.

## 2.7.4 Reset Configuration Logic

The BIOS determines the processor stepping, cache size, etc., through the CPUID instruction.

All processors in the system must operate at the same frequency, have the same cache size, and have the same voltage identification (VID). No mixing of product families is supported. Processors run at a fixed speed and cannot be programmed to operate at a lower or higher speed.

#### 2.7.5 Processor Module Presence Detection

Logic is provided on the server board to detect the presence and identity of installed processors. In dual-processor configurations, the onboard mini Baseboard Management Controller (mBMC) must read the processor VID bits for each processor before turning on the VRD. If the VIDs of the two processors are not identical, then the BMC will not turn on the VRD.

The following circuit is designed to ensure that three criteria are met prior to enabling the embedded VRD:

- Ensure that in a UP configuration, the end agent CPU (P1) is installed

- Disable older-generation Intel® Xeon™ processors from running in the system. This

prevents possible damage to the MCH

- Ensure in a DP configuration that both processors support the same FSB frequency

#### 2.7.6 GTL2006\*

The GTL2006\* is a 13-bit translator designed for 3.3V to GTL/GTL+ translations to the system bus. The translator incorporates all the level shifting and logic functions required to interface between the processor subsystem and the rest of the system.

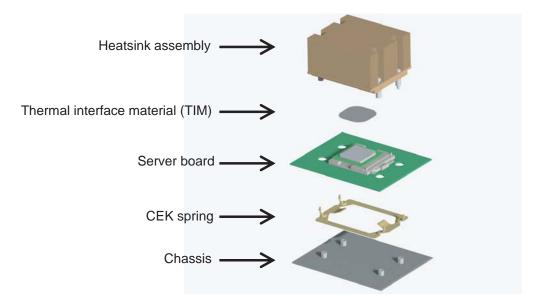

## 2.7.7 Common Enabling Kit (CEK) Design Support

The server board has been designed to comply with Intel's Common Enabling Kit (CEK) processor mounting and heatsink retention solution. The server board as shipped from Intel's factory will ship with a CEK spring snapped onto the bottom side of the board beneath each processor socket. The CEK spring is removable allowing for the use of non-Intel heatsink retention solutions.

#### 2.7.8 Process fan Variable Speed Control

The Intel® Xeon™ boxed processor with 2MB L2 cache with active heatsink solution ships with a heatsink fan that has a 4-pin harness. See the figure below. All DDR2 versions of the Server Board SE7520BD2 ship with the 4-pin CPU fan headers. This enables the fan speed to be controlled to reduce system acoustics when an active heatsink solution is used.

DDR versions of the Server Board SE7520BD2 ship with the 3-pin CPU fan header. Any change to this will be communicated with a Product Change Notification (PCN). Both the Intel® Xeon™ boxed processor with 2MB L2 cache and the Intel® Xeon™ boxed processor with 1MB L2

cache active heatsink solutions can be used of both 3-pin and 4-pin CPU fan header but there will be no variable fan speed control when a 4-pin fan is used on a 3-pin header.

Figure 9. 3-pin and 4-pin Heatsink Fan Harnesses

## 2.8 Memory Sub-System

The DDR versions of the Server Board SE7520BD2 support both DDR266 and DDR333 memory. For these server boards, there are two DDR channels (channels A and B) from the MCH, each supporting three DIMM slots.

The DDR2 versions of the server board support DDR2-400 memory. For these server boards, there are two DDR2 channels (channels A and B) from the MCH, each supporting four DIMM slots.

The channels for each version of the server board can be configured to operate in dual-channel or single-channel mode. The MCH chipset requirements dictate that certain memory population rules have to be followed depending on the type of memory and the number of loads per memory channel.

The DDR server boards automatically detect the appropriate speed for the memory bus based on these rules, and sets the bus to 266 or 333 MT/s. DDR DIMMs are described as single-rank (s/r) or dual-rank (d/r). To equate loads and DIMM rank, the MCH considers a single-rank DIMM to be one load and a dual-rank DIMM to be two loads.

DIMM population starts from slot 1, the slot that is furthest from the MCH. The following table lists the numbering of the DIMM slots. The silkscreen labels are located next to each DIMM connector.

**Table 2. Memory Bank Labels**

| Intel® Server Board SE7520BD2<br>Memory DIMM | Bank |

|----------------------------------------------|------|

| J7B1 (DIMM 3A), J7B2 (DIMM 3B)               | 3    |

| J7B3 (DIMM 2A), J8B1 (DIMM 2B)               | 2    |

| J8B2 (DIMM 1A), J8B3 (DIMM 1B)               | 1    |

## 2.8.1 DDR266 Memory

For a DDR266 installation, six loads per channel are allowed on the Server Board SE7520BD2, although the Intel E7520 chipset supports eight loads. This means that for both single- and dual-rank DIMMs, the test setups previously listed can be populated with no further considerations. The test setups assume dual-channel operation. The maximum memory that can be populated is 24GB, after 4GB DIMMs are available.

#### 2.8.2 DDR333 Memory

For a DDR333 installation, four loads per memory channel are allowed. This is a limitation of the data duty cycle of the higher frequency. This means that for both single/dual-rank DIMMs, the test setups previously listed must be populated according to the following table for each memory channel. The test setups assume dual-channel operation. Empty slots are also noted. The maximum memory that can be populated is 16GB, after 4GB DIMMs are available.

TSOP DDR333 DIMMs are not supported due to memory timing violations. Based on this, the Server Board SE7520BD2 supports only DDR333 memory in the BGA package.

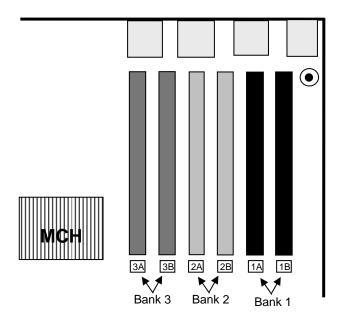

## 2.8.3 DDR266 and DDR333 Memory Population

The following diagram identifies the memory bank locations on the server board.

Figure 10. DDR DIMM Socket Configuration

**Table 3. DDR266 Memory Population**

| DIMM Configuration             | DIMM 1      | DIMM 2      | DIMM 3      |

|--------------------------------|-------------|-------------|-------------|

| One single-rank                | Single-rank | Empty       | Empty       |

| One dual-rank                  | Dual-rank   | Empty       | Empty       |

| Two single-rank                | Single-rank | Single-rank | Empty       |

| One dual-rank, One single-rank | Single-rank | Dual-rank   | Empty       |

| Two dual-rank                  | Dual-rank   | Dual-rank   | Empty       |

| 3 single-rank                  | Single-rank | Single-rank | Single-rank |

| One dual-rank, Two single-rank | Single-rank | Single-rank | Dual-rank   |

| Two dual-rank, One single-rank | Single-rank | Dual-rank   | Dual-rank   |

| Three dual-rank                | Dual-rank   | Dual-rank   | Dual-rank   |

**Table 4. DDR333 Memory Population**

| DIMM Configuration             | DIMM 1      | DIMM 2      | DIMM 3      |

|--------------------------------|-------------|-------------|-------------|

| One single-rank                | Single-rank | Empty       | Empty       |

| One dual-rank                  | Dual-rank   | Empty       | Empty       |

| Two single-rank                | Single-rank | Single-rank | Empty       |

| One dual-rank, one single-rank | Single-rank | Dual-rank   | Empty       |

| Two dual-rank                  | Dual-rank   | Dual-rank   | Empty       |

| Three single-rank              | Single-rank | Single-rank | Single-rank |

## 2.8.4 DDR2-400 Memory

DDR2 versions of the Server Board SE7520BD2 support four single-ranked registered DDR2-400 DIMMs per channel, which provides a total of eight DIMMs. The maximum memory capacity supported is 16GB using eight modules of 1 Gbit DRAM technology devices.

**Table 5. Supported DIMM Modules**

| Technology | Organization   | DRAM Components / DIMM | Row / Column<br>Address Bits |

|------------|----------------|------------------------|------------------------------|

| 128Mb      | 4M X 8 X 4bks  | 8                      | 12/10                        |

|            | 8M X 4 X 4bks  | 16                     | 12/11                        |

| 256Mb      | 8M X 8 X 4bks  | 8                      | 13/10                        |

|            | 16M X 4 X 4bks | 16                     | 13/11                        |

| 512Mb      | 16M X 8 X 4bks | 8                      | 14/10                        |

|            | 32M X 4 X 4bks | 16                     | 14/11                        |

| 1Gb        | 32M X 8 X 8bks | 8                      | 14/10                        |

|            | 64M X 4 X 8bks | 16                     | 14/11                        |

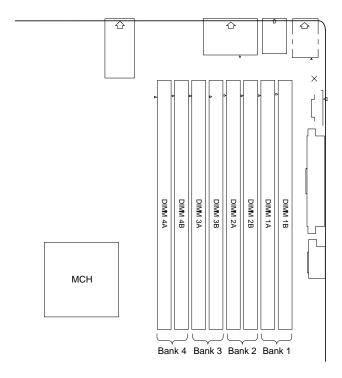

## 2.8.5 DDR2 DIMM Population Rules and Supported Configurations

The server board contains four banks of DIMMs: memory Bank 1 through memory Bank 4. Memory Bank 1, with DIMM sockets 1B and 1A, is located closest to the edge of the board. Moving in from the edge on the board are sockets for banks 2, 3, and 4 in order. Sockets associated with any given bank are located next to each other.

Figure 11. DIMM Socket Configuration

DIMM and memory configurations must adhere to the following:

- DDR2-400 registered ECC DIMM modules

- DIMM organization: x72 ECC

- Pin count: 240 pins

- DIMM capacity: 256MB, 512MB, 1GB, 2GB, 4GB DIMMs using current SDRAM densities

- Support up to 16GB of system memory capacity

- Support a maximum of four ranks per channel<sup>1</sup>

- Serial PD: JEDEC Rev 2.0

- Voltage options: 1.8 V (VDD/VDDQ)

- Interface: SSTL2

<sup>&</sup>lt;sup>1</sup> To populate eight DIMM modules on the board, all DIMMs must be single-rank. See the DIMM manufacturer specification to determine the number of ranks on the specific DIMM intended to be used.

- Two DIMMs must be populated in a bank for a x144 wide memory data path

- DIMMs must be populated beginning with the socket furthest away from the MCH (DIMM 1B and DIMM 1A)

- DIMMs must be identical within the same bank. For example, the DIMM in socket DIMM 1A must be identical to the DIMM in socket DIMM 1B)

## 2.8.6 Single-Channel Operation

The Server Board SE7520BD2 supports single-channel DIMM operation. This is where one DIMM is populated in slot 1 of either memory channel A or B. Population in other slots is not supported. The minimal size of memory that will be considered for this testing is 128MB. Single channel DIMM setups are not part of the test setups listed for the qualification process; however, they will be tested to ensure their functionality during all phases of the project.

#### 2.8.7 ECC

The ECC used for DRAM provides Intel® SDDC x4 technology for x4 SDRAMs. DRAMs that are x8 use the same algorithm but will not have Intel® SDDC x4 technology, since at most only four bits can be corrected with this ECC.

The method provides more ECC bits so each ECC word can correct more than a single-bit failure. This is possible because different mathematical algorithms provide multiple-bit correction with the right number of data bits and ECC bits. For example, a 144-bit ECC word that consists of 128 data bits and 16 ECC bits can be used to correct up to 4-bit errors within certain bit fields of data. These four bits must be adjacent, not random. Even though the ratio of the ECC bits to data bits is the same as the previous example (16/128 vs. 8/64), the longer ECC word allows for a correction and detection algorithm that is more efficient.

#### 2.8.7.1 DIMM Sparing Function

To increase fault tolerance, the MCH includes specialized hardware to support fail-over to a spare DIMM device in the event that a primary DIMM in use exceeds a specified threshold of runtime errors. One of the DIMMs installed per channel will not be used, but is kept in reserve. In the event of significant failures in a particular DIMM, the failing DIMM and its corresponding partner in the other channel (if applicable), will, over time, have its data copied over to the DIMM(s) held in reserve. When all the data has been copied to the reserve DIMM, the reserve DIMM(s) are put into service and the failing DIMM is removed from service. Only one sparing cycle is supported. If this feature is not enabled, then all DIMMs will be visible in normal address space.

Hardware additions for this feature include the implementation of a tracking register per DIMM to maintain a history of error occurrences, and a programmable register to hold the fail-over error threshold level. The operational model is straightforward: set the fail-over threshold register to a non-zero value to enable the feature, and if the count of errors on any DIMM exceeds that value, fail-over begins.

The tracking registers themselves are implemented in a way that they do not contain an absolute cumulative count of all errors since power-on. Instead, they contain an aggregate count of the number of errors received over a running time period. The rate for this is selectable by a DIMM software algorithm. It is possible to set the threshold to a value that will never be

reached by a "healthy" memory subsystem experiencing the rate of errors expected for the size and type of memory devices in use.

The fail-over mechanism is slightly more complex. Once fail-over has been initiated the MCH must execute every write twice; once to the primary DIMM, and once to the spare. (This requires that the spare DIMM be at least the size of the largest primary DIMM in use.) The MCH will also begin tracking the progress of its built-in memory scrub engine. Once the scrub engine has covered every location in the primary DIMM, the duplicate write function will have copied every data location to the spare. At that point, the MCH can switch the spare into primary use, and take the failing DIMM off-line.

This mechanism requires no additional software support until the threshold has been triggered to request a data copy because it is programmed in BIOS. Hardware detects the threshold initiating fail-over, and hardware escalates the occurrence of the event as directed (signal an SMI, generate an interrupt, or wait to be discovered via polling).

A software routine must respond to the threshold detection and select a victim DIMM if multiple DIMMs have crossed the threshold prior to sparing invocation. Software must also initiate the memory copy.

Hardware isolates the "failed" DIMM once the copy has completed. The data copy is accomplished by address aliasing within the DDR control interface, thus it does not require reprogramming of the DRAM row boundary (DRB) registers, nor does it require notification to the operating system that anything has occurred in memory.

The memory mirroring feature and DIMM sparing are exclusive, only one may be activated during initialization. The selected feature must remain enabled until the next power-cycle. There is no provision in hardware to switch from one feature to the other without rebooting, nor is there a provision to "back out" of a feature once enabled without a full reboot.

#### 2.8.7.2 Memory Mirroring

Memory mirroring provides a way for hardware to maintain two copies of all data in the memory subsystem. This means a hardware failure or uncorrectable error is no longer fatal to the system. When an uncorrectable error is encountered during normal operation, hardware retrieves the "mirror" copy of the corrupted data. No system failure occurs unless both the primary and mirrored copies of the same data are corrupt simultaneously. This is statistically very unlikely.

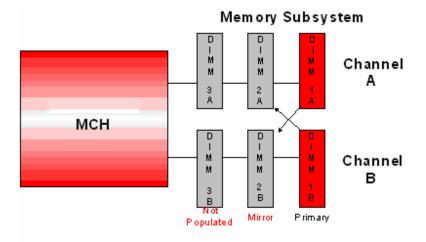

Mirroring is supported on dual-channel DIMM populations symmetric across both channels and within each channel. As seen in the following figure, potential mirroring pairs are DIMM 1A with DIMM 2B, or DIMM 1B with DIMM 2A. As a result, on the Server Board SE7520BD2 there are two supported configurations for memory mirroring:

• Four-DIMM population of completely identical devices (two per channel). DIMMs labeled 1A, 2A, 1B and 2B must be identical.

Figure 12. Memory Subsystem

These symmetry requirements are a result of the hardware mechanism for maintaining two copies of all main memory data while ensuring that each channel has a full copy of all data in preparation for fail-down to single-channel operation. Every write to memory is issued twice, once to the primary location and once to the mirror location. The data interleaved across the channel pair are swapped for the second write (1A is a copy of 2B, 1B is a copy of 2A, and so on.). The resulting memory image has two full copies of all data, with a complete copy available on each channel.

Hardware in the MCH tracks which DIMM slots are primaries, and which are mirrors, such that data may be internally realigned to correctly reassemble cache lines regardless of which copy is retrieved. There are four distinct cases for retrieval of the even and odd chunks of a cache-line of data:

- Interleaved dual-channel read to the primary DIMM with "even" data on channel A

- Interleaved dual-channel read to the mirror DIMM with "even" data on channel B

- Non-interleaved single-channel read pair to channel A with "even" data on the primary DIMM

- Non-interleaved single-channel read pair to channel B with "even" data on the mirror DIMM

When mirroring is enabled by the MCH configuration, the memory subsystem maintains two copies of all data as described above, and will retrieve requested data from either primary or mirror based on the state of system address bit 15 (SA[15]). BIOS may toggle which SA[15] polarity selects primary verses mirror via a configuration register bit setting. SA[15] was chosen because it is the lowest system address bit that is always used to select the memory row address across all DRAM densities and technologies supported by the MCH. The toggling of the primary read location based on an address bit will distribute request traffic across the primary and mirror DIMMs, thereby distributing the thermal image of the workload across all populated DIMM slots and reducing the chances of thermal-based memory traffic throttling.

In the "Mirrored" operating state, the occurrence of correctable and uncorrectable ECC errors are tracked and logged normally by the MCH, and escalated to system interrupt events as specified by the configuration register settings associated with errors on the memory subsystem. Counters implementing the "leaky bucket" function just described for on-line DIMM sparing track the aggregate count of single-bit and multiple-bit errors on a per DIMM basis.

### 2.8.8 I<sup>2</sup>C Bus

The system BIOS uses the I<sup>2</sup>C bus to retrieve DIMM information that is needed to program the MCH memory registers. These memory registers are required to boot the system.

The following table provides the I<sup>2</sup>C addresses for each DIMM slot.

Table 6. I<sup>2</sup>C Addresses for Memory Module SMB – DDR SKU's

| Device  | Address |

|---------|---------|

| DIMM 3B | 0xA8    |

| DIMM 3A | 0xA0    |

| DIMM 2B | 0xAA    |

| DIMM 2A | 0xA2    |

| DIMM 1B | 0xAC    |

| DIMM 1A | 0xA4    |

Table 7. I<sup>2</sup>C Addresses for Memory Module SMB – DDR2 SKU's

| Device  | Address |

|---------|---------|

| DIMM 4B | 0xA8    |

| DIMM 4A | 0xA0    |

| DIMM 3B | 0xAA    |

| DIMM 3A | 0xA2    |

| DIMM 2B | 0xAC    |

| DIMM 2A | 0xA4    |

| DIMM 1B | 0xAE    |

| DIMM 1A | 0xA6    |

# 2.9 PCI Sub-System

### 2.9.1 ICH5R PCI Interface

The Intel® 82801ER I/O Controller Hub (ICH5R) PCI interface is a multi-function device providing an upstream hub interface for access to several embedded I/O functions and features including:

- PCI Local Bus Specification, Revision 2.3 with support for 33MHz PCI operations.

- ACPI power management logic support

- Enhanced DMA controller, interrupt controller, and timer functions

- Integrated IDE controller supports Ultra ATA100/66/33

- Integrated SATA controller

- USB host interface with support for eight USB ports; four UHCI host controllers; one EHCI high-speed USB 2.0 host controller

- Integrated LAN controller

- Integrated ASF controller

- System Management Bus (SMBus) Specification, Version 2.0 with additional support for I<sup>2</sup>C devices

- Low Pin Count (LPC) interface

- Firmware Hub (FWH) interface support

Each function within the ICH5R has its own set of configuration registers. Once configured, each appears to the system as a distinct hardware controller sharing the same PCI bus interface.

#### 2.9.1.1 PCI Interface

The ICH5R PCI interface provides a 33MHz, Revision 2.3 compliant implementation. All PCI signals are 5V tolerant, except for PME#. The ICH5 integrates a PCI arbiter that supports up to six external PCI bus masters in addition to the internal ICH5 requests.

On the Server Board SE7520BD2, this PCI interface is used to support one onboard PCI device, the ATI RAGE XL video controller, and one 5V PCI 32-bit / 33MHz slot.

### 2.9.1.2 IDE Interface (Bus Master Capability and Synchronous DMA Mode)

The fast IDE interface supports up to two IDE devices providing an interface for IDE hard disks and ATAPI devices. Each IDE device can have independent timings. The IDE interface supports PIO IDE transfers up to 16MB/s and Ultra ATA transfers up 100MB/s. It does not consume any ISA DMA resources. The IDE interface integrates 16x32-bit buffers for optimal transfers. The ICH5R's IDE system contains two independent IDE signal channels. The SE7520BD2 board utilizes only one of these. They can be electrically isolated independently.

On the Server Board SE7520BD2, the primary bus is connected to the legacy IDE connector.

#### 2.9.1.3 SATA Controller

The SATA controller supports two SATA devices, providing an interface for SATA hard disks and ATAPI devices. The SATA interface supports PIO IDE transfers up to 16 Mb/s and Serial ATA transfers up to 1.5 Gb/s (150MB/s). The ICH5R's SATA system contains two independent SATA signal ports. They can be electrically isolated independently. Each SATA device can have independent timings. They can be configured to the standard primary and secondary channels.

The Server Board SE7520BD2 supports two SATA connectors for internal hard disk drives. The ICH5 SATA RAID has two channels of SATA RAID support. It uses the LSI Logic\* SATA RAID stack, which is similar to Intel's RAID stack. This provides support for RAID level 0 or 1.

The LSI\* 53C1030 integrated SCSI firmware RAID controller provides for one array. In one mode RAID 0 (Integrated Striping) or RAID 1/1e (Integrated Mirroring/Enhanced) the user is provided with one array. The array will not span across channels; all array drives need to be on one channel.

### 2.9.1.4 Low Pin Count (LPC) Interface

The ICH5R implements an LPC Interface as described in the Low Pin Count Interface Specification, Revision 1.1. The Low Pin Count (LPC) bridge function of the ICH5 resides in PCI Device 31:Function 0. In addition to the LPC bridge interface function, D31:F0 contains other functional units, including DMA, interrupt controllers, timers, power management, system management, GPIO, and RTC.

On the Server Board SE7520BD2, the LPC bus is connected from the ICH5R to both the SIO3 (National Semiconductor\* PC87427) and the Intel® Management Module connector.

# 2.9.1.5 Compatibility Modules (DMA Controller, Timer/Counters, Interrupt Controller)

The DMA controller incorporates the logic of two 82C37 DMA controllers with seven independently programmable channels. Channels 0–3 are hardwired to 8-bit, count-by-byte transfers. Channels 5–7 are hardwired to 16-bit, count-by-word transfers. Any two of the seven DMA channels can be programmed to support fast Type-F transfers.

The ICH5R supports two types of DMA: LPC and PC/PCI. DMA via LPC is similar to ISA DMA. LPC DMA and PC/PCI DMA use the ICH5R's DMA controller. The PC/PCI protocol allows PCI-based peripherals to initiate DMA cycles by encoding requests and grants via two PC/PC REQ#/GNT# pairs. LPC DMA is handled through the use of the LDRQ# lines from peripherals and special encoding on LAD[3:0] from the host. Single, Demand, Verify, and Increment modes are supported on the LPC interface. Channels 0–3 are 8-bit channels. Channels 5–7 are 16-bit channels. Channel 4 is reserved as a generic bus master request.

The timer/counter block contains three counters that are equivalent in function to those found in one 82C54 programmable interval timer. These three counters are combined to provide the system timer function, and speaker tone. The 14.31818MHz oscillator input provides the clock source for these three counters.

The ICH5R provides an ISA-compatible Programmable Interrupt Controller (PIC) that incorporates the functionality of two 82C59 interrupt controllers. The two interrupt controllers are cascaded so that 14 external and two internal interrupts are possible. In addition, the ICH5R supports a serial interrupt scheme. All of the registers in these modules can be read and restored. This is required to save and restore system state after power has been removed and restored to the platform.

### 2.9.1.6 Advanced Programmable Interrupt Controller (APIC)

In addition to the standard ISA-compatible PIC described in the previous section, the ICH5R incorporates the Advanced Programmable Interrupt Controller (APIC).

### 2.9.1.7 Universal Serial Bus (USB) Controller

The ICH5R contains an Enhanced Host Controller Interface Specification for Universal Serial Bus, Revision 1.0-compliant host controller that supports USB high-speed signaling. High-speed USB 2.0 allows data transfers up to 480 Mb/s, which is 40 times faster than full-speed USB.

The ICH5R also contains four Universal Host Controller Interface (UHCI) controllers that support USB full-speed and low-speed signaling. On the Server Board SE7520BD2, the ICH5R supports five USB 2.0 ports. All five ports are high-speed, full-speed, and low-speed capable. ICH5R's port-routing logic determines whether a USB port is controlled by one of the UHCI controllers or by the EHCI controller.