# Intel® Server System SR1680MV

# Technical Product Specification

Intel order number E76653-003

**Revision 1.3**

March 2010

**Enterprise Platforms and Services Division – Marketing**

# Revision History

| Date       | Revision Number | Modifications                                                            |  |

|------------|-----------------|--------------------------------------------------------------------------|--|

| July 2009  | 0.1             | First release.                                                           |  |

| July 2009  | 1.0             | Updated IO Board Pin definition and Regulator Information.               |  |

| Aug 2009   | 1.1             | Updated Pin definition for PDB, SATA board, and Function Jumper.         |  |

| Nov 2009   | 1.2             | Updated Pin definition for PDB,SATA board, Server board power connector, |  |

|            |                 | and Function Jumper.                                                     |  |

| March 2010 | 1.3             | Updated Regulation Section and remove CNCA(China- CCC) Certification     |  |

|            |                 | content.                                                                 |  |

# **Disclaimers**

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> Server System SR1680MV may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the license. The information in this manual is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Intel, Pentium and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2010.

# **Table of Contents**

| 1. | Introduc | ction                                                                                                           | 1  |

|----|----------|-----------------------------------------------------------------------------------------------------------------|----|

| 1  | 1.1      | Chapter Outline                                                                                                 | 1  |

| 1  | 1.2      | Server Board Use Disclaimer                                                                                     | 2  |

| 2. | Product  | Overview                                                                                                        | 3  |

| 2  | 2.1      | System Overview                                                                                                 | 4  |

| 2  | 2.2      | System Dimensions                                                                                               | 5  |

| 2  | 2.3      | System Components                                                                                               | 5  |

| 2  | 2.4      | Server System Front layout                                                                                      | 6  |

| 2  | 2.5      | Server System Rear Layout                                                                                       | 6  |

| 3. | System   | Board                                                                                                           | 7  |

| 3  | 3.1      | Introduction                                                                                                    | 7  |

| 3  | 3.2      | System Board Overview                                                                                           | 7  |

| 3  | 3.3      | Functional Architecture                                                                                         | 9  |

|    | 3.3.1    | Processors Support                                                                                              | 9  |

|    | 3.3.2    | Intel® 5500 Chipset (IOH 24D) and 82801JR(ICH10R)                                                               | 10 |

|    | 3.3.3    | Memory support                                                                                                  | 11 |

|    | DIMM     | ry TopologyPopulation Rules for Three Slots Configurationnel Population Rules for Memory RAS Mode Configuration | 12 |

| 3  | 3.4      | Graphics Controller                                                                                             | 15 |

| 3  | 3.5      | IO Boards support                                                                                               | 15 |

| 3  | 3.6      | System Management                                                                                               | 15 |

| 4. | Power S  | Subsystem                                                                                                       | 16 |

| 2  | 1.1      | Power Supply Mechanical Overview                                                                                | 16 |

|    | 4.1.1    | Output Connection (Card Edge)                                                                                   | 17 |

| 4  | 1.2      | Power system component and Connector Overview                                                                   | 18 |

|    | 4.2.1    | Power Distribution Board Connector to Power supply (J1)                                                         | 18 |

|    | 4.2.2    | Power Distrubution Board (PDB) Connectors to Sever board (J2, J3, J4, J5)                                       | 19 |

|    | 4.2.3    | Server Board Power Connectors                                                                                   | 20 |

| 4  | 1.3      | AC Input Requirements                                                                                           | 21 |

|    | 4.3.1    | AC Input Voltage Range                                                                                          | 21 |

|    | 4.3.2    | AC Power Cord Specification Requirements                                                                        | 22 |

| 4.3.3      | Efficiency                             | 22 |

|------------|----------------------------------------|----|

| 4.3.4      | AC Input Voltage Specification         | 23 |

| 4.3.5      | AC Line Dropout / Holdup               | 24 |

| 4.3.6      | AC Line Leakage Current                | 24 |

| 4.3.7      | AC Inrush                              | 24 |

| 4.3.8      | Power Factor Correction                | 24 |

| 4.4        | DC Output Specification                | 24 |

| 4.4.1      | Output Power / Currents                | 24 |

| 4.4.2      | Output Voltage Regulation              | 25 |

| 4.5        | Protection Circuits                    | 25 |

| 4.5.1      | Over-current Protection (OCP)          | 25 |

| 4.5.2      | Over-voltage Protection (OVP)          | 26 |

| 4.5.3      | Over-temperature Protection (OTP)      | 26 |

| 4.6        | Power Supply LED                       | 26 |

| 5. Cooling | g Subsystem                            | 27 |

| 5.1        | System Fan Module and Air Ducts        | 27 |

| 5.2        | System Fan Connectors                  | 28 |

| 6. System  | n Board Interconnects                  | 30 |

| 6.1        | IO Board                               | 30 |

| 6.1.1      | IO Board IO Connectors                 | 31 |

| 6.2        | Hard Drivers Backplane                 | 34 |

| 6.2.1      | HDD Backplane SATA Connectors (J2, J3) | 34 |

| 7. Hard D  | isk Drive Support                      | 36 |

| 7.1        | Hard Drive Bays                        | 36 |

| 7.1.1      | Hot-swap Drive Trays                   | 36 |

| 7.1.2      | Hard Driver Activity and Fault LEDs    | 36 |

| 8. System  | n LED, Button and Jumper Functionality | 37 |

| 8.1        | Front Panel LED and Button information | 37 |

| 8.2        | Rear Panel LED information             | 38 |

| 8.3        | System Confirguration Jumpers          | 39 |

| 8.4        | MISC Jumper (J48)                      | 40 |

| 8.5        | ICH Functions Jumper (J30)             | 41 |

| 9. IO Boa  | rd extended Assembly                   | 42 |

| 9.1        | Riser Card                             | 42 |

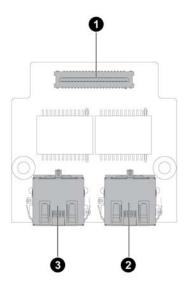

| 9.2        | NIC Board                              | 42 |

| 9.3          | Daughter Cards (Optional)             | 43 |

|--------------|---------------------------------------|----|

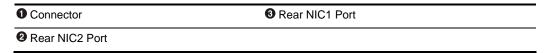

| 9.3.1        | 10 GB IO Card                         | 43 |

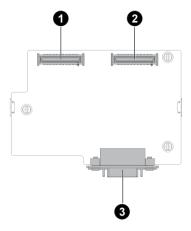

| 9.3.2        | InfiniBand Card                       | 44 |

| 10. Basic Ir | nput/Output System (BIOS)             | 45 |

| 10.1 BIOS A  | Architecture                          | 45 |

| 10.2         | BIOS Feature                          | 45 |

| 10.3         | BIOS POST (Power On Self Test) Code   | 47 |

| 10.4         | Beep Codes                            | 49 |

| 11. System   | n Management                          | 50 |

| 11.1         | System Block Diagram                  | 50 |

| 11.2         | Serial-Over LAN                       | 51 |

| 11.3         | KVM Over IP                           | 51 |

| 11.4         | Virtual Storage                       | 51 |

| 11.5         | LED Control                           | 51 |

| 11.6         | The Concept Of Message Channel        | 51 |

| 11.7         | PEF And Alerting Design               | 52 |

| 11.8         | Summary Of Sensors                    | 53 |

| 11.9         | Summary Of Supported IPMI Command     | 56 |

| 11.9.1       | IPMI Device Global Commands           | 56 |

| 11.9.2       | Broadcast Commands                    | 57 |

| 11.9.3       | Messaging Support Commands            | 57 |

| 11.9.4       | Firmware Firewall & Command Discovery | 58 |

| 11.9.5       | RMCP+ Support And Payload Commands    | 58 |

| 11.9.6       | IPMI LAN Commands                     | 58 |

| 11.9.7       | IPMI Serial/Modem Commands            | 59 |

| 11.9.8       | SOL Commands                          | 59 |

| 11.9.9       | BMC Watchdog Timer Commands           | 59 |

| 11.9.10      | Chassis Commands                      | 59 |

| 11.9.11      | Event Commands                        | 60 |

| 11.9.12      | PEF And Alerting Commands             | 61 |

| 11.9.13      | SEL Commands                          | 61 |

| 11.9.14      | SDR Repository Commands               | 62 |

| 11.9.15      | FRU Inventory Device Commands         | 62 |

| 11.9.16      | Sensor Device Commands                | 63 |

| 11.9.17      | OEM Commands                          | 63 |

| 12. Enviro | nmental Specifications                | 67 |

|------------|---------------------------------------|----|

| 12.1       | Operational Environment               | 67 |

| 12.2       | Storage Environmental Extremes        | 67 |

| 12.3       | Shock                                 | 67 |

| 12.4       | Vibration                             | 68 |

| 12.5       | Rotational Vibration                  | 69 |

| 12.6       | Acoustics                             | 69 |

| 12.6.1     | Drop Test                             | 70 |

| 12.6.2     | Vibration Test                        | 70 |

| 12.7       | Replacing the Backup Battery          | 71 |

| 13. Regula | atory and Certification Information   | 72 |

| 13.1       | Product Regulatory Compliance         | 72 |

| 13.2       | Use of Specified Regulated Components | 72 |

| 13.3       | Electromagnetic Compatibility Notices | 74 |

| 13.3.1     | USA                                   | 74 |

| 13.3.2     | ICES-003 (Canada)                     | 75 |

| 13.3.3     | Europe (CE Declaration of Conformity) | 75 |

| 13.3.4     | Japan EMC Compatibility               | 75 |

| 13.3.5     | BSMI (Taiwan)                         | 76 |

| 13.3.6     | KCC (Korea)                           | 76 |

| 13.4       | Rack Mount Installation Guidelines    | 76 |

| 13.5       | Power Cord Usage Guidelines           | 77 |

| 13.6       | Product Ecology Compliance            | 78 |

| 13.7       | Other Markings                        | 80 |

| Appendix A | A: Integration and Usage Tips         | 81 |

| Glossary   |                                       | 82 |

| Deference  | Decuments                             | 02 |

# List of Figures

| Figure 1. Intel® Server System SR1680MV with 2.5-inch Pluggable HDDs         | 4  |

|------------------------------------------------------------------------------|----|

| Figure 2. Server Components with 2.5-inch Pluggable HDDs                     | 5  |

| Figure 3. System Front View                                                  | 6  |

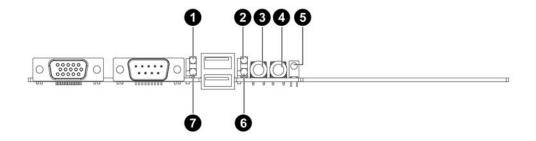

| Figure 4. System rear layout                                                 | 6  |

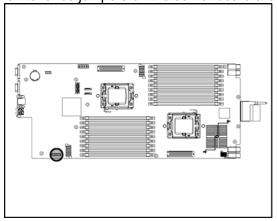

| Figure 5. Server Board Overview                                              | 7  |

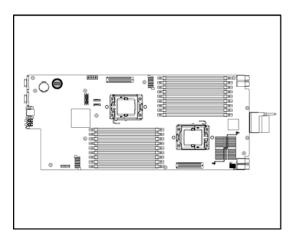

| Figure 6. Server Board Components                                            | 8  |

| Figure 7. Power Supply Module Dimensional Drawing                            | 16 |

| Figure 8. Power Distribution Board Connector                                 | 18 |

| Figure 9. PDB Connector to Power Supply                                      | 18 |

| Figure 10. PDB Connectors to Server Board                                    | 19 |

| Figure 11. Server Board Power Connectors                                     | 20 |

| Figure 12. AC Power Cord                                                     | 22 |

| Figure 13. System Fans and Air Ducts                                         | 27 |

| Figure 14. System Fan Connectors for IOB                                     | 28 |

| Figure 15. Connectors and Component Location of IO Board                     | 30 |

| Figure 16. IO Boards IO Connectors                                           | 31 |

| Figure 17. Connectors and Component Locations of 2.5-inch SATA HDD Backplane | 34 |

| Figure 18. HDD Backplane SATA Connectors                                     | 34 |

| Figure 19. Front Panel LEDs and Buttons                                      | 37 |

| Figure 20. Rear Panel LEDs                                                   | 38 |

| Figure 21. Location of MISC Jumper                                           | 39 |

| Figure 22. Location of Function Jumper                                       | 39 |

| Figure 23. MISC Jumper                                                       | 40 |

| Figure 24. Functions Jumpers                                                 | 41 |

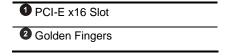

| Figure 25. PCI Riser Card                                                    | 42 |

| Figure 26. Connectors and Component Locations of NIC Board                   | 43 |

| Figure 27. Connectors and Component Locations of 10 GB IO Card               | 43 |

| Figure 28. Connectors and Component Locations of InfiniBand Card             | 44 |

| Figure 29. System Block Diagram                                              | 50 |

# List of Tables

| Table 1. System Feature Set                                                                                   | 3    |

|---------------------------------------------------------------------------------------------------------------|------|

| Table 2. System Dimensions                                                                                    | 5    |

| Table 3. Major Board Components                                                                               | 8    |

| Table 4. Processor Support Chart                                                                              | 9    |

| Table 5. RDIMM Population Configuration for Three Slots per Channel                                           | .12  |

| Table 6. UDIMM Population Configurations for Three Slots per Channel                                          | .13  |

| Table 7. RDIMM Population Configurations (Intel® Xeon® Processor 5600 series only) for thre slots per Channel |      |

| Table 8. UDIMM Population Configurations (Intel® Xeon® Processor 5600 series only) for thre slots per Channel |      |

| Table 9 DC output Top Side connection                                                                         | .17  |

| .Table 10 DC Output Connection (Card Edge)                                                                    | .17  |

| Table 11. Pin Definition of PDB Connector to Power Supply                                                     | .18  |

| Table 12. Pin Definition of PDB Connectors to Motherboard (J2, J4)                                            | 20   |

| Table 13. Pin Definition of PDB Connectors to Mohterboard (J3, J5)                                            | 20   |

| Table 14. Pin Definition of Server Board Power Connectors (J2, J4)                                            | 20   |

| Table 15. Pin Definition of Server Board Power Connectors (J3)                                                | 20   |

| Table 16. Pin Definition of Server Board Power Connectors (J5)                                                | .21  |

| Table 17. AC Input Voltage Specification                                                                      | .21  |

| Table 18. AC Power Cord Specification                                                                         | .22  |

| Table 19. Efficiency                                                                                          | .22  |

| Table 20. AC Input Rating                                                                                     | 23   |

| Table 21. AC Line Dropout / Holdup                                                                            | .24  |

| Table 22. AC In-rush                                                                                          | 24   |

| Table 23. Power Supply Module Load Ratings                                                                    | .24  |

| Table 24. Voltage Regulation Limits                                                                           | .25  |

| Table 25. Over Current Limits (Lout Limit)                                                                    | 26   |

| Table 26. Over-voltage Limits                                                                                 | 26   |

| Table 27. System Fan Connector Pin Definition (J7)                                                            | 28   |

| Table 28. Fan Connectors Pin Definition (J6, J8 – J6 on Left IO Board / J8 on Right IO Board)                 | 28   |

| Table 29. Fan Connectors Pin Definitions (J8, J9 – J8 on Left IO Board / J9 on Right IO Board                 | d)29 |

| Table 30. Pin Definitions of IO Boards IO Connector                                                           | .31  |

| Table 31. Pin Definition of HDD Backplane SATA Connector (J2) | 35 |

|---------------------------------------------------------------|----|

| Table 32. Pin Definition of HDD Backplane SATA Connector (J3) | 35 |

| Table 33. Hard Drive LED Function Definitions                 | 36 |

| Table 34. Front Panel LEDs information                        | 37 |

| Table 35. Rear LED information                                | 38 |

| Table 36. Function of MISC Jumper                             | 39 |

| Table 37. Function of Functions Jumper                        | 40 |

| Table 38. Pin Definition of MISC Jumper (J48)                 | 40 |

| Table 39. Pin Definition of Functions Jumper                  | 41 |

| Table 40. POST Code Information                               | 47 |

| Table 41. Beep Code Information                               | 49 |

| Table 42. KVM Features                                        | 51 |

| Table 43. State of UID LED and System Health LED              | 51 |

| Table 44. KCS Interface Register                              | 52 |

| Table 45. BMC Supported Channels                              | 52 |

| Table 46. Sensor Data Records                                 | 53 |

| Table 47. Defined Commands                                    | 56 |

| Table 48. IPMI Device Global Commands                         | 56 |

| Table 49. Broadcast Commands                                  | 57 |

| Table 50. Messaging Support Commands                          | 57 |

| Table 51 Firmware Firewall and Command Discovery              | 58 |

| Table 52. RMCP+ Support and Payload Commands                  | 58 |

| Table 53. IPMI LAN Commands                                   | 58 |

| Table 54. IPMI Serial / Modem Commands                        | 59 |

| Table 55. SOL Commands                                        | 59 |

| Table 56. BMC Watchdog Timer Commands                         | 59 |

| Table 57. Chassis Commands                                    | 59 |

| Table 58. Event Commands                                      | 60 |

| Table 59. PEF and Alerting Commands                           | 61 |

| Table 60. SEL Commands                                        | 61 |

| Table 61. SDR Repository Commands                             | 62 |

| Table 62. FRU Inventory Device Commands                       | 62 |

| Table 63. Sensor Device Commands                              | 63 |

| Table 64. OEM Commands                                        |    |

| Table 65. Velocity Change for Fully Packing Weight            | 68 |

## List of Tables

# Intel® Server System SR1680MV TPS

| Table 66. Acoustics Test Criteria                           | 69 |

|-------------------------------------------------------------|----|

| Table 67. Drop Test                                         | 70 |

| Table 68. Vibration Test                                    | 70 |

| Table 69. Product Safety & Electromagentic (EMC) Compliance | 73 |

| Table 70. Product Ecology Compliance                        | 78 |

| Table 71. Other Markings                                    | 80 |

<This page intentionally left blank.>

# 1. Introduction

This Technical Product Specification (TPS) provides system-specific information detailing the features, functionality, and high-level architecture of the Intel® Server System SR1680MV.

The Intel® Server System SR1680MV may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Refer *Intel® Server System SR1680MV Specification Update* for published errata.

# 1.1 Chapter Outline

This document is divided into the following chapters:

- Chapter 1 Introduction

- Chapter 2 Product Overview

- Chapter 3 System Board

- Chapter 4 Power Subsystem

- Chapter 5 Cooling Subsystem

- Chapter 6 System Board Interconnects

- Chapter 7 Hard Disk Drive Support

- Chapter 8 System LED, Button and Jumper Functionality

- Chapter 9 IO Board extended Assembly

- Chapter 10 Basic Input/Output System (BIOS)

- Chapter 11 System Management System

- Chapter 12 Environmental Specifications

- Chapter 13 Regulatory and Certification Requirements

- Appendix A Integration and Usage Tips

- Glossary

- Reference Documents

## 1.2 Server Board Use Disclaimer

Intel Corporation server boards support add-in peripherals and contain a number of high-density VLSI and power delivery components that need adequate airflow to cool. Intel ensures through its own system development and testing that when Intel server building blocks are used together, the fully integrated system will meet the intended thermal requirements of these components. It is the responsibility of the system integrator who chooses not to use Intel-developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of airflow required for their specific application and environmental conditions. Intel Corporation cannot be held responsible if components fail or the server board does not operate correctly when used outside any of their published operating or non-operating limits.

# 2. Product Overview

The Intel® Server System SR1680MV is a rack mount 1U server system with features designed to support the twin high-density high-performance computing server market. The system offers the following configuration:

■ Intel® Server System SR1680MV

This chapter provides a high-level overview of the system features. The following chapters provide greater detail for each major system component or feature.

**Table 1. System Feature Set**

| Feature                | Description                                                                                                                                                                                                                                             |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor              | <ul> <li>Support for one or two Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5500 series and Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5600 series processors in FC-LGA 1366 Socket B package with up to 95 W Thermal Design Power (TDP).</li> </ul> |

|                        | <ul> <li>Located on LGA 1366-pin processor socket</li> </ul>                                                                                                                                                                                            |

| Chipset                | ■ Intel® 5500 Chipset (IOH 24D)                                                                                                                                                                                                                         |

|                        | ■ Intel <sup>®</sup> ICH10R I/O Controller Hub                                                                                                                                                                                                          |

| System Memory          | Three channels per processor; up to three DIMMs per channel                                                                                                                                                                                             |

|                        | <ul> <li>72 GB max per processor; 8GB DIMM modules available at launch</li> </ul>                                                                                                                                                                       |

|                        | <ul><li>Support DDR3 speeds of 800/1066/1333 MHz</li></ul>                                                                                                                                                                                              |

|                        | <ul> <li>Support up to three registered DIMMs per channel, 8GB max per registered DIMM<br/>(4GB qualified), up to 144 GB total</li> </ul>                                                                                                               |

|                        | <ul> <li>Support up to two unbuffered DIMMs per channel, 4GB max per unbuffered DIMM</li> </ul>                                                                                                                                                         |

|                        | <ul> <li>Support single-rank (SR), dual-rank (DR), and quad-rank (QR) DIMM modules</li> </ul>                                                                                                                                                           |

| Video                  | On-board SeverEngines* Pilot II controller                                                                                                                                                                                                              |

|                        | <ul> <li>Integrated 2D Video Controller</li> </ul>                                                                                                                                                                                                      |

|                        | High speed Integrated 24-bit RAMDAC                                                                                                                                                                                                                     |

|                        | Single lane PCI-Express host interface                                                                                                                                                                                                                  |

| LAN                    | Two 10/100/1000 ports provided by Intel® 82576 PHYs                                                                                                                                                                                                     |

| Expansion Capabilities | One PCI Express* Gen2 riser slot supporting half-length/low-profile riser cards                                                                                                                                                                         |

| Hard Drives            | <ul> <li>Up to four 2.5-inch SATA drivers with two backplanes (two for each node)</li> </ul>                                                                                                                                                            |

|                        | <ul> <li>Intel<sup>®</sup> Matrix RAID with Software RAID levels 0/1</li> </ul>                                                                                                                                                                         |

| Peripheral Interfaces  | Front connections:                                                                                                                                                                                                                                      |

|                        | One DB-15 video connector                                                                                                                                                                                                                               |

|                        | One DB-9 Serial connector                                                                                                                                                                                                                               |

|                        | Two USB 2.0 connector                                                                                                                                                                                                                                   |

|                        | Rear connections:                                                                                                                                                                                                                                       |

|                        | <ul> <li>Two RJ-45 10/100/1000 Mbps network connections</li> </ul>                                                                                                                                                                                      |

| Power Supply           | One 1100-W power supply module                                                                                                                                                                                                                          |

| Fans                   | Six system fans (three for each node)                                                                                                                                                                                                                   |

|                        | One power supply fans                                                                                                                                                                                                                                   |

| Feature           | Description                                                                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Server Management | On-board Server Engines* Pilot II Controller  Integrated Baseboard Management Controller (Integrated BMC), IPMI 2.0 compliant |

# 2.1 System Overview

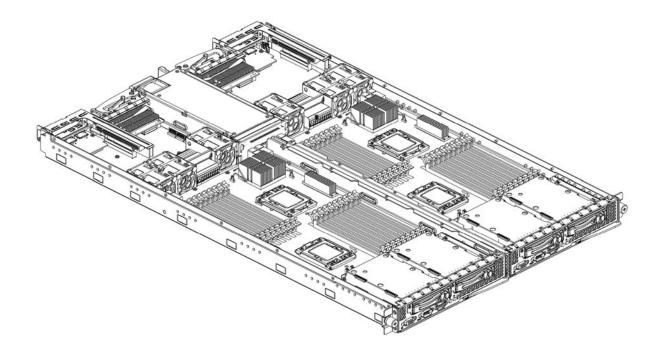

Figure 1. Intel<sup>®</sup> Server System SR1680MV with 2.5-inch Pluggable HDDs

# 2.2 System Dimensions

**Table 2. System Dimensions**

| Height                      | 43.2 mm  |

|-----------------------------|----------|

| Width                       | 448 mm   |

| Depth (without front panel) | 714.2 mm |

| Minimum Weight              | 11.7 kg  |

| Maximum Weight              | 17.16 kg |

# 2.3 System Components

| Power Supply            | Power Distributon Boards  |

|-------------------------|---------------------------|

| 2 IO Boards             | 6 Motherboards            |

| 3 Riser Card Assemblies | SATA HDD Backplane        |

| 4 System Fans           | 3 2.5" Pluggable HDD Bays |

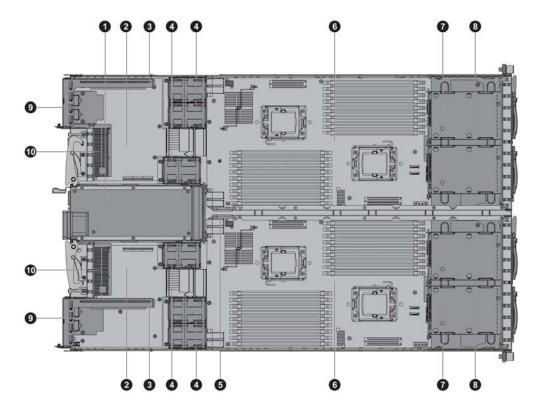

Figure 2. Server Components with 2.5-inch Pluggable HDDs

## 2.4 Server System Front layout

The system is designed to support 2.5-inch hot-swap SATA hard disk drives.

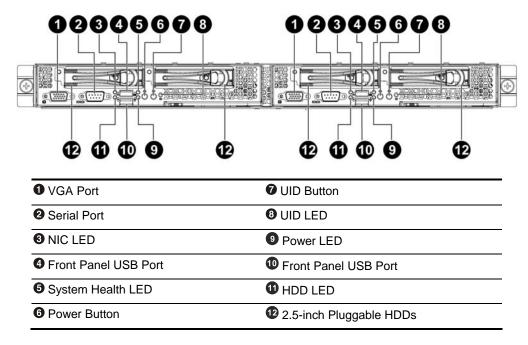

Figure 3. System Front View

# 2.5 Server System Rear Layout

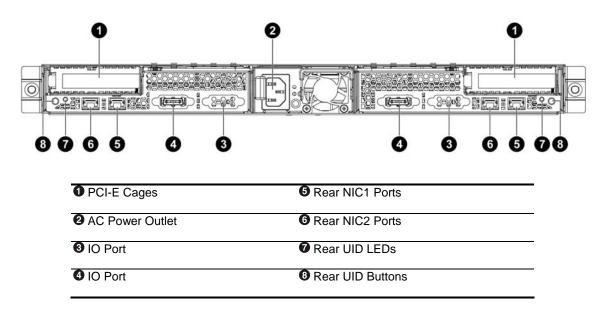

Figure 4. System rear layout

# 3. System Board

This chapter describes the system board for the Intel® Server System SR1680MV.

## 3.1 Introduction

The Intel® Server SR1680MV system Board provides most of the basic functions for the system. Nearly all of the boards from the board set plug into or cable to the main board.

# 3.2 System Board Overview

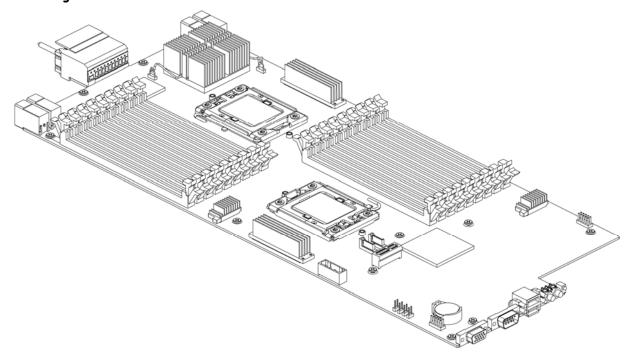

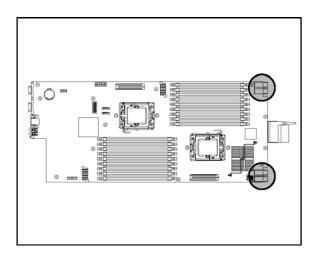

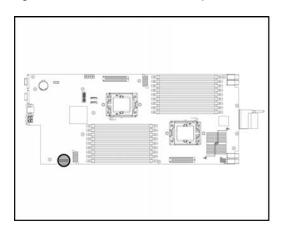

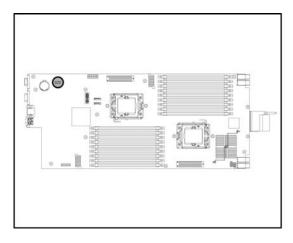

Figure 5. Server Board Overview

The following figure shows the server board's layout. Each connector and major component is identified by a number or letter, and a description is given below the figure.

**Figure 6. Server Board Components**

**Table 3. Major Board Components**

| System Battery (BH1)                                            | 14 Processor 2 (CPU 2)                                               |  |  |  |

|-----------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|

| 2 ICH Functions Jumper (J30)                                    | 15 DIMM Socket Group 2 (J17, J18, J19, J20, J21, J22, J23, J24, J25) |  |  |  |

| HDD Backplane Connector                                         | 16 MISC Jumper                                                       |  |  |  |

| 4 SATA Power Connector (J47)                                    | 17 Front UID LED                                                     |  |  |  |

| Motherboard SATA4 Connector (J29)                               | Front UID Button                                                     |  |  |  |

| 6 Motherboard SATA3 Connector (J31)                             | 19 Power Button                                                      |  |  |  |

| Processor 1 (CPU 1)                                             | System Health LED                                                    |  |  |  |

| B DIMM Socket Group1 (J7, J8, J9, J10, J11, J12, J13, J14, J15) | 2) Power LED                                                         |  |  |  |

| Motherboard Power Connector4 (J5)                               | 2 Front USB Ports                                                    |  |  |  |

| Motherboard Power Connector3 (J4)                               | <sup>3</sup> NIC LED                                                 |  |  |  |

| Motherboard IO Connector (J1)                                   | <b>❷</b> HDD LED                                                     |  |  |  |

| Motherboard Power Connector2 (J3)                               | 3 Serial Port                                                        |  |  |  |

| Motherboard Power Connector1 (J2)                               | <sup>20</sup> VGA Port                                               |  |  |  |

#### 3.3 Functional Architecture

This section describes the primary functions, blocks, and components that reside on the main board. The section is laid out as follows:

- Chipset components

- Primary interfaces to the memory and I/O riser

- Additional information regarding other functional blocks on the board

#### 3.3.1 Processors Support

Each system board is designed to support dual Intel<sup>®</sup> Xeon<sup>®</sup> Processor series and Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5600 series. This section provides more information on the processor sequence and its supported technologies.

The following table lists the processor sequence and each processor property that the board can support.

Processor Intel® Xeon® Processor 5500 series and Intel® Xeon® Processor 5600 series Generation Processor 45 nm and 32nm Technology FC-LGA 1366 Lands Package X5570/X5560/X | E5540/E5530/E | E5506/E5504/E Processor L5530 L5520 L5506 5550 5520 5502 Sequence 2.93/2.80/266/95 2.53/2.40/2.26/8 2.13/2.00/1.86/ Clock speed 2.40/60W 2.26/60W 2.13/60W W 0W 80W (GHz)/Watt 6.4 5.86 4.8 5.86 5.86 4.8 QPI Speed (GT/sec) 8 MB 8 MB 4 MB 8 MB 8 MB 4 MB Cache Memory Speed 800 1333/1066/800 1066/800 800 1066/800 1066/800 (DDR3 only) Applied Technology ٧ DBS V Virtualization Technology V FlexMigration

**Table 4. Processor Support Chart**

The Intel® Xeon® 5500 series processor and Intel® Xeon® Processor 5600 series are multi-core processors based on 45 nm and 32nm process technology. Intel QuickPath Interconnection, a cache-coherent point to point links capable of up to 6.4GT/s, up to 8MB of shared cache, and an integrated memory controller.

#### 3.3.2 Intel® 5500 Chipset (IOH 24D) and 82801JR(ICH10R)

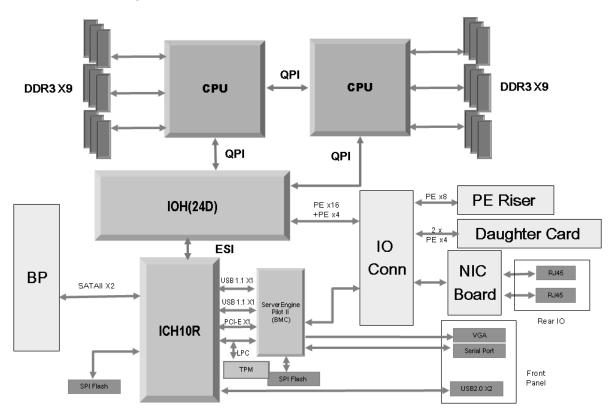

The Intel® SR1680MV Server System board implements Intel® 5500 (IOH 24D) chipset and 82801JR (ICH10R). This section describes the general functionality and features of this chipset.

The Intel<sup>®</sup> 5500 IOH 24D chipset provides the connection point between the Intel<sup>®</sup> processor QuickPath Interconnection and a variety of I/O components.

The Intel® 5500 IOH 24D has the following capabilities:

- Two Intel® QuickPath Interconnection full-width links with 20 lanes in each direction

- One x16 PCI Express\* Gen2 port or two x8 PCI Express\* Gen2 ports, each supporting up to 5 GB/s/direction peak bandwidth

- One x4 ESI link interface supporting PCI Express\* Gen1 (2.5 Gbps) transfer rate

- Dedicated legacy bridge (Intel<sup>®</sup> I/O Controller Hub (ICH)) interface

- Intel<sup>®</sup> I/O Acceleration Technology (I/OAT) 3 support

- Intel<sup>®</sup> Virtualization Technology for Directed I/O (Intel<sup>®</sup> VT-d), 2<sup>nd</sup> revision support

- Servers supported by Intel<sup>®</sup> Manageability Engine (Intel<sup>®</sup> ME)

- Improved RAS features achieved by protecting internal data paths through ECC and parity protection mechanism

- Power management supports system states (S0, S1, S3, S4, S5)

- Server security supported by TPM 1.2 and Intel VT-d

ICH10R functions and capabilities include:

- Provides up to six PCI Express\* root ports. Each root port supports 2.5 Gb/s bandwidth in each direction. PCI Express\* is compliant with PCI Express\* Base Specification, Rev 1.1. Each PCI-E bus support for 33 MHz PCI operations.

- Two integrated SATA controllers that support independent DMA operation on up to six ports and support data transfer rates of up to 3.0 Gb/s.

- Provides up to 12 USB 2.0 ports. Data transfer speed up to 480 Mb/s, 40 times faster than full-speed USB.

- Gigabit Ethernet Controller incorporated. The LAN controller operates at multiple speeds (10/100/1000 MB/s) either in duplex or half-duplex mode.

- Low pin count interface

- System Management Bus (SMBus) 2.0 compliant

- Intel<sup>®</sup> Matrix Storage Technology support. The industry-leading technology provides RAID 0, 1, 5, 10 functionality on up to six SATA ports.

- Supports Intel<sup>®</sup> High Definition Audio

- Supports Intel<sup>®</sup> Trusted Execution Technology

- Firmware Hub (FWH) interface support

- Serial Peripheral Interface (SPI) support

- Intel<sup>®</sup> Quiet System Technology (Intel<sup>®</sup> QST)

The ICH10 integrates four fan speed sensors (four Tach signals) and three fan speed controllers that allow the monitoring and controlling up to four system fans on the system. Coupled with Intel<sup>®</sup> QST, the server provides more effective thermal and acoustic management for the platform.

- Intel<sup>®</sup> Anti-Theft Technology: This feature helps the end-user the ability to restrict access to HDD data by unknown parties.

- Integrated Intel Trusted Platform Module (TPM) Rev.1.2.

#### 3.3.3 Memory support

This section contains information on memory topology, memory type, capacity and population rules.

#### **Memory Topology**

Intel<sup>®</sup> Xeon<sup>®</sup> 5500 platform offers a wide variety of configurations; the following are generic population requirements:

- All DIMMs must be DDR3 DIMMs.

- If 1.35V (DDR3L) and 1.50V (DDR3) DIMMs are mixed, the DIMMs will run at 1.50V.

- Registered DIMMs must be ECC only, Unbuffered DIMMs can be ECC or non-ECC.

- Mixing of Registered and Unbuffered DIMMs is not allowed.

- It is allowed to mix ECC and non-ECC Unbuffered DIMMs. The presence of a single non-ECC Unbuffered DIMM will result in disabling ECC functionality.

- DIMMs with different timing parameters can be installed on different slots within the same channel, but only timings that support the slowest DIMM will be applied to all. As a consequence, faster DIMMs will be operated at timings supported by the slowest DIMM populated. The same interface frequency (DDR3-800, DDR3-1066, or DDR3-1333) will be applied to all DIMMs on all channels on the platform (both processors).

- DIMM with DDR3-1333 speed is allowed only when one DIMM per Channel (1DPC) is populated. If two 1333 MT/s capable UDIMMs or RDIMMs are detected in the same channel, BIOS would flag this as a warning and force the speed to 1066 MT/s.

- When one quad rank DIMMs is used, it must be populated in DIMM slot0 (farthest away from the CPU) of a given channel.

- Mixing of quad ranks DIMMs in one channel and three DIMMs in other channel (3DPC) on the same CPU socket is not allowed. If such configuration is detected on a CPU socket, BIOS would flag this as a warning and disable the QR DIMM channel(s)

For the following sub-sections, there will be more information on the DIMM population rules for your reference.

Memory Controller integrated in processor:

- DDR3 1333/1066/800 MT/s depending on DIMM population

- Supports both registered (RDIMM) and unbuffered (UDIMM) DIMM modules

- Supports single-rank (SR), dual-rank (DR), and quad-rank (QR) DIMM modules

- 72 GB max memory limit per processor, 8GB DIMM modules available at launch

- Three channels per processor

- Up to three DIMMs-per-channel (DPC), depending on platform implementation

- RAS Independent, Mirrored, Combined Channel (Lockstep) functionality

#### DIMM Population Rules for Three Slots Configuration

For three slots per channel configurations, the Intel Xeon platform requires DIMMs within a channel to be populated starting with the DIMMs farthest from the processor in a "fill farthest" approach. Intel recommends checking for correct DIMM placement during BIOS initialization. Additionally, Intel strongly recommends that all designs follow the DIMM ordering, command clock, and control signal routing. This addressing must be maintained to be compliant with the reference BIOS code supplied by Intel.

Table 5. RDIMM Population Configuration for Three Slots per Channel

| Configuration<br>Number | POR Speed          | 1N or 2N | DIMM3 | DIMM2       | DIMM1       |

|-------------------------|--------------------|----------|-------|-------------|-------------|

| 1                       | DDR3-1333,1066&800 | 1N       | Empty | Empty       | Single-rank |

| 2                       | DDR3-1333,1066&800 | 1N       | Empty | Empty       | Dual-rank   |

| 3                       | DDR3-1066&800      | 1N       | Empty | Empty       | Quad-rank   |

| 4                       | DDR3-1066&800      | 1N       | Empty | Single-rank | Single-rank |

| 5                       | DDR3-1066&800      | 1N       | Empty | Single-rank | Dual-rank   |

| 6                       | DDR3-1066&800      | 1N       | Empty | Dual-rank   | Single-rank |

| 7                       | DDR3-1066&800      | 1N       | Empty | Dual-rank   | Dual-rank   |

| 8                       | DDR3-800           | 1N       | Empty | Single-rank | Quad-rank   |

| 9                       | DDR3-800           | 1N       | Empty | Dual-rank   | Quad-rank   |

| Configuration<br>Number | POR Speed | 1N or 2N | DIMM3       | DIMM2       | DIMM1       |

|-------------------------|-----------|----------|-------------|-------------|-------------|

| 10                      | DDR3-800  | 1N       | Empty       | Quad-rank   | Quad-rank   |

| 11                      | DDR3-800  | 1N       | Single-rank | Single-rank | Single-rank |

| 12                      | DDR3-800  | 1N       | Single-rank | Single-rank | Dual-rank   |

| 13                      | DDR3-800  | 1N       | Single-rank | Dual-rank   | Single-rank |

| 14                      | DDR3-800  | 1N       | Dual-rank   | Single-rank | Single-rank |

| 15                      | DDR3-800  | 1N       | Single-rank | Dual-rank   | Dual-rank   |

| 16                      | DDR3-800  | 1N       | Dual-rank   | Single-rank | Dual-rank   |

| 17                      | DDR3-800  | 1N       | Dual-rank   | Dual-rank   | Single-rank |

| 18                      | DDR3-800  | 1N       | Dual-rank   | Dual-rank   | Dual-rank   |

**Table 6. UDIMM Population Configurations for Three Slots per Channel**

| Configuration<br>Number | POR Speed          | 1N or 2N | DIMM3 | DIMM2       | DIMM1       |

|-------------------------|--------------------|----------|-------|-------------|-------------|

| 1                       | DDR3-1333,1066&800 | 1N       | Empty | Empty       | Single-rank |

| 2                       | DDR3-1333,1066&800 | 1N       | Empty | Empty       | Dual-rank   |

| 3                       | DDR3-1066&800      | 2N       | Empty | Single-rank | Single-rank |

| 4                       | DDR3-1066&800      | 2N       | Empty | Single-rank | Dual-rank   |

| 5                       | DDR3-1066&800      | 2N       | Empty | Dual-rank   | Single-rank |

| 6                       | DDR3-1066&800      | 2N       | Empty | Dual-rank   | Dual-rank   |

Table 7. RDIMM Population Configurations (Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5600 series only) for three slots per Channel

| Configuration<br>Number | POR Speed      | 1N or 2N | DIMM3 | DIMM2       | DIMM1       |

|-------------------------|----------------|----------|-------|-------------|-------------|

| 1                       | DDR3L-1066&800 | 1N       | Empty | Empty       | Single-rank |

| 2                       | DDR3L-1066&800 | 1N       | Empty | Empty       | Dual-rank   |

| 3                       | DDR3L-800      | 1N       | Empty | Empty       | Quad-rank   |

| 4                       | DDR3L-800      | 1N       | Empty | Dual-rank   | Single-rank |

| 5                       | DDR3L-800      | 1N       | Empty | Single-rank | Dual-rank   |

| 6                       | DDR3L-800      | 1N       | Empty | Dual-rank   | Single-rank |

| 7                       | DDR3L-800      | 1N       | Empty | Dual-rank   | Dual-rank   |

Table 8. UDIMM Population Configurations (Intel® Xeon® Processor 5600 series only) for three slots per Channel

| Configuration<br>Number | POR Speed      | 1N or 2N | DIMM3 | DIMM2       | DIMM1       |

|-------------------------|----------------|----------|-------|-------------|-------------|

| 1                       | DDR3L-1066&800 | 1N       | Empty | Empty       | Single-rank |

| 2                       | DDR3L-1066&800 | 1N       | Empty | Empty       | Dual-rank   |

| 3                       | DDR3L-800      | 1N       | Empty | Single-rank | Single-rank |

| 4                       | DDR3L-800      | 1N       | Empty | Single-rank | Dual-rank   |

| 5                       | DDR3L-800      | 1N       | Empty | Dual-rank   | Single-rank |

| 6                       | DDR3L-8000     | 1N       | Empty | Dual-rank   | Dual-rank   |

#### Channel Population Rules for Memory RAS Mode Configuration

Different RAS mode used comes with different rules on channel population. No matter what RAS mode it is, the requirements for populating within a channel should follow the RDIMM/UDIMM slots configurations in a channel at all times. RAS modes that demands matching DIMM population between channels (Sparing, Mirroring, Lockstep) require that ECC DIMMs be populated.

For RAS modes that require matching populations, the same slot positions across channels must hold the same DIMM type with regards to size and organization. DIMM timings do not have to match but timings will be lowered down due to slower timings.

The following modes are supported in the system.

Independent Mode

Channels can be populated in any order in Independent Channel Mode--there are no matching requirements. All channels must run at the same interface frequency but individual channels may run at different DIMM timings (RAS latency, CAS latency, and so forth).

#### Mirrored Channel Mode

Three Channels under Mirrored Channel Mode, only Channel 0 and Channel 1 are used. The memory contents are mirrored between Channel 0 and 1. That means the total physical memory available to the server would appear as only half of what is populated. DIMMs populated in Channel 0 and Channel 1 must be identical with regards to size and organization. Within a channel, the DIMM slot population could be in any order, but the same DIMM slot location across Channel 0 and Channel 1 must be populated the same.

#### Lockstep Channel Mode

In Lockstep Channel Mode, each memory access is a 128-bit data access that spans Channel 0 and Channel 1. Lockstep Channel mode is the only RAS mode that supports x8 SDDC. Lockstep Channel Mode requires that Channel 0 and Channel 1 must be populated identically with regards to size and organization. DIMM slot populations within a channel do not have to be identical but the same DIMM slot location across Channel 0 and Channel 1 must be populated the same. Channel 2 is unused in Lockstep Channel Mode.

## 3.4 Graphics Controller

The system board implements the Pilot-II ServerEngines \* ASIC and the Graphics controller features list as:

- Graphics Controller

- Integrated Graphics Core

- 2D Hardware Graphics Acceleration

- DDR2 memory interface supports up to 128 Mbytes of memory

- Supports all display resolutions up to 1600 x 1200 16 bpp at 75 Hz

- High speed Integrated 24-bit RAMDAC

- Single lane PCI-Express\* host interface

## 3.5 IO Boards support

The system board supports one IO board. For more detailed information, refer to the IO board information in Chapter 6.

## 3.6 System Management

The system management sub-system is based on Pilot-II using for Baseboard Management Controller (BMC) for the motherboard. The system management is IPMI2.0 compliant. The Sever Management Controller (Pilot-II) facilitates the system management being accessible. .It is a highly integrated single-chip solution, integrating several devices typically found servers. Pilot-II is mainly targeted at next generation servers, and provides a highly integrated server class product. The following functionality is integrated into Pilot-II:

- Server Class Super I/O function

- Baseboard Management Controller

- Graphics Controller

# 4. Power Subsystem

The power sub-system is designed to configure one single 1100-W Power Supply (PS) module with an integrated Power Distribution Board.

This chapter provides technical details on the operation of the power supply module and power sub-system.

# 4.1 Power Supply Mechanical Overview

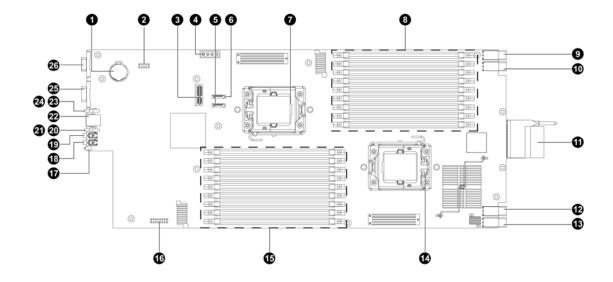

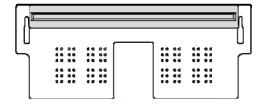

Figure 7. Power Supply Module Dimensional Drawing

# 4.1.1 Output Connection (Card Edge)

Output connector is card edge extension of PCB and blind mates with 32 positions each side (Tyco 1761469(vertical) and 1761468(right angle) or FCI pn 10046971-100LF (vertical) and 10053363-200LF (right angle)

**Table 9 DC output Top Side connection**

| PCB Top Side |                |                |                      |

|--------------|----------------|----------------|----------------------|

| Pin#         | Signal Name    | Amps/PinRating | Application Usage    |

| 53-64        | +12V           | 5.5 A rms      | 90A / 24pins = 3.75A |

| 41-52        | RTN            | 5.5 A rms      | 90A / 24pins = 3.75A |

| 40           | Remote Sense + | 5.5 A rms      | <100mA               |

| 39           | 12v_SB         | 5.5 A rms      | Standby = 2A rms     |

| 38           | PS_A0          | 5.5 A rms      | <100mA               |

| 37           | POK            | 5.5 A rms      | <100mA               |

| 36           | Return         | 5.5 A rms      | <100mA               |

| 35           | SCL            | 5.5 A rms      | Short Pin <100mA     |

| 34           | -PS_Present    | 5.5 A rms      | Short Pin <100mA     |

| 33           | SDA            | 5.5 A rms      | Short Pin <100mA     |

#### .Table 10 DC Output Connection (Card Edge)

| PCB Bottom Side |              |                |                              |

|-----------------|--------------|----------------|------------------------------|

| Pin#            | Signal Name  | Amps/PinRating | Application Usage            |

| 1-12            | +12V         | 5.5 A rms      | 90A / 24pins = 3.75A         |

| 13-24           | RTN          | 5.5 A rms      | 90A / 24pins = 3.75A         |

| 25              | Tach         | 5.5 A rms      | <100mA                       |

| 26              | Remote Sense | 5.5 A rms      | <100mA                       |

| 27              | Vin_Good     | 5.5 A rms      | See Exception #1<br>(<100mA) |

| 28              | Cshare       | 5.5 A rms      | <100mA                       |

| 29              | -PS_On       | 5.5 A rms      | <100mA                       |

| 30              | PS_Kill      | 5.5 A rms      | (Short Pin)<100mA            |

| 31              | Reset        | 5.5 A rms      | (Short Pin)<100mA            |

| 32              | Alert        | 5.5 A rms      | (Short Pin)<100mA            |

# 4.2 Power system component and Connector Overview

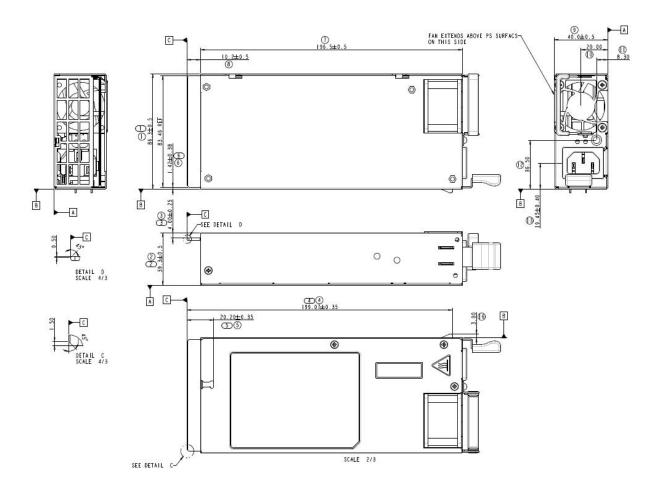

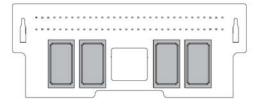

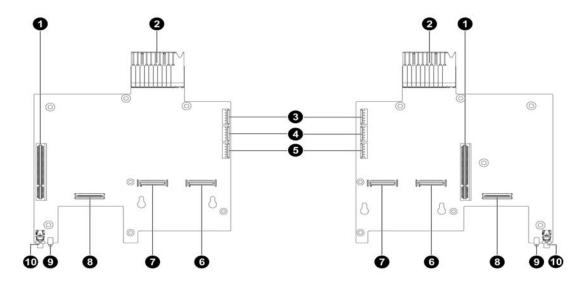

A power distribution board (PDB) provides a connection between the power supply and two server boards. The PDB is shown below:

Figure 8. Power Distribution Board Connector

| Power Supply Slot        | Power Connector 3 (J3)   |

|--------------------------|--------------------------|

| 2 Power Connector 1 (J5) | 9 Power Connector 4 (J2) |

| 3 Power Connector 2 (J4) |                          |

# 4.2.1 Power Distribution Board Connector to Power supply (J1)

Figure 9. PDB Connector to Power Supply

Table 11. Pin Definition of PDB Connector to Power Supply

| Signal Name | Pin | Pin | Signal Name |

|-------------|-----|-----|-------------|

| P12V        | 1   | 33  | I2C_SDA_PS  |

| P12V        | 2   | 34  | PS_PRSNT_N  |

| P12V        | 3   | 35  | I2C_SCL_PS  |

| P12V        | 4   | 36  | Ground      |

| P12V        | 5   | 37  | PGD_PS      |

| Signal Name  | Pin | Pin | Signal Name |

|--------------|-----|-----|-------------|

| P12V         | 6   | 38  | PS_ADD_A0   |

| P12V         | 7   | 39  | P12V_STBY   |

| P12V         | 8   | 40  | RMT_SNS_DP  |

| P12V         | 9   | 41  | Ground      |

| P12V         | 10  | 42  | Ground      |

| P12V         | 11  | 43  | Ground      |

| P12V         | 12  | 44  | Ground      |

| Ground       | 13  | 45  | Ground      |

| Ground       | 14  | 46  | Ground      |

| Ground       | 15  | 47  | Ground      |

| Ground       | 16  | 48  | Ground      |

| Ground       | 17  | 49  | Ground      |

| Ground       | 18  | 50  | Ground      |

| Ground       | 19  | 51  | Ground      |

| Ground       | 20  | 52  | Ground      |

| Ground       | 21  | 53  | P12V        |

| Ground       | 22  | 54  | P12V        |

| Ground       | 23  | 55  | P12V        |

| Ground       | 24  | 56  | P12V        |

| FAN_TACH     | 25  | 57  | P12V        |

| RMT_SNS_DN   | 26  | 58  | P12V        |

| VIN_GOOD     | 27  | 59  | P12V        |

| PS_CSHARE    | 28  | 60  | P12V        |

| PS_ON_N      | 29  | 61  | P12V        |

| PS_KILL      | 30  | 62  | P12V        |

| RST_PS_N     | 31  | 63  | P12V        |

| I2C_ALERT_PS | 32  | 64  | P12V        |

## 4.2.2 Power Distrubution Board (PDB) Connectors to Sever board (J2, J3, J4, J5)

There are four connectors from the PDB to the server board. Connectors designated J2 and J4 share the same pin definition while J3 and J5 share the same pin definition.

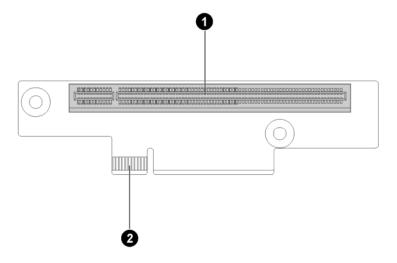

Figure 10. PDB Connectors to Server Board

Table 12. Pin Definition of PDB Connectors to Motherboard (J2, J4)

| Signal Name | Pin | Pin | Signal Name |

|-------------|-----|-----|-------------|

| Ground      | A1  | B1  | P12V        |

| Ground      | A2  | B2  | P12V        |

Table 13. Pin Definition of PDB Connectors to Mohterboard (J3, J5)

| Signal Name | Pin | Pin | Signal Name |

|-------------|-----|-----|-------------|

| I2C_SDA_PS  | A1  | B1  | 2C_SCL_PS   |

| Ground      | A2  | B2  | P12V        |

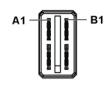

#### 4.2.3 Server Board Power Connectors

There are four power connectors on one server board and they have the same pin definition.

**Figure 11. Server Board Power Connectors**

Table 14. Pin Definition of Server Board Power Connectors (J2, J4)

| Signal Name | Pin | Pin | Signal Name |

|-------------|-----|-----|-------------|

| Ground      | A1  | B1  | P12V_PS     |

| Ground      | A2  | B2  | P12V_PS     |

Table 15. Pin Definition of Server Board Power Connectors (J3)

| Signal Name | Pin | Pin | Signal Name |

|-------------|-----|-----|-------------|

| Ground      | A1  | B1  | I2C_SCL_PS  |

| Ground      | A2  | B2  | P12V_PS     |

Table 16. Pin Definition of Server Board Power Connectors (J5)

| Signal Name | Pin | Pin | Signal Name |

|-------------|-----|-----|-------------|

| Ground      | A1  | B1  | NC          |

| Ground      | A2  | B2  | P12V_PS     |

# 4.3 AC Input Requirements

# 4.3.1 AC Input Voltage Range

**Table 17. AC Input Voltage Specification**

| Parameter Description   | Min | Тур     | Max  | Units | MFR Test 1 |

|-------------------------|-----|---------|------|-------|------------|

| Vin (Voltage 1st Range) | 90  | 115/230 | 264  | Vrms  | Yes        |

| Vin (Voltage 2nd Range) | -   | N/A     |      | Vrms  | Х          |

| Vin (frequency)         | 47  | 50/60   | 63   | Hz    | Yes        |

| lin (90VAC)             | -   | -       | 14.0 | Arms  | Yes        |

| lin(100VAC)             | -   | -       | 12.0 | Arms  | -          |

| lin (180VAC)            | -   | -       | 7.0  | Arms  | Yes        |

| Vin (turn-on)           | 85  | -       | 90   | Vrms  | Yes        |

| Vin (turn-off)          | 80  | -       | 85   | Vrms  | Yes        |

| Max Input Power         | -   | -       | 1400 | Watts | Yes        |

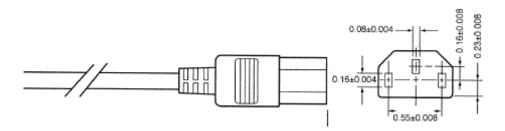

## 4.3.2 AC Power Cord Specification Requirements

The AC power cord used must meet the minimum specification requirements listed in the following table.

Cable Type SVT

Wire Size 18 AWG

Temperature Rating 60°C

Amperage Rating 10 A

Voltage Rating 125 V

**Table 18. AC Power Cord Specification**

Figure 12. AC Power Cord

## 4.3.3 Efficiency

The power supply meets recommended efficiency levels at various conditions as discussed in the following table, tested over the full-specified AC input voltage range.

Table 19. Efficiency

| 115VAC Input Voltage | Minimum Efficiency (%) |

|----------------------|------------------------|

| 20% Loading          | 87                     |

| 50% Loading          | 90                     |

| 100% Loading         | 87                     |

| 230VAC Input Voltage | Minimum Efficiency (%) |

| 10% Loading          | 80                     |

| 20% Loading          | 88                     |

| 50% Loading          | 92                     |

| 100% Loading         | 88                     |

#### 4.3.4 AC Input Voltage Specification

The power supply must operate within all specified limits over the input voltage range shown in the following table.

Table 20. AC Input Rating

| Parameter             | Minimum              | Rated                    | Maximum              | Startup<br>VAC | Power-off<br>VAC | Maximum Input<br>AC Current         |

|-----------------------|----------------------|--------------------------|----------------------|----------------|------------------|-------------------------------------|

| Line Voltage<br>(110) | 90 V <sub>rms</sub>  | 100-115 V <sub>rms</sub> | 140 V <sub>rms</sub> | 85VAC          | 80VAC            | 12 A <sub>rms</sub> <sup>1,3</sup>  |

| Line Voltage<br>(220) | 180 V <sub>rms</sub> | 200-230 V <sub>rms</sub> | 264 V <sub>rms</sub> | 90VAC          | 85VAC            | 7.0 A <sub>rms</sub> <sup>2,3</sup> |

| Frequency             | 47 Hz                | 50/60 Hz                 | 63 Hz                | -              | -                | -                                   |

#### Notes:

- 1. Maximum input current at low input voltage range is measured at 90 VAC, at maximum load.

- 2. Maximum input current at high input voltage range is measured at 180 VAC, at maximum load.

- 3. This is not to be used for determining agency input current markings.

- 4. Maximum rated input current is measured at 100 VAC and 200 VAC.

Harmonic distortion of up to 10% of the rated AC input voltage must not cause the power supply to go out of specified limits. The power supply powers off on or after/below 75 VAC  $\pm$  5 VAC range. The power supply starts up on or before/above 85 VAC  $\pm$  4 VAC. Application of an input voltage below 85 VAC does not cause damage to the power supply or blow a fuse.

### 4.3.5 AC Line Dropout / Holdup

Table 21. AC Line Dropout / Holdup

| Parameter Description            | Min | Тур | Max | Units                  |

|----------------------------------|-----|-----|-----|------------------------|

| AC Line Dropout                  | 12  | -   | -   | msec                   |

| Dropout Loading Conditions       | -   | 100 | -   | %max<br>output<br>load |

| Hold-up Time Applicable Voltages | 90  | -   | 264 | Vrms                   |

| Hold-up Time Duration            | 12  | -   | -   | Msec                   |

#### 4.3.6 AC Line Leakage Current

The maximum leakage current to ground for each power supply is not more than 3.5 mA when tested at 254 VAC/60HZ.

#### 4.3.7 AC Inrush

Table 22. AC In-rush

| Parameter Description     | Max | Units      |

|---------------------------|-----|------------|

| Initial In-rush Current   | 55  | Amps(peak) |

| Secondary In-rush Current | 35  | Amps(peak  |

#### 4.3.8 Power Factor Correction

The power supply incorporates a Power Factor Correction circuit. The power factor is 0.98 at 230VAC input voltages and >=90% load.

# 4.4 DC Output Specification

The following provides a summary of specifications for each individual output. These requirements apply under all conditions unless otherwise stated. Note that maximum continuous total output power should not 1024 W at Low Line and 100W at High line.

#### 4.4.1 Output Power / Currents

The following table defines the power requirements for the power supply module.

**Table 23. Power Supply Module Load Ratings**

|                      | 1100 W  |            |      |

|----------------------|---------|------------|------|

| Voltage              | Minimum | Maximum    | Peak |

| +12 V <sup>2,4</sup> | 1 A     | 89.6 A     | 105A |

|                      |         | (83.25,low |      |

|               | 1100 W  |         |       |  |  |

|---------------|---------|---------|-------|--|--|

| Voltage       | Minimum | Maximum | Peak  |  |  |

|               |         | line)   |       |  |  |

| Standby 1,2,4 | 0 A     | 2.00 A  | 2.7 A |  |  |

#### Notes:

- 1. Peak standby current specification is only valid during the ramp up from 0V to the point where standby is within regulation. (250 mS)

- 2. Peak +12V output power not to exceed 100 mS seconds in duration. Maximum duty cycle is 5%.

- 3. +12V rail at loading conditions of 0 A to 1 A must comply with all +12V specification parameters except for load regulation.

- 4. Max current ratings based on a nominal 12.0 V main and standby rail with a remote sense voltage compensation of 0 V.

#### 4.4.2 Output Voltage Regulation

The power supply output voltages must stay within the voltage limits defined in the following table when operating at steady state and dynamic loading conditions. These limits include the peak-peak ripple/noise. All outputs are measured with reference to the return remote sense signal (ReturnS). The +12 V and +12 VSB voltages are measured at the PDB output harness connector.

| Output   | Minimum | Normal | Maximum | Units |

|----------|---------|--------|---------|-------|

| + 12 V   | +11.64  | +12.00 | +12.60  | Volts |

| + 12 VSB | +11 40  | +12 00 | +12 60  | Volts |

**Table 24. Voltage Regulation Limits**

Note: Min and Max regulation limits represent absolute limits. Under normal operating conditions (static or dynamic), the +12V rail or standby exceeds these limits.

#### 4.5 Protection Circuits

Protection circuits inside the PDB (and the power supply) shall cause only the power supply's main outputs to shutdown. The microprocessor and its I²C communication bus is expected to continue operational. 12VSB output shall remain powered on if the failure does not involve this output. When a protection circuit shuts down the power supply, the green LED shall change to unlighted status and the PS OK signal shall be asserted LOW. If the power supply latches off due to a protection circuit tripping, AC input or PSON# signal toggle shall release latch condition and the power supply shall attempt to provide output power to the load. Minimum time delay for the toggle function shall be AC input OFF for 15sec, PSON# cycle HIGH for 1sec. Power to Micro controller circuitry associated with I²C communication to the system shall be logic OR between internal source and system side 12 Vsb.

## 4.5.1 Over-current Protection (OCP)

Power supply provides limited output current to the load for protecting the power supply from damage under indefinite over load conditions. Table 25 describes output minimum and maximum current levels required from each output during an overload condition. 12 V over current protection is the current type. Over-current limit level is maintained for a period of 1 sec. minimum and 2 sec. maximum. After this time the power supply latches off. The latch is cleared

by toggling PSON# signal or by an AC input re-cycle. A sustained overload should not latch off 12SB output. Over current limit level shall be maintained for a period of 100 msec. minimum and 500 msec maximum for 12 VSB.

**Table 25. Over Current Limits (Lout Limit)**

| Output Voltage | Min OCP Trip Limits | Max OCP Trip Limits |  |

|----------------|---------------------|---------------------|--|

| +12V           | 120%                | 150%                |  |

| +12VSB         | 3.5A                | 5A                  |  |

#### 4.5.2 Over-voltage Protection (OVP)

Each DC/DC converter output on PDB has individual OVP protection circuits built-in and is locally sensed. The PS+PDB combo shuts down and latches off when an over-voltage condition occurs. This latch is cleared by toggling the PSON# signal or by an AC power interruption. Table 26 contains the over voltage limits. The values are measured at the PDB harness connectors. The voltage cannot exceed the maximum levels when measured at the power pins of the output harness connector during any single point of fail. The voltage cannot trip any lower than the minimum levels when measured at the power pins of the PDB connector.

Table 26. Over-voltage Limits

| Output Voltage | OVP MIN | OVP MAX |

|----------------|---------|---------|

| +12V           | 13.6    | 15.0    |

| +12VSB         | 13.6    | 15.0    |

#### 4.5.3 Over-temperature Protection (OTP)

The power supply shall be protected against over temperature conditions caused by loss of fan cooling or excessive ambient temperature which could cause internal part/s failures. In an over temperature condition the PS shall shutdown. The Standby output shall not shut down during an OTP condition on the main outputs. When the temperature drops to within safe operating limit for internal parts, the power supply shall restore power automatically. The OTP circuit shall incorporate built-in hysteresis such that the power supply does not oscillate on and off due to temperature recovering condition. The power supply shall alert the system of the OTP condition through the power supply DC OK signal changing to a false state and the green LED changing to an unlighted condition. The OTP condition shall be stored in a register for troubleshooting purposes.

## 4.6 Power Supply LED

The power supply module has a single green LED to indicate power supply status. The LED light green indicates +12V is output, if the LED does not light, it indicates no AC on or no main power on. The LED is visible on the rear panel of the power supply module.

# 5. Cooling Subsystem

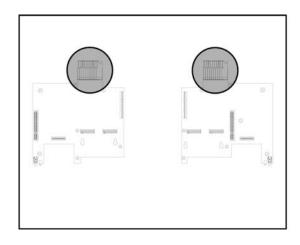

The chassis cooling system, designed in a 35 C maximum environment, consists of several components. These include one set of three system fans, air ducts, and one fan of power supply. Three key essential components shape out the complete and sound thermal solution provided for the chassis.

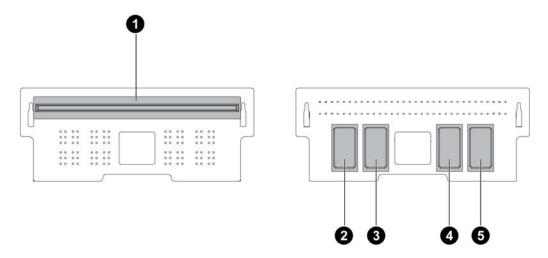

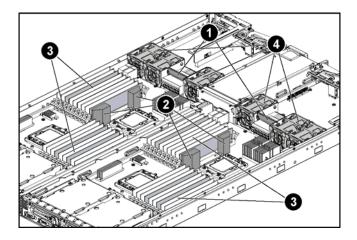

### 5.1 System Fan Module and Air Ducts

The system fan, three on each IO board, is a 40x40x56 mm non-hot-swappable module.

Three kinds of air ducts are built into the system and are designed to isolate and direct air flow to the main components. For which components these air ducts aid, refer to the zones of processor, DIMM, and HDDs. One is located on the IO board module; one is located between processor1 and according to DIMM group1. The third kind of air duct consists of blank DIMMs inserted in DIMM slots.

The air ducts intensify the air flow being emphasized on the fore-mentioned main zones in case the event of a single fan/motor occurs. The two sets of system fans would be boosted according the BMC's commands to provide sufficient cooling for the system and can hold for a while until the out-of-order fan/motor is replaced. However, acoustic noise will reach the maximum due to the highest speed operated on the remaining fans. The noise is also another reminder to you of a potentially harmful fan condition and instant component replacement.

Figure 13. System Fans and Air Ducts

There are temperature sensors designed to locate around selective main components on the motherboard to monitor crucial components and the ambient temperature for the system. The BMC generates information parameters detected by temperatures sensors and carries out adequate management over the thermal limits control. The most known parameter is the fan's RPM (revolutions per minute). The BMC adjusts the fan speeds to the RPM and, if the temperature exceeds the regulated thermal limits, the BMC sends out log errors to the System Event Log (SEL) in order to report the abnormality.

The third cooling solution is one 40x40x28 mm power fan inside the 1100-W single power supply module. This fan generates cooling air from the back and provides the power system ideal thermal condition. It acts to provide appropriate cooling to the power module and maintain the stability of system temperature within the specified range set by the BMC.

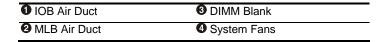

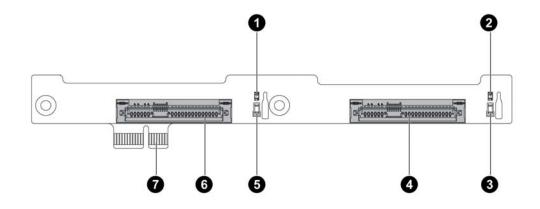

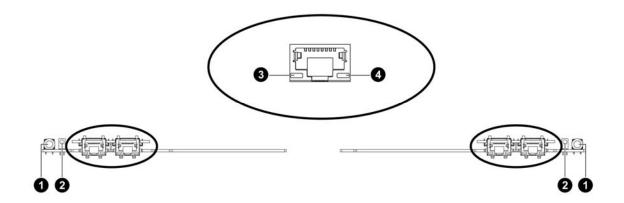

### 5.2 System Fan Connectors

System fan connectors on the two IO boards have different designators. Connectors on the left IO board are designated as J6, J7, and J8; while on the right IO board, they are J7, J8, and J9. Two J7 connectors share the same pin definition: J6 connector on left IO board and J8 connector on right IO board share the same pin definition; while the J8 connector on the left IO board and J9 connector on the right IO board share the same pin definition.

Figure 14. System Fan Connectors for IOB

Table 27. System Fan Connector Pin Definition (J7)

| Pin | Signal Name    |  |  |

|-----|----------------|--|--|

| 1   | FAN_BMC_TACH0  |  |  |

| 2   | FAN_BMC_PWM0_R |  |  |

| 3   | FAN_BMC_TACH3  |  |  |

| 4   | P12V           |  |  |

| 5   | Ground         |  |  |

| 6   | P12V           |  |  |

Table 28. Fan Connectors Pin Definition (J6, J8 – J6 on Left IO Board / J8 on Right IO Board)

| Pin | Signal Name    |  |  |

|-----|----------------|--|--|

| 1   | FAN_BMC_TACH2  |  |  |

| 2   | FAN_BMC_PWM1_R |  |  |

| 3   | FAN_BMC_TACH5  |  |  |

| 4   | P12V           |  |  |

| 5   | Ground         |  |  |

| 6   | P12V           |  |  |

Table 29. Fan Connectors Pin Definitions (J8, J9 – J8 on Left IO Board / J9 on Right IO Board)

| Pin | Signal Name    |

|-----|----------------|

| 1   | FAN_BMC_TACH1  |

| 2   | FAN_BMC_PWM0_R |

| 3   | FAN_BMC_TACH4  |

| 4   | P12V           |

| 5   | Ground         |

| 6   | P12V           |

# 6. System Board Interconnects

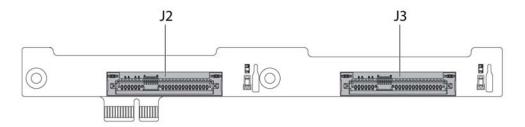

System boards within the system include an IO board, hard drive backplane, and PCI riser board. This chapter describes the interconnect features of each and defines the pin-outs for each of their connectors. Later chapters describe the functional details of each system board.

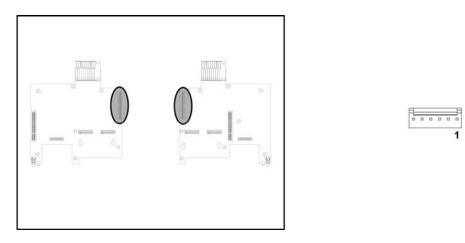

#### 6.1 IO Board

IO boards are designed to specify NIC functionality. The main IO functions are listed:

- Connection between motherboard and riser card

- Connection between motherboard and NIC board

- PCI-E connection