# Intel® Server Board S870BN4 Board Set

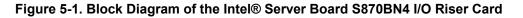

**Technical Product Specification**

**Revision 2.5**

June, 2003

**Enterprise Platforms and Services Division**

## **Revision History**

| Date       | Revision<br>Number | Modifications                      |

|------------|--------------------|------------------------------------|

| June, 2003 | 2.5                | Initial release to external users. |

|            |                    |                                    |

### Disclaimers

THIS SPECIFICATION [DOCUMENT] IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE. Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

The Intel® Server Board S870BN4 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and Itanium are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation 2003.

## Table of Contents

| 1. | Intr | oduction                                   | 1-1  |

|----|------|--------------------------------------------|------|

| 2. | Pro  | ocessor Baseboard                          | 2-1  |

| 2  | 2.1  | Features                                   | 2-1  |

| 2  | 2.2  | Chapter Structure and Outline              | 2-1  |

| 2  | 2.3  | Introduction                               | 2-2  |

|    | 2.3. | .1 Block Diagram                           | 2-4  |

|    | 2.3. | .2 Placement Diagram                       | 2-5  |

| 2  | 2.4  | Functional Architecture                    | 2-6  |

|    | 2.4. | .1 Itanium 2 Front Side Bus (FSB)          | 2-6  |

|    | 2.4. | .2 Memory Interface                        | 2-7  |

|    | 2.4. | .3 Scalability Port I/O Bus Interface      | 2-8  |

|    | 2.4. | .4 Clock Distribution                      | 2-8  |

|    | 2.4. | .5 Voltage Regulators                      | 2-10 |

|    | 2.4. | .6 Power Good/Reset Control                | 2-14 |

|    | 2.4. | .7 Programmable Logic Devices              | 2-18 |

|    | 2.4. | .8 Configuring Baseboard Jumpers           | 2-28 |

|    | 2.4. | .9 Server Management Block                 | 2-29 |

|    | 2.4. | .10 I <sup>2</sup> C* Address Map          | 2-30 |

|    | 2.4. | .11 Debug Port/In-Target Probe (ITP)       | 2-34 |

|    | 2.4. | .12 ISP interface                          | 2-36 |

|    | 2.4. | .13 Firmware Hub                           | 2-37 |

| 2  | 2.5  | Signal Descriptions                        | 2-38 |

|    | 2.5. | .1 Itanium® 2 Processor System Bus Signals | 2-39 |

| 2.5.2   | Scalability Port (SP) Bus Signals                      | 2-39 |

|---------|--------------------------------------------------------|------|

| 2.5.3   | Memory Interface Signals                               | 2-39 |

| 2.5.4   | Server Management Interface Signals                    | 2-40 |

| 2.5.5   | Power Connection                                       |      |

| 2.6 El  | ectrical, Mechanical, and Environmental Specifications | 2-41 |

| 2.6.1   | Electrical Specifications                              | 2-41 |

| 2.6.2   | Mechanical Specifications                              | 2-50 |

| 2.6.3   | Processor Retention Mechanism                          |      |

| 2.6.4   | Thermal Requirements                                   | 2-54 |

| 2.6.5   | Quality and Reliability Target                         | 2-54 |

| 3. Memo | ry Module                                              | 3-1  |

| 3.1 Ov  | verview                                                | 3-1  |

| 3.2 Fu  | nctional Architecture                                  |      |

| 3.2.1   | DDR Memory Array                                       |      |

| 3.2.2   | DMH                                                    | 3-9  |

| 3.2.3   | System Management Interface                            | 3-9  |

| 3.2.4   | Embedded 2.5-V to 1.25-V D2D                           |      |

| 3.3 Si  | gnal Descriptions                                      |      |

| 3.3.1   | Rambus Signals                                         |      |

| 3.3.2   | DDR Signals                                            |      |

| 3.3.3   | Miscellaneous Signals                                  |      |

| 3.3.4   | Voltage References                                     |      |

| 3.4 Ele | ectrical, Mechanical, and Environmental Specifications | 3-12 |

| 3.4.1   | Absolute Maximum Ratings                               |      |

| 3.4.2   | Thermal                                                |      |

|    | 3.4 | .3   | Memory Board Thermal Requirements              | 3-13 |

|----|-----|------|------------------------------------------------|------|

|    | 3.4 | .4   | Electrical                                     | 3-13 |

|    | 3.4 | .5   | Voltage Tolerances                             | 3-13 |

|    | 3.4 | .6   | Mechanical                                     | 3-15 |

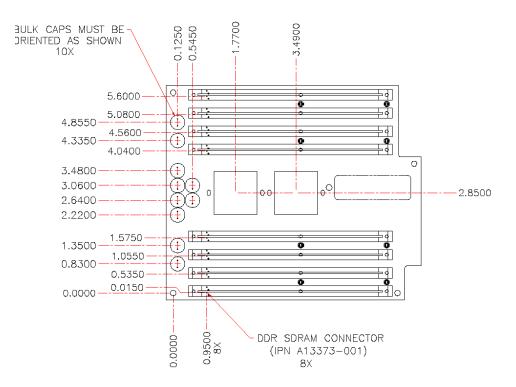

|    | 3.4 | .7   | Connectors                                     | 3-16 |

| 4. | 4-V | Vay  | / I/O Board                                    | 4-1  |

| 4  | 4.1 | Fea  | atures                                         | 4-1  |

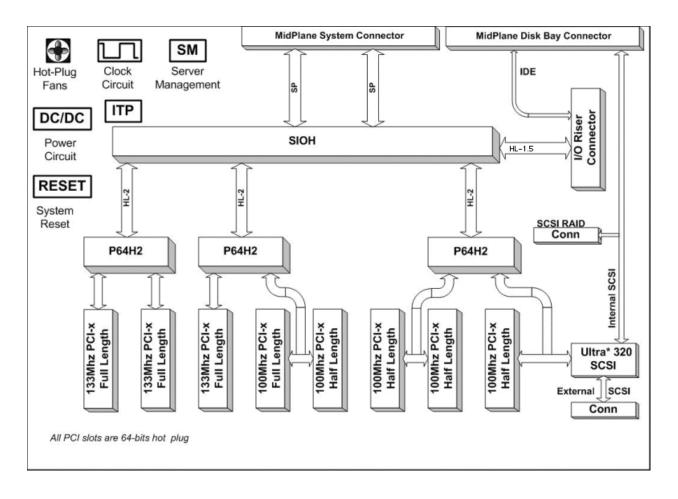

| 4  | 4.2 | Arc  | chitectural Overview                           | 4-1  |

| 4  | 4.3 | Bu   | ses and Interfaces                             | 4-3  |

|    | 4.3 | 5.1  | Midplane System Interface                      | 4-3  |

|    | 4.3 | 5.2  | Midplane Disk Bay Interface                    | 4-3  |

|    | 4.3 | 5.3  | Peripheral Component Interconnect (PCI) Busses | 4-3  |

|    | 4.3 | 6.4  | I/O Riser Board Interface                      | 4-4  |

|    | 4.3 | 5.5  | Hot-Plug Fan Interface                         | 4-4  |

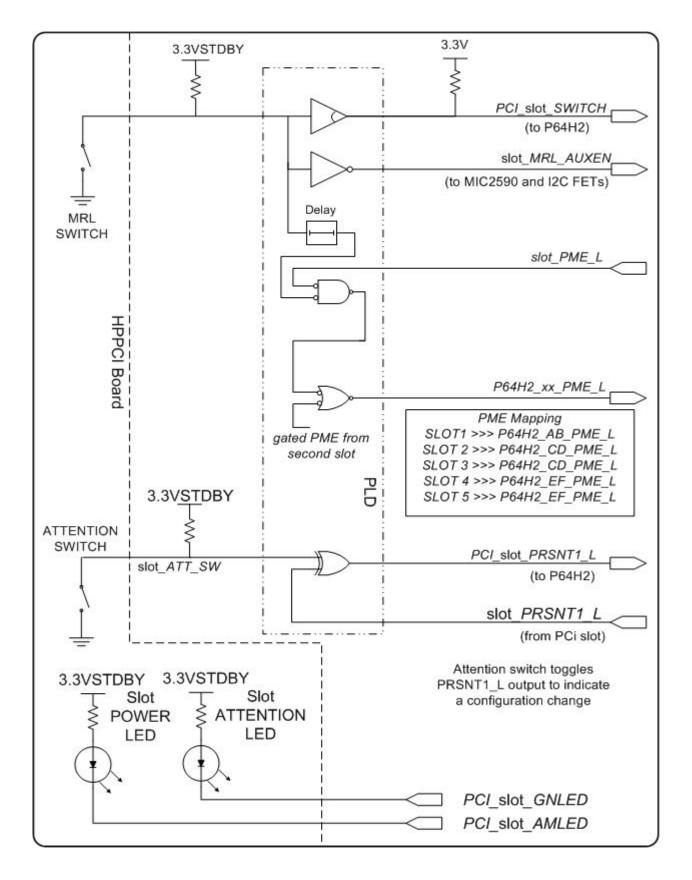

|    | 4.3 | 6.6  | PCI Power Management Interface                 | 4-4  |

|    | 4.3 | 5.7  | PCI Hot Plug Control Interface                 | 4-5  |

|    | 4.3 | 8.8  | D2D Power Interface                            | 4-5  |

|    | 4.3 | 9.9  | Hardware Status Interface                      | 4-5  |

|    | 4.3 | 5.10 | In-Target Probe (ITP) Interface                | 4-5  |

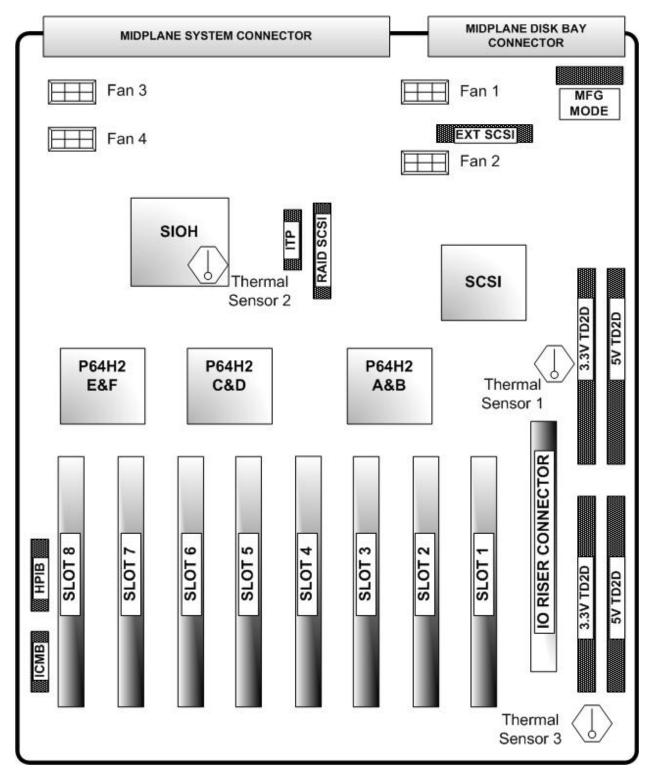

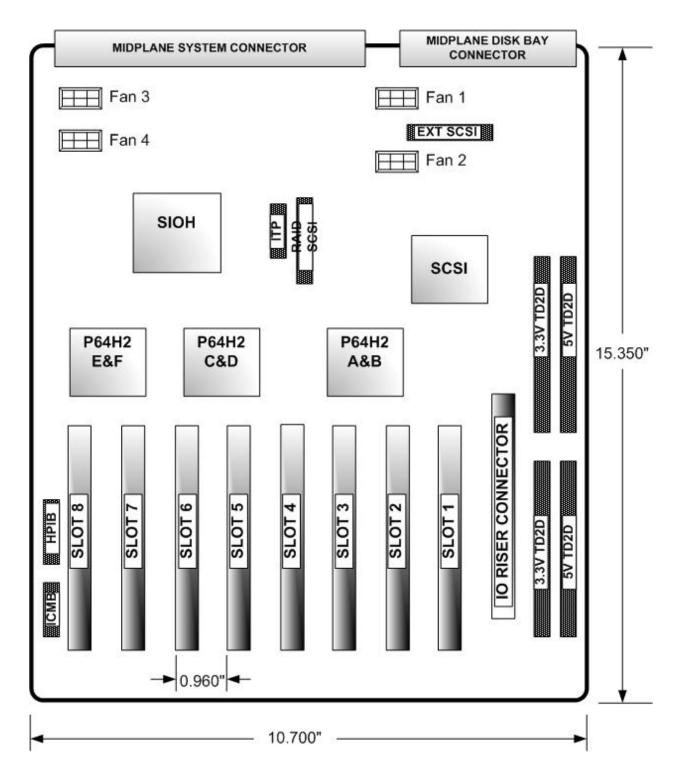

|    | 4.4 | Pla  | acement Diagrams                               | 4-5  |

|    | 4.5 | Fu   | nctional and Logical Blocks                    | 4-7  |

|    | 4.5 | 5.1  | Midplane Interface                             | 4-7  |

|    | 4.5 | 5.2  | Server I/O Hub (SIOH)                          | 4-11 |

|    | 4.5 | 5.3  | P64H2                                          | 4-12 |

|    | 4.5 | 5.4  | PCI Busses                                     | 4-12 |

|    | 4.5.5   | PCI Hot-Plug Interface               | . 4-18 |

|----|---------|--------------------------------------|--------|

|    | 4.5.6   | PCI Power Management Interface       | . 4-22 |

|    | 4.5.7   | SCSI Interface                       | . 4-24 |

|    | 4.5.8   | IDE Interface                        | . 4-26 |

|    | 4.5.9   | I/O Riser Interface                  | . 4-27 |

|    | 4.5.10  | Server Management Functions          | . 4-30 |

|    | 4.5.11  | In-System Programming Bus            | . 4-38 |

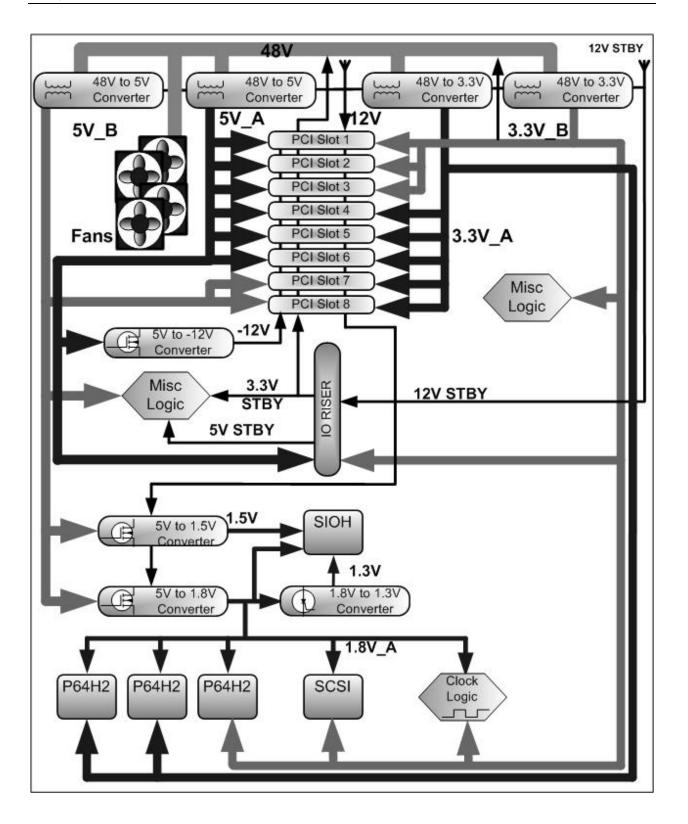

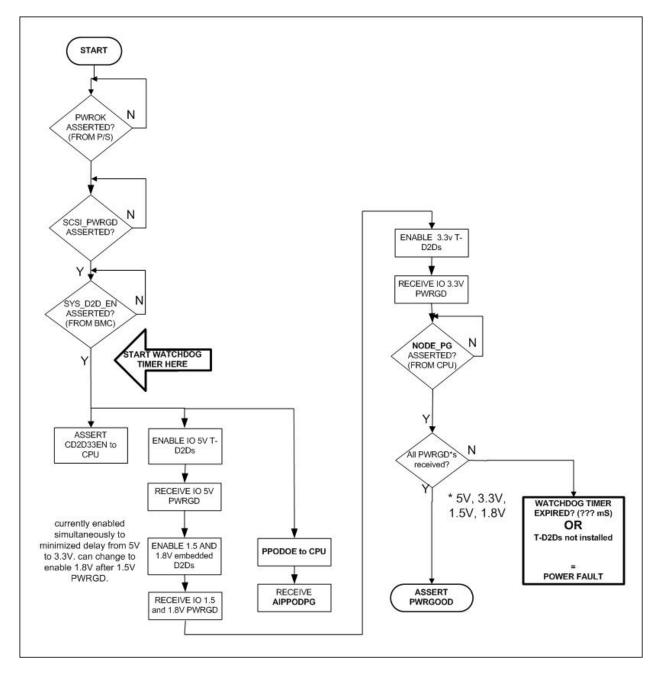

|    | 4.5.12  | Power System                         | . 4-39 |

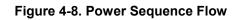

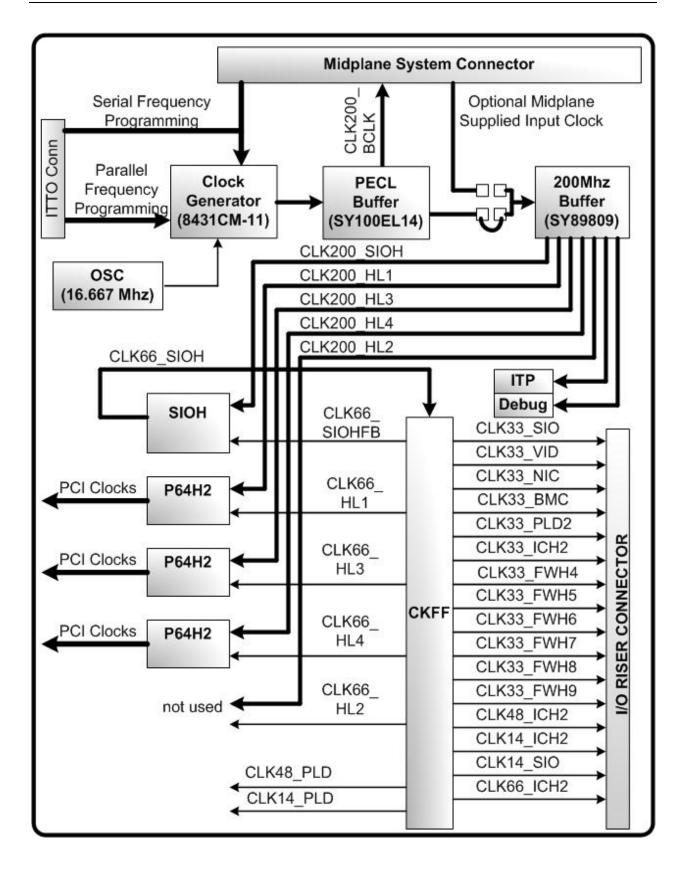

|    | 4.5.13  | Clock Generation Logic               | . 4-47 |

|    | 4.5.14  | Reset Generation Logic               | . 4-51 |

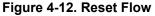

|    | 4.5.15  | Interrupts and Errors                | . 4-53 |

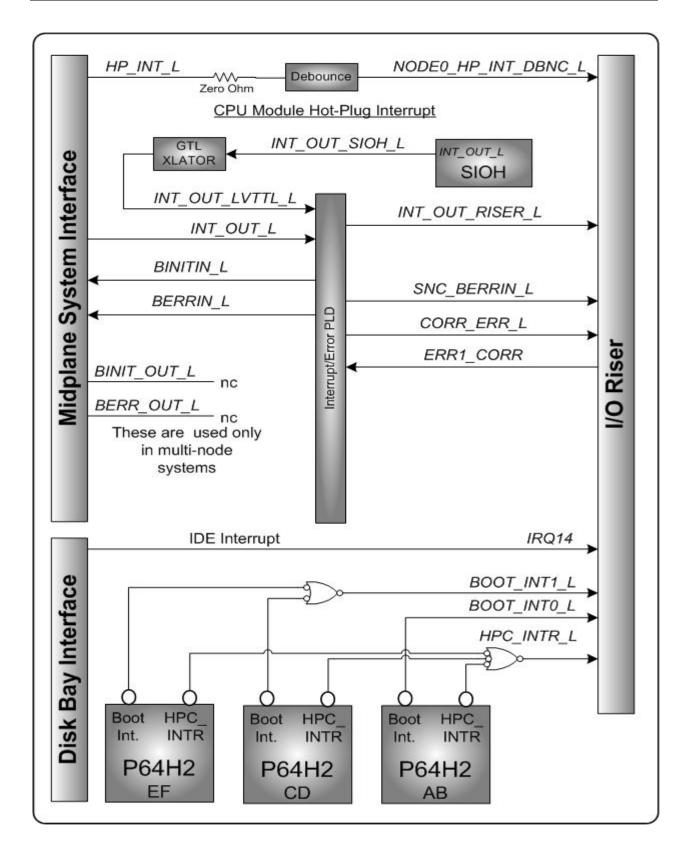

|    | 4.5.16  | Error Handling Logic                 | . 4-56 |

|    | 4.5.17  | Front Panel Interface                | . 4-56 |

|    | 4.5.18  | Internal Power-On Connector          | . 4-57 |

|    | 4.5.19  | Manufacturing Mode                   | . 4-57 |

|    | 4.5.20  | ICMB/IPMB Connectors                 | . 4-57 |

|    | 4.5.21  | Board Revision ID                    | . 4-58 |

|    | 4.5.22  | General Board Thermal Specifications | . 4-58 |

|    | 4.5.23  | I/O Board Thermal Requirements       | . 4-59 |

|    | 4.5.24  | EMI Reduction Features               | . 4-59 |

|    | 4.5.25  | Mechanical Features                  | . 4-60 |

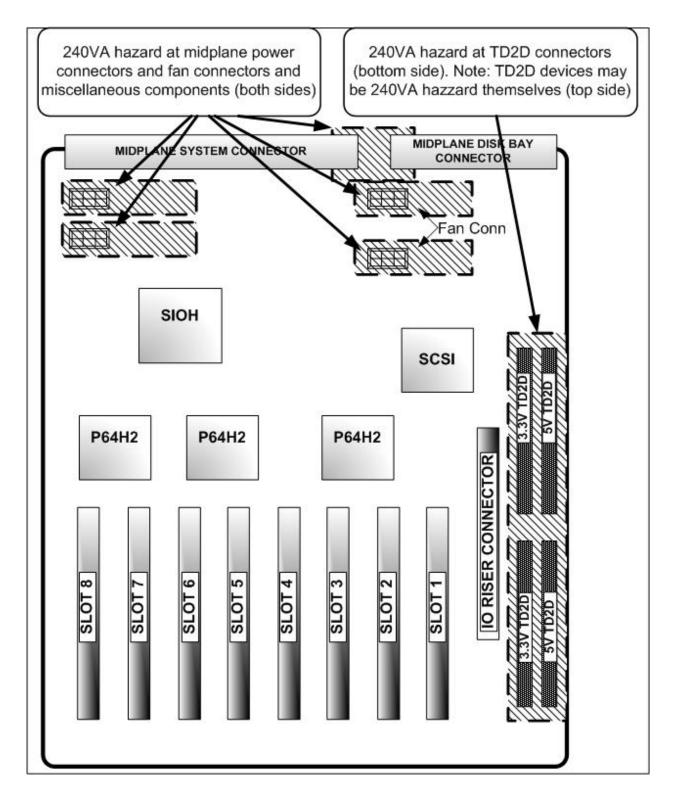

|    | 4.5.26  | 240 VA Safety                        | . 4-62 |

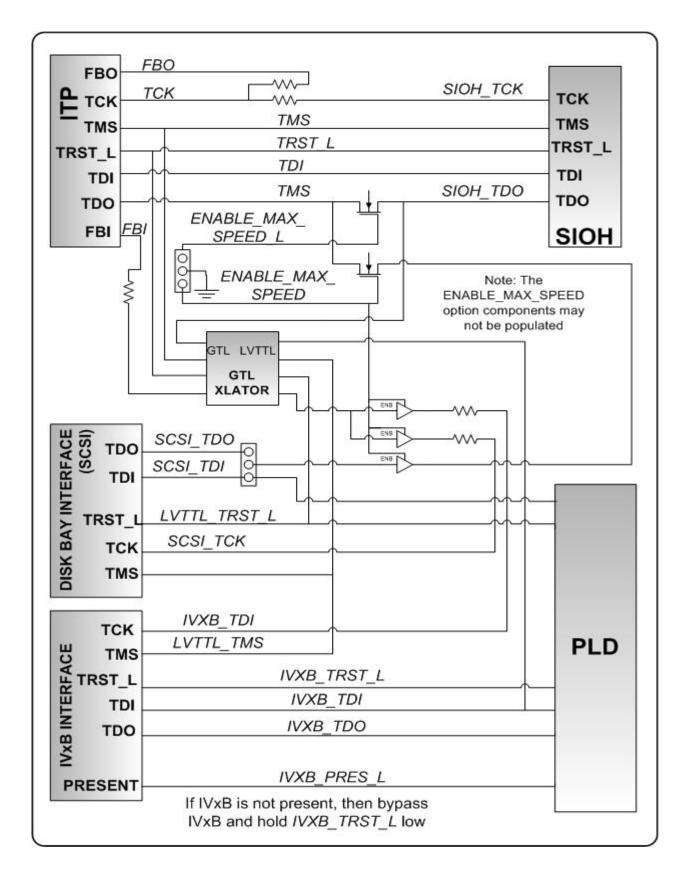

|    | 4.5.27  | In-Target Probe (ITP)                | . 4-64 |

| 5. | I/O Ris | ser Card                             | . 5-1  |

| 5  | 5.1 Fe  | atures                               | 5-1    |

5.

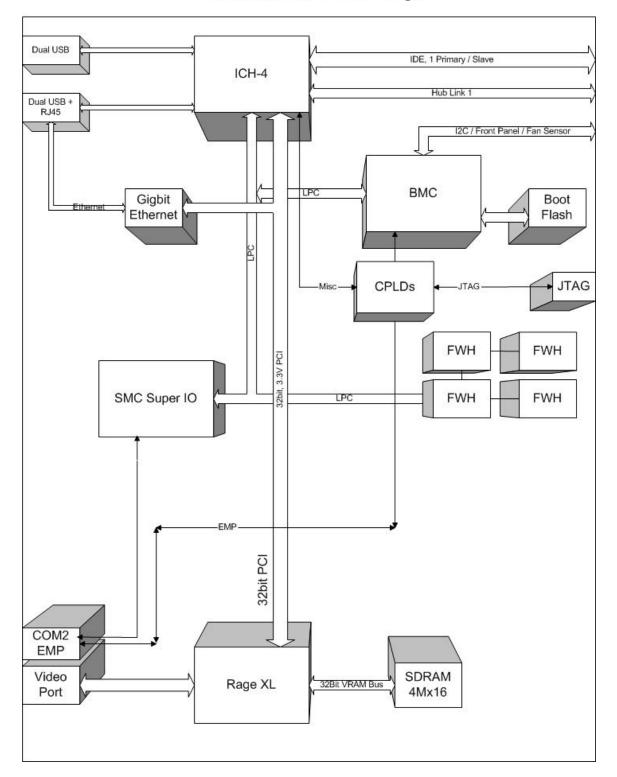

| 5.2 | Ar         | chitectural Overview                         | 5-1  |

|-----|------------|----------------------------------------------|------|

| 5.3 | Ma         | ajor Components                              | 5-4  |

| 5.3 | 3.1        | ICH4                                         | 5-4  |

| 5.3 | 3.2        | BMC                                          | 5-7  |

| 5.3 | 3.3        | Firmware Hub (FHW)                           | 5-9  |

| 5.3 | 3.4        | Super I/O*                                   | 5-10 |

| 5.3 | 3.5        | Video                                        | 5-10 |

| 5.3 | 3.6        | 82540EM* 10/100/1000 Ethernet                | 5-10 |

| 5.4 | Bu         | usses and Interfaces                         | 5-12 |

| 5.4 | 4.1        | Hublink 1.5 Interface                        | 5-12 |

| 5.4 | 1.2        | Integrated Drive Electronics (IDE) Interface | 5-12 |

| 5.4 | 1.3        | LPC Bus                                      | 5-13 |

| 5.4 | 1.4        | PCI Interface                                | 5-13 |

| 5.5 | I/C        | O Ports and Interface                        | 5-14 |

| 5.5 | 5.1        | USB                                          | 5-14 |

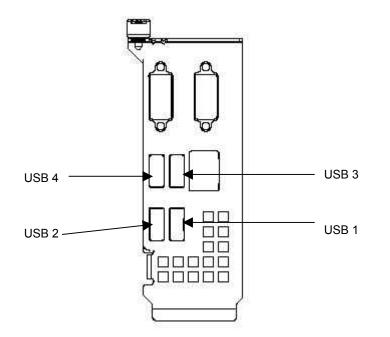

| 5.5 | 5.2        | Ethernet Port                                | 5-15 |

| 5.5 | 5.3        | Serial Port                                  | 5-16 |

| 5.5 | 5.4        | Video Jack                                   | 5-16 |

| 5.5 | 5.5        | I <sup>2</sup> C* Post Code Header           | 5-17 |

| 5.5 | 5.6        | ISP Headers                                  | 5-17 |

| 5.5 | 5.7        | Switch                                       | 5-17 |

| 5.5 | 5.8        | Jumper                                       | 5-18 |

| 5.6 | Se         | erver Management                             | 5-19 |

| 5.6 | <u>.</u> 1 | Server Management Block Diagram              | 5-19 |

| 5.6 | 6.2        | Power Up Sequence                            | 5-19 |

| 5.7 I/C                                                                          | D Riser Reset                                                            | 20                                                 |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------|

| 5.7.2                                                                            | I <sup>2</sup> C, IPMB and FRU5-2                                        | 21                                                 |

| 5.7.3<br>(EMP                                                                    | Inter-Chassis Management Bus (ICMB) and Emergency Management Port ) 5-22 |                                                    |

| 5.7.4                                                                            | JTAG                                                                     | 3                                                  |

| 5.7.5                                                                            | ISP Chain5-2                                                             | 24                                                 |

| 5.7.6                                                                            | Front Panel Interface5-2                                                 | 25                                                 |

| 5.7.7                                                                            | CPLD Interface                                                           | 25                                                 |

| 5.8 Cl                                                                           | ock                                                                      | 9                                                  |

| 5.9 IR                                                                           | Q and Bus Master                                                         | 2                                                  |

| 5.10                                                                             | I/O Riser and I/O Board Interface5-3                                     | 4                                                  |

| 5.11                                                                             | Power / Standby Power5-3                                                 | 57                                                 |

| 5.12                                                                             | Strap Option Summary5-4                                                  | 1                                                  |

|                                                                                  |                                                                          |                                                    |

| 6. Midpl                                                                         | ane Board 6-1                                                            | I                                                  |

| •                                                                                | ane Board                                                                |                                                    |

| 6.1 In                                                                           |                                                                          | -1                                                 |

| 6.1 In                                                                           | troduction6-                                                             | -1<br>-1                                           |

| 6.1 In<br>6.2 Ha                                                                 | troduction                                                               | -1<br>-1<br>-1                                     |

| 6.1 In<br>6.2 Ha<br>6.2.1                                                        | troduction                                                               | -1<br>-1<br>-2                                     |

| 6.1 In<br>6.2 Ha<br>6.2.1<br>6.2.2                                               | troduction                                                               | -1<br>-1<br>-2<br>-3                               |

| 6.1 In<br>6.2 Ha<br>6.2.1<br>6.2.2<br>6.2.3                                      | troduction                                                               | -1<br>-1<br>-2<br>-3                               |

| 6.1 In<br>6.2 Ha<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5                    | troduction                                                               | -1<br>-1<br>-2<br>-3<br>-4                         |

| 6.1 In<br>6.2 Ha<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5                    | troduction                                                               | -1<br>-1<br>-2<br>-3<br>-4<br>-5                   |

| 6.1 In<br>6.2 Ha<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.3 Co          | troduction                                                               | -1<br>-1<br>-2<br>-3<br>-4<br>-5<br>-5             |

| 6.1 In<br>6.2 Ha<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.3 Co<br>6.3.1 | troduction                                                               | -1<br>-1<br>-2<br>-3<br>-4<br>-5<br>-5<br>-5<br>-6 |

| Append | ix B: Reference Documents                |      |

|--------|------------------------------------------|------|

|        |                                          |      |

| Append | ix A: Glossary                           | I    |

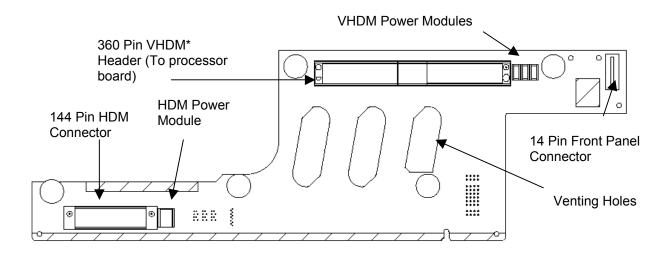

| 6.4.4  | Venting Holes                            | 6-30 |

| 6.4.3  | 8 Mechanical Outline                     | 6-29 |

| 6.4.2  | 2 Power Requirements                     | 6-29 |

| 6.4.1  | Midplane Board Thermal Requirements      | 6-29 |

| 6.4 E  | Electrical and Mechanical Specifications | 6-29 |

| 6.3.5  | Midplane / SCSI Backplane Interface      | 6-27 |

## List of Figures

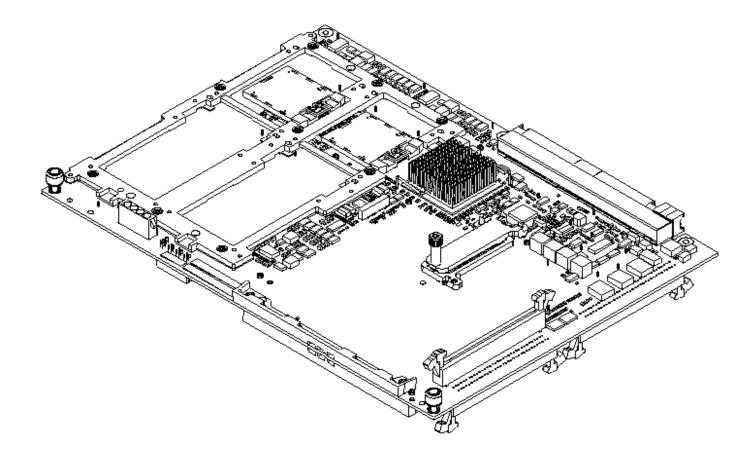

| Figure 2-1. Processor Board Complex without Memory Board                                        | 2-3  |

|-------------------------------------------------------------------------------------------------|------|

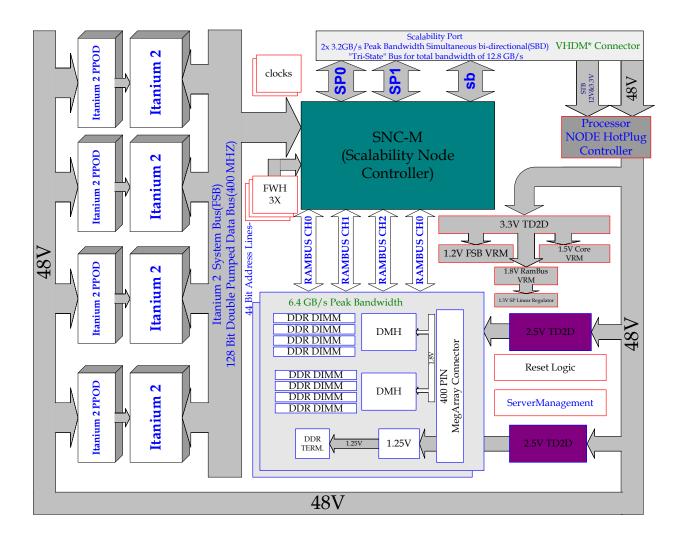

| Figure 2-2: Processor Baseboard Block Diagram                                                   | 2-4  |

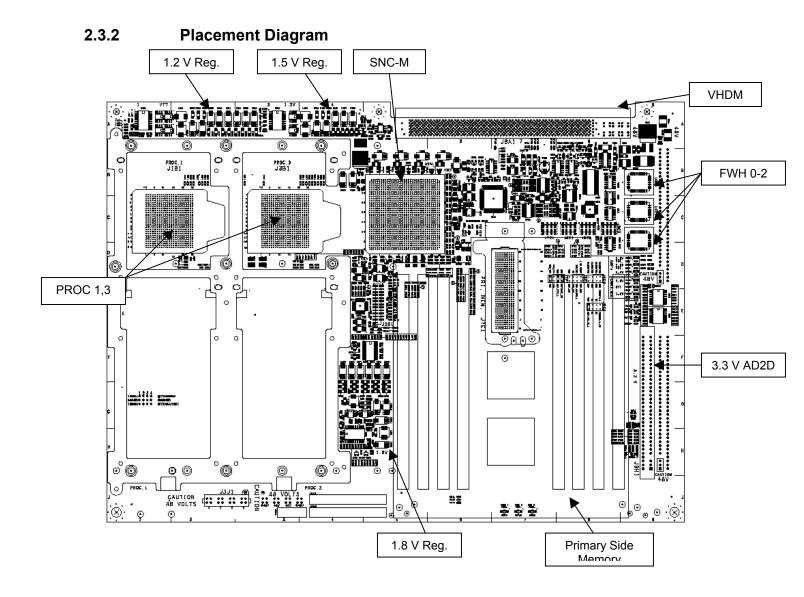

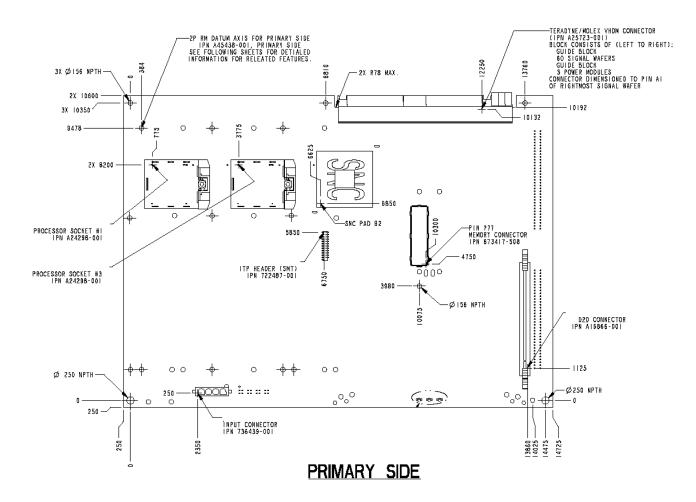

| Figure 2-3: Processor Baseboard Component Location (Primary Side)                               | 2-5  |

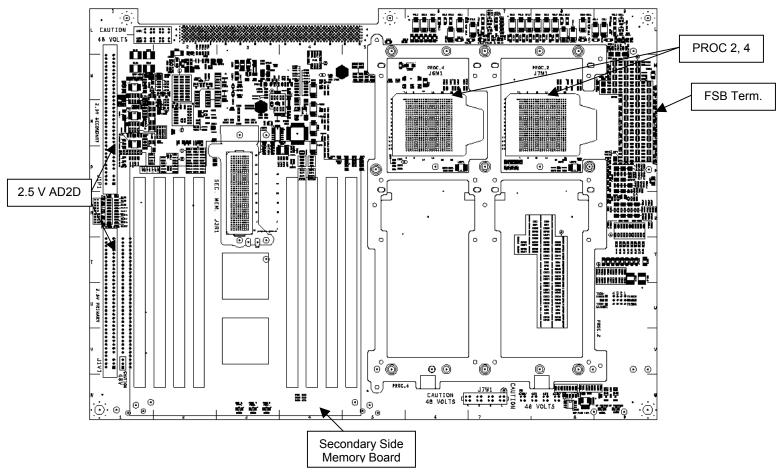

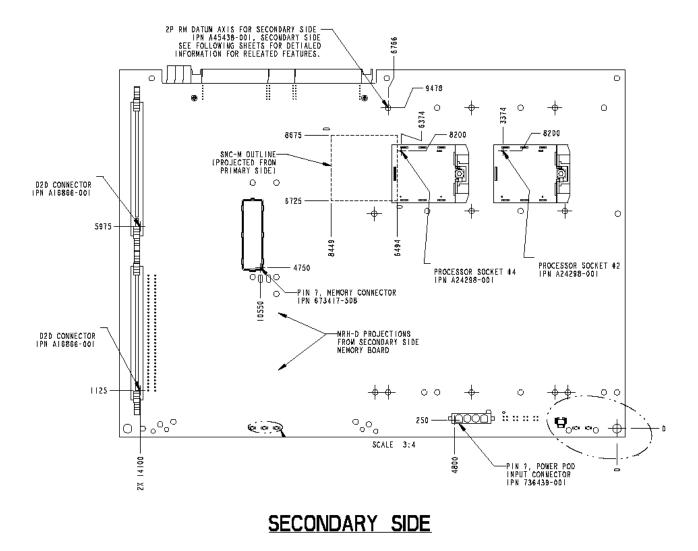

| Figure 2-4: Processor Baseboard Component Location (Secondary Side)                             | 2-6  |

| Figure 2-5: Processor Baseboard Clock Distribution                                              | 2-9  |

| Figure 2-6: Rail Power-up Sequence.                                                             | 2-17 |

| Figure 2-7: The Processor Board's Power Sequencing Control System                               | 2-17 |

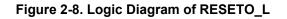

| Figure 2-8: Logic Diagram of RESETO_L                                                           | 2-23 |

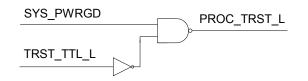

| Figure 2-9: Processor TRST Logic diagram                                                        | 2-24 |

| Figure 2-10: SNC-M TRST Logic diagram                                                           | 2-24 |

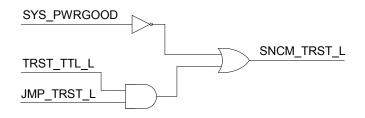

| Figure 2-11: Firmware ID Select Logic                                                           | 2-25 |

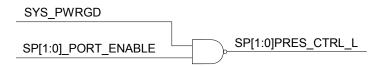

| Figure 2-12: SP Port Enable                                                                     | 2-25 |

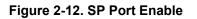

| Figure 2-13: Glitch Timer connections                                                           | 2-26 |

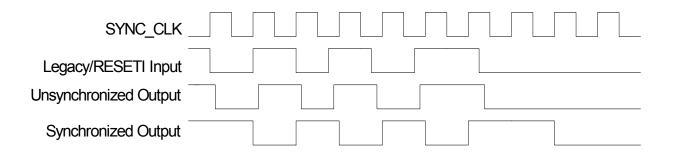

| Figure 2-14: Example of Synchronized and Unsynchronized Outputs                                 | 2-28 |

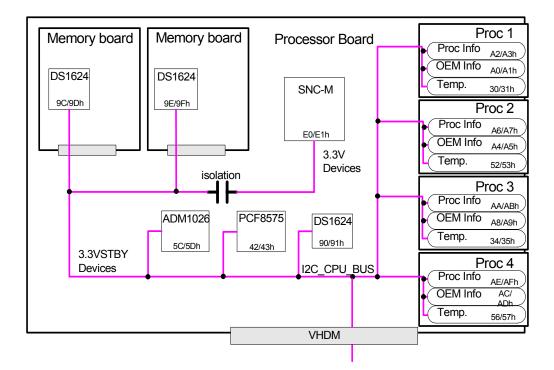

| Figure 2-15: SR870BN4 Intel <sup>®</sup> Itanium <sup>®</sup> 2/E8870 Server Management Diagram | 2-30 |

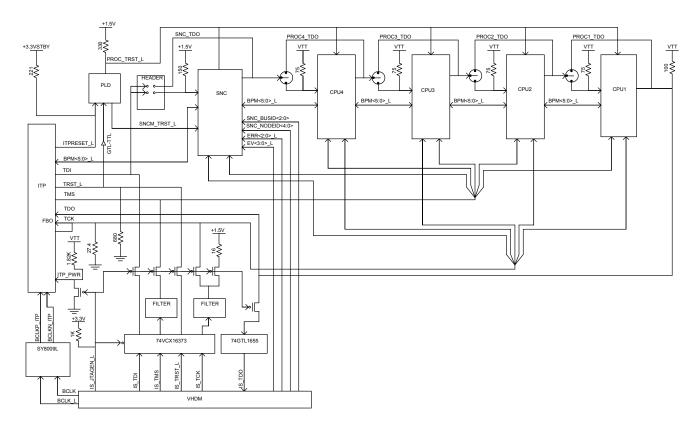

| Figure 2-16: Implementation of JTAG on the Processor/Memory Node                                | 2-34 |

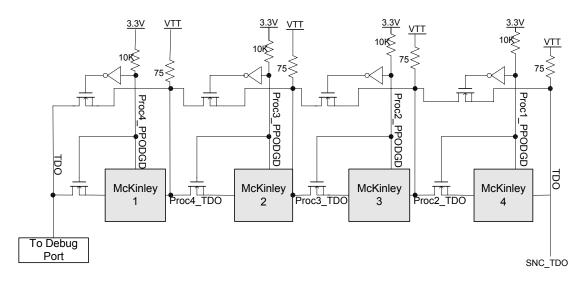

| Figure 2-17: Intel <sup>®</sup> Itanium <sup>®</sup> 2 Processor Bypass Scheme                  | 2-36 |

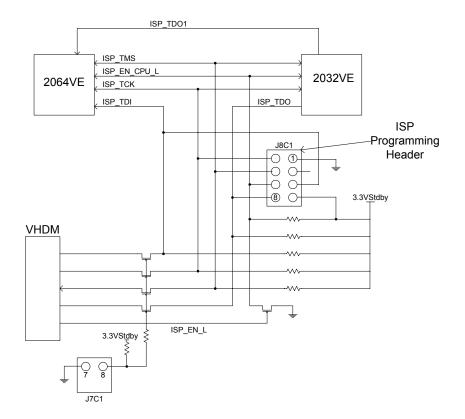

| Figure 2-18: ISP Programming Chain Block Diagram                                                | 2-37 |

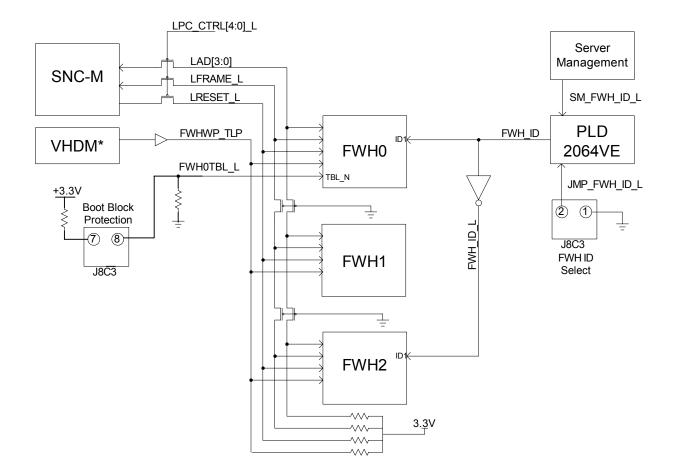

| Figure 2-19: LPC Block Diagram                                                                  | 2-38 |

| Figure 2-20: Processor Baseboard Mechanical Drawing (Primary)                                   | 2-51 |

| Figure 2-21: Processor Baseboard Mechanical Drawing (Secondary)                                 | 2-52 |

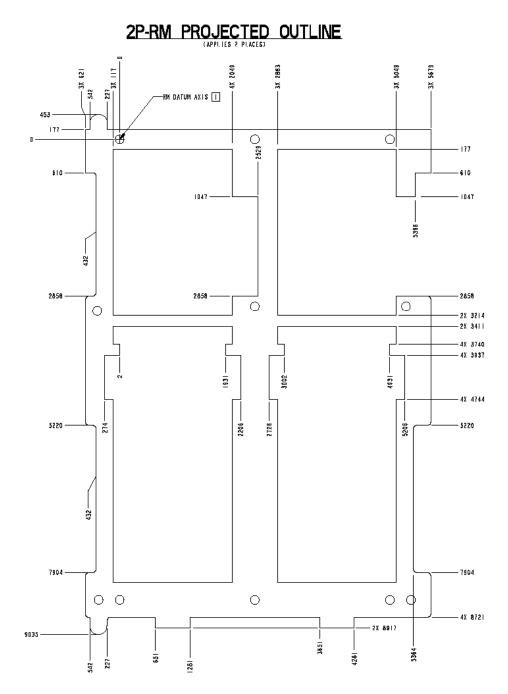

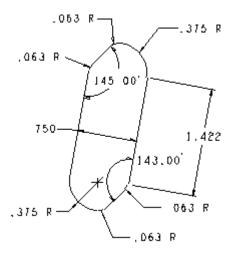

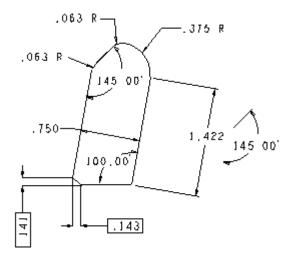

| Figure 2-22: Processor Retention Mechanism                                                      | 2-53 |

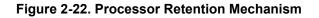

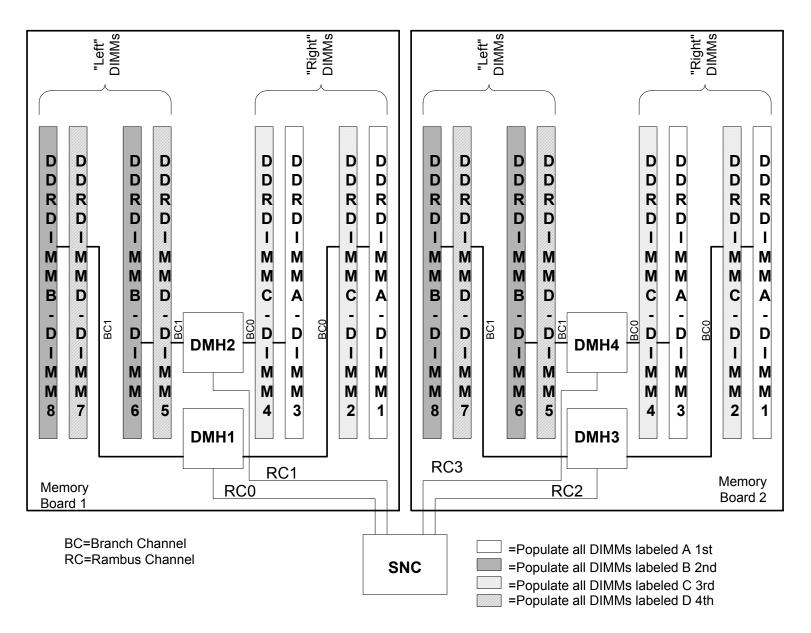

| Figure 3-1. Top Level SR870BN4 Memory System Block Diagram                                      | 3-2  |

| Figure 3-2. Memory Signals                                                                      | 3-3  |

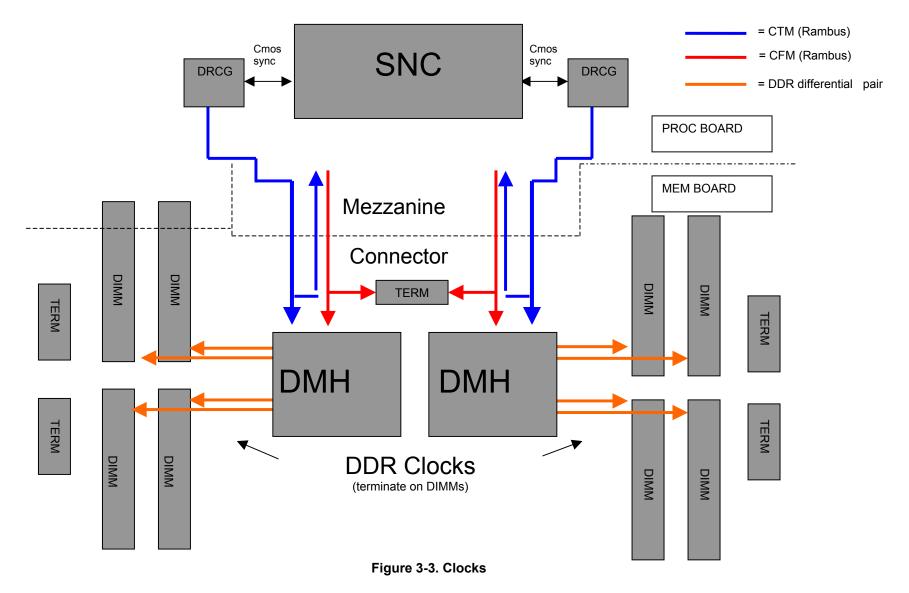

| Figure 3-3. Clocks                                                                              | 3-4  |

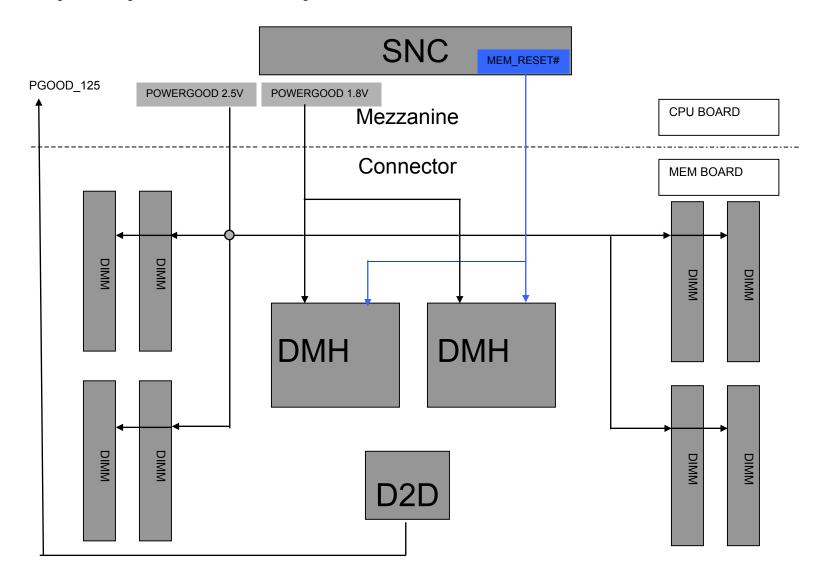

| Figure 3-4. Reset Signals                                                                       | 3-5  |

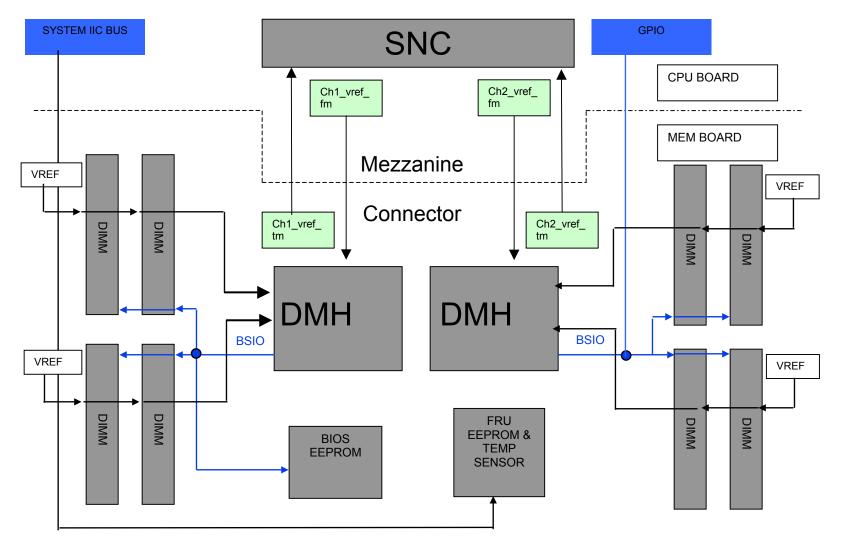

| Figure 3-5. Miscellaneous Signals                                                               | 3-6  |

| Figure 3-6. Memory Board Mechanical Diagram                                                     | 3-15 |

| Figure 4-1. I/O Board Block Diagram                                                             | 4-2  |

| Figure 4-2. I/O Board Placement Plot                                                            | 4-6  |

| Figure 4-3. PCI AUX Control and PME Control                             | 4-23 |

|-------------------------------------------------------------------------|------|

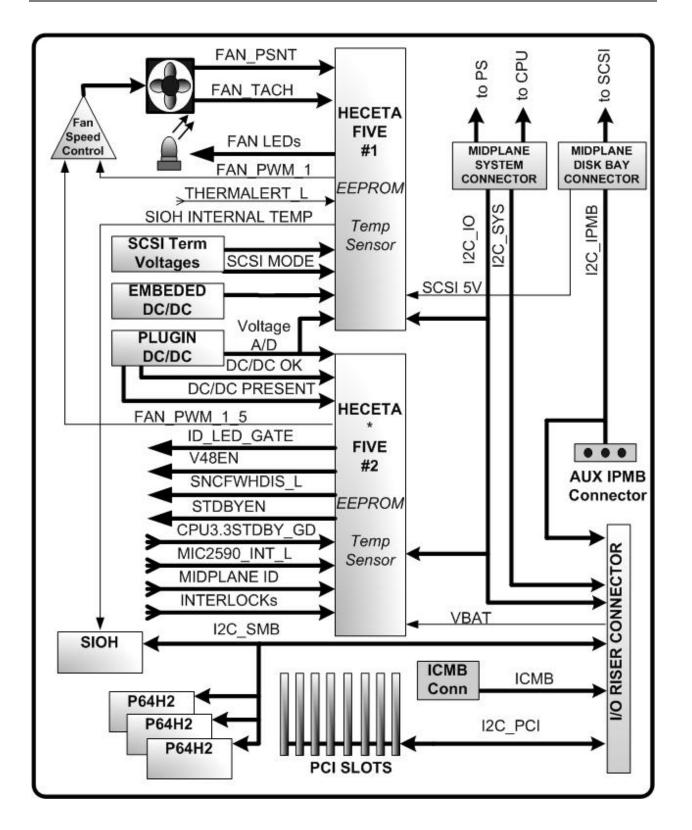

| Figure 4-4. Server Management Block Diagram                             | 4-31 |

| Figure 4-5. Server Management Sensor Assignment                         | 4-32 |

| Figure 4-6. In-System Programmable Diagram                              | 4-38 |

| Figure 4-7. Power Distribution                                          | 4-40 |

| Figure 4-8. Power Sequence Flow                                         | 4-45 |

| Figure 4-9. Power Sequence Timing                                       | 4-46 |

| Figure 4-10. Clock Block Diagram                                        | 4-48 |

| Figure 4-11. System Reset Block Diagram                                 | 4-51 |

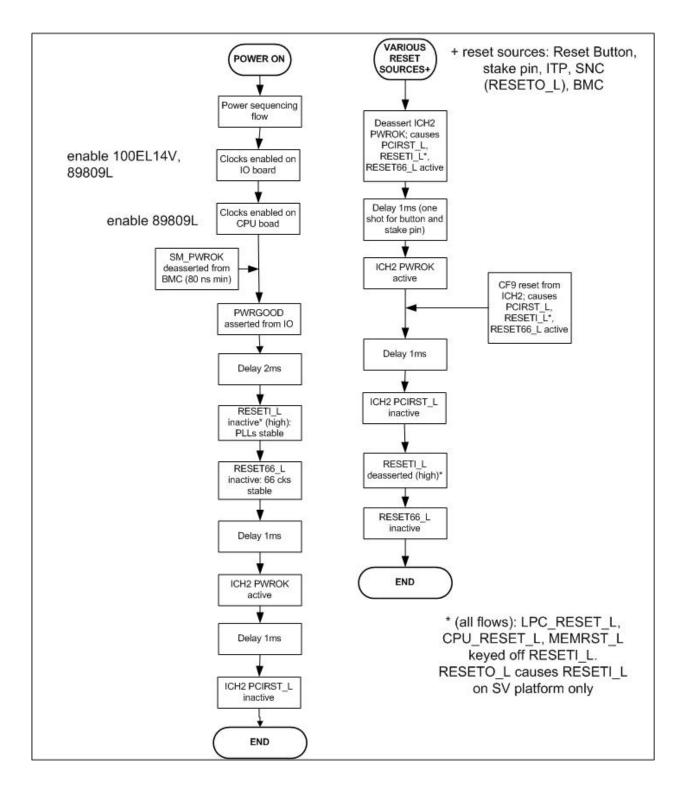

| Figure 4-12. Reset Flow                                                 | 4-52 |

| Figure 4-13. Reset Timing                                               | 4-53 |

| Figure 4-14. Interrupt Block Diagram                                    | 4-55 |

| Figure 4-15. Error Handling Logic Diagram                               | 4-56 |

| Figure 4-16. Board Outline Drawing and Key Dimensions                   | 4-61 |

| Figure 4-17. 240VA Hazard Diagram                                       | 4-63 |

| Figure 4-18. ITP Diagram                                                | 4-65 |

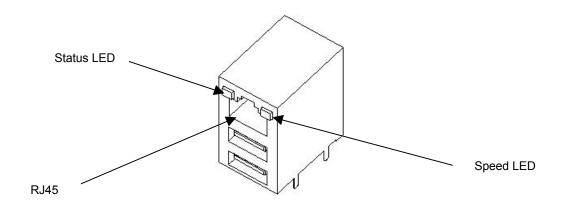

| Figure 5-1. Block Diagram of the S870BN4 I/O Riser Card                 | 5-3  |

| Figure 5-2. LED and RJ45 Locations                                      | 5-16 |

| Figure 5-3. Server Management Block Diagram                             | 5-19 |

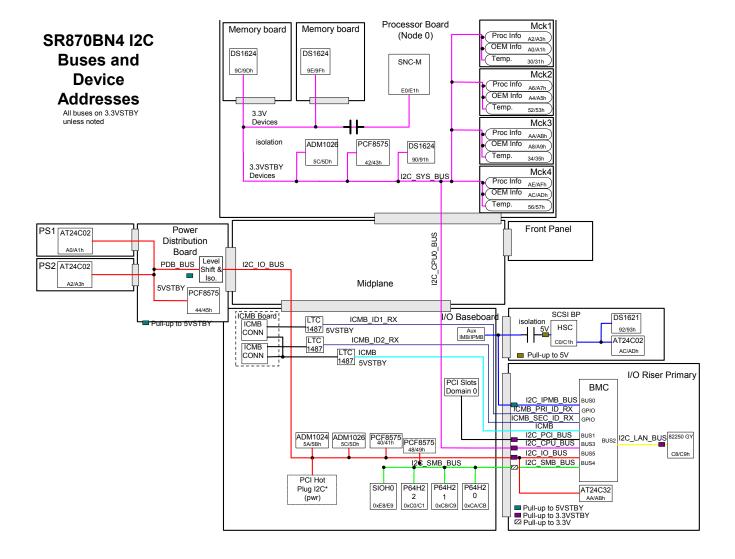

| Figure 5-4. SR870BN4 I <sup>2</sup> C* Buses and Device Addresses       | 5-22 |

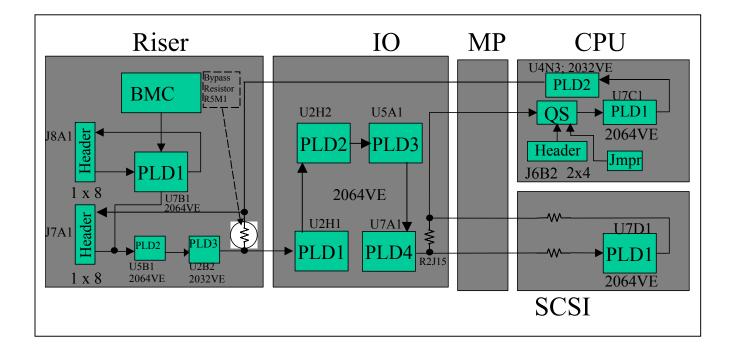

| Figure 5-5. SR870BN4 System ISP Chain Block Diagram                     | 5-25 |

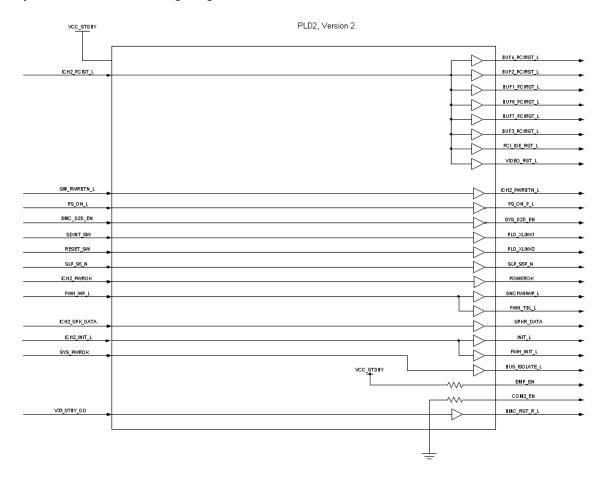

| Figure 5-6. PLD2- Miscellaneous Control PLD                             | 5-29 |

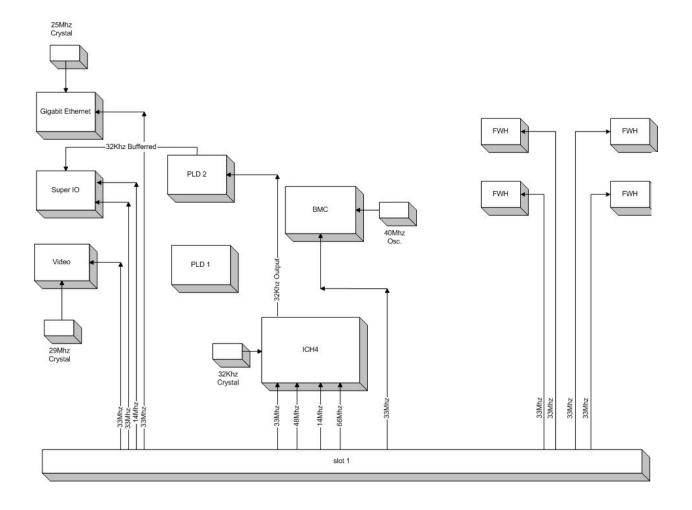

| Figure 5-7. S870BN4 I/O Riser Clock Distribution                        | 5-31 |

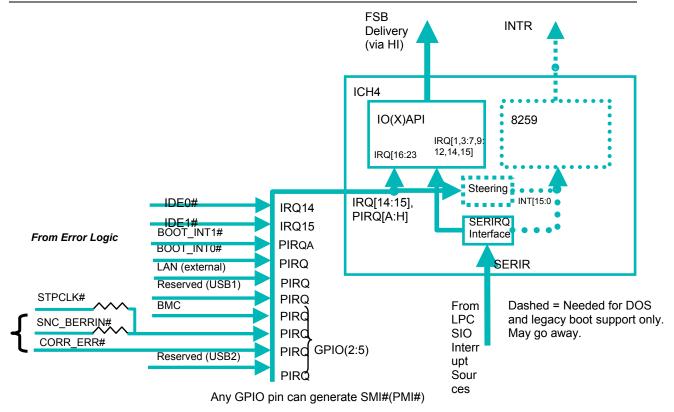

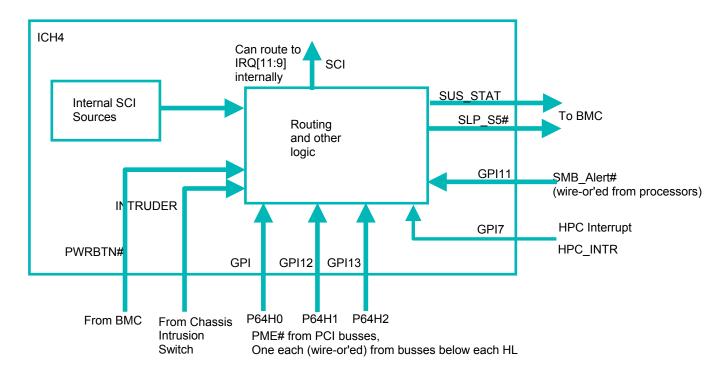

| Figure 5-8. ICH4 IRQ Routing                                            | 5-33 |

| Figure 5-9. GPIO Connectivity                                           | 5-34 |

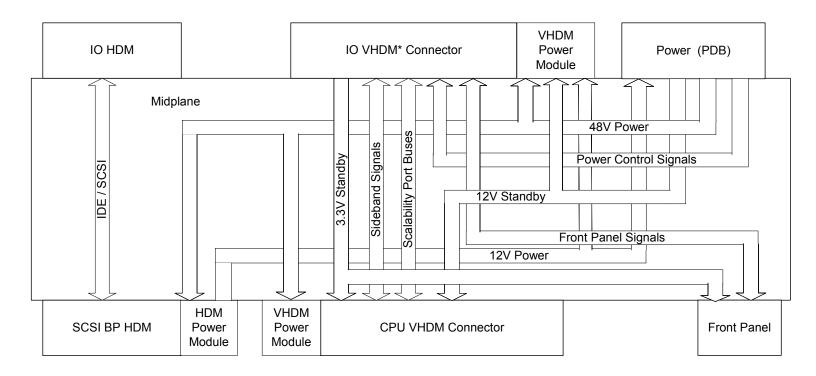

| Figure 6-1. Midplane Block Diagram                                      | 6-2  |

| Figure 6-2. S870BN4 Midplane Primary Side (looking from processor side) | 6-3  |

| Figure 6-3. S870BN4 Midplane Secondary Side (looking from I/O side)     | 6-4  |

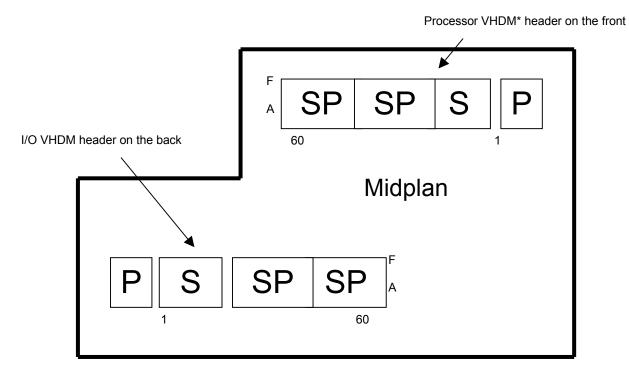

| Figure 6-4. Signal Location on VHDM* Connectors                         | 6-5  |

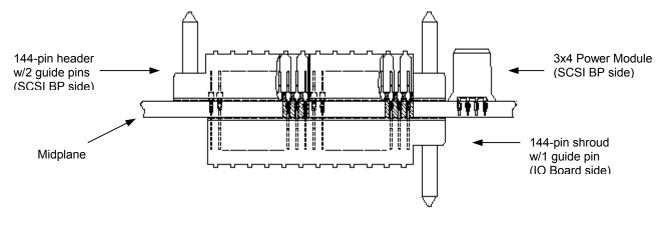

| Figure 6-5. HDM Connector Concept                                       | 6-27 |

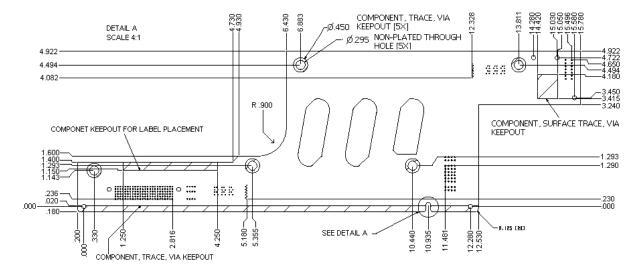

| Figure 6-6. S870BN4 Midplane Mechanical Specification (Processor Side)  | 6-30 |

| Figure 6-7. S870BN4 Midplane Ventilation Hole Specification (Type 1)    | 6-30 |

| Figure 6-8. S870BN4 Midplane Ventilation Hole Specification (Type 2)    | 6-31 |

## List of Tables

| Table 2-1: Clock Frequency Chart                                                        | 2-9  |

|-----------------------------------------------------------------------------------------|------|

| Table 2-2: Embedded Regulator VID table                                                 | 2-11 |

| Table 2-3: AD2D VID table                                                               | 2-11 |

| Table 2-4: 1.2 V and Vref Typical Voltage and Tolerance                                 | 2-13 |

| Table 2-5: 1.5 V Tolerance                                                              | 2-13 |

| Table 2-6: 1.8 V Tolerance                                                              | 2-14 |

| Table 2-7: 1.3 V Tolerance                                                              | 2-14 |

| Table 2-8. Processor Board and I/O Board Power Good/Reset Interface Signals             | 2-15 |

| Table 2-9: Different Resets Supported by the Procesor Board                             | 2-17 |

| Table 2-10: Power Good/Reset PLD Signals                                                | 2-19 |

| Table 2-11: Legacy Synchronization PLD Inputs and Outputs                               | 2-26 |

| Table 2-12: Miscellaneous Jumper Definitions                                            | 2-28 |

| Table 2-13: ISP Header (J8C1) Connector Interface Signals                               | 2-29 |

| Table 2-14: Device List on System I <sup>2</sup> C* Bus                                 | 2-30 |

| Table 2-15: DS1624 SEEPROM Programming Areas                                            | 2-31 |

| Table 2-16: Example of Subset of FRU Information for SR870BN4 Processor Board           | 2-31 |

| Table 2-17: I <sup>2</sup> C_PROCESSOR Signals and their Interface to Server Management | 2-32 |

| Table 2-18: Signals Monitored by the ADM1026*                                           | 2-32 |

| Table 2-19: Memory Interface Signals Including RAMBUS Channels 0, 1, 2, 3               | 2-39 |

| Table 2-20: System Server Management Interface                                          | 2-40 |

| Table 2-21: Power Connection                                                            | 2-41 |

| Table 2-22: Processor Baseboard Maximum Ratings                                         | 2-41 |

| Table 2-23: Maximum Power Requirements                                                  | 2-41 |

| Table 2-24: Baseboard Connector Specifications                                          | 2-43 |

| Table 2-25: SP Signals and Non-SP Signals Pinout                                        | 2-43 |

| Table 2-26: Non-SP Signal List                                                          | 2-44 |

| Table 2-27: Processor Baseboard Memory Connector Pinout (MegArray*) – Pins A1<br>F40    |      |

| Table 2-28: Processor Baseboard Power Connection (VHDM*)                                | 2-50 |

| Table 2-29. Critical Processor Board Components                   |      |

|-------------------------------------------------------------------|------|

| Table 3-1. Available Memory Configurations                        |      |

| Table 3-2. Device Address by Processor MegArray* Location         |      |

| Table 3-3. Rambus Signals                                         |      |

| Table 3-4. DDR Signals                                            | 3-11 |

| Table 3-5. Miscellaneous Signals                                  | 3-11 |

| Table 3-6. Voltage Reference Signals                              | 3-12 |

| Table 3-7. Absolute Maximum Ratings                               |      |

| Table 3-8. Critical Memory Board Components                       | 3-13 |

| Table 3-9. Acceptable Tolerance Ranges                            |      |

| Table 3-10. Voltage Power Consumption                             |      |

| Table 3-11. Calculations for Voltage Power Requirements – 2.5 V   |      |

| Table 3-12. Calculations for Voltage Power Requirements – 1.8 V   | 3-14 |

| Table 3-13. Calculations for Voltage Power Requirements – 1.25 V. | 3-15 |

| Table 3-14. Memory Module Connector Specifications                | 3-16 |

| Table 4-1. I/O Board Component Reference                          | 4-7  |

| Table 4-2. Midplane System Connector Signal List                  |      |

| Table 4-3. Midplane VHDM Power Connector Pinout                   |      |

| Table 4-4. Midplane Disk Bay Connector Signal List and Pinout     |      |

| Table 4-5. Midplane Connector Current Rating                      | 4-11 |

| Table 4-6. Summary of PCI Slot Characteristics                    | 4-13 |

| Table 4-7. IDSEL# Mapping for PCI Bus Segment A                   | 4-13 |

| Table 4-8. IDSEL# Mapping for PCI Bus Segment B                   | 4-14 |

| Table 4-9. IDSEL# Mapping for PCI Bus Segment C                   | 4-14 |

| Table 4-10. IDSEL# Mapping for PCI Bus Segment D                  | 4-15 |

| Table 4-11. IDSEL# Mapping for PCI Bus Segment E                  | 4-15 |

| Table 4-12. IDSEL# Mapping for PCI Bus Segment F                  | 4-16 |

| Table 4-13. PCI Electrical Levels                                 | 4-16 |

| Table 4-14. PCI Signal Descriptions                               | 4-16 |

| Table 4-15. 3.3-V PCI Slot Pinout                                 | 4-17 |

| Table 4-16. PCIHP LED/Switch Connector                            | 4-21 |

| Table 4-17. SCSI Signal Descriptions                              | 4-24 |

| Table 4-18. SCSI Connector Pinout – LVDS Mode                     | 4-26 |

| Table 4-19. IDE Signal Descriptions                             | . 4-27 |

|-----------------------------------------------------------------|--------|

| Table 4-20. I/O Riser Connector Current Rating                  | . 4-28 |

| Table 4-21. I/O Riser Connector Pinout                          | . 4-29 |

| Table 4-22. Server Management Address Map                       | . 4-33 |

| Table 4-23. Fan Connector Signal Description                    | . 4-34 |

| Table 4-24. Fan Connector Pinout                                | . 4-34 |

| Table 4-25. Server Management Fan Control Assignment            | . 4-35 |

| Table 4-26. Voltage Sense List                                  | . 4-36 |

| Table 4-27. Server Management D2D Control Assignment            | . 4-36 |

| Table 4-28. Server Management Miscellaneous Control Assignment  | . 4-37 |

| Table 4-29. ISP Bypass Resistors                                | . 4-39 |

| Table 4-30. 5-V T-D2D Connector Pinout                          | . 4-41 |

| Table 4-31. VID T-D2D Connector Pinout                          | . 4-42 |

| Table 4-32. D2D Fault LEDs                                      | . 4-43 |

| Table 4-33. 1.3 V, 1.5 V, 1.8 V, -12 V Converter Specifications | . 4-43 |

| Table 4-34. Input Power Requirements                            | . 4-44 |

| Table 4-35. PCI 3.3 V and 5 V Power Restrictions                | . 4-44 |

| Table 4-36. CK429S Operational Mode                             | . 4-49 |

| Table 4-37. CKFF Clocks and Target Devices                      | . 4-50 |

| Table 4-38. IRQ Mapping                                         | . 4-54 |

| Table 4-39. Front Panel Interface                               | . 4-57 |

| Table 4-40. Internal Power-On Connector Pinout (J9E1)           | . 4-57 |

| Table 4-41. ICMB Connector Pinout (J9C1)                        | . 4-58 |

| Table 4-42. IPMB Connector Pinout (J9D1)                        | . 4-58 |

| Table 4-43. Board Revision ID                                   | . 4-58 |

| Table 4-44. General Board Thermal Specifications                | . 4-59 |

| Table 4-45. Critical I/O Board Components                       | . 4-59 |

| Table 4-46. Mounting Hole EMI Resistors                         | . 4-60 |

| Table 4-47. ITP Connector Pinout                                | . 4-64 |

| Table 5-1. ICH4 Signals                                         | 5-5    |

| Table 5-2. ICH4 Strap Option                                    | 5-7    |

| Table 5-3. BMC Pins and Signals Group Description               | 5-8    |

| Table 5-4. Firmware Hub General Purpose Input                   | . 5-10 |

| 5-10  |

|-------|

| 5-11  |

| 5-12  |

| 5-13  |

| 5-14  |

| 5-15  |

| 5-16  |

| 5-23  |

| 5-23  |

| 5-23  |

| 5-25  |

| 5-29  |

| 5-32  |

| 5-34  |

| 5-38  |

| . 6-1 |

| . 6-4 |

| . 6-6 |

| . 6-6 |

| . 6-7 |

| 6-16  |

| 6-17  |

| 6-26  |

| 6-27  |

| 6-29  |

|       |

<This page intentionally left blank.>

## 1. Introduction

The Intel® Server Board S870BN4 Board Set Technical Product Specification (TPS) provides the specifications for the Intel® Server System SR870BN4 board set. This system is designed to utilize the first microprocessor based on the Intel® Itanium® Processor Family architecture, known as the Itanium® 2 processor. The Itanium 2 processor expands the Intel® Architecture (IA) with new levels of performance and features. The Server System SR870BN4 design is based on the Intel<sup>®</sup> E8870 chip set.

This document is a combination of the processor board, memory board, midplane board, I/O board, and I/O riser specifications that define the firmware components of the Server System SR870BN4. The purpose of this document is to pull together pertinent information about all of the components.

This document is subject to change. Every effort has been made to ensure that the information contained in this document is correct. Some of the reference documents that were used to create this document have planned revisions that will require this document to be updated.

<This page intentionally left blank.>

## 2. Processor Baseboard

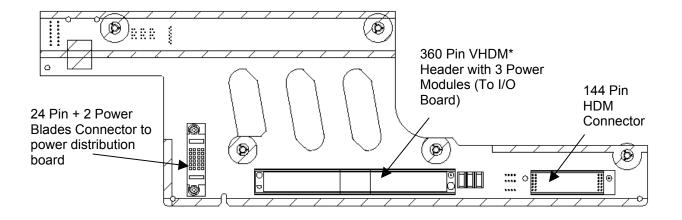

This chapter describes the architecture of the Intel® Itanium® 2/Intel® E8870 processor baseboard. The baseboard contains the Itanium 2 processors, the Intel E8870 Scalabale Node Controller-McKinley (SNC-M) chip, two memory board connectors, and support circuits. The two memory boards plug into the processor baseboard via two high-density MegArray\* connectors. The processor baseboard plugs into the midplane of an Server System SR870BN4 through a 6-row X 60-column, 360-pin, very high density metric (VHDM) connector for connection to the I/O subsystem of an Itanium 2-based server.

### 2.1 Features

The processor baseboard has the following features:

- Four Itanium 2 processor sockets

- 48-V DC-to-DC (D2D) converter power pod for each Itanium 2 processor

- D2D voltage converters for 2.5 V, 3.3 V

- Two 48 V to 2.5 V plug-in D2D for DDR memory support

- One 48 V to 3.3 V plug-in D2D

- Embedded Regulators for 1.2 V, 1.5 V, 1.8 V and 1.3 V

- 3.3 V to 1.2 V

- 3.3 V to 1.5 V

- 3.3 V to 1.8 V

- 1.8 V to 1.3 V linear regulator

- One SNC-M component of the Intel E8870 chip set

- Three Firmware Hubs (FWH) for BIOS and system configuration utility (SCU) software

- Two memory board connectors supporting 2 Rambus channels each

- One VHDM 360-pin connector for I/O connections

- Debug port for use with an In-Target Probe (ITP) (debug only)

- Two I<sup>2</sup>C system management buses (SMBus)

### 2.2 Chapter Structure and Outline

The information contained in this chapter is organized into four sections. Information is presented in a modular format, with numbered headings for each major topic and subtopic. The content of each section is summarized below:

Section 2.3:

Introduction

Provides an overview of the processor baseboard showing functional blocks and board layout.

Section 2.4:

Functional Architecture

Describes the way each functional block of the processor baseboard works.

Section 2.5:

Signal Descriptions

Summarizes the processor baseboard connector interface signal pin

names and their meanings. Their mnemonics appear throughout this chapter.

Section 2.6: Electrical, Mechanical, and Environmental Specifications Specifies operational parameters and considerations, and connector pinouts.

### 2.3 Introduction

The Server Board S870BN4 Itanium 2/E8870 processor baseboard is designed for use as a building block for 4-way, and greater, processor systems. The Itanium 2 processor baseboard provides the support for one to four Itanium 2 processors, each with a dedicated power pod. The system controller is provided via the Intel<sup>®</sup> E8870 SNC-M chip that interfaces with the Itanium 2 processor system bus, DDR (Double Data Rate) memory via Rambus interface and I/O subsystem via the scalability port. The LPC (Low Pin Count) interface allows for localized FWH support. The processor baseboard design is partitioned according to the following functional blocks:

- Itanium 2 processors

- E8870 SNC-M chip for the Itanium 2-based system bus, memory, and scalability port interface

- Rambus memory interface and connector

- Scalability port/system power interface and connector

- Clock distribution

- Voltage regulators/Itanium 2 power pod

- Processor/system reset

- Server management

- Debug port for ITP

The following figure shows a physical representation of the processor baseboard without memory boards or Itanium 2 processors installed.

Figure 2-1. Processor Board Complex without Memory Board

#### 2.3.1 Block Diagram

The following figure illustrates the general architecture of the processor baseboard.

Figure 2-2. Processor Baseboard Block Diagram

Figure 2-3. Processor Baseboard Component Location (Primary Side)

Figure 2-4. Processor Baseboard Component Location (Secondary Side)

Figure 2-3 and Figure 2-4 show the placement of the major components and connectors on the processor baseboard.

### 2.4 Functional Architecture

This section provides a more detailed architectural description of the processor baseboard functional blocks.

### 2.4.1 Itanium 2 Front Side Bus (FSB)

All four Itanium 2 processors are connected to the E8870/SNC-M through the system (Front Side) bus. The system bus consists of a 44-bit address bus and a 128-bit data bus. The address and control signals have parity protection. The data bus has Error Correcting Code (ECC) protection on each 64-bit half of the 128-bit data bus. The bus signals use Assisted Gunning Transceiver Logic (AGTL+) technology and are functionally compatible with the Itanium processor bus. The system bus strobes data on both the rising and falling edges of the 200-MHz clock to achieve an effective source synchronous transfer rate of 400 MT/s. The bus structure can support a load limit of five devices: four processors and one SNC-M. The processors are mounted on both sides of the processor baseboard to limit the length of the bus.

The system bus signals are daisy chained with termination resistors at both ends of the bus (the SNC-M termination is on-die). This eliminates the need for a termination card when a processor is absent. The processor baseboard supports up to four processors.

The features of the system bus are:

- Full support for 4-way multiprocessing

- 200 MHz with 2x strobes for equivalent 400-Mhz operation

- 6.4 GB/s peak bandwidth

- 128-bit data bus

- 128-byte cache line size

- Utilization of 44 bits of the 50-bit processor address bus

- Parity protection on address and control signals; ECC protection on the data signals

- AGTL+ bus driver technology

- Enhanced defer feature for out-of-order data delivery

- System bus interrupt delivery (SAPIC architecture)

- Supports Itanium 2 processor special cycles

#### 2.4.2 Memory Interface

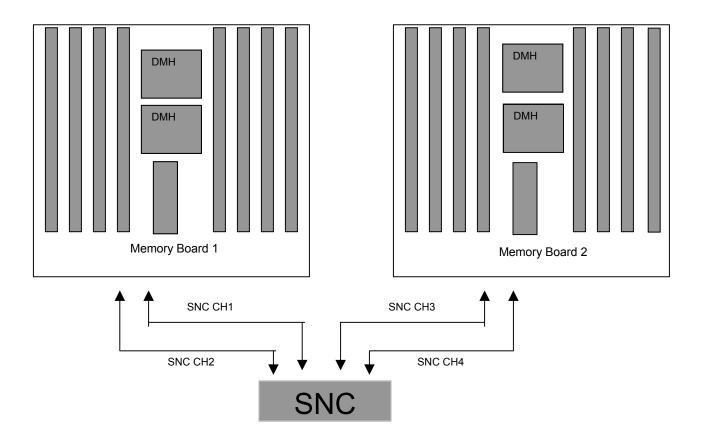

The Itanium 2/E8870 memory subsystem consists of two memory boards that connect to the processor baseboard through a 400-pin MegArray connector. Each memory board contains two memory repeater (DMH) chips, one per RDRAM channel, that support up to four 72-bit wide DIMM modules. The DMH translates Rambus memory transactions to SDRAM DDR. The DIMM modules can be 64, 128, 256, 512 Mbit, 1 and 2 Gbit technology. Each memory board can support up to 16 GB of system memory.

**Note:** The DIMMs off each DMH must be symetrical with the DIMMs of all the other DMHs. That is, each DMH must hold the same type of DIMM on DMH 1, 2, 3, and 4. The memory upgrade granularity is the row of four DIMMs, one on each main channel, which collectively provide a cache line.

The SNC-M and DMH incorporate a 400 MHz Rambus interface. Data is transferred on each edge of the clock giving an equivalent 800 MHz bus, 16-bit data and 2-bit ECC running at 1.6 GT/s per port. Each of the four Rambus ports on the SNC-M is connected to one DMH.

The second memory port is located on the secondary side of the processor baseboard, in order to minimize the baseboard dimension and to shorten the address/control bus to the memory module. As a result, the DIMMs of the first memory board face upward while the DIMMs of the second memory module face downward. Note that both memory boards must be populated with a minimum of two DIMMs on each board.

**Note:** Both primary and secondary side memory boards must be installed for the processor node to function properly.

#### 2.4.3 Scalability Port I/O Bus Interface

The primary interface between the I/O baseboard and the processor baseboard is the scalability port (SP) bus provided by the SNC-M. The scalability port is a simultaneous bidirectional (SBD) trilevel bus, which provides a high-speed point-to-point link between a processor baseboard and a target (IO board or SPS). Each port is a 4 byte, quad-pumped (4x) 200MHz bus. This gives a raw throughput of 3.2 GT/s per direction for each bus off the SNC-M. The SNC-M has two SP ports that, combined, have a total bandwidth of 6.4 GB/s per direction, or a total bidirectional bandwidth of 12.8 GB/s.

**Note:** The scalability port bus has a maximum signal routing length of 20 inches plus two VHDM connectors between the SNC-M and SIOH/SPS. Approximately 3.5 inches is used on the Itanium 2 processor baseboard.

For bus specifications, refer to the Intel<sup>®</sup> E8870 External Design Specification and the Electrical, Mechanical, and Thermal Specification.

Along with the SP bus, there are other signals shared between the processor baseboard and the I/O baseboard to support error handling, reset and power control, and system configuration and monitoring (BIOS and server management). Refer to Table 2-26 for a list of non-SP bus signals.

#### 2.4.4 Clock Distribution

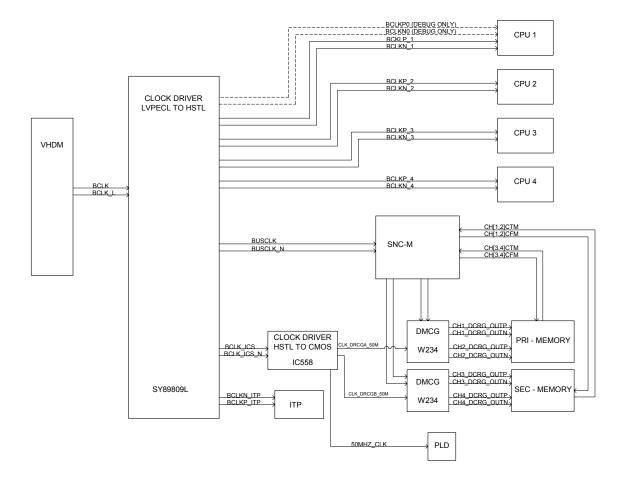

Figure 2-5 shows the clock distribution architecture for the Itanium 2/E8870 processor baseboard. In the Server System SR870BN4, the 200-MHz clock is provided by the I/O board. The processor baseboard provides the clock buffers/drivers for clock distribution.

Figure 2-5. Processor Baseboard Clock Distribution

| Clock                           | Description                                             | Logic Family                 | Frequency |

|---------------------------------|---------------------------------------------------------|------------------------------|-----------|

| BCLK/BCLK_L                     | Main Bus Clock from I/O board                           | HSTL                         | 200 Mhz   |

| BCLKP_1/BCLKN_1                 | Processor 1 Clock                                       | HSTL                         | 200 Mhz   |

| BCLKP_1/BCLKN_1                 | Processor 1 Clock                                       | HSTL                         | 200 Mhz   |

| BCLKP_1/BCLKN_1                 | Processor 1 Clock                                       | HSTL                         | 200 Mhz   |

| BCLKP_1/BCLKN_1                 | Processor 1 Clock                                       | HSTL                         | 200 Mhz   |

| BUSCLK/BUSCLK_L                 | SNC-M Clock                                             | HSTL                         | 200 Mhz   |

| BCLK_ICS/BCLK_IC<br>S_N         | ICS558 Clock                                            | HSTL                         | 200 Mhz   |

| BCLKN_ITP/BCLKP_I<br>TP         | ITP input Clock                                         | HSTL                         | 200 Mhz   |

| CLK_DRCGA_50M                   | Input Clock for DRCG (Direct Rambus<br>Clock Generator) | CMOS                         | 50 Mhz    |

| CLK_DRCGB_50M                   | Input Clock for DRCG                                    | CMOS                         | 50 Mhz    |

| 50Mhz_Clk                       | PLD input clock                                         | CMOS                         | 50 Mhz    |

| Ch1_DRCG_OUTP/<br>Ch1_DRCG_OUTN | Channel 1 Rambus Clock                                  | RSL (Rambus<br>Signal Level) | 400 Mhz   |

#### Table 2-1. Clock Frequency Chart

| Ch2_DRCG_OUTP/<br>Ch2_DRCG_OUTN | Channel 2 Rambus Clock | RSL (Rambus<br>Signal Level) | 400 Mhz |

|---------------------------------|------------------------|------------------------------|---------|

| Ch3_DRCG_OUTP/<br>Ch3_DRCG_OUTN | Channel 3 Rambus Clock | RSL (Rambus<br>Signal Level) | 400 Mhz |

| Ch4_DRCG_OUTP/<br>Ch4_DRCG_OUTN | Channel 4 Rambus Clock | RSL (Rambus<br>Signal Level) | 400 Mhz |

| CH[1,2]_CTM                     | Clock To Memory        | RSL                          | 400 Mhz |

| CH[3,4]_CTM                     | Clock To Memory        | RSL                          | 400 Mhz |

| CH[1,2]_CFM                     | Clock From Memory      | RSL                          | 400 Mhz |

| CH[3,4]_CFM                     | Clock From Memory      | RSL                          | 400 Mhz |

#### 2.4.5 Voltage Regulators

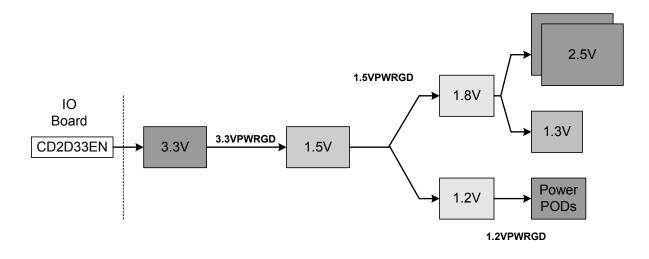

The processor board contains three plug-in D2D regulators to generate two primary voltages, 2.5 V and 3.3 V from 48 V. The 2.5 V D2Ds supply voltage for the DIMM interface of the DMH chip, the DDR DRAM devices, and drive the 1.25 V regulator (for DDR termination). The 3.3 V D2D is the primary voltage used for miscellaneous logic, FWH interface, clock drivers, and drives the input voltage for the 1.2 V, 1.5 V, and 1.8V embedded regulators.

The processor board has three embedded switching regulators, one for the AGTL+ termination voltage (1.2 V) required by the FSB, one 1.8V regulator for the Clocks and Rambus Signaling Level (RSL) logic between the SNC-M and DMH, and one for the SNC-M core (1.5 V) power. There is also one linear regulator to supply the Scalability Port Power (1.3 V). The switching regulators convert 3.3 V from the +3.3 V supply rail into their respective supply outputs. The Scalability Port linear regulator converts 1.8 V into 1.3 V. In addition to the on-board regulators, the Itanium 2 processor requires a separate power pod that supplies the voltage necessary to power the core and cache for each processor. The power pod connects directly to the Itanium 2 processor and runs off of +48 V.

#### 2.4.5.1 Embedded Regulator Voltage ID (VID) table

|       | VID  | Pin Nam | e    | VID Pin Name |        |       |      |      |      |      |        |

|-------|------|---------|------|--------------|--------|-------|------|------|------|------|--------|

| VID25 | VID3 | VID2    | VID1 | VID0         | Vout   | VID25 | VID3 | VID2 | VID1 | VID0 | Vout   |

| mV    |      |         |      |              |        | mV    |      |      |      |      |        |

| 0     | 0    | 1       | 0    | 0            | 1.050  | 0     | 1    | 1    | 0    | 0    | 1.450  |

| 1     | 0    | 1       | 0    | 0            | 1.075  | 1     | 1    | 1    | 0    | 0    | 1.475  |

| 0     | 0    | 0       | 1    | 1            | 1.100  | 0     | 1    | 0    | 1    | 1    | 1.500* |

| 1     | 0    | 0       | 1    | 1            | 1.125  | 1     | 1    | 0    | 1    | 1    | 1.525  |

| 0     | 0    | 0       | 1    | 0            | 1.150  | 0     | 1    | 0    | 1    | 0    | 1.550  |

| 1     | 0    | 0       | 1    | 0            | 1.175  | 1     | 1    | 0    | 1    | 0    | 1.575  |

| 0     | 0    | 0       | 0    | 1            | 1.200* | 0     | 1    | 0    | 0    | 1    | 1.600  |

| 1     | 0    | 0       | 0    | 1            | 1.225  | 1     | 1    | 0    | 0    | 1    | 1.625  |

| 0     | 0    | 0       | 0    | 0            | 1.250  | 0     | 1    | 0    | 0    | 0    | 1.650  |

| 1     | 0    | 0       | 0    | 0            | 1.275  | 1     | 1    | 0    | 0    | 0    | 1.675  |

| 0     | 1    | 1       | 1    | 1            | 1.300  | 0     | 0    | 1    | 1    | 1    | 1.700  |

| 1     | 1    | 1       | 1    | 1            | 1.325  | 1     | 0    | 1    | 1    | 1    | 1.725  |

| 0     | 1    | 1       | 1    | 0            | 1.350  | 0     | 0    | 1    | 1    | 0    | 1.750  |

| 1     | 1    | 1       | 1    | 0            | 1.375  | 1     | 0    | 1    | 1    | 0    | 1.775  |

| 0     | 1    | 1       | 0    | 1            | 1.400  | 0     | 0    | 1    | 0    | 1    | 1.800* |

| 1     | 1    | 1       | 0    | 1            | 1.425  | 1     | 0    | 1    | 0    | 1    | 1.825  |

#### Table 2-2. Embedded Regulator VID table

Note: 0 = stuffed 0 ohm resistor

1 = unstuffed

\* VID configuration for current regulators being used.

#### 2.4.5.2 AD2D VID Specification

#### Table 2-3. AD2D VID table

|      | VID               | Pin Nam | e <sup>1</sup> |      | Vout |      | VID Pin Name |      |      |      | Marit |

|------|-------------------|---------|----------------|------|------|------|--------------|------|------|------|-------|

| VID4 | VID3 <sup>2</sup> | VID2    | VID1           | VID0 | Vout | VID4 | VID3         | VID2 | VID1 | VID0 | Vout  |

| 1    | 1                 | 1       | 1              | 1    | 2.0  | 0    | 1            | 1    | 1    | 1    | 1.30  |

| 1    | 1                 | 1       | 1              | 0    | 2.1  | 0    | 1            | 1    | 1    | 0    | 1.35  |

| 1    | 1                 | 1       | 0              | 1    | 2.2  | 0    | 1            | 1    | 0    | 1    | 1.40  |

| 1    | 1                 | 1       | 0              | 0    | 2.3  | 0    | 1            | 1    | 0    | 0    | 1.45  |

| 1    | 1                 | 0       | 1              | 1    | 2.4  | 0    | 1            | 0    | 1    | 1    | 1.50  |

| 1    | 1                 | 0       | 1              | 0    | 2.5* | 0    | 1            | 0    | 1    | 0    | 1.55  |

| 1    | 1                 | 0       | 0              | 1    | 2.6  | 0    | 1            | 0    | 0    | 1    | 1.60  |

| 1    | 1                 | 0       | 0              | 0    | 2.7  | 0    | 1            | 0    | 0    | 0    | 1.65  |

| 1    | 0                 | 1       | 1              | 1    | 2.8  | 0    | 0            | 1    | 1    | 1    | 1.70  |

| 1    | 0                 | 1       | 1              | 0    | 2.9  | 0    | 0            | 1    | 1    | 0    | 1.75  |

| 1    | 0                 | 1       | 0              | 1    | 3.0  | 0    | 0            | 1    | 0    | 1    | 1.80  |

| 1    | 0                 | 1       | 0              | 0    | 3.1  | 0    | 0            | 1    | 0    | 0    | 1.85  |

| 1    | 0                 | 0       | 1              | 1    | 3.2  | 0    | 0            | 0    | 1    | 1    | 1.90  |

| 1    | 0                 | 0       | 1              | 0    | 3.3* | 0    | 0            | 0    | 1    | 0    | 1.95  |

| 1    | 0                 | 0       | 0              | 1    | 3.4  | 0    | 0            | 0    | 0    | 1    | 2.00  |

| 1    | 0                 | 0       | 0              | 0    | 3.5  | 0    | 0            | 0    | 0    | 0    | 2.05  |

Note: (1): 0 = 0 ohm resistor stuffed (GND)

1 = resistor unstuffed (Open)

(2): TD2D support uses pin 9 which selects between 2.5V and 3.3V. Please note that TD2D is a subset of the AD2D specification.

\*Current Configuration for processor board D2Ds.

#### 2.4.5.3 Processor Power Pod

The voltage supply for each of the four processors is supplied independently by a power pod. Each power pod will provide the processor and cache with the voltages they require from the +48 V power rail provided to it from the processor board. The 48 volts will be supplied to the processor power pods via a Y-cable from a four-pin connector on the processor board to each power pod.

The following list shows the features of the power pod regulator:

- 48 V input @ 3.85 A +/- 10%

- 48 V ground return

- Output: 0.95 V to 1.70 V @ 130 W

- Efficiency at 130 W is 77%

#### 2.4.5.4 +3.3 V Regulator

The 3.3 V converter on the processor baseboard provides power for the SNC-M core regulator, the FSB regulator, the 1.8 V regulator for the Rambus termination, the firmware hubs, and the clock buffer/driver circuits and other miscellaneous logic.

The following list shows the features of the 3.3 V DC to DC regulator (Source: *A-D2D Server Distributed Power 48 V Input (Advanced) DC-to-DC Converter Design Specification*)

- 48 V input @ 2.37 A +/- 10%

- 48 V ground return

- Output: 3.3 V @ 30 Amps (Max)

#### 2.4.5.5 +2.5 V Regulator

The 2.5 V regulator on the processor baseboard provides power for the DIMM interface pins of the DMH, 1.25 V regulator on the memory boards, and DDR DRAMs. There are two 2.5 V D2D which are configured for current sharing.

The following list shows the features of the 3.3 V D2D regulator (source: *A-D2D Server Distributed Power 48 V Input (Advanced) DC-to-DC Converter Design Specification*).

- 48 V input @ 2.37 A +/- 10%

- 48 V ground return

- Output: 2.5 V @ 32 Amps (Max)

#### 2.4.5.6 +1.2 V (Vtt) Embedded Regulator

The 1.2 V voltage regulator circuit utilizes a HIP4006E<sup>\*</sup> controller, which provides an accurate, high drive programmable supply voltage to the processor bus. The following list shows the features of the onboard  $V_{tt}$  voltage regulator.

- 0 A to 16 A maximum output current

- 85% efficiency at maximum load

- Active-High PWRGD open collector output

- Active-Low output disable input

- Short circuit protection

#### Table 2-4. 1.2 V and Vref Typical Voltage and Tolerance

| Voltage       | Description                                            | Min     | Туре            | Max     | Tolerance          |

|---------------|--------------------------------------------------------|---------|-----------------|---------|--------------------|

| 3.3 V         | Input voltage                                          | 3.003 V | 3.3 V           | 3.597 V | 3.3 V +/-9%        |

| 12 V<br>Stdby | Input Bias Voltage                                     | 10.8 V  | 12 V            | 13.2 V  | 12 V +/-<br>10%10% |

| 1.2 V         | Output buffer and termination voltage for GTL+ drivers | 1.182 V | 1.2 V           | 1.218 V | 1.2 V +/-1.5%      |

| Vref          | Reference voltage for GTL+ receivers                   |         | (2/3)*(1.2 V) V |         |                    |

#### 2.4.5.7 +1.5 V Embedded Regulator

The 1.5 V voltage regulator circuit utilizes a HIP4006E controller, which provides accurate, high drive, programmable supply voltage to the E8870 SNC-M component on the processor baseboard. The following list shows the features of the onboard VCC 1.5 voltage regulator:

- 0 A to 16 A maximum output current

- 85% efficiency at maximum load

- Active-High PWRGD open collector output

- Active-Low output disable input

- Short circuit protection

#### Table 2-5. 1.5 V Tolerance

| Voltage       | Description                                                       | Min     | Туре  | Max     | Tolerance   |

|---------------|-------------------------------------------------------------------|---------|-------|---------|-------------|

| 3.3 V         | Input voltage                                                     | 3.003 V | 3.3 V | 3.597 V | 3.3 V +/-9% |

| 12 V<br>Stdby | Input Bias Voltage                                                | 10.8 V  | 12 V  | 13.2 V  | 12 V +/-10% |

| 1.5 V         | Provides core voltage to Intel <sup>®</sup> E8870 SNC-M component | 1.45 V  | 1.5 V | 1.53 V  | 1.5 V +/-3% |

#### 2.4.5.8 +1.8 V Embedded Regulator

The 1.8 V voltage regulator circuit utilizes a HIP4006E controller which provides accurate, high drive, programmable supply voltage to the Intel E8870 SNC-M component on the processor baseboard, and defines the RSL logic. The following list shows the features of the onboard VCC 1.8 voltage regulator:

- 0 A to 16 A maximum output current

- 85% efficiency at maximum load

- Active-High PWRGD open collector output

- Active-Low output disable input

Short circuit protection

| Voltage    | Description                                                          | Min     | Туре          | Max     | Tolerance   |

|------------|----------------------------------------------------------------------|---------|---------------|---------|-------------|

| 3.3 V      | Input voltage                                                        | 3.003 V | 3.3 V         | 3.597 V | 3.3 V +/-9% |

| 12 V Stdby | Input Bias Voltage                                                   | 10.8 V  | 12 V          | 13.2 V  | 12 V +/-10% |

| 1.8 V      | Provides core voltage to Intel <sup>®</sup><br>E8870 SNC-M component | 1.74 V  | 1.8 V         | 1.85 V  | 1.8 V +/-3% |

| Vref(RSL)  | Reference voltage for RSL Logic<br>Receivers                         |         | (77% 1.8 V) V |         |             |

#### 2.4.5.9 +1.3V Linear Regulator

The 1.3 V voltage regulator circuit utilizes a EZ1581 linear regulator, which provides accurate voltage to the E8870 SNC-M SP bus drivers on the processor baseboard. The following list shows the features of the onboard 1.3 V voltage regulator.

- 2.0 A maximum output current

- 70% efficiency at maximum load

- Thermal shutdown short circuit protection

- Active-High output disable input (3.3 V enables circuit, 0 V disables output)

- Output protection Schottky to input

#### Table 2-7. 1.3 V Tolerance

| Voltage | Description                | Min     | Туре  | Max     | Tolerance   |

|---------|----------------------------|---------|-------|---------|-------------|

| 1.8 V   | Input Voltage              | 1.74 V  | 1.8 V | 1.85 V  | 1.8 V +/-3% |

| 1.3 V   | SP bus driver bias voltage | 1.235 V | 1.3 V | 1.365 V | 1.3 V +/-5% |

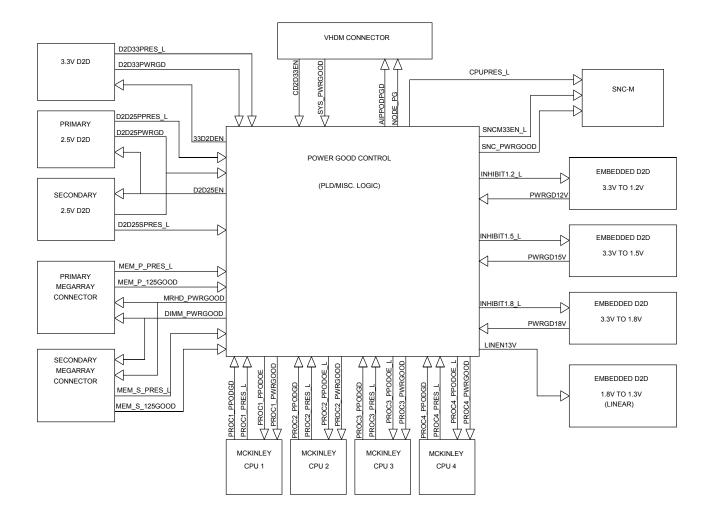

#### 2.4.6 Power Good/Reset Control

Reset and power good information is communicated between the I/O and processor board using several different signals. The processor board uses the input signals to control the order that power rails and board components are enabled. The I/O board uses the processor board outputs to control the system power sequencing. Table 2-8 describes the power good and reset signals shared between the processor and I/O baseboard. The sections that follow the table describe the power sequencing events on the processor board and the types of resets that are supported.

Processor board and I/O board Power Good/Reset Interface signal details are as follows (see the VHDM Connector section for more information).

#### **Buffer Signal Directions**

| Buffer Type | Direction |

|-------------|-----------|

| 1           | Input     |

| 0           | Output    |

#### **Signal Descriptors**

| Buffer Type | Description    |

|-------------|----------------|

| CMOS        | Push/Pull CMOS |

| OD          | Open drain     |

#### Table 2-8. Processor Board and I/O Board Power Good/Reset Interface Signals

| Signal               | Туре                    | Description                                                                                                                                                               |

|----------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYS_PWRGOOD          | I<br>3.3V STDBY<br>CMOS | <b>System Power Good:</b> I/O board output that notifies the processor board that all power rails in the system are valid.                                                |

| CD2D33EN             | I<br>3.3V STDBY<br>CMOS | <b>3.3 V D2D Enable:</b> I/O board output that is asserted when the I/O portion of the system is ready for the processor board to enable the 3.3V D2D.                    |

| PPODOE               | I<br>3.3V STDBY<br>CMOS | <b>Power Pod Output Enable:</b> I/O board output that is asserted when the I/O portion of the system is ready for the processor board to enable the processor power pods. |

| RESETI_L             | I<br>3.3V STDBY<br>CMOS | <b>RESET Input:</b> I/O board output that is asserted when the I/O portion of the system wants to reset the processors and Intel <sup>®</sup> E8870 SNC-M.                |

| AIPPODGD             | O<br>3.3VSTDBY<br>OD    | All Installed Power Pod Good: Asserted when at least<br>one of the installed processors has asserted processor<br>power pod power good.                                   |

| PROCESSOR_PRES<br>_L | 0<br>1.5V OD            | <b>Processor Present:</b> This signal is asserted when there is at least one processor present in the system. This signal is located only on the processor board.         |

| NODE_PG              | O<br>3.3VSTDBY<br>CMOS  | <b>Node Power Good:</b> Tells the I/O portion of the system that all power rails on the processor board are valid.                                                        |

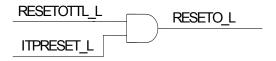

| RESETO_L             | O<br>3.3VSTDBY<br>CMOS  | <b>Reset Output:</b> This signal is asserted to notify the I/O portion of the system of SNC-M hard resets and ITP resets (defined in Section 2.4.6.2, "Reset").           |

#### 2.4.6.1 Power Sequencing

When a system is first powered-up, there is a specific order in which the power rails need to be brought up. Several events occur to ensure this order and notify the rest of the system when the power rails are valid. The following list describes the sequence of these events.

#### **Power-Up Sequence**

- 1. By default, the 12 Vstndby and 3.3 Vstndby rails should be enabled when the system is plugged in. These rails are enabled on the processor board when the I/O board asserts STDBYEN to the processor board standby hot-plug switches.

- 2. The I/O board drives 48VEN to enable +48 V on the processor board.

- 3. The 3.3 V D2D is enabled if both memory boards are in the system and the I/O board asserts CD2D33EN.

- 4. The 3.3 V D2D power good signal drives the enable for the 1.5 V regulator.

- 5. The power good signal from the 1.5 V embedded regulator drives the enable for the 1.2 V regulator.

- 6. The power good signal from the 1.5 V regulator drives the enable for the 1.8 V regulator.

- 7. The power good signal from the 1.2 V regulator drives the output enables for the installed processor power pods.

- 8. The power good signal from the 1.5 V regulator drives the enable to the 1.3 V linear regulator.

- 9. The enable for the 2.5 V D2Ds is driven by the power good signal from the 1.8 V regulator and the 3.3v D2D power good. If either one of the D2Ds is not present on the board, the 2.5 V rail will not be brought up.

- 10. Node power good (Node\_PG) is asserted back to the I/O board when all embedded regulators, D2Ds, memory board 1.25 V rails, and installed power pods are good. The I/O baseboard uses NODE\_PG to determine when it tells the processor board that the power rails for the entire system are good.

- 11. The clocks are enabled (ALLCLKSEN) when Node\_pg is asserted.

- 12. The processor board drives the installed power pod power good signal (AIPPODGD) back to the I/O board when any one of the installed processors asserts power pod power good (PPODGD).

- 13. The processor board enables the processors on the board as soon as SYS\_PWRGOOD is received from the I/O board and each installed processor power pod indicates that power is good (PROC[4:1]\_PPODGD is asserted).

- 14. SYS\_PWRGOOD from the I/O board drives the enable for the SNC-M, DMH, and memory DIMMS.

Figure 2-6 shows the order in which the processor board power rails are enabled.

#### Figure 2-6. Rail Power-up Sequence.

Figure 2-7 shows a block diagram of the processor board's power sequencing control system.

#### Figure 2-7. The Processor Board's Power Sequencing Control System

#### 2.4.6.2 Reset

There are six types of system resets supported by the processor baseboard. These resets are described in Table 2-9.

| Reset Type       | Description                                                                                                                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-Good Reset | Occurs when the system power logic causes a power good assertion.<br>This resets the SNC-M configuration and transaction states, as well as<br>the processors. Whenever the system is powered on, it goes through a<br>power good reset. |

#### Table 2-9. Different Resets Supported by the Procesor Board

| Reset Type                   | Description                                                                                                                                                                                                                                                                                                              |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hard Reset                   | A system reset caused by the assertion of RESETI_L. As a result of a hard reset, the processors, SNC-M, and memory bus are reset to a known state.                                                                                                                                                                       |

| Processor-Only Hard<br>Reset | A system reset that only resets the processors. This reset can be triggered by setting the SAVCFG, SAVMEM, and SNC RESET command bits in the SNC System Reset register (SYRE).                                                                                                                                           |

| SNC-M Local Hard Reset       | This is a type of warm reset that resets only the processors, DMH, and LPC-related components. This reset can be performed by setting the SNCReset configuration bit in the SNC-M System Reset Register (SYRE).                                                                                                          |

| Processor Bus BINIT_L        | This reset only resets the SNC-M and forces the Processors to the BINIT vector. The reset occurs when the processor bus drives BINIT_L low. Only local memory will be accessible after BINIT_L has been driven low.                                                                                                      |

| Soft Reset                   | This reset forces the processors to begin executing code at the boot vector. Soft resets are triggered when INIT_L is driven on the processor bus. INIT_L can be driven by either the SNC-M (when the SoftReset configuration bit is set in the System Reset Register [SYRE]) or the ICHX (as a result of an I/O event). |

For further information on these resets, please refer to the *Intel*® *E8870 System Architecture Specification*.

#### 2.4.7 Programmable Logic Devices

There are two programmable logic devices (PLD) on the processor board. The first PLD is the Power Good/Reset PLD. This device's primary responsibility is managing the power sequencing described in Section 2.4.6.1. However, the PLD also provides logic that performs reset, server management, and JTAG functions.

The second PLD is called the Legacy Synchronization PLD and it supports synchronizing the legacy interrupt signals and RESETI\_L so that they deterministically arrive at the processors. As an additional feature, this PLD also controls firmware hub initialization. The Power Good/Reset and Legacy Synchronization PLD's are described in Sections 2.4.7.1 and 2.4.7.2. The following conventions are used to help describe the PLDs.

| Buffer | Signal | Directions |

|--------|--------|------------|

|--------|--------|------------|

| Buffer Type | Direction |

|-------------|-----------|

| 1           | Input     |

| 0           | Output    |

#### **Signal Descriptors**

| Buffer Type | Description    |

|-------------|----------------|

| CMOS        | Push/Pull CMOS |

| OD          | Open drain     |

| OC          | Open Collector |

#### 2.4.7.1 Power Good/Reset PLD

The Power Good/Reset PLD implements most of the power sequencing and reset-related logic on the processor board. This PLD also contains logic to enable/disable the SP ports and drive TRST\_L to the processors and SNC-M.

A Lattice\* ISPLSI2064VE part is used for the Power Good/Reset PLD. This component can be powered off of 3.3 V standby and supports in-system programming. The ISPLSI2064VE has 64 I/O pins, 64 registers, and the ability to define open-drain outputs. The processor board uses the 100-pin TQFP version of the part. Refer to the Lattice Data sheet for further information on the ISPLSI2064VE. Table 2-10 defines the PLD signals, their pin numbers, and pin names. The PLD is powered off of 3.3v standby. However, the device can be configured with Open Drain outputs and, thus, requires external circuitry for the voltage.

| Signal       | Туре                   | Description                                                                                                                                                     | Pin # | Pin Name |

|--------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|

| ALLCLKSEN    | 0<br>3.3V OD           | <b>Enable All Clocks :</b> This signal<br>enables the processor board clocks. It<br>is asserted when all of the processor<br>and memory boards rails are valid. | 48    | IO23     |

| AIPPODGD     | O<br>3.3VSTDBY<br>CMOS | All installed Power Pod Power<br>Good: Asserted when at least one<br>processor sends a power pod good<br>signal.                                                | 22    | 104      |

| CD2D33EN     | I<br>3.3VSTDBY<br>CMOS | <b>3.3 V D2D Enable:</b> I/O board output that is asserted when the I/O portion of the system is ready for the processor board to enable the 3.3 V D2D.         | 34    | IO14     |

| CPUPRES_L    | 0<br>1.5V OD           | <b>PROCESSOR Present:</b> This signal is asserted when there is at least one processor present in the system.                                                   | 24    | 106      |

| D2D25EN      | O<br>3.3VSTDBY<br>CMOS | 2.5 V Enable: Enables the 2.5 V rail.                                                                                                                           | 2     | IO58     |

| D2D33EN      | O<br>3.3VSTDBY<br>CMOS | 3.3 V Enable: Enables the 3.3 V rail.                                                                                                                           | 91    | IO49     |

| D2D25PWRGD   | I<br>3.3VSTDBY<br>OC   | <b>2.5 V Power Good:</b> Asserted when the 2.5 V primary and secondary D2D output is valid.                                                                     | 57    | IO30     |

| D2D33PWRGD   | I<br>3.3VSTDBY<br>OC   | <b>3.3 V Power Good:</b> Asserted when the 3.3 V rail is valid.                                                                                                 | 55    | IO28     |

| D2D33PRES_L  | I<br>3.3VSTDBY<br>CMOS | <b>3.3 V D2D Enable:</b> Asserted when the D2D is present.                                                                                                      | 5     | 1060     |

| D2D25PPRES_L | I<br>3.3VSTDBY<br>CMOS | <b>2.5 V Primary Side D2D Present:</b><br>Asserted when the D2D is present.                                                                                     | 53    | 1027     |

#### Table 2-10. Power Good/Reset PLD Signals

| Signal        | Туре                   | Description                                                                                                                                                                                                                 | Pin # | Pin Name |

|---------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|

| D2D25SPRES_L  | I<br>3.3VSTDBY<br>CMOS | <b>2.5 V Secondary Side D2D Present:</b> Asserted when the D2D is present.                                                                                                                                                  | 27    | 108      |

| EMBEN12V      | O<br>3.3VSTDBY<br>CMOS | <b>1.2 V Embedded Regulator Enable:</b><br>Enables the 1.2 V regulator.                                                                                                                                                     | 56    | IO29     |

| EMBEN15V      | O<br>3.3VSTDBY<br>CMOS | <b>1.5 V Embedded Regulator Enable:</b><br>Enables the 1.5 V regulator.                                                                                                                                                     | 96    | IO53     |

| EMBEN18V      | O<br>3.3VSTDBY<br>CMOS | <b>1.8 V Embedded Regulator Enable:</b><br>Enables the 1.8 V regulator.                                                                                                                                                     | 93    | IO51     |

| FWH_ID_L      | O<br>3.3VSTDBY<br>OD   | <b>Firmware Hub ID:</b> This signal is<br>asserted to swap the ID bits of FWH 0<br>and 2. The signal must be held for as<br>long as the IDs need to be swapped.                                                             | 46    | IO21     |

| ITPRESET_L    | I<br>3.3V CMOS         | In Target Probe (ITP) Reset: This signal is asserted to perform an ITP initiated hard reset.                                                                                                                                | 84    | IO46     |

| JMP_FWH_ID_L  | I<br>3.3V CMOS         | <b>Jumper FWH ID:</b> This signal is<br>asserted when the FWH ID jumper is<br>installed. When this signal is active,<br>the system will change firmware hub 0<br>to firmware hub 2 and firmware hub 2<br>to firmware hub 0. | 49    | 1024     |

| JMP_TRST_L    | I<br>3.3VSTDBY<br>CMOS | <b>Jumper TRST_L:</b> Asserted when the TRST jumper is put in place.                                                                                                                                                        | 98    | IO55     |

| LINEN13V      | O<br>3.3VSTDBY<br>CMOS | <b>1.3 V Embedded Regulator Enable:</b><br>Enable for the 1.3V Embedded<br>Regulator.                                                                                                                                       | 52    | IO26     |

| LPC_CTRL_L    | O<br>3.3VSTDBY<br>CMOS | <b>LPC Control Signal:</b> When asserted, this signal enables the LPC bus.                                                                                                                                                  | 99    | IO56     |

| MEM_P_PRES_L  | I<br>3.3VSTDBY<br>CMOS | <b>Primary-side Memory Board</b><br><b>Present:</b> Asserted when the primary-<br>side memory board is connected to<br>the processor board.                                                                                 | 85    | IO47     |

| MEM_S_PRES_L  | I<br>3.3VSTDBY<br>CMOS | Secondary-side Memory Board<br>Present: Asserted when the<br>secondary-side memory board is<br>connected to the processor board.                                                                                            | 23    | 105      |

| MEM_P_125GOOD | I<br>3.3VSTDBY<br>CMOS | <b>Primary Memory 1.25 V Power</b><br><b>Good:</b> Asserted when the primary-<br>side memory board 1.25 V rail is good.                                                                                                     | 83    | IO45     |

| MEM_S_125GOOD | I<br>3.3VSTDBY<br>CMOS | Secondary Memory 1.25 V Power<br>Good: Asserted when the secondary-<br>side memory board 1.25 V rail is good.                                                                                                               | 90    | IO48     |