# Intel® Server System SSH4 Board Set

**Technical Product Specification**

Intel order number C20142-001

**Revision 1.4**

**October**, 2003

**Enterprise Platforms and Services Marketing**

intel®

## **Revision History**

| Date     | Revision<br>Number | Modifications                                                                                                                       |

|----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 10/2002  | 1.0                | Initial release of this document.                                                                                                   |

| 12/18/02 | 1.1                | Revised to include Intel® Xeon MP® processors (Gallatin) stepping, Adaptec 7902 U320 support, 100MHz PCI Unified in this document   |

| 07/21/03 | 1.3                | Added Support for Intel® Xeon™ MP processor 2.8 GHz stepping,<br>miscellaneous clarifying edits.                                    |

| 10/15/03 | 1.4                | Revised to include PCI-X in Drawings and descriptions Added a section for Advanced Memory Configurations (memory mirroring/sparing) |

### Disclaimers

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

The Intel Server System SSH4 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel, Pentium, and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2002.

## **Table of Contents**

| 1. Introd | uction                                                        | 15 |

|-----------|---------------------------------------------------------------|----|

| 1.1       | Server System SSH4 Architecture                               | 16 |

| 2. Proces | ssor and Chipset                                              | 19 |

| 2.1       | Processor Support                                             | 19 |

| 2.1.2     | APIC Bus                                                      | 20 |

| 2.1.3     | Server Management Registers and Sensors                       | 20 |

| 2.2       | ServerWorks Grand Champion Chipset                            | 20 |

| 2.2.1     | CMIC: Champion Memory and I/O Controller                      | 21 |

| 2.2.2     | CIOB30: Champion I/O Bridge                                   | 21 |

| 2.2.3     | CSB5: Champion South Bridge                                   | 22 |

| 2.2.4     | REMC: Reliability Enhanced Memory Controller                  | 22 |

| 2.2.5     | ServerWorks Grand Champion HE Chipset Memory Architecture     | 22 |

| 2.2.6     | ServerWorks Grand Champion HE Chipset System I/O Architecture | 23 |

| 2.3       | Super I/O                                                     | 23 |

| 2.3.1     | GPIO                                                          | 24 |

| 2.3.2     | Serial Ports                                                  | 25 |

| 2.3.3     | Floppy                                                        | 25 |

| 2.3.4     | Keyboard and Mouse                                            | 25 |

| 2.3.5     | Parallel Port                                                 | 25 |

| 2.3.6     | Real-time Clock                                               | 25 |

| 2.3.7     | Wake-up Control                                               | 25 |

| 2.4       | BIOS Flash                                                    | 25 |

| 3. Baseb  | oard PCI I/O Subsystem                                        | 26 |

| 3.1       | 32-bit, 33-MHz PCI Subsystem                                  | 27 |

| 3.1.1     | P32-A Slot Specifics                                          | 27 |

| 3.2       | 64-bit, 133-MHz PCI-X Subsystem                               | 28 |

| 3.2.1     | PCI-X Bus Arbitration                                         | 28 |

| 3.2.2     | P64 Slot Specifics                                            | 28 |

| 3.3       | PCI Hot Plug Support                                          | 29 |

| 3.3.1     | PCI Hot Plug Functionality                                    | 29 |

| 3.3.2     | Operating System Support                                      | 29 |

|    | 3.3.3     | Interlock Switch Support                      | 30 |  |

|----|-----------|-----------------------------------------------|----|--|

|    | 3.3.4     | Hot Plug Write Operations                     | 31 |  |

|    | 3.3.5     | PCI Power Budgeting                           |    |  |

| 3  | .4        | Device IDs (IDSEL)                            | 33 |  |

| 3  | .5        | Ultra 320 SCSI                                | 34 |  |

| 3  | .6        | Network Interface Controllers (NIC)           | 34 |  |

|    | 3.6.1     | 82559 NIC                                     | 34 |  |

|    | 3.6.2     | 82544 NIC                                     | 35 |  |

|    | 3.6.3     | Video Controller                              | 36 |  |

| 3  | .7        | Interrupt Routing                             | 37 |  |

|    | 3.7.1     | Serialized IRQ support                        | 40 |  |

|    | 3.7.2     | IRQ Scan for PCIIRQ                           | 40 |  |

| 4. | Server \$ | System SSH4 ACPI Implementation               | 41 |  |

| 4  | .1        | Front Panel Switches                          | 41 |  |

| 4  | .2        | Wake Up Sources (ACPI and Legacy)             | 42 |  |

| 5. | Server \$ | System SSH4 System Bus Error Monitoring       | 43 |  |

| 5  | .1        | PCI Bus Errors                                | 43 |  |

| 5  | .2        | Intel® Xeon™ Processor Bus Errors             | 43 |  |

| 5  | .3        | Memory Bus Errors                             | 43 |  |

| 5  | .4        | IMB Bus Errors                                | 44 |  |

| 5  | .5        | Error Escalation                              | 44 |  |

| 6. | Server    | System SSH4 DDR Memory Board                  | 45 |  |

| 6  | 5.1       | Memory DIMM Support                           | 46 |  |

| 6  | .2        | Memory Configuration                          | 46 |  |

| 6  | .3        | DDR Memory Board Components                   | 47 |  |

|    | 6.3.1     | 330-pin Edge Connector                        | 47 |  |

|    | 6.3.2     | REMC                                          | 47 |  |

|    | 6.3.3     | I <sup>2</sup> C Buses                        | 47 |  |

|    | 6.3.4     | Clocks                                        | 48 |  |

| 6  | .4        | Advanced Memory Configuration                 | 49 |  |

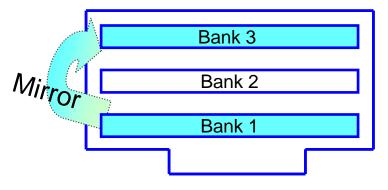

|    | 6.4.1     | Single Board Mirrored Memory                  | 49 |  |

|    | 6.4.2     | Online Spare Memory                           | 51 |  |

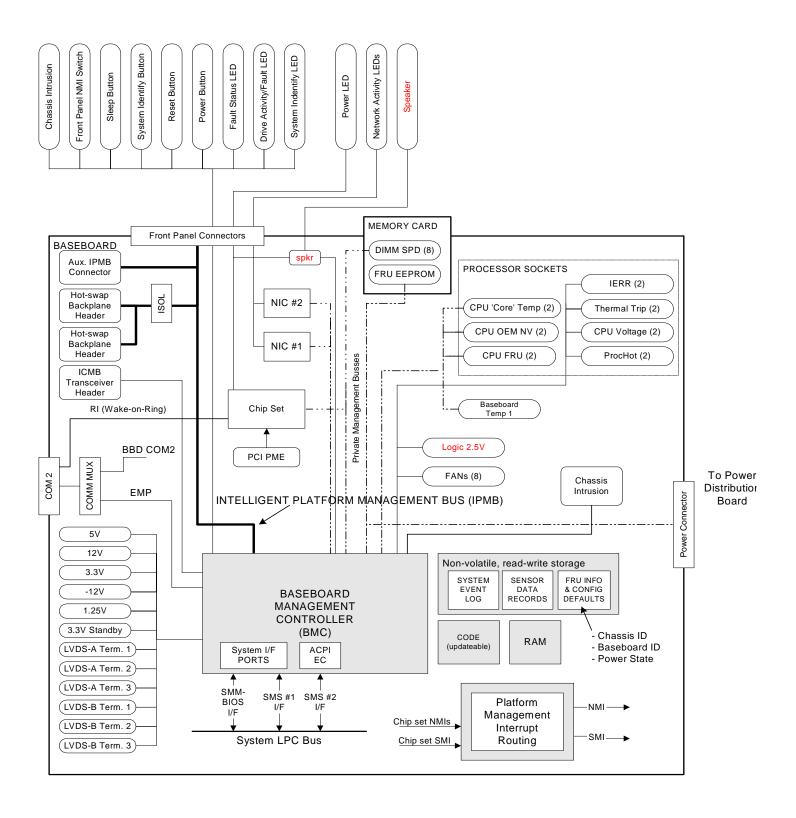

| 7. | Server I  | Management                                    | 54 |  |

| 7  | .1        | Sahalee Baseboard Management Controller (BMC) | 56 |  |

|    | 7.1.1    | Fault Resilient Booting                                   | 57 |

|----|----------|-----------------------------------------------------------|----|

| 7  | 7.2      | System Reset Control                                      | 59 |

|    | 7.2.1    | Power-up Reset                                            | 59 |

|    | 7.2.2    | Hard Reset                                                | 59 |

|    | 7.2.3    | Soft Reset                                                | 59 |

| 7  | 7.3      | Intelligent Platform Management Buses                     | 60 |

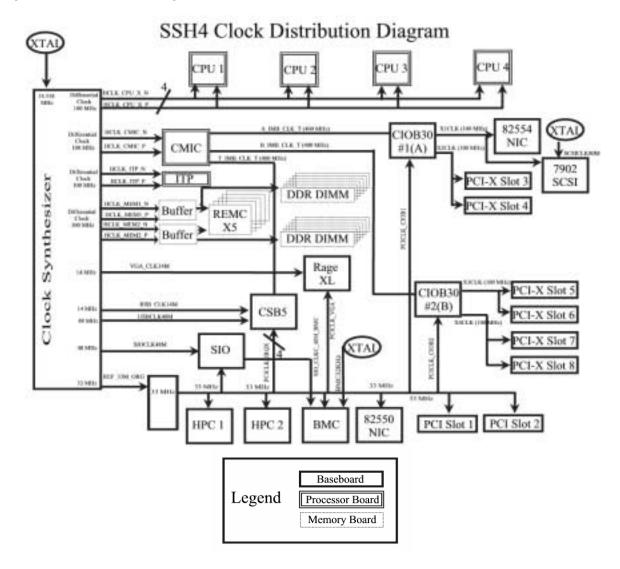

| 8. | Clock G  | Generation and Distribution                               | 62 |

| 9. | Jumper   | s and Connectors                                          | 64 |

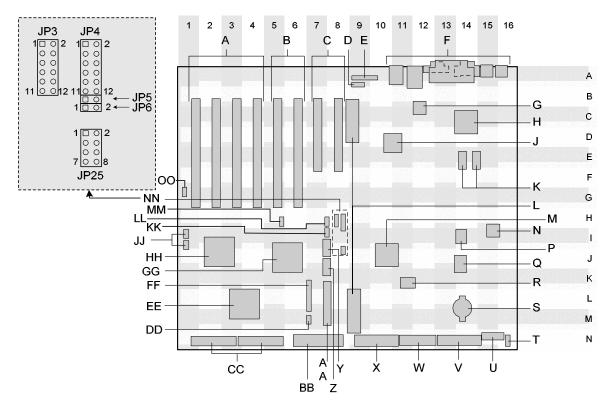

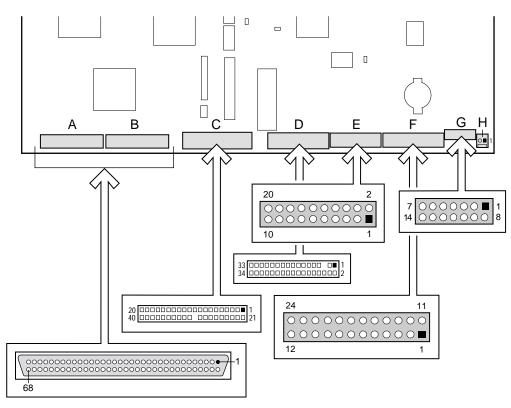

| ć  | 9.1      | Baseboard Jumper, Connector, and Component Locations      | 64 |

| ç  | 9.2      | Processor Board Connector and Component Locations         | 65 |

| ç  | 9.3      | Memory Board Connector and Component Locations            | 66 |

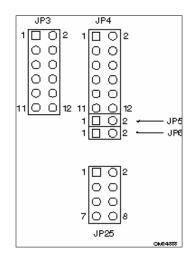

| ę  | 9.4      | Primary Baseboard Jumpers                                 | 67 |

|    | 9.4.1    | Boot Block Jumpers (JP3)                                  | 67 |

|    | 9.4.2    | Main Jumpers (JP4, JP5, JP6)                              | 68 |

| ę  | 9.5      | Extended Baseboard Jumpers                                | 69 |

| 10 | . Connec | tors                                                      | 70 |

|    | 10.1     | Connector Locations                                       | 70 |

|    | 10.2     | ICMB Connector                                            | 70 |

|    | 10.3     | HPIB Connector                                            | 70 |

|    | 10.4     | Processor Board Connectors, P21, P22 (F)                  | 71 |

|    | 10.5     | Front Panel Interface, P19, (J)                           | 73 |

|    | 10.6     | USB #3 Header                                             | 74 |

|    | 10.7     | Serial Port B Header                                      | 75 |

|    | 10.8     | IPMB Connector                                            | 75 |

|    | 10.9     | Fan Connector                                             | 76 |

|    | 10.10    | RAID LED Connector                                        | 76 |

|    | 10.11    | Power Distribution Board Interface Connectors (P10/11/29) | 77 |

|    | 10.12    | SCSI Connectors                                           | 78 |

|    | 10.13    | IDE Connector, P13 (B)                                    | 79 |

|    | 10.14    | Floppy Connector, P25 (C)                                 | 79 |

|    | 10.15    | Power Connectors                                          | 80 |

|    | 10.16    | Chassis Intrusion Connector                               | 81 |

|    | 10.17    | Memory Board Riser Connector, P12 (P)                     | 82 |

|    | 10.18    | Back Panel Connectors                                     | 84 |

| 10.18.1      | Keyboard and Mouse Ports                        | 85  |

|--------------|-------------------------------------------------|-----|

| 10.18.2      | Serial Ports                                    | 85  |

| 10.18.3      | Parallel Port Connector                         | 86  |

| 10.18.4      | Video Port                                      | 86  |

| 10.18.5      | Universal Serial Bus (USB) Interface            | 87  |

| 10.18.6      | Ethernet Connectors                             | 87  |

| 10.19        | Connector Manufacturers and Part Numbers        | 88  |

| 11. Electric | al and Thermal Specifications                   | 91  |

| 11.1         | Absolute Maximum Electrical and Thermal Ratings | 91  |

| 11.2         | Electrical Specifications                       | 92  |

| 11.2.1       | Power Budget                                    | 92  |

| 11.2.2       | Power Supply Specifications                     |     |

| 11.2.3       | Power Timing                                    |     |

| 11.2.4       | Voltage Recovery Timing Specifications          | 97  |

| 12. Mechan   | ical Specifications                             | 98  |

| 13. System   | BIOS                                            |     |

| 13.1         | BIOS Overview                                   |     |

| 13.1.1       | System BIOS                                     |     |

| 13.1.2       | Flash Update Utility                            |     |

| 13.2         | Security Features                               |     |

| 13.2.1       | Operating Model                                 |     |

| 13.2.2       | Password Protection                             |     |

| 13.2.3       | Secure Mode Timer                               |     |

| 13.2.4       | Hot Key Activation                              |     |

| 13.2.5       | Password Clear Jumper                           |     |

| 13.2.6       | Secure Mode                                     |     |

| 13.2.7       | Floppy Write Protection                         |     |

| 13.2.8       | Front Panel Lock                                |     |

| 13.2.9       | Video Blanking                                  |     |

| 13.2.10      | PS/2 Keyboard and Mouse Lock                    | 105 |

| 13.2.11      | Secure Boot (Unattended Start)                  |     |

| 13.2.12      | Fixed Disk Write Protect                        |     |

| 13.2.13      | Power Switch Inhibit                            |     |

| 13.3         | Auto-configuration Features                     |     |

|              |                                                 |     |

| 13.3.1  | Plug and Play                                       | 106 |

|---------|-----------------------------------------------------|-----|

| 13.3.2  | Multiple Processor Support                          | 108 |

| 13.3.3  | Memory Sizing                                       | 109 |

| 13.3.4  | Boot Device Selection                               | 110 |

| 13.3.5  | PS/2 Mouse and Keyboard Swapping                    | 111 |

| 13.3.6  | Boot without Keyboard and/or Mouse                  | 111 |

| 13.3.7  | Universal Serial Bus                                | 111 |

| 13.3.8  | Processor Microcode Update API                      | 111 |

| 13.3.9  | CMOS Reset                                          | 112 |

| 13.3.10 | Processor Speed Settings                            | 112 |

| 13.3.11 | Boot Logo                                           | 112 |

| 13.4    | Performance Features                                | 113 |

| 13.4.1  | Cache State on Boot                                 | 113 |

| 13.4.2  | Option ROM Shadowing                                | 113 |

| 13.5    | Reliability Features                                | 113 |

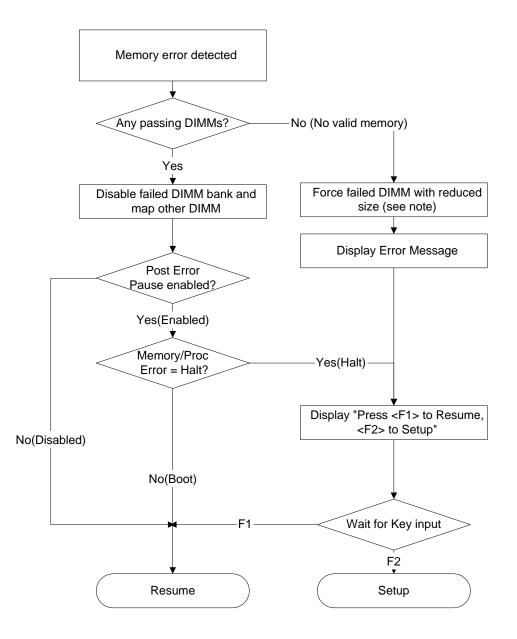

| 13.5.1  | Defective DIMM Detection and Memory Reconfiguration | 113 |

| 13.5.2  | Memory Test                                         | 116 |

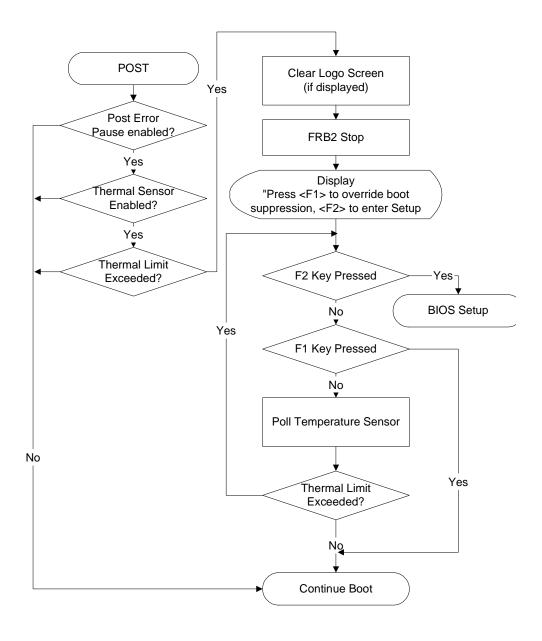

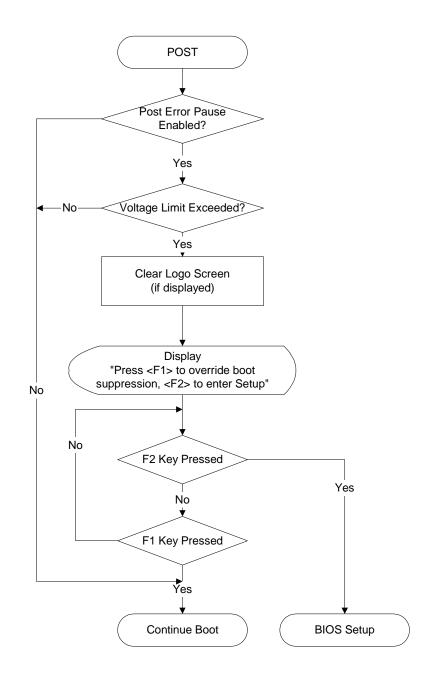

| 13.5.3  | Fault Resilient Booting (FRB)                       | 116 |

| 13.5.4  | Boot Inhibit                                        | 118 |

| 13.6    | Wired for Management (WFM)                          | 121 |

| 13.6.1  | System Management BIOS (SMBIOS)                     | 121 |

| 13.6.2  | UUID                                                | 124 |

| 13.7    | Post Memory Manager                                 | 124 |

| 13.8    | ACPI                                                | 124 |

| 13.8.1  | Front Panel Switches                                | 125 |

| 13.8.2  | Legacy Wakeup Features                              | 126 |

| 13.9    | OEM Customization                                   | 127 |

| 13.9.1  | User-supplied BIOS Code Support                     | 127 |

| 13.9.2  | OEM Logo Screen                                     | 130 |

| 13.10   | Serial Console Redirection                          | 130 |

| 13.10.1 | Operation                                           | 130 |

| 13.10.2 | Keystroke Mappings                                  | 131 |

| 13.10.3 | Limitations                                         | 133 |

| 13.10.4 | Console Redirection Menu Synchronization with BMC   | 133 |

| 13.11        | LAN Console Redirection                                   | 133 |

|--------------|-----------------------------------------------------------|-----|

| 13.12        | Service Partition Boot                                    | 134 |

| 13.13        | Warm Reset Processing                                     | 134 |

| 13.14        | Hot Key                                                   | 135 |

| 13.15        | HWID                                                      | 135 |

| 13.16        | Localization                                              | 135 |

| 13.17        | BMC Initialization                                        | 135 |

| 13.17.1      | BMC Self Test                                             | 135 |

| 13.17.2      | BMC Initialization Sequence                               | 135 |

| 13.18        | PCI-X Hot-plug Support                                    | 137 |

| 13.18.1      | PCI/PCI-X Speed and Capabilities Determination            | 137 |

| 14. Error Ha | andling                                                   | 138 |

| 14.1         | Error Sources and Types                                   | 138 |

| 14.2         | Handling and Logging System Errors                        | 138 |

| 14.2.1       | Logging Format Conventions                                | 138 |

| 14.3         | SMI Handler                                               | 141 |

| 14.3.1       | PCI Bus Error                                             | 141 |

| 14.3.2       | Intel <sup>®</sup> Xeon <sup>TM</sup> Processor Bus Error | 141 |

| 14.3.3       | Memory Bus Error                                          | 141 |

| 14.3.4       | System Limit Error                                        | 141 |

| 14.3.5       | Processor Failure                                         | 141 |

| 14.3.6       | Boot Event                                                | 141 |

| 14.3.7       | Chipset Failure                                           | 142 |

| 14.4         | Firmware (BMC)                                            | 142 |

| 14.4.1       | SEL Full                                                  | 142 |

| 14.4.2       | Timestamp Clock                                           | 142 |

| 14.5         | Error Messages and Error Codes                            | 142 |

| 14.5.1       | ASF Progress Codes                                        | 143 |

| 14.5.2       | POST Codes                                                | 143 |

| 14.5.3       | POST Error Codes and Messages                             | 148 |

| 14.5.4       | LCD Display                                               | 151 |

| 15. Setup U  | tility                                                    | 153 |

| 15.1         | Setup Utility Operation                                   | 153 |

| 15.1.1       | Entering Setup Utility                                    |     |

| 15.1.2      | Keyboard Command Bar           | 154 |

|-------------|--------------------------------|-----|

| 15.1.3      | Menu Selection Bar             | 155 |

| 15.2        | CMOS Memory Definition         | 165 |

| 15.3        | Clearing CMOS                  | 165 |

| 16. Flash U | pdate Utilities                | 166 |

| 16.1        | Loading System BIOS via iFlash | 166 |

| 16.2        | User Binary Area               | 166 |

| 16.3        | Language Area                  | 166 |

| 16.4        | OEM Logo Screen                | 166 |

| 16.5        | Recovery Mode                  | 167 |

| 16.5.1      | Performing BIOS Recovery       | 167 |

| Appendix A  | : Obsolete BIOS Features       | 169 |

| Appendix B  | B: Specifications Supported    | 170 |

| Glossary    |                                | 171 |

| Reference [ | Documents                      | 173 |

| Index       |                                | 176 |

## **List of Figures**

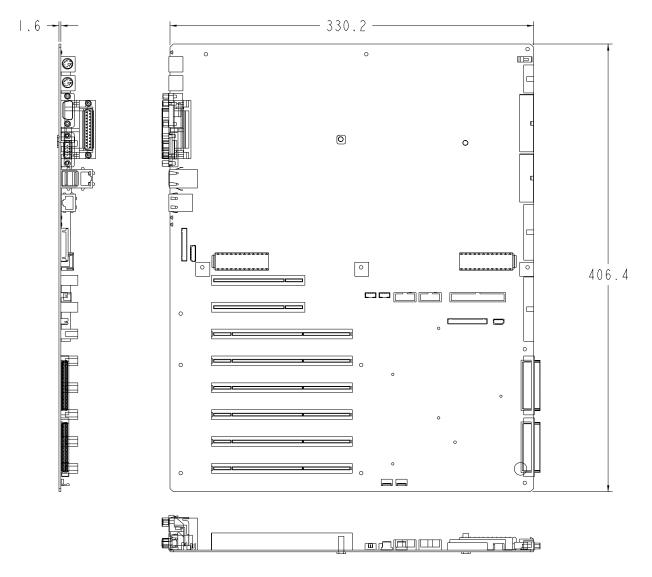

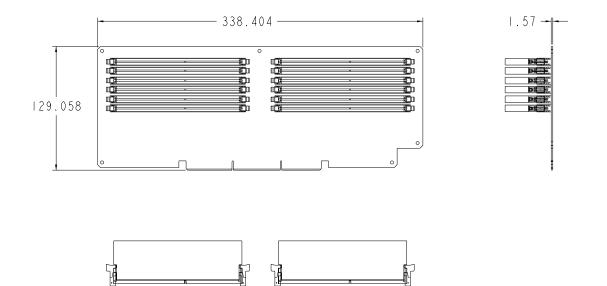

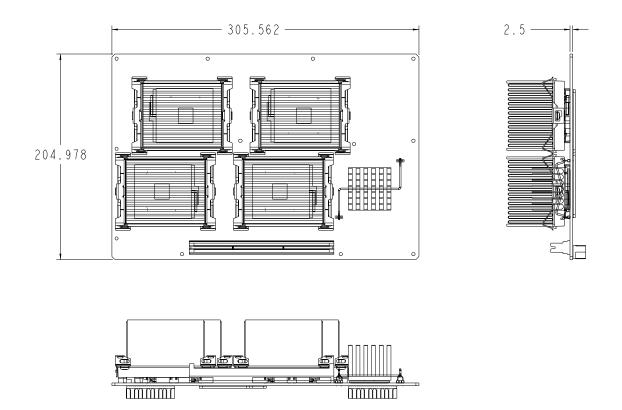

| Figure 1. Baseboard, Processor Board, and Memory Board                     | 18  |

|----------------------------------------------------------------------------|-----|

| Figure 2. PCI Bus Layout                                                   | 26  |

| Figure 3. Interrupt Routing (PIC Mode)                                     |     |

| Figure 4. Interrupt Routing (Symmetric Mode)                               | 40  |

| Figure 5. Memory Board Outline Diagram                                     | 45  |

| Figure 6. Memory Block Diagram                                             | 48  |

| Figure 7 Advanced memory Configuration                                     | 49  |

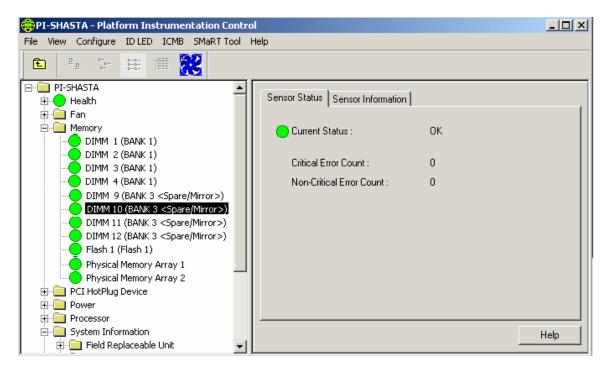

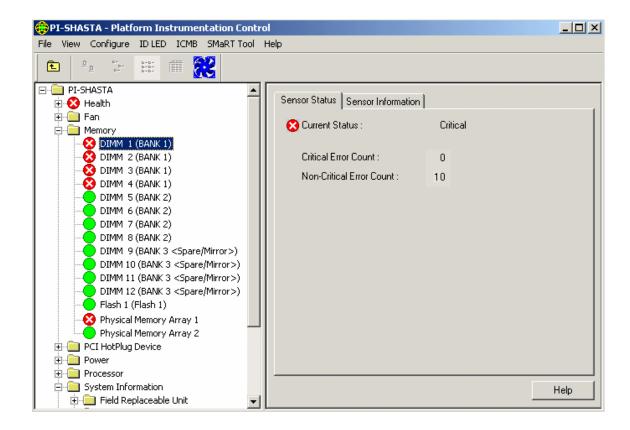

| Figure 8 Advanced Mirror Memory Configuration status Tab (Normal           | 50  |

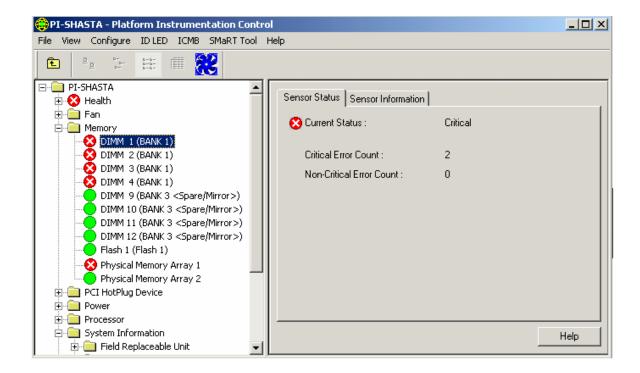

| Figure 9 Advanced Mirrir Memory Configuration Sensor Status Tab (Critical) | 51  |

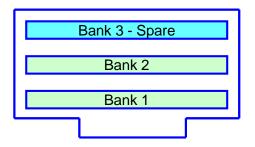

| Figure 10 Advanced Spare Memory Configuration                              | 51  |

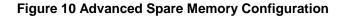

| Figure 11 Advanced Spare Memory Configuration Sensor Status Tab (Normal)   | 52  |

| Figure 12 Advanced Spare Memory Configuration Status Tab (Critical)        | 53  |

| Figure 13. SSH4 Sahalee BMC Block Diagram                                  | 55  |

| Figure 14. Baseboard and Memory Clock Distribution                         | 63  |

| Figure 15. Baseboard Connector and Component Locations                     | 65  |

| Figure 16. Processor Board Connector and Component Locations               | 65  |

| Figure 17. Memory Board Connector and Component Locations                  | 66  |

| Figure 18. Baseboard Jumpers                                               | 67  |

| Figure 19. Baseboard Front Edge Connectors                                 | 77  |

| Figure 20. Back Panel I/O Connector Graphical Locations                    | 84  |

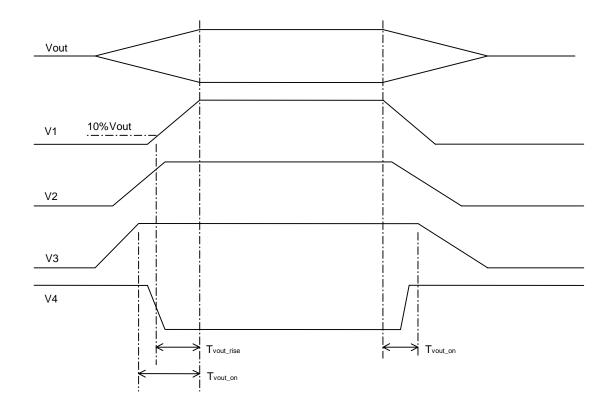

| Figure 21. Output Voltage Timing                                           | 94  |

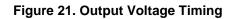

| Figure 22 Turn On Turn Off Timing                                          | 96  |

| Figure 23. Baseboard Mechanical Diagram                                    |     |

| Figure 24. Memory Board Mechanical Diagram                                 |     |

| Figure 25. Processor Board Mechanical Diagram                              |     |

| Figure 26. Memory Reconfiguration Flow Chart                               | 115 |

| Figure 27. Thermal Sensor                                                  | 119 |

| Figure 28. Voltage Sensor                                                  | 120 |

## **List of Tables**

| Table 1. Hardware Overview                                        | 16  |

|-------------------------------------------------------------------|-----|

| Table 2. Chipset Table                                            | 17  |

| Table 6. Super I/O GPIO Usage Table (Preliminary)                 | 24  |

| Table 7. PCI and PCI-X Bus Segment Characteristics                | 27  |

| Table 8. PCI-X Arbitration Connections                            | 28  |

| Table 9. Slot State and Attention Indicators                      | 30  |

| Table 10. Hot Plug Controller Write Operations                    | 31  |

| Table 11. Slot Status Register Definitions (Read to Offsets 0-14) | 32  |

| Table 12. PCI Power Consumption                                   | 33  |

| Table 13. PCI IDs                                                 | 33  |

| Table 14. Standard VGA Modes                                      | 36  |

| Table 15. Video Port Connector Pinout                             | 37  |

| Table 16. Interrupt Routing (Symmetric Mode)                      | 39  |

| Table 17. Supported Wake Events                                   | 42  |

| Table 18. I <sup>2</sup> C Addresses for Memory Module SMB        | 47  |

| Table 19. ADM1026 Input Definition                                | 56  |

| Table 20. Temperature Sensors                                     | a57 |

| Table 21. Private I <sup>2</sup> C Bus, One Devices               | 60  |

| Table 22. Private I <sup>2</sup> C Bus, Two Devices               | 60  |

| Table 23. Private I <sup>2</sup> C Bus, Three Devices             | 61  |

| Table 24. Private I <sup>2</sup> C Bus, Four Devices              | 61  |

| Table 25. Private I <sup>2</sup> C Bus, Five Devices              | 61  |

| Table 26. Boot Block Jumper Descriptions                          | 67  |

| Table 27. Main Jumper Descriptions                                | 68  |

| Table 28. Serial Port B Jumper Descriptions                       | 68  |

| Table 29. SSH4 Extended Baseboard Jumper Options                  | 69  |

| Table 30. ICMB Connector Pinout, P24 (D)                          | 70  |

| Table 31. HPIB Connector Pinout, P23, (E)                         | 70  |

| Table 32. Processor Board Connector A Pinout, P21                 | 71  |

| Table 33. Processor Board Connector B Pinout, P22                 | 72  |

| Table 34. Front Panel Header Pinout, P19 (J)                      | 73  |

| Table 35. USB #3 Header, P18 (H)                                  | 74  |

| Table 36. | Serial Port B Header, P17 (J)                          | 75  |

|-----------|--------------------------------------------------------|-----|

| Table 37. | IPMB Connector Pinout, P12 (K)                         | 75  |

| Table 38. | Fan Connector, P11 (L)                                 | 76  |

| Table 39. | RAID LED Connectors, P1 and P2 (M)                     | 76  |

| Table 40. | 68-pin SCSI Connector Pin-out, P4, P7 (A)              | 78  |

| Table 41. | IDE 40-pin Connector Pin-out                           | 79  |

| Table 42. | Legacy 34-pin Floppy Connector Pin-out                 | 79  |

| Table 43. | 20-Pin Power Connector, P28 (E)                        | 80  |

| Table 44. | 24-Pin Power Connector, P32 (F)                        | 81  |

| Table 45. | 14-Pin Power Control Connector P35 (G)                 | 81  |

| Table 46. | Chassis Intrusion Connector, P36 (H)                   | 81  |

| Table 47. | Memory Board Connector Pinout, P12 (6D)                | 82  |

| Table 48. | Keyboard and Mouse Ports (A, B)                        | 85  |

| Table 49. | Serial Port A Connector (C)                            | 85  |

| Table 50. | Parallel Port Connector                                | 86  |

| Table 51. | Video Connector                                        | 86  |

| Table 52. | Dual USB Connector                                     | 87  |

| Table 53. | LAN1 Connector                                         | 87  |

| Table 54. | LAN2 Connector                                         | 88  |

| Table 55. | Baseboard Connector Manufacturer Part Numbers          | 88  |

| Table 56. | Absolute Maximum Electrical and Thermal Specifications | 91  |

| Table 57. | Thermal Specification for Key Components               | 91  |

| Table 58. | Power Budget for SRSH4 Chassis                         | 92  |

| Table 59. | Power Budget for SPSH4 Chassis                         | 92  |

| Table 60. | Static Power Supply Voltage Specification              | 93  |

| Table 61. | Dynamic Power Supply Voltage Specification             | 93  |

| Table 62. | Voltage Timing Parameters                              | 94  |

| Table 63. | Turn On / Off Timing                                   | 95  |

| Table 64. | Transient Load Requirements                            | 97  |

| Table 65. | Security Features Operating Model                      | 102 |

| Table 66. | SMBIOS Header Structure                                | 121 |

| Table 67. | System Information (Type 1)                            | 123 |

| Table 68. | Base Board Information (Type 2)                        | 123 |

| Table 69. | System Chassis or Enclosure (Type 3)                   | 124 |

| Table 70. Supported Wake Events                                 | 126 |

|-----------------------------------------------------------------|-----|

| Table 71. User Binary Area Scan Point Definitions               | 129 |

| Table 72. Format of the User Binary Information Structure       | 129 |

| Table 73. Non-ASCII Key Mappings                                | 131 |

| Table 74. ASCII Key Mappings                                    | 132 |

| Table 75. BIOS Logging SEL List                                 | 139 |

| Table 76. Event Data 3 Definitions for Optional OEM SEL Entries | 140 |

| Table 77. Event Request Message Event Data Field Contents       | 140 |

| Table 78. Event Request Message Event Data Field Contents       | 143 |

| Table 79. Port-80h Code Definition                              | 143 |

| Table 80. Standard BIOS POST Codes                              | 144 |

| Table 81. Recovery BIOS POST Codes                              | 147 |

| Table 82. POST Error Messages and Codes                         | 148 |

| Table 83. Setup Utility Screen                                  | 153 |

| Table 84. Main Menu Selections                                  | 155 |

| Table 85. Primary Master and Slave IDE Submenu Selections       | 156 |

| Table 86. Processor Settings Submenu Selections                 | 157 |

| Table 87. Advanced Menu Selections                              | 158 |

| Table 88. Memory Configuration Menu Selections                  | 158 |

| Table 89. PCI Configuration Menu Selections                     | 159 |

| Table 90. Hot Plug PCI Control Submenu Selections               | 159 |

| Table 91. Embedded SCSI, LAN and VGA Submenu Selections         | 159 |

| Table 92. PCI Slot Submenu Selections                           | 160 |

| Table 93. I/O Device Configuration Submenu Selections           | 160 |

| Table 94. Advanced Chipset ControlSubmenu Selections            | 161 |

| Table 95. PCI Device Submenu Selections                         | 161 |

| Table 96. Security Menu Selections                              | 161 |

| Table 97. Server Menu Selections                                | 162 |

| Table 98. System Management Submenu Selections                  | 163 |

| Table 99. Console Redirection Submenu Selections                | 163 |

| Table 100. Boot Device Priority Selections                      | 164 |

| Table 101. Hard Drive Selections                                | 164 |

| Table 102. Removable Drive Selections                           | 164 |

| Table 103. Exit Menu Selections                                 | 165 |

### 1. Introduction

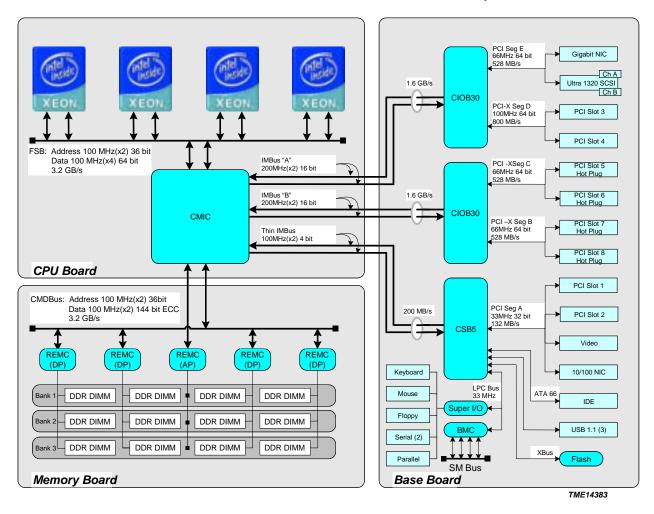

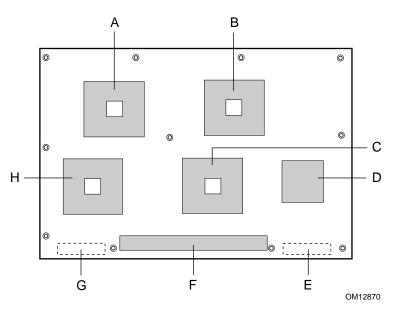

This chapter provides an architectural overview of the Intel® Server System SSH4 board set, including functional blocks and their electrical relationships. The following figure shows the functional blocks of the SSH4 baseboard, Processor Board, and Memory Board.

#### 1.1 Server System SSH4 Architecture

The server system SSH4 board set is designed around the Intel<sup>®</sup> Xeon<sup>™</sup> processor and the ServerWorks\* Grand Champion\* HE chipset. This combination provides the basis for a high performance system with leading edge processor, memory, and I/O performance.

The SSH4 baseboard architecture provides for four 603-pin surface mount technology (SMT) zero insertion force (ZIF) lever-actuated processor sockets. It supports quad processing operation using the Intel<sup>®</sup> Xeon<sup>™</sup> processor. It also contains eight industry standard PCI expansion slots supporting a mixture of 32-bit/33-MHz slots and 64-bit/100-MHz slots.

The baseboard provides an array of embedded I/O devices including a SCSI controller (with two external connection points), one embedded 10/100 Network Interface Controller, one embedded gigabit Network Interface Controller, and an ATI\* Rage XL 2D/3D graphics accelerator with 4 MB graphics memory. Server management and monitoring hardware are also included.

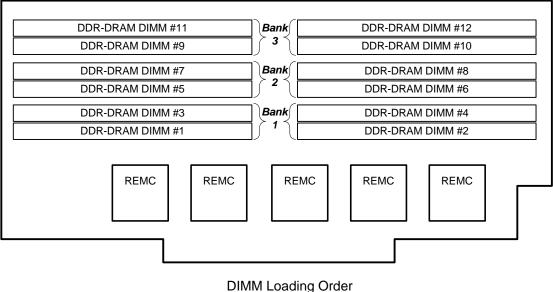

The SSH4 memory subsystem consists of a single memory expansion board in the form of a memory riser board. This board supports up to 12 DDR registered SDRAM memory modules (DIMMs). Each DIMM may provide up to 2 GB of memory capacity, providing up to 24 GB of system memory.

The boardset provides the following features:

| Processor Board | Processor        | Up to four Intel <sup>®</sup> Xeon™ processor MP (2.8GHz)                                                                                                                           |  |  |  |  |

|-----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                 | Slot Type        | PGA 603 Socket                                                                                                                                                                      |  |  |  |  |

|                 | VRM              | Four                                                                                                                                                                                |  |  |  |  |

|                 | Termination      | Automatic                                                                                                                                                                           |  |  |  |  |

| Memory Board    | Memory Type      | 2.5v buffered, ECC DDR SDRAM PC3200/PC2100-<br>compliant DIMM (DDR200/DDR266)                                                                                                       |  |  |  |  |

|                 | Slots            | 12                                                                                                                                                                                  |  |  |  |  |

|                 | Supported sizes  | 128 MB, 256 MB, 512 MB, 1 GB, 2 GB DIMM                                                                                                                                             |  |  |  |  |

|                 | Minimum          | 512 MB (128 MB DIMM x 4)                                                                                                                                                            |  |  |  |  |

|                 | Maximum          | 24 GB (2 GB DIMM x 12)                                                                                                                                                              |  |  |  |  |

|                 | Bank size        | 4                                                                                                                                                                                   |  |  |  |  |

|                 | Bus Speed        | 100 MHz Address Bus, 200 MHz Data Bus                                                                                                                                               |  |  |  |  |

|                 | Error Correction | ECC; chipkill                                                                                                                                                                       |  |  |  |  |

| Baseboard       | Chipset          | ServerWorks Grand Champion HE ServerSet<br>Memory Controller (CMIC x 1)<br>PCI Bridge (CSB5 x 1)<br>PCI-X Bus Bridge (CIOB30 x 2)<br>Reliable Enhanced Memory Controller (REMC x 5) |  |  |  |  |

|                 | PCI BUS          | Eight slots:<br>Two PCI 32-bit, 33 MHz slots<br>Four PCI-X 64-bit, 100 MHz Hot Plug slots<br>Two PCI-X 64-bit, 100 MHz non-Hot Plug slots                                           |  |  |  |  |

|                 | SCSI             | Two Ultra320 ports on a single Adaptec*7902 controller.                                                                                                                             |  |  |  |  |

#### Table 1. Hardware Overview

| IDE          | ATA66, 1 channel, two devices total                                                                  |

|--------------|------------------------------------------------------------------------------------------------------|

| LAN          | 1 x 10/100base-Tx (82550PM)                                                                          |

|              | 1 x 1000base-Tx (82544)                                                                              |

| Graphics     | ATI* Rage XL with 4 MB VRAM<br>Resolutions: 640 x 480 to 1280 x 1024                                 |

| Floppy Drive | 3.5" (720 KB / 1.2 MB / 1.44 MB) three-mode                                                          |

| Legacy IO    | National Semiconductor PC87417 I/O controller.                                                       |

|              | Floppy disk controller<br>Two serial ports<br>Parallel port<br>Keyboard and mouse<br>Real-time clock |

| Video        | ATI Rage XL with 4 MB VRAM                                                                           |

| USB          | Three Type "A" USB 1.1 (two rear pannel, one header)                                                 |

| Other        | ICMB Header                                                                                          |

| Flash ROM    | 8 megabit                                                                                            |

| Backup RAM   | 8 KB                                                                                                 |

#### Table 2. Chipset Table

| Component                  | Name                          | Model                 | Vendor                     | Features                                            |

|----------------------------|-------------------------------|-----------------------|----------------------------|-----------------------------------------------------|

| Processor                  | Intel <sup>®</sup><br>Xeon™   | -MP                   | Intel <sup>®</sup>         | Up to 2.8 GHz                                       |

| Host Bus                   | Grand                         | CMIC                  | ServerWorks*               | Memory controller                                   |

| Bridge                     | Champion<br>Chipset           | REMC                  | ServerWorks                | Memory address path and data path                   |

| PCI Bus                    | ompoer                        | CSB5                  | ServerWorks                | PCI Bridge. Includes:                               |

| Bridge                     |                               |                       |                            | DMAC, Timer, 8259A-PIC, IDE, USB XIOAPIC            |

|                            |                               | CIOB30                | ServerWorks                | PCI-X bus Bridge                                    |

| PCI Hot-Plug<br>Controller | PCI Hot<br>Plug<br>Controller | PCI-X PHP             | IBM*                       | PCI Hot Plug Controller (Xilinx* XCS20XL-<br>VQ100) |

| PCI On-board peripherals   | SCSI                          | AIC-7899W<br>AIC-7902 | Adaptec*                   | Ultra 320, two channels.                            |

|                            | Ethernet                      | 182550                | Intel <sup>®</sup>         | Ethernet Controller                                 |

|                            |                               | 182544                | Intel <sup>®</sup>         | Ethernet Controller (Gigabit)                       |

|                            | VGA                           | Rage XL               | ATI*                       | Graphics controller                                 |

| I/O                        | Super IO                      | PC87417               | National<br>Semiconducter* | KB/MS, serial port, parallel port, FDD, RTC         |

| Server<br>Management       | BMC                           | BMC                   |                            | Server Management Controller                        |

One megabyte of flash ROM is provided by an X-Bus interface to the CSB5. The Super I/O provides real-time clock (RTC) functionality.

The ServerWorks\* Champion and Grand Champion chipset consists of four components: the CMIC, REMC, CSB5 and CIOB30. The CMIC is responsible for accepting access requests from the host (processor) bus, and if appropriate, directing those accesses to memory or to one of the I/O buses. The REMC, which is connected to the CMIC, provides the memory operation. The CIOB30, which is connected to the CMIC via IMBus, provides the interface to the 64-bit, 100-MHz PCI-X bus. The CSB5, which is connected to the CMIC via the Thin IMB Bus, provides the interface to the X-bus, the LPC bus, and I/O APICs.

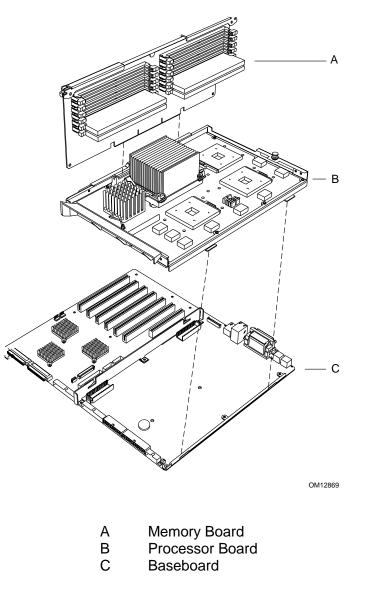

Figure 1 provides a view of how the baseboard, processor board, and memory are connected.

Figure 1. Baseboard, Processor Board, and Memory Board

### 2. **Processor and Chipset**

The Server System SSH4 processor/PCI bridge/memory subsystem consists of one to four identical Intel® Xeon<sup>™</sup> processors, the Grand Champion HE chipset, a plug-in memory board, a processor board, and support circuitry. The processor board houses four surface mount zero insertion force (ZIF) processor sockets and two embedded VRMs.

The Grand Champion HE chipset provides the 36-bit address, 64-bit data processor host bus interface, operating at 100 MHz in the AGTL+ signaling environment. The Champion Memory and I/O Controller (CMIC) provides an integrated memory controller, a high-speed I/O connection to the CIOB through the IMB bus and a legacy PCI segment through the Thin IMB bus. The board set supports up to 24 GB of ECC memory, using DDR registered SDRAM DIMMs.

Additional descriptions and features include the following:

- Champion HE chipset providing an integrated I/O bridge and memory controller and a flexible I/O subsystem core (PCI) optimized for multiprocessor systems and standard high-volume (SHV) servers.

- Four processor sockets that accept Intel<sup>®</sup> Xeon<sup>™</sup> processors.

- 330-pin connector interface to the memory expansion board.

- Processor host bus AGTL+ support circuitry, including termination power supply.

- Integrated APIC signals support.

- Miscellaneous logic for reset configuration, processor presence detection, ITP port, and server management.

#### 2.1 **Processor Support**

The Server System SSH4 supports Intel<sup>®</sup> Xeon<sup>™</sup> processor MP frequencies greater than 1.4 GHz. Processor speeds are automatically configured by the BMC, which automatically reads the processor data and sets the CPU speed setting necessary for the Intel Xeon processor(s). Therefore, processor speed setting jumpers are not necessary.

The processor is packaged in a 603-pin micro-PGA (Pin-Grid Array) and provides an Integrated Heat Spreader (IHS) for a heat sink attachment.

The Intel® Xeon<sup>™</sup> processor socket conforms to the *603-pin Socket Design Guidelines* and is a surface mount technology (SMT), ZIF socket using solder ball attachment to the platform.

The Intel® Xeon<sup>™</sup> processor MP contains a local APIC section for interrupt handling. When more than one processor is installed, all processors must be of identical revision, core voltage, cache voltage and bus/core speeds.

**Note:** If using a single processor in the system, it must be installed into the primary processor socket (processor1). The BMC will not allow DC power to be applied to the system unless the primary slot is populated with a processor. Processors must be populated in order by processor slot number.

The processor board consists of four processor sockets, a CMIC component, and a 300-pin connector for the memory board. The processor board sits parallel to the baseboard and is supported by a metallic skirt.

#### 2.1.1.1 Reset Configuration Logic

The BIOS determines the processor stepping, cache size, etc. through the CPUID instruction. The processor information is read at every system power-on. The requirements are as follows:

- All processors in the system must operate at the same frequency and have the same cache sizes. No mixing of product families or speeds are supported.

- Processors run at a fixed speed as determined by the processor and BMC and cannot be programmed to operate at a lower or higher speed.

#### 2.1.1.2 Processor Presence Detection

Logic is provided on the baseboard to detect the presence and identity of installed processors. The BMC checks the logic and will not turn on the system DC power until a processor is installed in the processor1 slot. Processors must be installed in sequential order according to the processor slot number. If processors are not installed in order, voltage rails will not be passed to the downstream processors and a system fault will be detected for the missing processor(s) or termination card.

#### 2.1.2 APIC Bus

Interrupt notification and generation for the processors is done using the front side bus (FSB) between local APICs in each processor and the I/O APIC in the CSB5 located on the baseboard.

#### 2.1.3 Server Management Registers and Sensors

The baseboard management controller manages registers and sensors associated with the processor/memory subsystem. For more information, refer to the Sahalee Baseboard Management Controller (BMC) section, beginning on page 56.

#### 2.2 ServerWorks Grand Champion Chipset

The ServerWorks Grand Champion chipset provides an integrated I/O bridge and memory controller and a flexible I/O subsystem core (PCI), targeted for multiprocessor systems and standard high-volume servers based on the Intel<sup>®</sup> Xeon<sup>™</sup> MP processor. The ServerWorks Grand Champion chipset used on the baseboard consists of the four components listed in the sections below.

#### 2.2.1 CMIC: Champion Memory and I/O Controller

The CMIC is responsible for accepting access requests from the host (processor) bus and for directing those accesses to memory or to one of the PCI buses. The CMIC monitors the host bus, examining addresses for each request. Accesses may be directed to a memory request queue for subsequent forwarding to the memory subsystem, or to an outbound request queue for subsequent forwarding to one of the PCI buses. The CMIC also accepts inbound requests from the CIOB and the legacy PCI bus. The CMIC is responsible for generating the appropriate controls to the REMC to control data transfer to and from the memory.

The Champion Memory and I/O Controller (CMIC) is the fourth generation product in ServerWorks Champion ServerSet Technology. The CMIC integrates two main functional units:

- An integrated high performance main memory subsystem

- An IMB bus interface that provides a high-performance data flow path between the processor bus and the I/O subsystem

In addition to the above-mentioned units, the CMIC incorporates a Thin-Intra Module Bus (Thin-IMB) Interface. Other features provided by the CMIC include the following:

- Full support of processor bus protocol with multiprocessor support

- Full support of ECC on the memory interface

- Twelve deep in-order queue

- Full support of registered DDR ECC SDRAM DIMMs

- Support for 24 GB of 4-way interleaved SDRAM

- Memory scrubbing

- ECC correction for 1-4 bits, multiple-bit error detection

#### 2.2.2 CIOB30: Champion I/O Bridge

The CIOBs provide the interfaces for the 64-bit, 100-MHz Rev. 2.2-compliant PCI bus and the 64-bit, 100 MHz PCI-X addendum to Rev. 2.2-compliant PCI-X busses. The CIOBs are both master and target on the PCI buses.

The Champion I/O Bridge (CIOB) provides an integrated I/O bridge that provides a highperformance data flow path between the IMB and the 64-bit I/O subsystem. This subsystem supports peer 64-bit PCI segments. Having multiple PCI interfaces, the CIOB can provide large and efficient I/O configurations. The CIOB functions as the bridge between IMB and the multiple 64-bit PCI I/O segments.

The IMB interface is capable of supporting 1.6 GB/sec of data bandwidth in both the upstream and downstream direction simultaneously.

The internal PCI arbiter implements the Least Recently used algorithm to grant access to requesting masters.

#### 2.2.3 CSB5: Champion South Bridge

The CSB5 controller has several components. It provides the interface for a 32-bit, 33-MHz Rev. 2.2-compliant PCI bus. The CSB5 can be both a master and a target on that PCI bus. The CSB5 also includes a USB controller and an IDE controller. The CSB5 is responsible for many of the power management functions, with ACPI control registers built in. The CSB5 also acts as a bridge between the PCI and the Low Pin Count (LPC) bus.

The CSB5 is a PCI device that provides multiple PCI functions in a single package: PCI-to-LPC bridge, PCI IDE interface, PCI USB controller, and power management controller. Each function within the CSB5 has its own set of configuration registers; once configured, each appears to the system as a distinct hardware controller sharing the same PCI bus interface.

The CSB5 is a 352-pin BGA device. On the SSH4 baseboard, the primary role of the CSB5 is to provide the gateway to all PC-compatible I/O devices and features. The SSH4 baseboard uses the following CSB5 features:

- PCI interface

- IDE interface, with Ultra DMA 66 capability

- USB interface

- PC-compatible timer/counters and DMA controllers

- Baseboard Plug and Play support

- General purpose I/O

- Power management

- APIC and 8259 interrupt controller

- Host interface for AT compatible signaling

- Internal-only ISA bus (no ISA expansion connectors) bridge for communication with Super I/O, BIOS flash, and BMC

#### 2.2.4 REMC: Reliability Enhanced Memory Controller

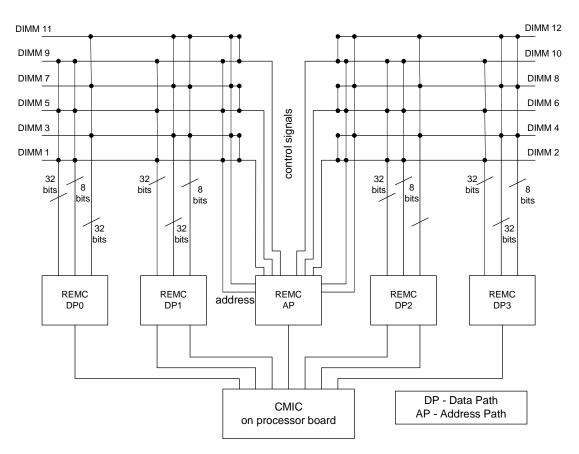

The Server System SSH4 memory board has five REMC components. These devices are used to expand the SDRAM signaling environment to support up to 12 DDR Registered SDRAM DIMMs. These DIMMs can be up to 2 GB each.

#### 2.2.5 ServerWorks Grand Champion HE Chipset Memory Architecture

The CMIC provides the memory controller for the system. The main memory interface consists of two channels, with 16-bit address channel running at 100 MHz and 144-bit CMDbus (data) running at 200 MHz.

These channels run to five REMC components (four data components and one address component) on the memory board to interface with DDR Registered ECC SDRAM DIMMs. The memory board provides 12 DIMM slots. Main memory sizes from 512 MB to 24 GB are supported with 144-bit, four-way interleaved DDR Registered SDRAM DIMMs. The ECC algorithm used during main memory accesses is capable of correcting single-bit errors and detecting all double-bit errors. The interface between the CMIC and the five REMC devices on the memory board provides 3.2 GB/sec bandwidth to/from main memory.

#### 2.2.6 ServerWorks Grand Champion HE Chipset System I/O Architecture

The CMIC, CIOB, and CSB5 chips provide the pathway between the processor and I/O systems. The CMIC is responsible for accepting access requests from the host (processor) bus, and directing all I/O accesses to one of the PCI buses or legacy I/O locations. I/O communications between the CMIC and PCI busses is conducted over one of two possible private interfaces called an IMB.

If the cycle is directed to one of the 64-bit PCI segments, the CMIC communicates with the CIOB through a private interface called the IMB bus. The IMB bus consists of two data paths, one upstream (to the CMIC from the CIOB) and one downstream (from the CMIC to the CIOB). The interface is 16 bits wide and operates at 200 MHz with double-pumped data, providing over 0.8 GB/sec of bandwidth in each direction or 1.6 GB/sec of bandwidth in both directions concurrently. The CIOB translates the IMB bus operation to a 64-bit PCI Rev. 2.2-compliant PCI-X addendum to PCI Rev. 2.2-compliant signaling environment, operating at 100 MHz.

If the cycle is directed to the 32-bit PCI segment or to the CSB5, the cycle is output on the private interface between the CMIC and the CSB5 called the Thin-IMB bus. The Thin-IMB a 16 bit wide bus (8 bits wide in each direction) and runs at 100 MHz with double pumped data. Throughput is 0.2 GB/sec of bandwidth in each direction or 0.4 GB/sec of bandwidth in both directions concurrently.

All I/O for the Server System SSH4 board set, including PCI, is directed through the CMIC and then either through the CIOB- or the CSB5-provided 32-bit, 33-MHz PCI bus.

- The CSB5 provides a 32-bit, 33-MHz PCI bus.

- The CIOB provides a 64-bit, 100-MHz PCI-X bus .

#### 2.3 Super I/O

The National Semiconductor\* PC87417 Super I/O device contains all of the necessary circuitry to control two serial ports, one parallel port, floppy disk, and PS/2-compatible keyboard and mouse. The SSH4 baseboard supports the following features:

- GPIO

- Two serial ports

- Floppy

- Keyboard and mouse through PS/2 connectors

- Parallel port

- Real-time clock

- Wake-up control

#### 2.3.1 GPIO

The National Semiconductor PC87417 Super I/O provides number of general-purpose input/output pins that the baseboard utilizes. Table 3 lists the pin, the signal name used in the schematic, and a brief description of its usage.

| Pin # | Signal Name     | Description                                                          |

|-------|-----------------|----------------------------------------------------------------------|

| 1     | IDES0-00        | IDE Chip Select                                                      |

| 9     | SXRDY+00        | Transmit ready signal from SIO to HPCs                               |

| 10    | BMC_SYSIRQ-00   | System Interrupt Controller interrupt from BMC                       |

| 13    | SIO_CLK_40M_BMC | 40 MHz clock output to BMC                                           |

| 14    | IOR-00          | Read from the HP controller                                          |

| 15    | IOW-00          | Write to the HP controller                                           |

| 16-18 | SA+00<0-3>      | 4-bit Address bus                                                    |

| 20    | HPC4CS-00       | Chip select for HP controller #1                                     |

| 21    | HPC3CS-00       | Chip select for HP controller #2                                     |

| 24-31 | SD+10<0-7>      | 8-bit data bus                                                       |

| 33    | SXSTB1-00       | Strobe signal for standard latched address mode                      |

| 34    | SXSTB0-00       | Strobe signal for standard latched address mode                      |

| 35    | BMC_SWIN        | Region 0 strapping option to determine 8-bit / 16-bit wide data path |

| 36    | BMC_PWRN        | Power LED from BMC                                                   |

| 37    | EXTEV-00        | External Event                                                       |

| 38    | SUPERSCI-00     | SuperI/O Interrupt request to CSB5                                   |

| 45    | SIO_CLK_RTC_BMC | Real Time Clock input to BMC                                         |

| 49    | PCIX_PME        | Power Management Event from PCI-X bus                                |

| 50    | HPCINT-10       | Interrupt from HPC to SuperI/O                                       |

| 51    | FP_PWR_LED      | Power LED indicator to Front Panel                                   |

| 52    | LAN_PME         | Power Management Event from onboard LAN controller                   |

| 53    | BMC_SCIN        | System Management Interrupt from BMC                                 |

| 125   | KBCLK           | Keyboard clock                                                       |

| 126   | KBDATA          | Keyboard data                                                        |

| 127   | MSCLK           | Mouse clock                                                          |

| 128   | MSDATA          | Mouse data                                                           |

#### Table 3. Super I/O GPIO Usage Table (Preliminary)

#### 2.3.2 Serial Ports

Two serial ports are provided on the baseboard, a 9-pin DB9 connector is located on the rear I/O to supply Serial Port A and a 10-pin header on the baseboard provides Serial Port B.

#### 2.3.2.1 Serial Port A

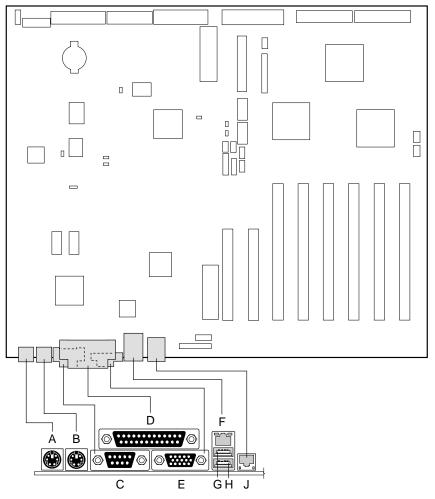

Serial Port A is accessed through a 9-pin connector on the rear I/O panel. The Serial Port A interface follows the standard RS-232 pinout. The baseboard has a Serial Port A silkscreen label next to the connector and a location designator of P31. The Serial Port A connector is located below the parallel port connector, as shown in Figure 20.

#### 2.3.2.2 Serial Port B

Serial Port B is provided via a header on the baseboard. See section 10.7 on page 74 for information about Serial Port B.

#### 2.3.3 Floppy

The floppy disk controller in the SIO is functionally compatible with floppy disk controllers in the DP8473 and N844077. All the FDC functions are integrated into the SIO including analog data separator and 16-byte FIFO.

#### 2.3.4 Keyboard and Mouse

Two PS/2 ports are provided for keyboard and mouse and are mounted within a single stacked housing. The mouse connector is stacked over the keyboard connector.

#### 2.3.5 Parallel Port

The parallel port is supported on the baseboard through the rear I/O. The parallel port supports Bi-directional, EPP and ECP modes.

#### 2.3.6 Real-time Clock

The SIO contains a real-time clock with external battery backup. The device also contains 242 bytes of general purpose battery-backed CMOS RAM.

#### 2.3.7 Wake-up Control

The SIO contains functionality that allows various events to control the power-on and power-off of the system.

#### 2.4 BIOS Flash

The baseboard incorporates a Fujitsu\* 8176 8 megabit Flash ROM. The flash device is connected through the X-bus of the CSB5.

### 3. Baseboard PCI I/O Subsystem

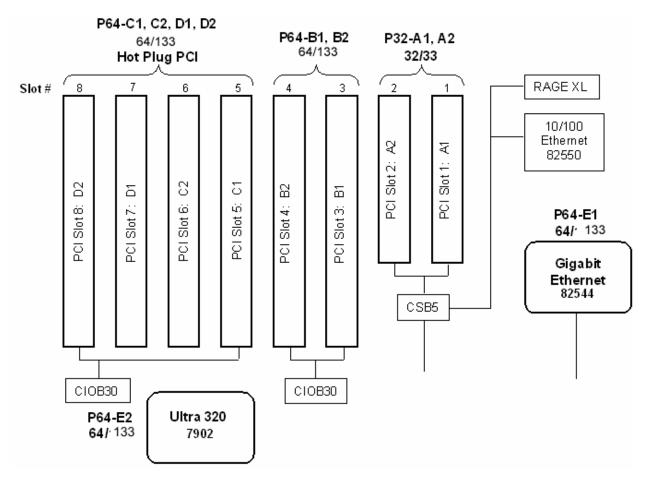

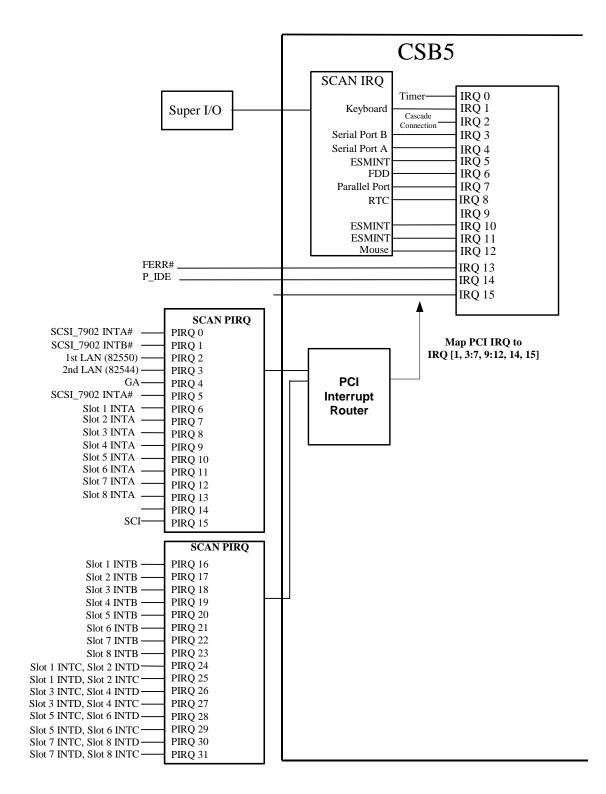

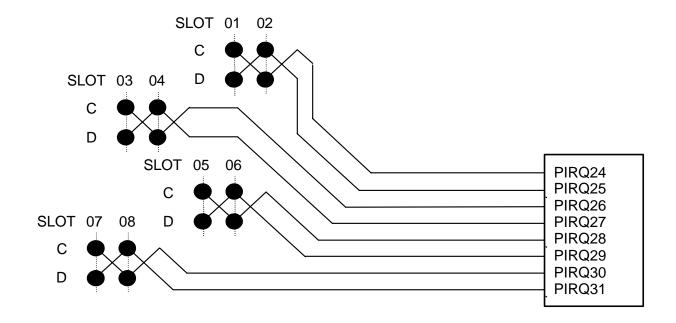

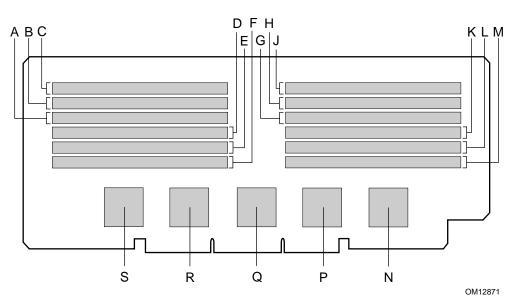

The primary I/O bus for the Server System SSH4 MP baseboard is PCI, with one PCI bus segment and four PCI-X bus segments. Each PCI and PCI-X bus complies with the PCI Local Bus Specification, Rev 2.2 and the PCI-X addendum to the PCI local bus specification. The P32-A bus segment is directed through the CSB5 while the four 64-bit segments, P64-B, P64-C, P64-D, and P64-E are directed through the two CIOB30 I/O Bridges. Figure 2 illustrates the PCI bus layout. Table 4 lists the characteristics of the PCI and PCI-X bus segments.

Figure 2. PCI Bus Layout

| PCI Bus<br>Segment | Voltage | Width   | Speed           | Туре                      | PCI Slots                                                                                                   |

|--------------------|---------|---------|-----------------|---------------------------|-------------------------------------------------------------------------------------------------------------|

| PCI<br>P32-A       | 5V      | 32 bits | 33 MHz          | Non-Hot Plug,<br>Peer bus | Slots 1 and 2. Full-length system cable routing may interfere with insertion of some full-length PCI cards. |

| PCI-X<br>P64-B     | 3.3V    | 64 bits | 133/ 100<br>MHz | Non-Hot Plug,<br>Peer bus | Slots 3 and 4. Full length                                                                                  |

| PCI-X<br>P64-C     | 3.3V    | 64 bits | 133/100<br>MHz  | Hot Plug, Peer<br>bus     | Slots 5 and 6. Full length                                                                                  |

| PCI-X<br>P64-D     | 3.3V    | 64 bits | 1 33/100<br>MHz | Hot Plug, Peer<br>bus     | Slots 7 and 8. Full length                                                                                  |

| PCI-X<br>P64-E     | 3.3 V   | 64 bits | 133/100<br>MHz  | Embedded<br>Peer bus      | N/A                                                                                                         |

| Table 4. PCI and PCI-X Bus Segment Characteristics |

|----------------------------------------------------|

|----------------------------------------------------|

#### 3.1 32-bit, 33-MHz PCI Subsystem

All 32-bit (P32-A), 33-MHz PCI I/O for the baseboard is directed through the CSB5. The 32-bit, 33-MHz PCI segment created by CSB5 is called the P32-A segment. The P32-A segment contains the following embedded devices and connectors:

- 2D/3D graphics accelerator: ATI RAGE XL Video Controller

- One Network Interface Controller: Intel<sup>®</sup> 82550 Fast Ethernet Controller

- PCI Slots 1 and 2

Each of the embedded devices above will be allocated a GPIO to disable the device.

#### 3.1.1 P32-A Slot Specifics

The PCI slots support the PME# and 3.3VAUX signals as described in the *PCI Bus Power Management Interface Specification*. The 3.3VAUX signal is a limited current 3.3 V supply maintained even when the system power is turned off.

**Note:** The baseboard supports only one slot consuming 375 mA of Standby current on the 3.3V AUX power line, although it can be any of the eight PCI slots. All other slots can consume a maximum of 20 mA each. The system will not operate correctly if this limit is exceeded.

#### 3.2 64-bit, 133-MHz PCI-X Subsystem

P64 supports the following six 184-pin, 3.3 V, 64-bit PCI-X expansion connectors: Each embedded device is allocated a GPIO to disable the device.

- Slot 3 numbered P64-B1

- Slot 4 numbered P64-B2

- Slot 5 numbered P64-C1

- Slot 6 numbered P64-C2

- Slot 7 numbered P64-D1

- Slot 8 numbered P64-D2

- The P64-E segment supports the following embedded devices: One Ultra 320/m (Channel 0 and 1): AIC-7902W SCSI controller

- One Gigabit Network Interface Controller: Intel<sup>®</sup> 82544 Fast Ethernet Controller

#### 3.2.1 PCI-X Bus Arbitration

P64-Bus segments 2 and 3 support five PCI-X masters (U-320 SCSI, Gigabit NIC, Slots P64-B1, P64-B2, and CIOB-1). P64-Bus segments 4 and 5 support five PCI-X masters (Slots P64-C1, P64-C2, P64-D1, P64-D2, and CIOB-2). All PCI-X masters must arbitrate for PCI-X access, using resources supplied by the CIOB. The host bridge PCI-X interface (CIOB) arbitration lines *REQx#* and *GNTx#* are a special case in that they are internal to the host bridge. The following table defines the arbitration connections.

| Baseboard Signals | Device                                              |

|-------------------|-----------------------------------------------------|

| P_REQ0#/P_GNT0#   | PCI-X Slot P64-B1                                   |

| P_REQ1#/P_GNT1#   | PCI-X Slot P64-B2                                   |

| P_REQ2#/P_GNT2#   | PCI-X Slot P64-C1                                   |

| P_REQ3#/P_GNT3#   | PCI-X Slot P64-C2                                   |

| S_REQ0#/S_GNT0#   | PCI-X Slot P64-D1                                   |

| S_REQ1#/S_GNT1#   | PCI-X Slot P64-D2                                   |

| S_REQ2#/S_GNT2#   | PCI-X P64-E<br>AIC-7902W SCSI controller            |

|                   |                                                     |

| S_REQ3#/S_GNT3#   | PCI-X P64-E<br>Gigabit Network Interface Controller |

Table 5. PCI-X Arbitration Connections

#### 3.2.2 P64 Slot Specifics

The PCI slots support the PME# and 3.3VAUX signals as described in the PCI Bus Power Management Interface Specification. The 3.3VAUX signal is a limited current 3.3 V supply maintained even when the system power is turned off.

**Note:** The baseboard only supports one slot consuming 375 mA of Standby current on the 3.3V AUX power line, although it can be any of the eight PCI slots. All other slots can consume a maximum of 20 mA each. The system will not operate correctly if this limit is exceeded.

#### 3.3 PCI Hot Plug Support

Hot plug support is provided on four of the PCI-X slots on the 133/64-bit PCI bus segments (C and D). No hot plug support is provided on the 133/64-bit bus segments (B and E). Segment A operates at only 33 MHz and is not hot plug supported. The logic for powering-on and powering-off the slots is controlled by the PHP ASIC.

#### 3.3.1 PCI Hot Plug Functionality

To support PCI Hot-plug, systems require hot-plug hardware, a hot-plug compatible operating system, and hot-plug capable adapter drivers. To ensure backward compatibility, any combination of hot-plug and conventional versions of each of these components is permitted, including mixing both hot-plug and conventional adapter drivers. If a conventional driver is loaded under a hot-plug capable operating system, or a hot plug driver is loaded under a conventional operating system, the driver will maintain the capability it had in the conventional environment.

#### 3.3.2 Operating System Support

The initial steps involved in booting to an operating system are not impacted because of PHP support. After the operating system has booted, adapter drivers may be required to be installed or updated to get PHP functionality. Three terms that are commonly used to describe PCI Hot-plug operations are Hot Replace, Hot Add, and Hot Upgrade.

- Hot Replace: The process of removing an adapter card and then inserting an identical adapter into the same slot. The replacement adapter card will use the same PCI resources that were assigned to the previous card and its driver will not be updated. Hot Replace is also commonly referred to as "Like-for-Like Replacement."

- Hot Add: The process of inserting an adapter card into a previously unoccupied slot. This operation requires that a driver also be loaded for the added adapter and that PCI resources have been reserved by the system BIOS for the added adapter card. Hot Add is also sometimes referred to as "Hot Expansion."

- **Hot Upgrade:** The process of removing an adapter card and inserting an upgraded adapter (i.e., a new revision) that requires different PCI resources than the original card. The adapter's driver may or may not use the same driver as the previous adapter.

"Hot Removal" and "Hot Insertion" refer to the sequence of steps involved in removing and inserting, respectively, a PCI card from a hot-pluggable PCI slot. Not all of these operations are supported by every hot-plug capable operating system. Each operating system may implement these operations in a different manner.

The following steps outline a typical enabling sequence for Windows NT\* 4.0:

- 1. After booting, load the necessary drivers.

- 2. Enable the PHP graphical user interface (GUI) by clicking Start / Programs / PCI Hot Plug / PCI HP Utility on the Windows NT menu bar.

This GUI provides the adapter status to the hot-plug user interface, and also allows the user to control hot-plug functionality. The initial screen lists *LED Condition* (Green, Amber), *Location* (logical slot number), *Board* (description, driver support), and *Status* (Normal/Not Ready). Logical slot numbering starts at 5 and ends at 8, in increments of 1. Only slots containing a card with hot-plug capable drivers can be controlled from the GUI. LED Control

Each slot has two LEDs. A green LED indicates the state of power on each slot. The amber LED is the slot attention indicator. The amber LED indicates an error condition with that slot. The following table summarizes typical LED states that may be encountered during operation.

| LED States     | Interpretation                                                |

|----------------|---------------------------------------------------------------|

| Green On       | The slot is on and functioning normally                       |

| Amber Off      |                                                               |

| Green On       | The slot is on and an attention condition exists (error)      |

| Amber On       |                                                               |

| Green Off      | The slot is off and an attention condition exists (error)     |

| Amber On       |                                                               |

| Green Off      | The slot is off                                               |

| Amber Off      |                                                               |

| Green On       | The slot is on and an attention condition exists (Remove OK)  |

| Amber blinking |                                                               |

| Green Off      | The slot is off and an attention condition exists (Remove OK) |

| Amber blinking |                                                               |

Table 6. Slot State and Attention Indicators

#### 3.3.3 Interlock Switch Support

The baseboard does not support a mechanical interlock switch. The switch input is permanently grounded (enabled) on the baseboard.

#### 3.3.4 Hot Plug Write Operations

Table 7 summarizes Hot Plug Write Operations. Table 8 defines the states of the slot status registers.

| Command<br>Encoding | Write to registers at offset: | Affects    | Command                                   | State Machine |

|---------------------|-------------------------------|------------|-------------------------------------------|---------------|

| 00h                 | 15                            | Controller | Enable IRQ                                | No            |

| 01h                 | 15                            | Controller | Disable IRQ                               | No            |

| 02h                 | 0-14                          | Slot       | Turn Slot OFF                             | Yes           |

| 03h                 | 0-14                          | Slot       | Turn Slot ON                              | Yes           |

| 04h                 | 0-14                          | Slot       | Turn ATTENTION indicator OFF              | No            |

| 05h                 | 0-14                          | Slot       | Turn ATTENTION indicator ON               | No            |

| 06h                 | 15                            | Controller | Clear IRQ                                 | No            |

| 07h                 | 15                            | Controller | Reset Controller                          | Yes           |

| 08h                 | 15                            | Controller | IRQ Steering (SCI/SMI toggle)             | No            |

| 09h                 | 31-34                         | Bus        | Set 33 MHz Conventional Bus Mode          | Yes           |

| 0Ah                 | 31-34                         | Bus        | Set 66 MHz Conventional Bus Mode          | Yes           |

| 0Bh                 | 31-34                         | Bus        | Set 66 MHz PCI-X Bus Mode                 | Yes           |

| 0Ch                 | 31-34                         | Bus        | Set 100 MHz PCI-X Bus Mode                | Yes           |

| 0Dh                 | 31-34                         | Bus        | Set 133 MHz PCI-X Bus Mode                | Yes           |

| 0Eh                 |                               |            | Reserved                                  | Yes           |

| 0Fh                 |                               |            | Reserved                                  | Yes           |

| 10h                 |                               |            | Reserved                                  | Yes           |

| 11h                 | 15                            | All Slots  | All Slots Off                             | Yes           |

| 12h                 | 15                            | All Slots  | All Slots On                              | Yes           |

| 13h                 | 15                            | Slot       | Activate 'Locator' (Blinking ATTN LED) No |               |

| 14h to FFh          |                               |            | Reserved                                  | Reserved      |

#### Table 7. Hot Plug Controller Write Operations

Notes:

- Certain commands require time to complete. Device driver software must issue state machine commands using the pseudocode shown later in this document.

- Commands that do not require the state machine can be issued by waiting for a non-busy controller and then writing the command to the proper register.

- The current state of SCI/SMI is available using bit 6 of the controller status register. Disabling interrupts affects both SCI and SMI. SCI/SMI should be initialized to SCI.

- Interrupt steering is optional. If it is not implemented, the value of bit 6 in the controller status register will be 0 and will not change when command 08h is issued.

- Command 13h (Locator ON) causes the Attention indicator to blink at a rate of 2 Hz with 50% duty cycle until another command that affects the Attention indicator is written to the controller. (The Attention indicator is in one of three states (off, on, or blinking) and these three states are selected using commands 04 (Attention Off), 05h (Attention On), and 13h (Locator On).

| Bit Position (0<br>is LSB) | Name              | Description                                                             |

|----------------------------|-------------------|-------------------------------------------------------------------------|

| 0                          | Power             | 0 = Power off<br>1 = Power on to slot                                   |

| 1                          | Connect#          | 0 = Connected to PCI bus<br>1 = Disconnected                            |

| 2                          | Attention         | 0 = Off<br>1 = On                                                       |

| 3                          | PRSNT2#           | PCI card Present signal 2; pulled up by system                          |

| 4                          | PRSNT1#           | PCI card Present signal 1; pulled up by system                          |

| 5                          | PWRGD             | From slot power module<br>0 = No power or power fault<br>1 = Power good |

| 6                          | BusSpeed Mismatch | 0 = Bus speed OK<br>1 = Bus speed mismatch (this slot)                  |

| 7                          | Latch             | 0 = Tab latch is open<br>1 = Tab latch is closed                        |

#### Table 8. Slot Status Register Definitions (Read to Offsets 0-14)

#### Notes:

- Allow one second to pass between the applying power and checking bit 5. If bit 5 indicates no power one second after power is applied to the slot, a power fault has occurred.

- If a hot-plug card insertion results in a bus speed mismatch (bit 6), the controller will decline all "Turn Slot On" commands (command 03h) addressed to the slot by returning "Command Failed" results in bits 2 and 3 of the command status register and asserting IRQ (if enabled). Commands to "Turn Slot Off" (command 02h), "Turn Attention Indicator On" (command 04h), and "Turn Attention Indicator Off" (command 05h) for the slot will be honored and, barring hardware faults, will complete successfully.

- Because M66EN may be used as an input on some adapters (and may, therefore, have clamping diodes on this signal line), M66EN should only be sampled when the adapter is powered up. The adapter may be powered up with PCIRST# asserted and the bus and clocks disconnected for the purpose of checking M66EN without affecting the bus, even if the card cannot operate at the current bus speed. The state of Bus Speed Mismatch (bit 6) must reflect the value of M66EN obtained while the adapter was powered and must be updated after each PCI bus reset operation involving this slot. (Bus speed mismatch [bit 6] must also take into account the state of the PCIXCAP bit (as reported in the Extended Slot Status register) versus the speed of the bus.

#### 3.3.5 PCI Power Budgeting

The Server System SSH4 boardset is capable of supplying power to the eight PCI slots as identified in Table 9.

| Subsystem        | Quantity<br>of slots | +5 V<br>Current | +3.3 V<br>Current | +12 V<br>Current | -12 V<br>Current | +5 V<br>Standby<br>Current | Total Power<br>(W) |

|------------------|----------------------|-----------------|-------------------|------------------|------------------|----------------------------|--------------------|

| 64 bit PCI/PCI-X | 6                    | 9.00 A          | 13.64 A           |                  |                  | 0.31 A                     | 91.56 W            |

| 32 bit PCI       | 2                    | 6.00 A          |                   |                  |                  | 0.03 A                     | 30.15 W            |

#### Table 9. PCI Power Consumption

#### 3.4 Device IDs (IDSEL)