# Intel<sup>®</sup> Server Board X38ML

**Technical Product Specification**

Intel order number E15331-006

**Revision 1.3**

June 2010

**Enterprise Platforms and Services Division – Marketing**

## **Revision History**

| Date           | Revision Number | Modifications                                                     |

|----------------|-----------------|-------------------------------------------------------------------|

| September 2007 | 1.0             | Initial release.                                                  |

| May 2008       | 1.1             | iBMC fix to Integrated the BMC and fix the FAN sensors.           |

| April 2009     | 1.2             | Corrected the heading typo at the top of some even numbered page. |

| June 2010      | 1.3             | Updated China CCC/CNCA related information.                       |

## Disclaimers

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® Server Board X38ML may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel Corporation server baseboards support peripheral components and contain a number of high-density VLSI and power delivery components that need adequate airflow to cool. Intel's own chassis are designed and tested to meet the intended thermal requirements of these components when the fully integrated system is used together. It is the responsibility of the system integrator that chooses not to use Intel developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of air flow required for their specific application and environmental conditions. Intel Corporation can not be held responsible if components fail or the server board does not operate correctly when used outside any of their published operating or non-operating limits.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2010. All rights reserved.

## Table of Contents

| 1. | Introdu | ction                                                   | 1    |

|----|---------|---------------------------------------------------------|------|

| 1  | 1.1     | Server Board Use Disclaimer                             | 1    |

| 2. | Server  | Board Overview                                          | 2    |

| 2  | 2.1     | Server Board Feature Set                                | 2    |

| 2  | 2.2     | Server Board Layout                                     | 4    |

| 3. | Functio | nal Architecture                                        | 7    |

| 3  | 3.1     | Processor Subsystem                                     | 8    |

| 3  | 3.2     | Intel <sup>®</sup> X38 Chipset                          | 8    |

|    | 3.2.1   | Memory Controller Hub (MCH): Intel <sup>®</sup> X38 MCH | 9    |

|    | 3.2.2   | I/O Controller Hub: Intel <sup>®</sup> ICH9-R           | 9    |

| 3  | 3.3     | Integrated Baseboard Management Controller              | . 12 |

|    | 3.3.1   | Functionality Overview                                  | . 12 |

|    | 3.3.2   | Block Diagram                                           | 14   |

| 3  | 3.4     | Memory Subsystem                                        | 15   |

|    | 3.4.1   | Memory Support                                          | 15   |

|    | 3.4.2   | Memory Population Rules                                 | . 15 |

| 3  | 3.5     | I/O Subsystem                                           | 16   |

|    | 3.5.1   | PCI Express* x16 Riser Slot                             | . 16 |

|    | 3.5.2   | SATA Support                                            | 16   |

|    | 3.5.3   | Video Support                                           | 17   |

|    | 3.5.4   | Network Interface Controller (NIC)                      | 17   |

|    | 3.5.5   | USB Support                                             | 17   |

|    | 3.5.6   | Super I/O Chip                                          | 18   |

| 3  | 3.6     | Replacing the Back-Up Battery                           | . 19 |

| 4. | System  | BIOS                                                    | 21   |

| 4  | ŀ.1     | BIOS Identification String                              | 21   |

| 4  | 1.2     | Logo/Diagnostic Screen                                  | 21   |

| 4  | 1.3     | BIOS Setup Utility                                      | 22   |

|    | 4.3.1   | Operation                                               | 22   |

|    | 4.3.2   | BIOS Setup Screens                                      | 25   |

| 4  | 1.4     | Loading BIOS Defaults                                   | 50   |

| 2  | 1.5     | Multiple Boot Blocks                                    | 50   |

| 4.6     | Recovery Mode                                     | 51 |

|---------|---------------------------------------------------|----|

| 4.7     | OEM Logo                                          | 51 |

| 5. Plat | form Management                                   | 53 |

| 5.1     | Platform Management Features                      | 53 |

| 5.1.1   | 1 IPMI 2.0 Features                               | 53 |

| 5.1.2   | 2 Non-IPMI Features                               | 54 |

| 5.2     | Power System                                      | 54 |

| 5.2.1   | 1 Power Supply Interface Signals                  | 55 |

| 5.2.2   | 2 Power-Good Dropout                              | 55 |

| 5.2.3   | 3 Power-up Sequence                               | 56 |

| 5.2.4   | 4 Power Down Sequence                             | 56 |

| 5.2.5   | 5 Power Control Sources                           | 56 |

| 5.2.6   | 6 Power State Retention                           | 57 |

| 5.2.7   | 7 Power State Restoration                         | 57 |

| 5.2.8   | 8 Wake-On-LAN (WOL)                               |    |

| 5.3     | Advanced Configuration and Power Interface (ACPI) |    |

| 5.3.1   | 1 ACPI Power Control                              | 58 |

| 5.3.2   | 2 ACPI State Synchronization                      | 59 |

| 5.4     | System Reset Control                              | 59 |

| 5.4.1   | 1 Reset Signal Output                             | 59 |

| 5.4.2   | 2 Reset Control Sources                           | 59 |

| 5.4.3   | 3 Front Panel System Reset                        | 59 |

| 5.4.4   | 4 Soft Reset and Hard Reset                       | 59 |

| 5.4.5   | 5 BMC Command Used to Reset System                | 60 |

| 5.4.6   | 6 Watchdog Timer Expiration                       | 60 |

| 5.5     | BMC Reset Control                                 | 60 |

| 5.5.1   | 1 BMC Exits Firmware Update                       | 60 |

| 5.5.2   | 2 Standby Power Comes Up                          | 60 |

| 5.6     | System Initialization                             | 60 |

| 5.6.1   | 1 Processor TControl Setting                      | 60 |

| 5.6.2   | 2 Fault Resilient Booting (FRB)                   | 60 |

| 5.6.3   | 3 BSP Identification                              | 61 |

| 5.6.4   | 4 Boot Control Support                            | 61 |

| 5.6.5   | 5 Post Code Display                               | 61 |

| 5.7     | Integrated Front Panel User Interface             | 62 |

| 5.7.1  | Power LED                                     | . 62 |

|--------|-----------------------------------------------|------|

| 5.7.2  | System Status LED                             | . 62 |

| 5.7.3  | Front Panel/Chassis Inputs                    | . 63 |

| 5.7.4  | Front Panel Lock-out Operation                | . 63 |

| 5.8    | Private Management I <sup>2</sup> C Buses     | . 64 |

| 5.9    | Watchdog Timer                                | . 64 |

| 5.10   | BMC Internal Timestamp Clock                  | . 64 |

| 5.10.1 | BMC Clock Initialization                      | . 64 |

| 5.10.2 | System Clock Synchronization                  | . 64 |

| 5.11   | System Event Log (SEL)                        | . 65 |

| 5.11.1 | Servicing Events                              | . 65 |

| 5.11.2 | SEL Entry Deletion                            | .65  |

| 5.11.3 | SEL Erasure                                   | . 65 |

| 5.12   | Sensor Data Record (SDR) Repository           | .65  |

| 5.12.1 | SDR Repository Erasure                        | .65  |

| 5.12.2 | Initialization Agent                          | . 66 |

| 5.13   | Field Replaceable Unit (FRU) Inventory Device | . 66 |

| 5.13.1 | BMC FRU Inventory Area Format                 | . 66 |

| 5.14   | Sensor Rearm Behavior                         | . 67 |

| 5.15   | Processor Sensors                             | . 68 |

| 5.15.1 | Processor Status Sensors                      | . 68 |

| 5.15.2 | Digital Thermal Sensor                        | . 69 |

| 5.16   | Standard Fan Management                       | . 69 |

| 5.16.1 | Fan Domains                                   | .70  |

| 5.16.2 | Nominal Fan Speed                             | .70  |

| 5.16.3 | Thermal and Acoustic Management               | .71  |

| 5.17   | Power Unit Management                         | .71  |

| 5.17.1 | Power Off                                     | .71  |

| 5.17.2 | AC Lost                                       | .71  |

| 5.17.3 | Soft Power Control Fault                      | .71  |

| 5.18   | BMC Self Test                                 | .72  |

| 5.19   | Messaging Interfaces                          | .72  |

| 5.19.1 | Channel Management                            | .72  |

| 5.19.2 | User Model                                    | .73  |

| 5.19.3 | Sessions                                      | .73  |

|    | 5.19.4   | Media Bridging                                   | .73  |

|----|----------|--------------------------------------------------|------|

|    | 5.19.5   | Request/Response Protocol                        | .73  |

|    | 5.19.6   | Host to BMC Communication Interface              | .73  |

|    | 5.19.7   | IPMB Communication Interface                     | .75  |

|    | 5.19.8   | LAN Interface                                    | .75  |

| 5  | .20      | Event Filtering and Alerting                     | .76  |

|    | 5.20.1   | Platform Event Filtering (PEF)                   | .76  |

|    | 5.20.2   | Alert-over-LAN                                   | . 76 |

|    | 5.20.3   | Factory Default Event Filters                    | .77  |

|    | 5.20.4   | Alert Policies                                   | .77  |

|    | 5.20.5   | MIB File                                         | .77  |

| 5  | .21      | Sensor Support                                   | .77  |

| 5  | .22      | BIOS-BMC interactions                            | . 83 |

| 5  | .23      | Platform Management Features Implemented by BIOS | . 83 |

|    | 5.23.1   | IPMI                                             | . 84 |

|    | 5.23.2   | Console Redirection                              | . 84 |

|    | 5.23.3   | IPMI Serial Interface                            | . 85 |

|    | 5.23.4   | Wired For Management (WFM)                       | . 88 |

|    | 5.23.5   | System Management BIOS (SMBIOS)                  | . 88 |

|    | 5.23.6   | Security                                         | . 88 |

| 6. | Error Re | eporting and Handling                            | . 90 |

| 6  | .1       | Fault Resilient Booting                          | . 90 |

|    | 6.1.1    | BSP POST Failures (FRB-2)                        | . 90 |

|    | 6.1.2    | Operating System Load Failures (OS Boot Timer)   | . 90 |

| 6  | .2       | Error Handling and Logging                       | . 91 |

|    | 6.2.1    | Error Sources and Types                          | . 91 |

|    | 6.2.2    | Error Logging via SMI Handler                    | . 91 |

|    | 6.2.3    | Logging Format Conventions                       | . 92 |

|    | 6.2.4    | Timestamp Clock Event                            | . 96 |

| 6  | .3       | Error Messages and Error Codes                   | . 97 |

|    | 6.3.1    | Diagnostic LEDs                                  | . 97 |

|    | 6.3.2    | POST Code Checkpoints                            | . 98 |

|    | 6.3.3    | POST Error Messages and Handling1                | 101  |

|    | 6.3.4    | POST Error Pause Option1                         | 103  |

| 7. | Connec   | tors and Jumper Blocks1                          | 104  |

| Reference      | Documents                                                  | 120 |

|----------------|------------------------------------------------------------|-----|

| Glossary       |                                                            | 117 |

| 8.3.6          | Korean Compliance (RRL)                                    | 116 |

| 8.3.5          | Taiwan Declaration of Conformity (BSMI)                    | 116 |

| 8.3.4          | VCCI (Japan)                                               |     |

| 8.3.3          | Europe (CE Declaration of Conformity)                      |     |

| 8.3.2          | ICES-003 (Canada)                                          |     |

| 8.3.1          | FCC (USA)                                                  |     |

| 8.3            | Electromagnetic Compatibility Notices                      |     |

| 8.2.5          | 113                                                        |     |

| 0.2.7          | Product Regulatory Compliance Markings                     |     |

| 8.2.4          | Product Ecology Requirements                               |     |

| 8.2.2          | Certifications/Registrations/Declarations                  |     |

| 8.2.1<br>8.2.2 | Product Safety Compliance – Class A Compliance             |     |

| 8.2<br>8.2.1   | Product Regulatory Compliance<br>Product Safety Compliance |     |

| 8.1<br>8.2     | Server Board Design Specification                          |     |

| -              | and Environmental Specifications                           |     |

| 7.8            | Jumper Blocks                                              |     |

| 7.7            | Chassis Intrusion Header                                   |     |

| 7.6<br>7.7     | Fan Headers                                                |     |

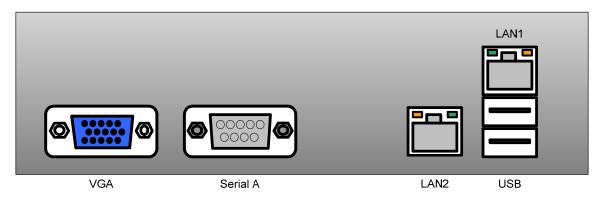

| 7.5.6          | Back Panel I/O Connectors                                  | -   |

| 7.5.5          | USB Connector                                              |     |

| 7.5.4          | Serial Port Connectors                                     |     |

| 7.5.3          | SATA Connectors                                            |     |

| 7.5.2          | NIC Connectors                                             |     |

| 7.5.1          | VGA Connector                                              |     |

| 7.5            | I/O Connectors                                             |     |

| 7.4            | Front Panel Connector                                      |     |

| 7.3            | SMBus Connector                                            |     |

| 7.2            | PCI Express* x16 Connector                                 |     |

| 7.1.1          | Main Power Connector                                       |     |

| 7.1            | Power Connectors                                           |     |

## List of Figures

| Figure 1. Intel <sup>®</sup> Server Board X38ML Layout                              | 5   |

|-------------------------------------------------------------------------------------|-----|

| Figure 2. Intel <sup>®</sup> Server Board X38ML Mechanical Drawing                  | 6   |

| Figure 3. Server Board Block Diagram                                                | 7   |

| Figure 4. Integrated BMC Block Diagram                                              | 15  |

| Figure 5. Setup Utility — Main Screen Display                                       | 26  |

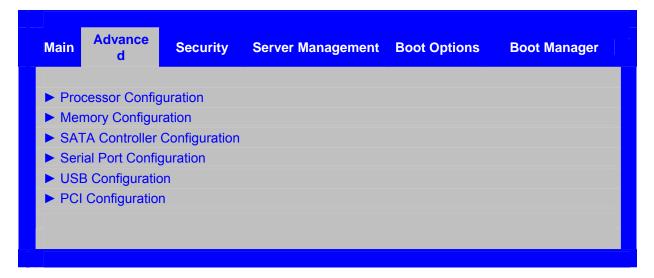

| Figure 6. Setup Utility — Advanced Screen Display                                   | 28  |

| Figure 7. Setup Utility — Processor Configuration Screen Display                    | 29  |

| Figure 8. Setup Utility — Memory Configuration Screen Display                       | 31  |

| Figure 9. Setup Utility — ATA Controller Configuration Screen Display               | 32  |

| Figure 10. Setup Utility — Serial Port Configuration Screen Display                 | 34  |

| Figure 11. Setup Utility — USB Controller Configuration Screen Display              | 35  |

| Figure 12. Setup Utility — PCI Configuration Screen Display                         | 37  |

| Figure 13. Setup Utility — Security Screen Display                                  | 38  |

| Figure 14. Setup Utility — Server Management Screen Display                         | 39  |

| Figure 15. Setup Utility — Console Redirection Screen Display                       | 41  |

| Figure 16. Setup Utility —System Information Screen Display                         | 42  |

| Figure 17. Setup Utility — Boot Options Screen Display                              | 43  |

| Figure 18. Setup Utility — Hard Disk Order Screen Display                           | 44  |

| Figure 19. Setup Utility — CDROM Order Screen Display                               | 45  |

| Figure 20. Setup Utility — Floppy Order Screen Display                              | 45  |

| Figure 21. Setup Utility — Network Device Order Screen Display                      | 46  |

| Figure 22. Setup Utility — BEV Device Order Screen Display                          | 46  |

| Figure 23. Setup Utility — Boot Manager Screen Display                              | 47  |

| Figure 24. Setup Utility — Error Manager Screen Display                             | 48  |

| Figure 25. Setup Utility — Exit Screen Display                                      | 49  |

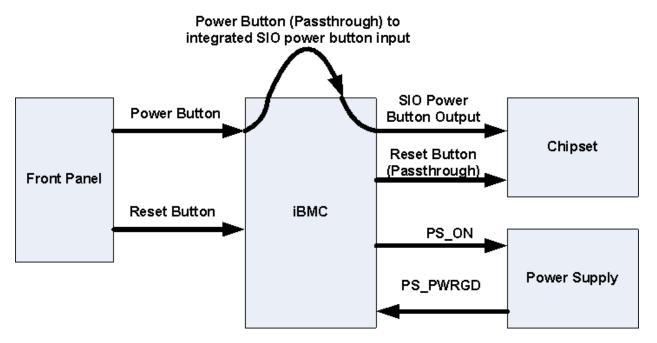

| Figure 26. BMC Power/Reset Signals                                                  | 55  |

| Figure 27. Location of Diagnostic LEDs on the Intel <sup>®</sup> Server Board X38ML | 98  |

| Figure 28. Intel <sup>®</sup> Server Board X38ML Back Panel I/O connectors          | 110 |

## List of Tables

| Table 1. Processor Support Matrix                                    | 8  |

|----------------------------------------------------------------------|----|

| Table 2. Serial A Header Pin-out                                     | 18 |

| Table 3. Serial B Header Pin-out                                     | 19 |

| Table 4. BIOS Setup Page Layout                                      | 22 |

| Table 5. BIOS Setup: Keyboard Command Bar                            | 23 |

| Table 6. Setup Utility — Main Screen Fields                          | 26 |

| Table 7. Setup Utility — Advanced Screen Display Fields              | 28 |

| Table 8. Setup Utility — Processor Configuration Screen Fields       | 29 |

| Table 9. Setup Utility — Memory Configuration Screen Fields          | 31 |

| Table 10. Setup Utility — ATA Controller Configuration Screen Fields | 33 |

| Table 11. Setup Utility — Serial Ports Configuration Screen Fields   | 34 |

| Table 12. Setup Utility — USB Controller Configuration Screen Fields | 36 |

| Table 13. Setup Utility — PCI Configuration Screen Fields            | 37 |

| Table 14. Setup Utility — Security Screen Fields                     | 38 |

| Table 15. Setup Utility — Server Management Screen Fields            | 39 |

| Table 16. Setup Utility — Console Redirection Configuration Fields   | 41 |

| Table 17. Setup Utility —System Information Fields                   | 42 |

| Table 18. Setup Utility — Boot Options Screen Fields                 | 43 |

| Table 19. Setup Utility — Hard Disk Order Fields                     | 44 |

| Table 20. Setup Utility — CDROM Order Fields                         | 45 |

| Table 21. Setup Utility — Floppy Order Fields                        | 45 |

| Table 22. Setup Utility — Network Device Order Fields                | 46 |

| Table 23. Setup Utility — BEV Device Order Fields                    | 47 |

| Table 24. Setup Utility — Boot Manager Screen Fields                 | 48 |

| Table 25. Setup Utility — Error Manager Screen Fields                | 48 |

| Table 26. Setup Utility — Exit Screen Fields                         | 49 |

| Table 27. Power Control Initiators                                   | 56 |

| Table 28. ACPI Power States                                          | 58 |

| Table 29. System Reset Sources and Actions                           | 59 |

| Table 30. BMC Reset Sources and Actions                              | 60 |

| Table 31. System Status LED Indicator States                         | 62 |

| Table 32. FRU Device ID Map                                          | 66 |

| Table 33. | Processor Sensors                                                       | . 68 |

|-----------|-------------------------------------------------------------------------|------|

| Table 34. | Processor Status Sensor Implementation                                  | . 68 |

| Table 35. | System Fan Domains                                                      | . 70 |

| Table 36. | BMC Self Test Results                                                   | .72  |

| Table 37. | Standard Channel Assignments                                            | .73  |

| Table 38. | Keyboard Controller Style Interfaces                                    | .74  |

| Table 39. | Factory Default Event Filters                                           | . 77 |

| Table 40. | Intel <sup>®</sup> Server Board X38ML Integrated BMC Sensors            | .79  |

| Table 41. | Console Redirection Escape Sequences for Headless Operation             | .85  |

| Table 42. | Memory Error Events                                                     | . 93 |

| Table 43. | Examples of Event Data Field Contents for Memory Errors                 | . 94 |

| Table 44. | PCI Error Events                                                        | .94  |

| Table 45. | Examples of Event Data Field Contents for PCI Errors                    | .95  |

| Table 46. | FRB-2 Error Events                                                      | .95  |

| Table 47. | Timestamp Clock Sync Format                                             | . 97 |

| Table 48. | POST Progress Code LED Example                                          | . 98 |

| Table 49. | POST Code Checkpoints                                                   | . 98 |

| Table 50. | POST Error Messages and Handling                                        | 101  |

| Table 51. | Power Connector Pin-out (J4K1)                                          | 104  |

| Table 52. | PCI Express* x16 Connector Pin-out (J7B1)                               | 104  |

| Table 53. | SMBus Connector Pin-out (J3C1)                                          | 106  |

| Table 54. | Front Panel 16-Pin Header Pin-out (J5K4)                                | 106  |

| Table 55. | VGA Connector Pin-out (J8A1)                                            | 107  |

| Table 56. | NIC1-Intel <sup>®</sup> 82575EB (10/100/1000) Connector Pin-out (JA2A1) | 107  |

| Table 57. | NIC2- Intel <sup>®</sup> 82575EB (10/100/1000) Connector Pin-out (J3A2) | 108  |

| Table 58. | SATA Connector Pin-out (J1C1, J1C2, J2C2, J2C1)                         | 108  |

| Table 59. | External DB-9 Serial A Port Pin-out (J5A1)                              | 108  |

| Table 60. | Internal 3-pin Serial B Port Pin-out (J4C1)                             | 109  |

| Table 61. | USB Connectors Pin-out (JA2A1)                                          | 109  |

| Table 62. | Optional USB Connection Header Pin-out (J1B3)                           | 109  |

| Table 63. | 8-pin Fan Headers Pin-out (J5K1, J5K2, J5K3)                            | 110  |

| Table 64. | Chassis Intrusion Header (J1B2) Pin-out                                 | 110  |

| Table 65. | Jumper Block Definitions (J1A2, J1A3, J1A4, J3A1, J6B1)                 | 111  |

| Table 66. | Absolute Maximum Ratings                                                | 112  |

< This page intentionally left blank. >

## 1. Introduction

This Technical Product Specification (TPS) provides a high-level technical description for the Intel<sup>®</sup> Server Board X38ML. It details the architecture and feature set for all functional subsystems that make up the server board.

## 1.1 Server Board Use Disclaimer

Intel<sup>®</sup> Server Boards support add-in peripherals and contain a number of high-density VLSI and power delivery components that require adequate airflow to cool. Intel develops and tests chassis to work with Intel server building blocks so the fully integrated system will meet the thermal requirements of all components. If Intel server building blocks are not used in the system, the system integrator must consult vendor datasheets and operating parameters to determine the air flow requirements for each application and the environmental conditions. Intel Corporation cannot be held responsible if components fail or the server board does not operate correctly when it is used outside of the published operating or non-operating limits.

## 2. Server Board Overview

The Intel<sup>®</sup> Server Board X38ML is a monolithic printed circuit board with features that support the entry HPC and high-density 1U server market.

## 2.1 Server Board Feature Set

- Processor and front side bus (FSB) support

- Single LGA775 Processor Socket

- Supports the following processors:

- Quad-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor X3360

- Quad-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor X3350

- Quad-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor X3320

- Quad-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor X3230

- Quad-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor X3220

- Quad-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor X3210

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor 3085

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor 3075

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor 3070

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor 3065

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor 3060

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor 3050

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor 3040

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual-Core Processor E2220

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual-Core Processor E2180

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual-Core Processor E2160

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual-Core Processor E2140

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad Processor Q9550

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad Processor Q9450

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad Processor Q9300

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad Processor Q6700

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad Processor Q6600

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme Processor X6800

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme Processor QX9770

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme Processor QX9650

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme Processor QX6700

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme Processor X6800

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo Processor E8500

- Intel<sup>®</sup> Core™2 Duo Processor E8400

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo Processor E6850

- Intel<sup>®</sup> Core™2 Duo Processor E8200

- Intel<sup>®</sup> Core™2 Duo Processor E6750

- Intel<sup>®</sup> Core™2 Duo Processor E6700

- Intel<sup>®</sup> Core™2 Duo Processor E6600

- Intel<sup>®</sup> Core™2 Duo Processor E4600

- Intel<sup>®</sup> Core ™2 Duo Processor E6840

- Intel<sup>®</sup> Core ™2 Duo Processor E4500

- Intel<sup>®</sup> Core™2 Duo Processor E6420

- Intel<sup>®</sup> Core™2 Duo Processor E6400

- Intel<sup>®</sup> Core™2 Duo Processor E4400

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo Processor E6320

- Intel<sup>®</sup> Core™2 Duo Processor E6300

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo Processor E4300.

- Supports 800/1066/1333MHz FSB

- Intel<sup>®</sup> X38 chipset components

- Intel<sup>®</sup> X38 MCH Memory Controller Hub

- Intel<sup>®</sup> ICH9R I/O Controller

- Memory subsystem

- DDR2 667/800 MHz, unbuffered ECC memory or non-ECC memory.

- Two memory channels, two DIMM sockets per channel

- 8 GB supported

- Video

- o 32 MB DDR2 667 MHz video memory

- o External VGA connector

- PCI Express\* connector

- One PCI Express\* x16 connector supporting PCI Express\* riser card

- HDD Interface

- Four SATA II, 300 Gb/s ports

- USB

- Two external USB 2.0 ports on rear I/O panel

- Two internal USB 2.0 headers

- LAN

- Dual Gigabit Ethernet device connects to PCI Express\* x4 interface on the ICH9R

- o Two 10/100/1000 Base-TX Interfaces through RJ45 Connectors

- System management

- Processor on-die temperature monitoring through Platform Environmental Control Interface (PECI)

- Board temperature measurement

- Fan speed monitoring and control

- Voltage monitoring

- o IPMI-based server management

- Power management

- o Support for power management of all capable components

- o ACPI compliant motherboard and BIOS

- Manufacturing

- o Surface mount technology, double-sided assembly

- Eight layer PCB

- Form factor

- o 13-inch by 5.9-inch, 1U thermally optimized design

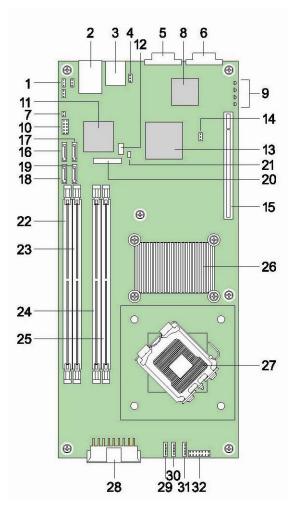

## 2.2 Server Board Layout

| Ref # | Description                                           | Ref # | Description |

|-------|-------------------------------------------------------|-------|-------------|

| 1     | (J1A2) BIOS Recovery Mode jumper                      | 17    | SATA Port 3 |

|       | (J1A3) CMOS Clear jumper                              |       |             |

|       | (J1A4) Integrated BMC Boot Block Write Protect jumper |       |             |

| 2     | (Bottom) USB Port 0                                   | 18    | SATA Port 0 |

|       | (Middle) USB Port 1                                   |       |             |

|       | (Top) NIC1 RJ-45 connector                            |       |             |

| Ref # | Description                                  | Ref # | Description                |

|-------|----------------------------------------------|-------|----------------------------|

| 3     | NIC2 RJ-45 connector                         | 19    | SATA Port 1                |

| 4     | (J3A1) Integrated BMC Force Update<br>Jumper | 20    | CMOS battery               |

| 5     | Serial A DB-9 connector                      | 21    | 1x3 Serial B header        |

| 6     | VGA connector                                | 22    | DIMM socket B2             |

| 7     | Chassis intrusion header                     | 23    | DIMM socket B1             |

| 8     | ServerEngines* Integrated BMC                | 24    | DIMM socket A2             |

| 9     | POST LED                                     | 25    | DIMM socket A1             |

| 10    | 2x5 USB header for USB 2 and 3               | 26    | Intel <sup>®</sup> X38 MCH |

| 11    | Intel <sup>®</sup> 82575EB LAN controller    | 27    | LGA775 processor socket    |

| 12    | SMBus connector                              | 28    | 2x9 main power connector   |

| 13    | Intel <sup>®</sup> 82801IR ICH9R             | 29    | System fan 1 (8-pin)       |

| 14    | (J6B1) Password Clear jumper                 | 30    | System fan 2 (8-pin)       |

| 15    | PCI Express* x16 riser slot                  | 31    | System fan 3 (8-pin)       |

| 16    | SATA Port 2                                  | 32    | 2x8 front panel connector  |

## Figure 1. Intel<sup>®</sup> Server Board X38ML Layout

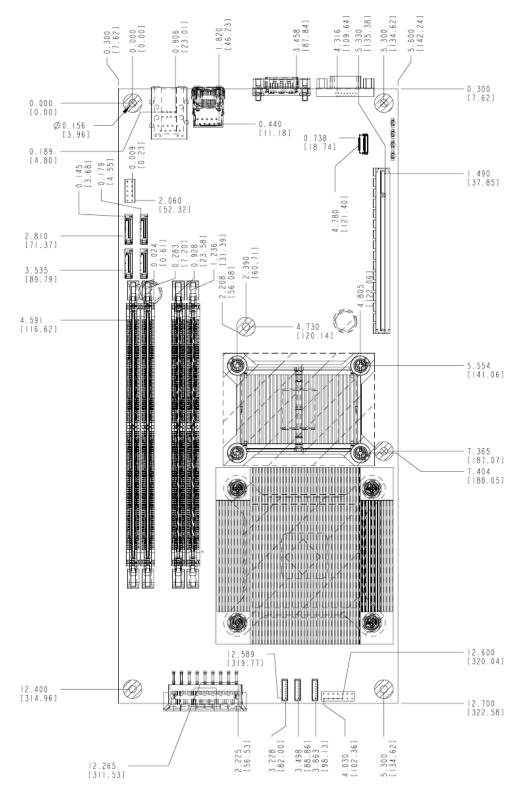

The following mechanical drawing shows the physical dimensions of the server board:

Figure 2. Intel<sup>®</sup> Server Board X38ML Mechanical Drawing

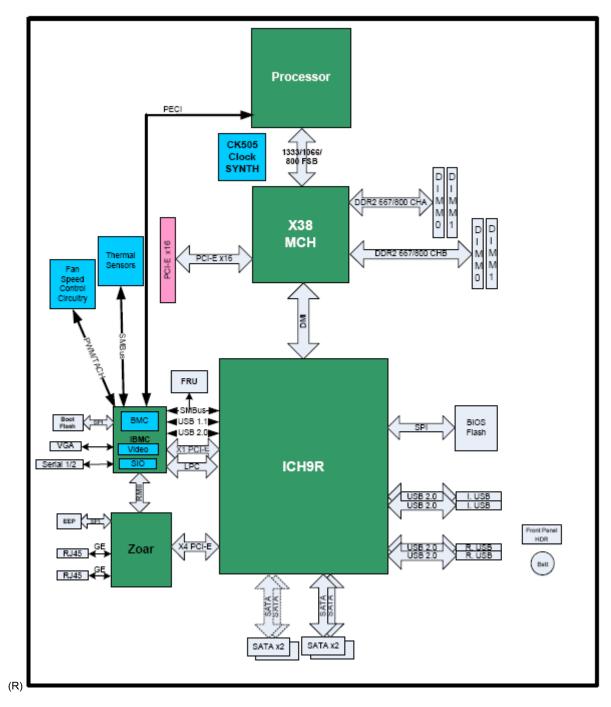

## 3. Functional Architecture

This chapter provides a high-level description of the functionality associated with the architectural blocks that make up the server board.

Figure 3. Server Board Block Diagram

## 3.1 Processor Subsystem

The Intel<sup>®</sup> Server Board X38ML supports one Intel<sup>®</sup> Xeon<sup>®</sup> or workstation processor utilizing Flip-Chip Land Grid Array (LGA) package technology, with an LGA775 socket. The supported processors are based on the Intel<sup>®</sup> Core<sup>™</sup> micro-architecture and built on 65 nm and 45 nm process technologies. They maintain compatibility with 32-bit software written for the IA-32 instruction set, while supporting 64-bit native mode operation when coupled with supported 64-bit operating systems and applications. Previous generations of Intel<sup>®</sup> processors are not supported.

The processors supported with the Intel<sup>®</sup> Server Board X38ML are listed below:

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor 3000 sequence

- Quad-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor 3200 sequence

- Quad-Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor 3300 sequence

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme Processor

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo Processor

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad Processor

The Intel<sup>®</sup> Server Board X38ML does not provide support for the following processors:

- Intel<sup>®</sup> Pentium<sup>®</sup> 4 Processor Extreme Edition

- Intel<sup>®</sup> Pentium<sup>®</sup> D Processor

- Intel<sup>®</sup> Pentium<sup>®</sup> 4 Processor

- Intel<sup>®</sup> Celeron<sup>®</sup> D Processor

| Processor Family                                                       | Processor Number | Clock Speed | Front Side Bus | L2 Cache |

|------------------------------------------------------------------------|------------------|-------------|----------------|----------|

| Dual-Core Intel <sup>®</sup> Xeon <sup>®</sup> Processor 3000 sequence | 3070             | 2.66 GHz    | 1066 MHz       | 4 MB     |

| Quad-Core Intel <sup>®</sup> Xeon <sup>®</sup> Processor 3200 sequence | X3210            | 2.13 GHz    | 1066 MHz       | 8 MB     |

| Quad-Core Intel <sup>®</sup> Xeon <sup>®</sup> Processor 3300 sequence | X3360            | 2.83 GHz    | 1333 MHz       | 12 MB    |

| Intel <sup>®</sup> Core™2 Extreme Edition                              | X6800            | 2.93 GHz    | 1066 MHz       | 4 MB     |

| Intel <sup>®</sup> Core™2 Duo                                          | E6300            | 1.86 GHz    | 1066 MHz       | 2 MB     |

| Intel <sup>®</sup> Core™2 Quad Processor                               | Q6600            | 2.40 GHz    | 1066 MHz       | 8 MB     |

**Note:** For a complete list of supported processors, refer to the Intel<sup>®</sup> Server Board X38ML support Web site: http://support.intel.com/support/motherboards/server/X38ML/.

### 3.2 Intel<sup>•</sup> X38 Chipset

The Intel<sup>®</sup> Server Board X38ML is designed around the Intel<sup>®</sup> X38 chipset. The chipset consists of two components that work together to provide the interface between all major subsystems found on the server board, including the processor, memory, and I/O subsystems. These components are:

- Memory Controller Hub (Intel<sup>®</sup> X38 MCH)

- I/O Controller Hub (Intel<sup>®</sup> ICH9-R)

The following sub-sections provide an overview of the primary functions and supported features of each chipset component as they are used on the Intel<sup>®</sup> Server Board X38ML. Later sections provide more detail on the implementation of the subsystems.

#### 3.2.1 Memory Controller Hub (MCH): Intel<sup>•</sup> X38 MCH

The MCH integrates four interfaces:

- 1. Processor/host interface (FSB)

- Supports LGA775 processors in a UP System configuration

- 200/266/333 MHz FSB clock frequency. Supports FSB transfer rates of 800/1066/1333 MT/s.

- GTL+ bus drivers with integrated GTL termination resistors

- 2. System memory interface (memory controller)

- Supports 512 Mbit, and 1 Gbit memory technologies

- DDR2 667, 800 MHz

- 8 GB addressable memory

- Supports unbuffered, ECC, and non-ECC DIMM

- 3. Direct media interface (DMI) interface

- Interface to the Intel<sup>®</sup> ICH9R South Bridge

- 100 MHz reference clock shared with PCI Express\* interface(s)

- 4. PCI Express\* interface

- Contains two PCI Express\* x16 ports. One PCI Express\* x16 port is connected to one PCI Express\* X16 connector as shown in the block diagram.

- Compliant with the PCI Express\* base specification revision 2.0.

#### 3.2.2 I/O Controller Hub: Intel<sup>•</sup> ICH9-R

The Intel<sup>®</sup> ICH9-R component integrates bridge functionality for PCI Express\*, LPC, USB, SATA II, IDE and SMBus, and numerous board management functions. The ICH9R is packaged in a 31 mm x 31 mm 676 pin mBGA.

#### 3.2.2.1 Direct Media Interface (DMI)

DMI is the name given to chip-to-chip connection between the Intel<sup>®</sup> X38 MCH and the Intel<sup>®</sup> ICH9-R. DMI is an X4 link that mostly adheres to the PCI Express\* specification. Deviations of the DMI from standard PCI Express\* specifications are described in the Intel<sup>®</sup> ICH9 component specification.

#### 3.2.2.2 PCI Express\* Interfaces

The Intel<sup>®</sup> ICH9R provides six PCI Express\* Root Ports (GEN1), which are compliant with the *PCI Express Base Specification*, Revision 1.1. The PCI Express\* root ports 1-4 can be statically configured as four x 1 ports, or ganged together to form two x 2 ports, one x 2 with two x1 ports, or one x4 port. Ports 5 and 6 can be used as two x1 ports or one x2. The x4 configuration supports lane reversal. Each Root Port fully supports 2.5 Gb/s bandwidth in each direction.

On the Intel<sup>®</sup> Server Board XM38ML, Root Ports 1-4 are ganged together to form a single x4 link connecting to an Intel<sup>®</sup> 82575EB NIC controller. Port 5 is connected to the Integrated BMC for 2D video function and Port 6 is not used.

#### 3.2.2.3 Serial ATA II Interface

The Intel<sup>®</sup> ICH9R has an integrated SATA II host controller that supports independent DMA operation on the six ports and supports data transfer rates of up to 300 MB/Sec. The SATA II Controller provides two modes of operation – a legacy mode that uses I/O space and an Advanced Host Controller Interface (AHCI) mode that uses memory space.

#### 3.2.2.4 Low Pin Count Interface (LPC)

The low pin count interface on the Intel<sup>®</sup> ICH9R provides a low system cost design interface solution for connecting the Super I/O (SIO) for the legacy interfaces such as the parallel port, serial port, and floppy drive.

#### 3.2.2.5 Compatibility Modules

The Intel<sup>®</sup> ICH9 incorporates compatibility modules such as DMA controller, timer/counters, and interrupt controller. The DMA controller incorporates the logic of two 8237 DMA controllers, with seven independently programmable channels. Channels 0 - 3 are hard-wired to 8-bit, count-by-byte transfers and channels 5 to 7 are hardwired to 16-bit, count-by-word transfers. DMA Channel 4 is used to cascade the two 8327 controllers together. The DMA controller is used to support the LPC DMA.

The LPC DMA is handled through the LDRQ# lines from peripherals and special encoding on LAD[3:0] from the host.

The timer/counter block contains three counters that are equivalent in function to those found in one 8254 programmable internal timer. These three counters are combined to provide the system timer function and speaker tone. The 14.318 MHz oscillator input provides the clock source for these three counters.

The Intel<sup>®</sup> ICH9 provides an ISA compatible Programmable Interrupt Controller (PIC) that incorporates the functionality of two 8259 interrupt controllers. Each 8259 supports eight interrupts that are cascaded via one master controller interrupt 2 for fifteen programmable interrupts. The interrupts are for the system timer, keyboard controller, serial ports, parallel ports, floppy disk, mouse, DMA channels, and mapped PCI-based interrupts.

#### 3.2.2.6 Universal Serial Bus (USB) Controller

The Intel<sup>®</sup> ICH9 contains two EHCI and six UHCI USB Controllers providing support for twelve USB 2.0 ports. All twelve ports are high speed, full-speed, and low speed capable. The port routing logic for the ICH9 determines whether a USB port is controlled by one of the UHCI controllers or by the EHCI controller. USB 2.0 based debug port is also implemented in the ICH9.

#### 3.2.2.7 Real Time Clock (RTC)

The Intel<sup>®</sup> ICH9 contains a Motorola MS146818A functionally compatible real-time clock with two 128-byte banks of battery-backed RAM. The RTC performs two key functions on the Intel<sup>®</sup> Server Board XM38ML:

#### Keeps track of the time of day

Stores system configuration data even when the system is powered down

The RTC operates on a 32.768 KHz crystal and a 3 V lithium battery.

#### 3.2.2.8 GPIO

The Intel<sup>®</sup> ICH9 contains 61 general purpose inputs/outputs. The General Purpose Inputs and Outputs (GPIO) are provided for custom system design.

#### 3.2.2.9 Enhanced Power Management

The Intel<sup>®</sup> ICH9R supports the Advanced Configuration and Power Interface, Version 2.0 (ACPI) that provides power and thermal management. The Intel<sup>®</sup> ICH9R also supports the Manageability Engine Power Management Support for new wake events from the MCH Management Engine.

#### 3.2.2.10 System Management Interface

The Intel<sup>®</sup> ICH9R provides a SMBus 2.0 compliant Host Controller that allows the processor to communicate with SMBus slaves. This interface is compatible with most I<sup>2</sup>C devices. The ICH9R also supports slave functionality. The SMBus logic exists in Device 31: Function 3 configuration space.

#### 3.2.2.11 Serial Peripheral Interface (SPI)

The Serial Peripheral Interface (SPI) is a 4-pin interface that provides a potentially lower-cost alternative for the system flash versus the Firmware Hub on the LPC Bus. The Intel<sup>®</sup> ICH9 supports two SPI flash components using two separate chip select pins. Each component may be up to 16 MB and operate in SPI Fast Read Instructions and frequencies of 20 MHZ or 33 MHz. The SPI Interface has the following features:

- Clock (CLK)

- Master Out Slave In (MOSI)

- Master In Slave Out (MISO)

- Chip Select (CS#)

Communication on the SPI is done with a Master – Slave protocol.

The SPI flash can operate in two operational modes: descriptor and non-descriptor. When operating in non-descriptor mode, the SPI Flash only supports the BIOS through register access.

When used in descriptor mode, the ICH9 allows a single SPI flash device to store the system BIOS, Intel<sup>®</sup> AMT Firmware, and Gigabit Ethernet EEPROM information.

The SPI Flash Memory device is an Atmel\* AT26DF321 - a 32 mbit, 2.7 to 3.6 volt serial interface FLASH memory, Intel part number D64145-001/D64145-002. This device is installed directly onto the server board without the use of sockets.

#### 3.2.2.12 Manageability

The Intel<sup>®</sup> ICH9 integrates several functions to manage the system and lower the total cost of ownership (TCO) of the system. These system management functions report errors, diagnose the system, and recover from system lockups without the aid of an external microcontroller.

The management engine includes the following features:

- TCO timer to detect system locks

- Process Present Indicator to determine if the processor fetches the first instruction after reset

- ECC Error reporting from the host controller

- Function Disable to prevent a disabled function from generating interrupts and power management events

- Intruder Detect input for system cases

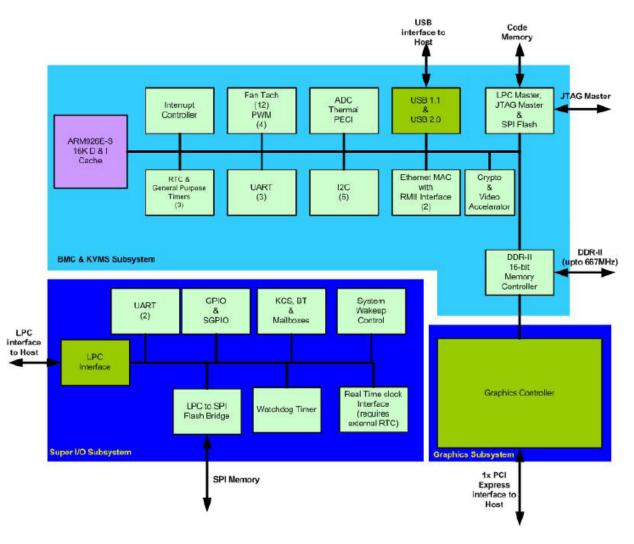

### 3.3 Integrated Baseboard Management Controller

A ServerEngines\* Baseboard Management Controller (Integrated BMC) is integrated onto the server board. This integrates the baseboard management controller (BMC and KVMS subsystem), graphics controller (graphics subsystem), and Super I/O interface (Super I/O subsystem). The Intel<sup>®</sup> Server Board XM38ML does not support remote KVMS features.

#### 3.3.1 Functionality Overview

- Baseboard management controller

- IPMI 2.0 compliant

- Integrated 250 MHz 32-bit ARM9 processor

- Six I<sup>2</sup>C SMBus Modules with master-slave support

- Two independent 10/100 Ethernet controllers with RMII support

- LPC master interface for non-volatile code storage

- SPI Flash interface

- Three UART for ICMB support

- DDR2 16-bit up to 667 MHz memory interface

- Sixteen mailbox registers for communication between the host and the BMC

- Watchdog timer

- Three general purpose timers

- Dedicated real-time clock for BMC

- Up to 16 direct and 64 serial GPIO ports

- Ability to maintain text and graphics controller history

- Twelve 10-bit analog to digital converters

- Three diode inputs for temperature measurements

- Eight fan tachometer inputs

- Four pulse width modulators (PWM)

- Chassis intrusion logic with battery-backed general purpose register

- LED support with programmable blink rate control

- Programmable I/O port snooping, which can be used to snoop on Port 80h

- Unique chip ID for each part, burned at the time production testing

- Hardware 32-bit random number generator

- JTAG master interface

- On-chip test Infrastructure for testing BMC firmware

- Remote KVMS features

- USB 2.0 interface for keyboard, mouse, and remote storage such as CD-ROM/DVD-ROM and floppy

- USB 1.1 interface for PS/2 to USB bridging, remote keyboard and mouse

- Hardware-based video compression and redirection logic

- Supports both text and graphics redirection

- Hardware-assisted video redirection using the frame processing engine

- Direct interface to the Integrated Graphics Controller registers and Frame buffer

- Hardware-based encryption engine

- Graphics controller

- Integrated graphics core

- 2D hardware graphics acceleration

- DDR2 memory interface supports up to 128 Mbytes of memory

- Supports all display resolutions up to 1600 x 1200 16 bpp @ 75 Hz

- High speed integrated 24-bit RAMDAC

- Single lane PCI Express\* host interface

- Server Class Super I/O functionality includes

- Keyboard style/BT interface for BMC support

- Two fully functional serial ports, compatible with the 16C550

- Serial IRQ support

- SMI/SCI/PME support

- ACPI-compliant

- Up to 16 shared GPIO ports

- Programmable wake-up event support

- Plug and play register set

- Power supply control

- Watchdog timer compliant with Microsoft SHDG

- LPC to SPI bridge for system BIOS support

- Real-time clock module with the external RTC interface

#### 3.3.2 Block Diagram

The following block diagram shows the three main host interface of the integrated BMC. The LPC, PCI Express\*, and USB interfaces are resourced by the Intel<sup>®</sup> ICH9R on the Intel<sup>®</sup> Server Board X38ML.

The LPC interface to the host is used for the Super I/O and BMC functionality. The BMC can communicate with the host through the KCS or BT interfaces. The Super I/O interface also integrates a LPC to SPI Flash bridge, which can be used to store multiple copies of the system ROM.

The PCI Express\* interface is mainly used for the graphics controller interface to the host. The graphics controller is a fully compliant VGA controller with 2D hardware acceleration and full bus master support. The graphics controller can support up to 1600 x1200 resolutions at high refresh rates.

The USB 1.1 is used for the remote keyboard and mouse support and the USB2.0 is used for the remote storage support. The Integrated BMC supports various storage devices such as CD-ROM, DVD-ROM, CD-ROM (ISO image), floppy, and USB flash disk. Any of the storage devices can be used as a boot device and the host can boot from this remote media.

Figure 4. Integrated BMC Block Diagram

## 3.4 Memory Subsystem

#### 3.4.1 Memory Support

The server board supports four DDR2 667/800 MHz unbuffered ECC or non-ECC DIMMs, two memory channels, two DIMMs per memory channel. The maximum memory capacity supported is 8 GB using four DIMMs of 2 GB unbuffered, 1 Gbit DDR2 memory.

Only DIMMs tested and qualified by Intel or a designated memory test vendor are supported. A list of qualified DIMMs is at <u>http://support.intel.com/support/motherboards/server/X38ML/</u>.

**Note:** All DIMMs are supported by design, but only fully qualified DIMMs are supported on the board.

#### 3.4.2 Memory Population Rules

The X38 MCH supports two DDR2 DIMM sockets for Channel A, and two DDR2 DIMM sockets for Channel B. The four slots are partitioned with Channel A representing the Channel A DIMMs

(DIMM A1 and DIMM A2) and Channel B representing the Channel B DIMMs (DIMM B1 and DIMM B2). They are placed in a row and numbered as DIMM A1/DIMM A2/DIMM B1/DIMM B2 with DIMM A1 the closest to the MCH.

Memory population rules:

- If dual-channel operation is desired, Channel A and Channel B must be populated identically (for example, same capacity)

- Use DDR2 667/800 only

- The speed used on all the channels is the slowest DIMM in the system

- Use ECC or non-ECC DIMMs

- User can mix different memory technologies (size and density)

- For single-channel mode, either channel may be used and DIMM sockets within the same channel can be populated in any order

- For dual-channel interleaved mode, DIMM sockets may be populated in any order as long as the total memory in each channel is the same.

- For dual-channel asymmetric mode, DIMM sockets may be populated in any order.

## 3.5 I/O Subsystem

### 3.5.1 PCI Express\* x16 Riser Slot

The server board provides a PCI Express\* x16 riser slot that is resourced with a PCI Express\* x16 interface from MCH and supports PCI Express\* x16 graphics.

### 3.5.2 SATA Support

The server board provides four SATA II ports by the integrated SATA controller of the Intel<sup>®</sup> ICH9-R. The SATA controller supports data transfer rates of up to 300 MB/sec and provides two modes of operation: a legacy mode using I/O space and an Advanced Host Controller Interface (AHCI) mode using memory space.

#### 3.5.2.1 SATA RAID

Intel<sup>®</sup> Embedded Server RAID Technology, available with the CH9R, supports four Serial ATA ports, providing a cost-effective way to achieve higher transfer rates and reliability. Intel<sup>®</sup> Embedded Server RAID Technology supports:

- RAID level 0 data striping for improved performance

- RAID level 1 data mirroring for improved data reliability

- RAID level 10 data striping and mirroring for high data transfer rates and data redundancy

Intel<sup>®</sup> Embedded Server RAID Technology functionality requires the following items:

- Intel<sup>®</sup> ICH9-R

- Intel<sup>®</sup> RAID Technology option ROM

- Most recent version of the Intel<sup>®</sup> Application Accelerator RAID Edition drivers

- Two SATA hard drives

Intel<sup>®</sup> RAID Technology is not available in these configurations:

- The SATA controller in compatible mode

- Intel<sup>®</sup> RAID Technology disabled

#### 3.5.2.2 Intel<sup>•</sup> RAID Technology Option ROM

The Intel<sup>®</sup> RAID Technology for SATA Option ROM provides a pre-operating system user interface for the Intel RAID Technology implementation and provides the ability for an Intel RAID Technology volume to be used as a boot disk as well as to detect any faults in the Intel RAID Technology volume(s) attached to the Intel RAID controller.

#### 3.5.3 Video Support

The Integrated BMC integrates a fully compliant VGA graphics controller with hardware acceleration for BLIT and 2D graphics. The graphics controller:

- Is resourced with a PCI Express\* x1 interface from the ICH9R

- Supports 16-bit DDR2 memory running at a configurable frequency of 500 MHz. The maximum capacity is 128 MB.

- Supports all display resolutions up to 1600 x 1200 16bpp @ 75Hz

#### 3.5.4 Network Interface Controller (NIC)

The server board integrates an Intel<sup>®</sup> 82575EB Gigabit Ethernet Controller to provide two Gigabit Ethernet Ports. The NIC is resourced with a PCI Express\* x4 interface from the ICH9R. The NIC supports the following features:

- PCI Express\* x4 interface

- IEEE 802.3x compliant flow control support

- Integrated PHY for full 10/100/1000 Mbps full and half duplex operation

- On-board microcontroller

- Wake-On LAN support

#### 3.5.5 USB Support

The server board provides up to four USB 2.0 ports by the USB controller functionality integrated into the ICH9-R. Two external connectors are located on the back edge of the

baseboard. One 10-pin internal on-board header is provided which is capable of supporting two additional USB 2.0 ports.

#### 3.5.6 Super I/O Chip

The Super I/O chip integrated into the Integrated BMC provides legacy I/O support. The Super I/O chip contains the necessary circuitry to support two serial ports and hardware control/monitor functions. The server board implements the following features:

- Two fully functional serial ports, compatible with the 16C550

- Up to 16 shared GPIO ports

- Programmable wake-up event support

- Plug and play register set

- Power supply control

- Watchdog timer compliant with Microsoft SHDG\*

- LPC to SPI bridge for system BIOS support

- Real-time clock module with the external RTC interface

#### 3.5.6.1 Serial Ports

The board provides two serial ports. Serial A is a standard DB-9 interface located at the rear I/O panel of the server board next to the video connector. The reference designator is J5A1. Serial B is a 3-pin header interface located near the CMOS battery. The reference designator is J4C1.

| Pin | Signal Name | Serial Port A Header Pin-out |

|-----|-------------|------------------------------|

| 1   | DCD         | -                            |

| 2   | RXD         | 1 0                          |

| 3   | TXD         |                              |

| 4   | DTR         | 2 0 0 7                      |

| 5   | GND         | 3 0 0 8                      |

| 6   | DSR         | 4 0                          |

| 7   | RTS         |                              |

| 8   | CTS         | 5 0                          |

| 9   | RI          |                              |

#### Table 2. Serial A Header Pin-out

| Pin | Signal Name | Serial Port B Header Pin-out |

|-----|-------------|------------------------------|

| 1   | RXD         |                              |

| 2   | GND         |                              |

| 3   | TXD         |                              |

|     |             | (2) GND                      |

|     |             |                              |

|     |             | (3) Tx                       |

|     |             |                              |

|     |             | 3-pin Serial B header        |

|     |             |                              |

#### Table 3. Serial B Header Pin-out

#### 3.5.6.2 Keyboard and Mouse Support

USB ports can be used to support keyboard and mouse. No PS/2 port is provided.

#### 3.5.6.3 Wake-up Control

The Super I/O contains functionality that allows various events to control the power-on and power-off the system.

### 3.6 Replacing the Back-Up Battery

The lithium battery on the server board powers the RTC for up to ten years in the absence of power. When the battery starts to weaken, it loses voltage, and the server settings stored in CMOS RAM in the RTC (for example, the date and time) may be incorrect. Contact your customer service representative or dealer for a list of approved devices.

####

Danger of explosion, if battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the equipment manufacturer. Discard used batteries according to manufacturer's instructions.

### ADVARSEL!

Lithiumbatteri - Eksplosionsfare ved fejlagtig håndtering. Udskiftning må kun ske med batteri af samme fabrikat og type. Levér det brugte batteri tilbage til leverandøren.

### ADVARSEL

Lithiumbatteri - Eksplosjonsfare. Ved utskifting benyttes kun batteri som anbefalt av apparatfabrikanten. Brukt batteri returneres apparatleverandøren.

VARNING

Explosionsfara vid felaktigt batteribyte. Använd samma batterityp eller en ekvivalent typ som rekommenderas av apparattillverkaren. Kassera använt batteri enligt fabrikantens instruktion.

## VAROITUS

Paristo voi räjähtää, jos se on virheellisesti asennettu. Vaihda paristo ainoastaan laitevalmistajan suosittelemaan tyyppiin. Hävitä käytetty paristo valmistajan ohjeiden mukaisesti.

## 4. System BIOS

## 4.1 BIOS Identification String

The BIOS identification string uniquely identifies the revision of the BIOS. The string is formatted as follows:

BoardFamilyID.OEMID.MajorRev.MinorRev.BuildID.BuildDateTime

Where:

- BoardFamilyID = String name for this board family

- OEMID = Three-character OEM ID. "86B" is used for Intel<sup>®</sup> Server Boards

- MajorRev = Two decimal digits

- MinorRev = Two decimal digits

- BuildID = Four decimal digits

- BuildDateTime = Build date and time in MMDDYYYYHHMM format:

- MM = Two-digit month

- DD = Two-digit day of month

- YYYY = Four-digit year

- HH = Two-digit hour using 24-hour clock

- M = Two-digit minute

For example, BIOS Build 3, generated on Jan 21, 2006 at 11:59 AM has the following BIOS ID string displayed in the POST diagnostic screen:

S3200X38.86B.01.00.0003.012120061159

The BIOS version in the Setup Utility is displayed as:

S3200X38.86B.01.00.0003

The BIOS ID is identifies the BIOS image. It is not used to designate the board ID (S3200X38) or the BIOS phase (Alpha, Beta, and so on). Support for INT15H, Function DA8Ch (Get BIOSID) was removed. The BIOS ID is available in the SMBIOS type 0 structure and in BIOS Setup.

The Board ID is available in the SMBIOS type 2 structure and in BIOS Setup. You can determine the phase of the BIOS by the release notes associated with the image.

### 4.2 Logo/Diagnostic Screen

The Logo/Diagnostic Screen is in one of two forms given below:

- If Quiet Boot is enabled in BIOS Setup, a logo splash screen is displayed. By default, Quiet Boot is enabled in BIOS Setup. If the logo is displayed during POST, pressing <Esc> hides the logo and displays the diagnostic screen.

- If no logo is present in the flash ROM or if Quiet Boot is disabled in the BIOS Setup, the summary and diagnostic screen is displayed.

The diagnostic screen consists of this information:

- BIOS ID

- Platform name

- Total memory detected (Total size of all installed DIMMs)

- Processor information (Intel branded string, speed, and number of physical processors identified)

- Types of keyboards detected if plugged in (USB)

- Types of mouse devices detected if plugged in (USB)

### 4.3 BIOS Setup Utility

The BIOS Setup utility is a text-based utility that allows the user to configure the system and view current settings and environment information for the platform devices. The Setup utility controls the platform's built-in devices, boot manager, and error manager.

The BIOS Setup utility interface consists of a number of pages or screens. Each page contains information or links to other pages. The Advanced tab in Setup displays a list of general categories as links. These links lead to pages containing a specific category's configuration.

The following sections describe the look and behavior for BIOS Setup.

#### 4.3.1 Operation

The BIOS Setup utility is only available in English. It is functional via console redirection over various terminal emulation standards. This may limit some functionality for compatibility (for example, usage of colors or some keys or key sequences or support of pointing devices).

#### 4.3.1.1 Setup Page Layout

The Setup utility page layout is sectioned into functional areas. Each occupies a specific area of the screen and has dedicated functionality as described by the table:

| Functional Area | Description                                                                                                                                                                                                                                                                                                              |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title Bar       | The title bar is located at the top of the screen and displays the title of the form (page) the user is currently viewing. It may also display navigational information.                                                                                                                                                 |

| Setup Item List | The Setup Item List is a set of controllable and informational items. Each item in the list occupies the left and center columns in the middle of the screen. The left column, the "Setup Item", is the subject of the item. The middle column, the "Option", contains an informational value or choices of the subject. |

#### Table 4. BIOS Setup Page Layout

| Functional Area         | Description                                                                                                                                                                                                                                           |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                         | A Setup Item may also be a hyperlink used to navigate form sets (pages). When it is a hyperlink, a Setup Item only occupies the "Setup Item" column.                                                                                                  |  |

| Item Specific Help Area | The Item Specific Help area is located on the right side of the screen and contains help text for the highlighted Setup Item. Help information includes the meaning and usage of the item, allowable values, effects of the options, and so on.       |  |

| Keyboard Command Bar    | The Keyboard Command Bar is located at the bottom right of the screen and continuously displays help for keyboard special keys and navigation keys. The keyboard command bar is context-sensitive—it displays keys relevant to current page and mode. |  |

#### 4.3.1.2 Entering BIOS Setup

The BIOS Setup utility is initiated by pressing <F2> during system boot when the OEM or Intel logo is displayed.

When Quiet Boot is disabled, the following message is displayed on the diagnostics screen: Press <F2> to enter setup.

Serious errors cause the system to enter the BIOS setup. The error manager screen will display in this occurrence.

#### 4.3.1.3 Keyboard Commands

The bottom right portion of the Setup screen provides a list of commands to navigate through the Setup utility. These commands are displayed at all times.

Except for features used for informative purposes, each feature on each Setup menu page is associated with a value field. This field contains user-selectable parameters. Depending on the security option chosen and in effect by the password, a menu feature's value may or may not be changeable. If a value is non-changeable, the feature's value field is inaccessible and displays as "grayed out."

The Keyboard Command Bar supports the following:

| Key             | Option             | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <enter></enter> | Execute<br>Command | The <enter> key is used to activate sub-menus when the selected feature is a sub-<br/>menu, or to display a pick list if a selected option has a value field, or to select a<br/>sub-field for multi-valued features such as time and date. If a pick list is displayed,<br/>the <enter> key will select the currently highlighted item, undo the pick list, and<br/>return the focus to the parent menu.</enter></enter> |

| Key         | Option         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <esc></esc> | Exit           | The <esc> key provides a mechanism for backing out of any field. When the <esc> key is pressed while editing any field or selecting features of a menu, the parent menu is re-entered.</esc></esc>                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             |                | When the <esc> key is pressed in any sub-menu, the parent menu is re-entered.<br/>When the <esc> key is pressed in any major menu, the exit confirmation window is<br/>displayed and the user is asked whether changes can be discarded. If "No" is<br/>selected and the <enter> key is pressed, or if the <esc> key is pressed, the user is<br/>returned to where he/she was before <esc> was pressed, without affecting any<br/>existing settings. If "Yes" is selected and the <enter> key is pressed, setup is<br/>exited and the BIOS returns to the main System Options Menu screen.</enter></esc></esc></enter></esc></esc> |

|             | Select Item    | The up arrow is used to select the previous value in a pick list, or the previous option in a menu item's option list. The selected item must then be activated by pressing the <enter> key.</enter>                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | Select Item    | The down arrow is used to select the next value in a menu item's option list, or a value field's pick list. The selected item must then be activated by pressing the <enter> key.</enter>                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             | Select Menu    | The left and right arrow keys are used to move between the major menu pages.<br>The keys have no effect if a sub-menu or pick list is displayed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <tab></tab> | Select Field   | The <tab> key is used to move between fields. For example, you can use <tab> to move from hours to minutes in the time item in the main menu.</tab></tab>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| -           | Change Value   | The minus key on the keypad is used to change the value of the current item to the previous value. This key scrolls through the values in the associated pick list without displaying the full list.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| +           | Change Value   | The plus key on the keypad is used to change the value of the current menu item to the next value. This key scrolls through the values in the associated pick list without displaying the full list. On 106-key Japanese keyboards, the plus key has a different scan code than the plus key on the other keyboard, but will have the same effect.                                                                                                                                                                                                                                                                                 |

| <f9></f9>   | Setup Defaults | Pressing <f9> causes the following to display:</f9>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                | Load Optimized Defaults?<br>Yes No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             |                | If Yes is highlighted and <enter> is pressed, all Setup fields are set to their default values. If No is highlighted and <enter> is pressed, or if the <esc> key is pressed, the user is returned to where they were before <f9> was pressed without affecting any existing field values.</f9></esc></enter></enter>                                                                                                                                                                                                                                                                                                               |

| <f10></f10> | Save and Exit  | Pressing <f10> causes the following message to display:</f10>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             |                | Save configuration and reset?<br>Yes No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |