# Intel<sup>®</sup> Quark<sup>™</sup> SoC X1000

**UEFI Firmware Writer's Guide**

June 2014

Order Number: 330236-003US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANT, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm

Any software source code reprinted in this document is furnished for informational purposes only and may only be used or copied and no license, express or implied, by estoppel or otherwise, to any of the reprinted source code is granted by this document.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. Go to: http://www.intel.com/products/processor\_number/

Code Names are only for use by Intel to identify products, platforms, programs, services, etc. ("products") in development by Intel that have not been made commercially available to the public, i.e., announced, launched or shipped. They are never to be used as "commercial" names for products. Also, they are not intended to function as trademarks.

Intel, the Intel logo, and Quark are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2014, Intel Corporation. All rights reserved.

## **Revision History**

| Date       | Document<br>Revision | Software<br>Release | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|------------|----------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| June 2014  | 003                  | 1.0.2               | <ul> <li>Updates are indicated with changebars and include:</li> <li>Removed: De-featured SPI DMA IOBAR (SPI DMA configured via Message Network and not via CPU IO Space).</li> <li>Updated: IMR protection no longer enabled by default.</li> <li>Updated: Firmware Recovery trusts SPI flash platform data if various checks pass.</li> <li>Updated: Trusted Platform Module (TPM) Support.</li> <li>Updated: UEFI Firmware Sources: Basic Firmware Requirements and GPIO Handling.</li> <li>Updated: Firmware Update to add clarification on capsule creation.</li> </ul>                                                                                   |  |

| May 2014   | 002                  | 1.0.1               | <ul> <li>Updates are indicated with changebars and include:</li> <li>Updated Table 1, Table 2, and Table 3.</li> <li>Modified UEFI Firmware Sources references in Section 4.13 and Section 10.7.</li> <li>Updated Section 13.1 and added UEFI Firmware Sources reference for Section 13.1.1.</li> <li>Modified UEFI Firmware Sources references in Section 20.3 and Section 21.12.</li> <li>Added Section 25.3, "I2C* Host Controller DXE Protocol" on page 125.</li> <li>Added Section 26.0, "Trusted Platform Module (TPM) Support" on page 126.</li> <li>Updated with trademarked term: Intel<sup>®</sup> Quark<sup>™</sup> SoC (no changebars).</li> </ul> |  |

| March 2014 | 001                  | 1.0.0               | First public release of document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

## Contents

|                                                                            | 11 |

|----------------------------------------------------------------------------|----|

| 1.1 Terminology                                                            |    |

| 1.2 Reference Documents                                                    |    |

| 1.3 Related Documents                                                      |    |

| 1.4 Related Websites                                                       |    |

| 1.5 Formats and Notations                                                  | 14 |

| 2.0 Introduction                                                           | 16 |

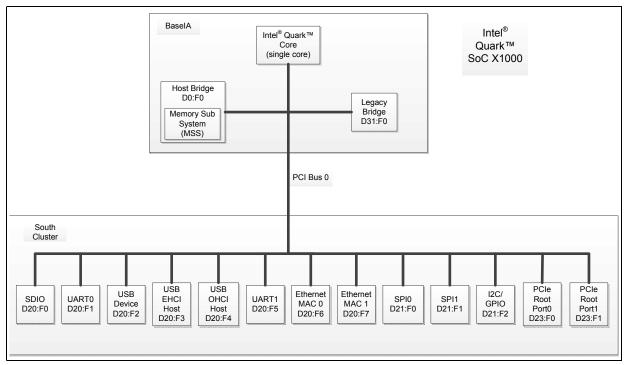

| 2.1 Component Identification                                               | 17 |

| 3.0 Register Access Mechanisms                                             | 19 |

| 3.1 Message Network                                                        | 19 |

| 3.1.1 Message Network Registers                                            |    |

| 3.1.2 Message Network Register Programming                                 |    |

| 3.2 PCI Express* Configuration Space Base Address                          |    |

| 3.2.1 Bus:Device:Function:Register Offset Translation                      | 22 |

| 4.0 Basic Firmware Requirements                                            |    |

| 4.1 Configuring Memory and MMIO Accesses                                   |    |

| 4.2 Early Memory Setup                                                     |    |

| 4.3 Isolated Memory Regions (IMRs)                                         |    |

| 4.4 Initializing Chipset Registers                                         |    |

| 4.4.1 MMIO Write Considerations                                            |    |

| 4.4.2 Non-Standard BARs                                                    |    |

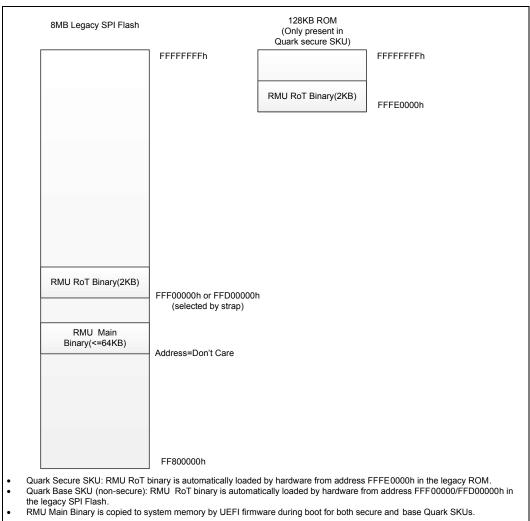

| 4.4.3 Static Register Programming<br>4.5 Remote Management Unit Binary     |    |

| 4.5 Remote Management Unit Binary                                          |    |

| 4.5.2 Base SKU (Non-Secure)                                                |    |

| 4.6 RMU Binary Relocation                                                  |    |

| 4.6.1 RMU Binary Relocation Considerations                                 |    |

| 4.7 PCI/PnP Enumeration                                                    |    |

| 4.8 ACPI Support                                                           |    |

| 4.9 Reporting Interrupt Routing to the OS                                  |    |

| 4.10 Reporting IO/Memory Resources to the OS                               |    |

| 4.11 Chipset Sticky Registers                                              | 33 |

| 4.12 Boot Checklist                                                        |    |

| 4.13 UEFI Firmware Sources                                                 | 34 |

| 5.0 DDR3 DRAM Configuration                                                |    |

| 5.1 Intel <sup>®</sup> Quark <sup>™</sup> SoC System Memory Controller     |    |

| 5.2 MRC Flow Selection                                                     |    |

| 5.3 Programming Considerations                                             |    |

| 5.4 Memory Controller Initialization                                       |    |

| 5.4.1 Clear Self-Refresh                                                   |    |

| 5.4.2 Program DDR Timing Control                                           |    |

| 5.4.3 Program Pre-JEDEC Rank Decoding                                      |    |

| 5.4.4 Perform DDR Reset                                                    |    |

| 5.4.5 Initialize DDRIO<br>5.4.6 Perform JEDEC Initialization               |    |

| 5.4.6 Perform JEDEC Initialization<br>5.4.7 Signal Initialization Complete |    |

|                                                                            |    |

|                                                                            |    |

| 5.4.8 Restore Timings                                                      |    |

|                                                                            | 40 |

|      |       | 5.4.12 Read Training                                                                   |           |

|------|-------|----------------------------------------------------------------------------------------|-----------|

|      |       | 5.4.13 Write Training                                                                  |           |

|      |       | 5.4.14 Store Timings                                                                   |           |

|      |       | 5.4.15 Enable Scrambling                                                               | . 44      |

|      |       | 5.4.16 Program Execution Control                                                       | . 44      |

|      |       | 5.4.17 Configure Rank Population                                                       | . 45      |

|      |       | 5.4.18 Perform Wake                                                                    |           |

|      |       | 5.4.19 Change Refresh Period                                                           | . 45      |

|      |       | 5.4.20 Set Periodic Compensation                                                       |           |

|      |       | 5.4.21 Enable ECC                                                                      |           |

|      |       | 5.4.22 Memory Test                                                                     |           |

|      |       | 5.4.23 Lock Registers                                                                  |           |

|      | 5.5   | Memory Training Engine                                                                 |           |

|      | 5.6   | Memory Reference Code Configuration                                                    |           |

|      | 5.7   | UEFI Firmware Sources                                                                  |           |

|      |       |                                                                                        |           |

| 6.0  |       | D Instruction                                                                          |           |

|      | 6.1   | CPUID Functions                                                                        |           |

|      | 6.2   | UEFI Firmware Sources                                                                  | . 51      |

| 7.0  | Mode  | el Specific Registers                                                                  | 52        |

| /.0  | 7.1   | UEFI Firmware Sources                                                                  |           |

|      |       |                                                                                        |           |

| 8.0  | Syste | em Management Mode (SMM)                                                               | . 53      |

|      | 8.1   | Initializing SMM                                                                       | . 53      |

|      |       | 8.1.1 Responsibilities of the SMM Relocation Handler                                   | . 53      |

|      | 8.2   | SMM Revision Identifier                                                                | . 54      |

|      | 8.3   | SMM State Save Map                                                                     | . 54      |

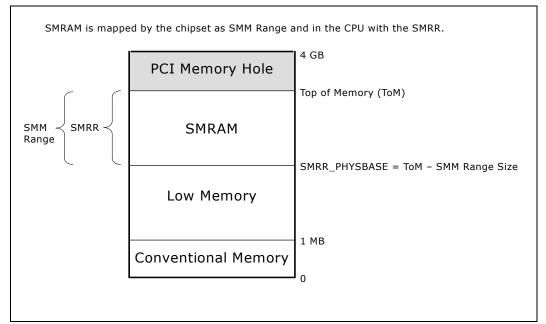

|      | 8.4   | SMRR Configuration Requirements                                                        |           |

|      | 8.5   | UEFI Firmware Sources                                                                  |           |

| 0.0  | Cash  | e Central                                                                              | <b>F7</b> |

| 9.0  |       | e Control                                                                              |           |

|      | 9.1   | MTRR Programming                                                                       |           |

|      | 9.2   | Processor Implications with Cached SMM Handler                                         |           |

|      |       | 9.2.1 System Management Mode Range Register                                            | . 58      |

|      |       | 9.2.1.1 UEFI Firmware Steps to Enable and Configure SMRR                               |           |

|      | 9.3   | UEFI Firmware Sources                                                                  | . 59      |

| 10.0 | Intel | <sup>®</sup> Legacy SPI Controller                                                     | . 60      |

|      | 10.1  | Legacy SPI Flash Decode Enable                                                         |           |

|      | 10.2  | Legacy SPI Flash Base Address                                                          |           |

|      | 10.3  | Write Protecting SPI Flash Ranges                                                      |           |

|      | 10.4  | Opcode/Opcode Type/Prefix Opcode Configuration                                         |           |

|      | 10.5  | Configuration Lockdown                                                                 |           |

|      | 10.6  | Legacy SPI Flash Update Protection                                                     | 61        |

|      | 10.7  | UEFI Firmware Sources                                                                  |           |

|      |       |                                                                                        |           |

| 11.0 |       | t Control                                                                              |           |

|      | 11.1  | Reset Control Overview                                                                 |           |

|      | 11.2  | Cold and Warm Reset Control                                                            |           |

|      | 11.3  | UEFI Firmware Sources                                                                  | . 63      |

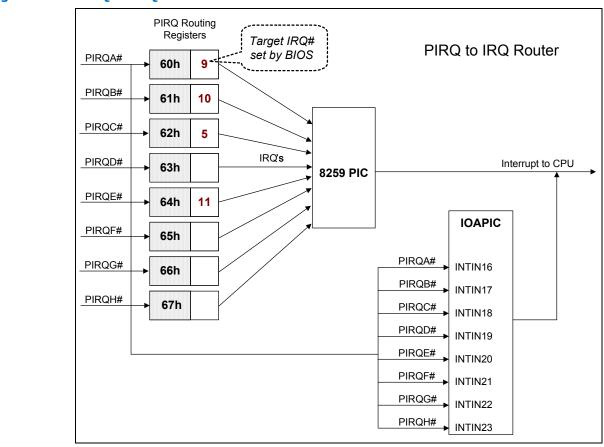

| 120  | РСТ Т | RQ Routing                                                                             | 64        |

| 12.0 | 12.1  | PCI Interrupt to IRQ Router                                                            |           |

|      |       |                                                                                        |           |

|      | 12.2  | Interrupt Routing for Internal Agents<br>Interrupt Routing for PCI Express* Root Ports | . 05      |

|      | 12.3  |                                                                                        |           |

|      | 12.4  | Reporting Interrupt Routing to the OS                                                  | . 6/      |

|      |       | 12.4.1 Example PRT Packages for Interrupt Routing                                      | . 68      |

|      | 12.5  | UEFI Firmware Sources                                                        | .69 |

|------|-------|------------------------------------------------------------------------------|-----|

| 13.0 | PCI E | xpress* Support                                                              | 70  |

|      |       | PCI Express* Configuration Space Base Address                                |     |

|      | -     | 13.1.1 Releasing PCIe Controller from Reset                                  |     |

|      |       | 13.1.2 Bus: Device: Function: Register Offset Translation                    |     |

|      |       | 13.1.3 Register Access Using Capabilities List                               | .71 |

|      |       | 13.1.4 Device/Port Type Field of PCI Express* Devices                        | .72 |

|      |       | 13.1.5 Initialize "Slot Implemented" for Root Ports                          | .72 |

|      |       | 13.1.6 Initialize "Physical Slot Number" for Root Ports                      | 72  |

|      |       | 13.1.7 Initialize "Slot Power Limit" for Root Ports                          |     |

|      |       | 13.1.8 Port Configuration Registers                                          |     |

|      |       | 13.1.9 SCI/SMI Generation                                                    |     |

|      | 13.2  | RCRB (Root Complex Register Block)                                           |     |

|      | 13.3  | Root Complex Topology Programming                                            |     |

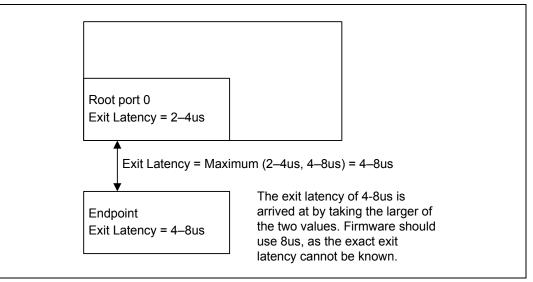

|      | 13.4  | PCI Express* Active State Power Management (ASPM)                            |     |

|      |       | 13.4.1 Root Port LOs Exit Latency Initialization by Firmware                 |     |

|      |       | 13.4.2 Calculation of Total L-State Exit Latency                             |     |

|      |       | 13.4.3 Firmware Software Flow for Enabling ASPM<br>13.4.4 ASPM vs. Isochrony |     |

|      | 13.5  | Root Port Error Reporting                                                    |     |

|      | 15.5  | 13.5.1 SERR# Generation                                                      |     |

|      | 13.6  | PCI Firmware Spec 3.0 Support                                                |     |

|      | 13.7  | ACPI Table and Methods for PCI Express* Support                              | 76  |

|      | 15.7  | 13.7.1 MCFG Table                                                            | 76  |

|      |       | 13.7.2 _HID and CID for PCI Host Bridge                                      | .79 |

|      |       | 13.7.3 _OSC() Method                                                         |     |

|      | 13.8  | PCI Express* PME Firmware Support                                            |     |

|      |       | 13.8.1 Native PME Software Model                                             | .82 |

|      |       | 13.8.2 Legacy PME Software Model                                             | .82 |

|      |       | 13.8.3 Firmware Enabling of PCI Express* PME SCI Generation                  | .82 |

|      |       | 13.8.4 Handling PCI Express* PME SCI Event                                   |     |

|      |       | 13.8.4.1 General Mechanism and Sequence                                      | .83 |

|      |       | 13.8.4.2 Firmware GPE Handler for PME Event                                  |     |

|      |       | 13.8.5 Transition from Legacy to Native PME Software Model                   |     |

|      | 12.0  | 13.8.6 WAKE# Support<br>UEFI Firmware Sources.                               |     |

|      | 13.9  |                                                                              |     |

| 14.0 | Proce | essor Interface                                                              |     |

|      | 14.1  |                                                                              |     |

|      |       | 14.1.1 Configuration of the IOxAPIC                                          |     |

|      |       | 14.1.2 Steps Involved in Delivering the Interrupt                            |     |

|      | 14.2  | UEFI Firmware Sources                                                        | .87 |

| 15.0 | NMI   | Handling                                                                     | 88  |

|      | 15.1  | Settings to Generate NMI                                                     | 88  |

|      | 15.2  | Steps for Handling NMI                                                       |     |

|      |       | 15.2.1 Steps for Execution                                                   | 88  |

|      | 15.3  | UEFI Firmware Sources                                                        | .89 |

| 16.0 | SMT I | Handling                                                                     | 90  |

| 10.0 | 16.1  | SMI on Sleep Enable                                                          |     |

|      | 16.2  | Setting the EOS Bit                                                          |     |

|      | 16.3  | SMI Status Bits                                                              |     |

|      |       |                                                                              |     |

| 17.0 |       |                                                                              |     |

| 1/.0 | POWe  | er Management                                                                | .92 |

|      | 17.1                                                                                                                                                    | Power Button Override                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 17.2                                                                                                                                                    | Power Failure Considerations                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 17.3                                                                                                                                                    | Processor Throttling                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 17.4                                                                                                                                                    | C States                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                                                                                                                         | 17.4.1 IRQ Break Events for C1 State               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                                                                                                                         | 17.4.2 C2 State Support                            | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                                                                                                                         | 17.4.3 Cx State Support Reporting for ACPI OS      | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                                                                                                                         | 17.4.4 Break Events                                | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | 17.5                                                                                                                                                    | Wake Events                                        | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | 17.6                                                                                                                                                    | UEFI Firmware Sources                              | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 100  | Suce                                                                                                                                                    | end Handler Considerations                         | 05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10.0 |                                                                                                                                                         |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 18.1                                                                                                                                                    | Power-On Suspend Handling Preparation              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 18.2                                                                                                                                                    | S3 Entry Steps.                                    | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                                                                                                                         | 18.2.1 Initiating Sleep States via SLP_EN Bit      | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | 18.3                                                                                                                                                    | S3 Resume Steps                                    | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | 18.4                                                                                                                                                    | UEFI Firmware Sources                              | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 19.0 | Hiah                                                                                                                                                    | Performance Event Timer (HPET) Support             | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | 19.1                                                                                                                                                    | HPET Basic Configuration                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                                                                                                                         | UEFI Firmware Sources                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                                                                                                                         |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 20.0 |                                                                                                                                                         | Handling                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 20.1                                                                                                                                                    | Legacy GPIOs                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                                                                                                                         | 20.1.1 Legacy GPIO Configuration                   | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |                                                                                                                                                         | 20.1.2 Legacy GPIO Interrupt Handling              | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | 20.2                                                                                                                                                    | Chipset South Cluster GPIO Controller              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                                                                                                                         | 20.2.1 South Cluster GPIO Controller Configuration | . 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 20.3                                                                                                                                                    | UEFI Firmware Sources                              | . 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      |                                                                                                                                                         |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 21 0 | Secur                                                                                                                                                   | ity Enhancements                                   | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 21.0 |                                                                                                                                                         | ity Enhancements                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 21.0 |                                                                                                                                                         | Introduction                                       | . 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21.0 | 21.1                                                                                                                                                    | Introduction                                       | . 102<br>. 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 21.0 | 21.1                                                                                                                                                    | Introduction                                       | . 102<br>. 102<br>. 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 21.0 | 21.1<br>21.2                                                                                                                                            | Introduction                                       | . 102<br>. 102<br>. 102<br>. 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 21.0 | 21.1<br>21.2<br>21.3                                                                                                                                    | Introduction                                       | . 102<br>. 102<br>. 102<br>. 103<br>. 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 21.0 | 21.1<br>21.2                                                                                                                                            | Introduction                                       | . 102<br>. 102<br>. 102<br>. 103<br>. 103<br>. 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 21.0 | 21.1<br>21.2<br>21.3                                                                                                                                    | Introduction                                       | . 102<br>. 102<br>. 103<br>. 103<br>. 103<br>. 104<br>. 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 21.0 | 21.1<br>21.2<br>21.3                                                                                                                                    | Introduction                                       | . 102<br>. 102<br>. 103<br>. 103<br>. 103<br>. 104<br>. 104<br>. 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 21.0 | 21.1<br>21.2<br>21.3                                                                                                                                    | Introduction                                       | . 102<br>. 102<br>. 102<br>. 103<br>. 103<br>. 103<br>. 104<br>. 104<br>. 104<br>. 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

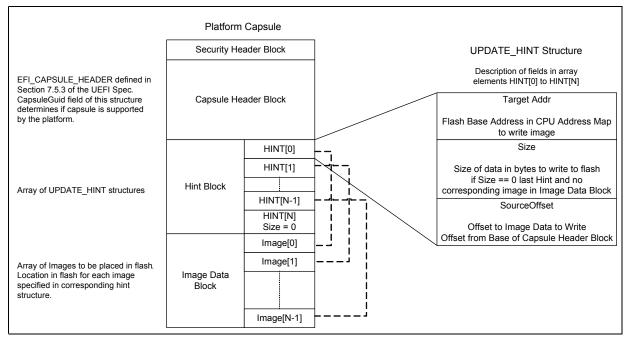

| 21.0 | 21.1<br>21.2<br>21.3                                                                                                                                    | Introduction                                       | . 102<br>. 102<br>. 103<br>. 103<br>. 103<br>. 104<br>. 104<br>. 104<br>. 104<br>. 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |